8051 Interrupts Lec note 8 hsabaghianb kashanu ac

8051 Interrupts Lec note 8 hsabaghianb @ kashanu. ac. ir Microprocessors 8 -1

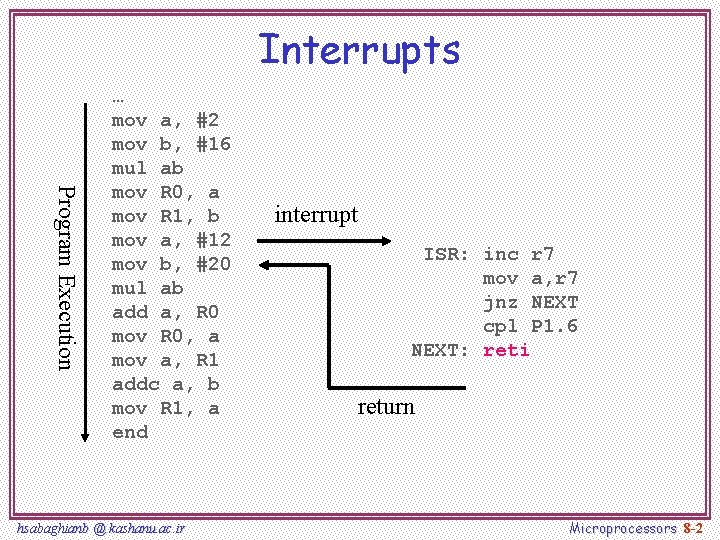

Interrupts Program Execution … mov a, #2 mov b, #16 mul ab mov R 0, a mov R 1, b mov a, #12 mov b, #20 mul ab add a, R 0 mov R 0, a mov a, R 1 addc a, b mov R 1, a end hsabaghianb @ kashanu. ac. ir interrupt ISR: inc r 7 mov a, r 7 jnz NEXT cpl P 1. 6 NEXT: reti return Microprocessors 8 -2

Interrupts Programming q An interrupt is an external or internal event that interrupts the microcontroller to inform it that a device needs its service. Interrupts vs. Polling q A single microcontroller can serve several devices. q There are two ways to do that: v interrupts v polling. q The program which is associated with the interrupt is called the interrupt service routine (ISR) or interrupt handler. hsabaghianb @ kashanu. ac. ir Microprocessors 8 -3

Steps in executing an interrupt q Finish current instruction and saves the PC on stack. q Jumps to a fixed location in memory depend on type of interrupt q Starts to execute the interrupt service routine until RETI (return from interrupt( q Upon executing the RETI the microcontroller returns to the place where it was interrupted. Get pop PC from stack hsabaghianb @ kashanu. ac. ir Microprocessors 8 -4

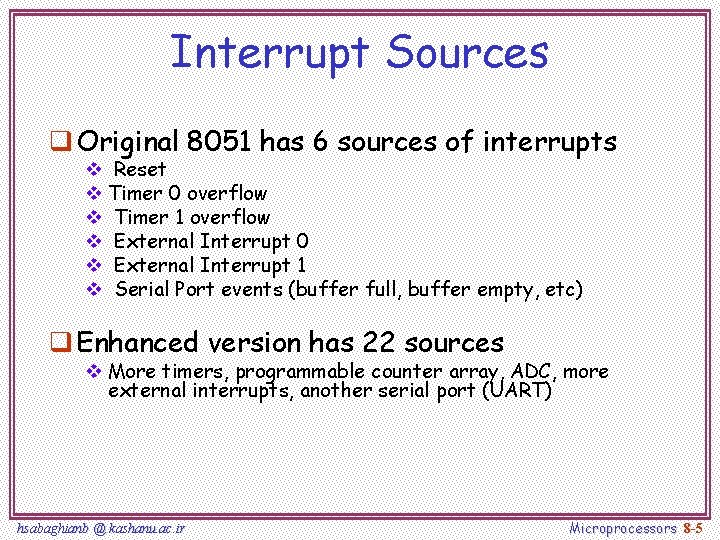

Interrupt Sources q Original 8051 has 6 sources of interrupts v Reset v Timer 0 overflow v Timer 1 overflow v External Interrupt 0 v External Interrupt 1 v Serial Port events (buffer full, buffer empty, etc) q Enhanced version has 22 sources v More timers, programmable counter array, ADC, more external interrupts, another serial port (UART) hsabaghianb @ kashanu. ac. ir Microprocessors 8 -5

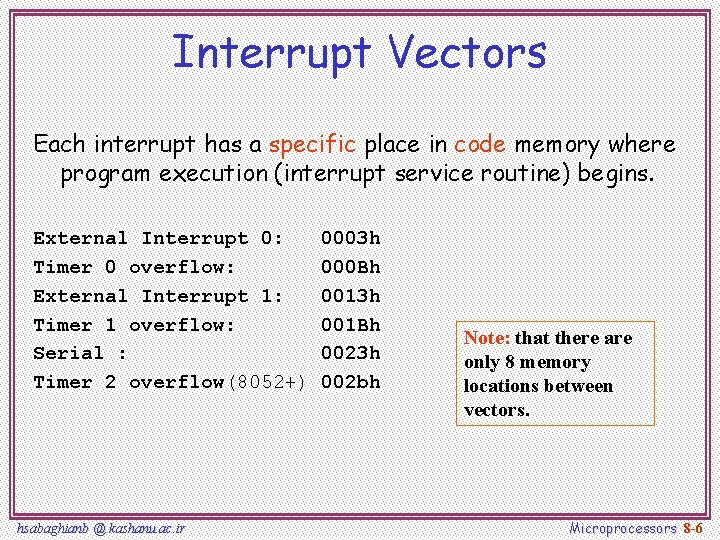

Interrupt Vectors Each interrupt has a specific place in code memory where program execution (interrupt service routine) begins. External Interrupt 0: Timer 0 overflow: External Interrupt 1: Timer 1 overflow: Serial : Timer 2 overflow(8052+) hsabaghianb @ kashanu. ac. ir 0003 h 000 Bh 0013 h 001 Bh 0023 h 002 bh Note: that there are only 8 memory locations between vectors. Microprocessors 8 -6

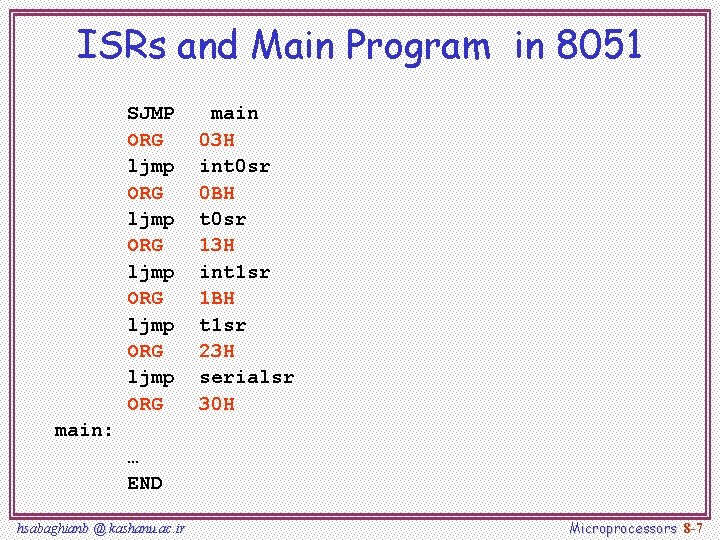

ISRs and Main Program in 8051 SJMP ORG ljmp ORG ljmp ORG main 03 H int 0 sr 0 BH t 0 sr 13 H int 1 sr 1 BH t 1 sr 23 H serialsr 30 H main: … END hsabaghianb @ kashanu. ac. ir Microprocessors 8 -7

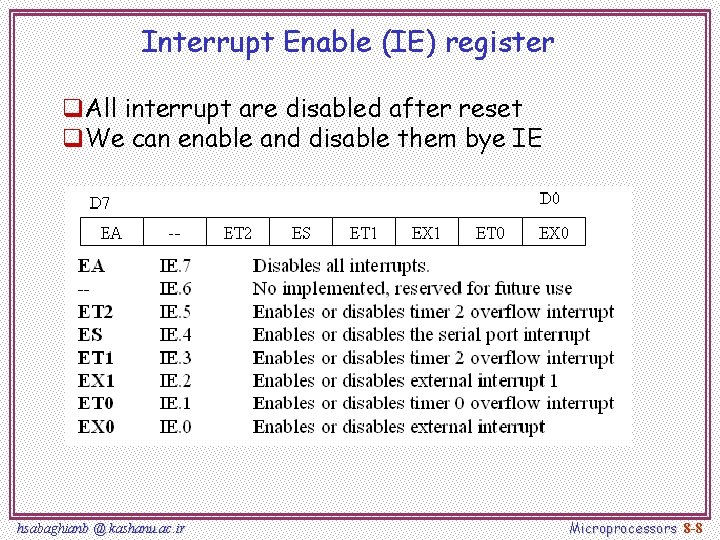

Interrupt Enable (IE) register q. All interrupt are disabled after reset q. We can enable and disable them bye IE hsabaghianb @ kashanu. ac. ir Microprocessors 8 -8

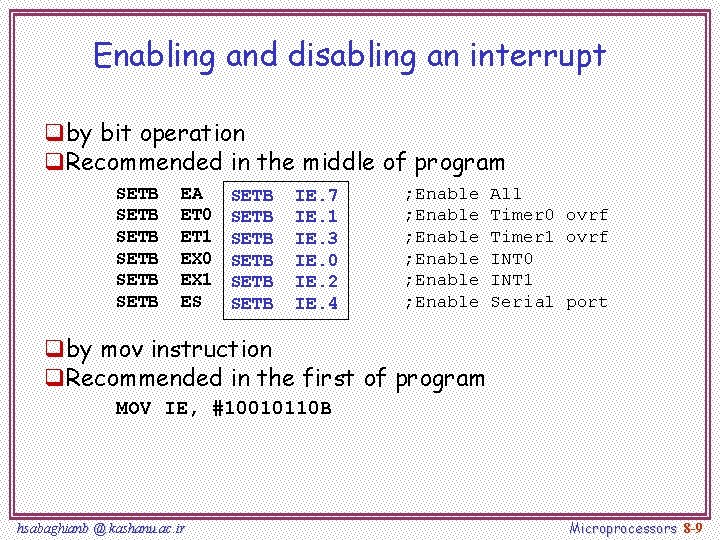

Enabling and disabling an interrupt qby bit operation q. Recommended in the middle of program SETB SETB EA ET 0 ET 1 EX 0 EX 1 ES SETB SETB IE. 7 IE. 1 IE. 3 IE. 0 IE. 2 IE. 4 ; Enable ; Enable All Timer 0 ovrf Timer 1 ovrf INT 0 INT 1 Serial port qby mov instruction q. Recommended in the first of program MOV IE, #10010110 B hsabaghianb @ kashanu. ac. ir Microprocessors 8 -9

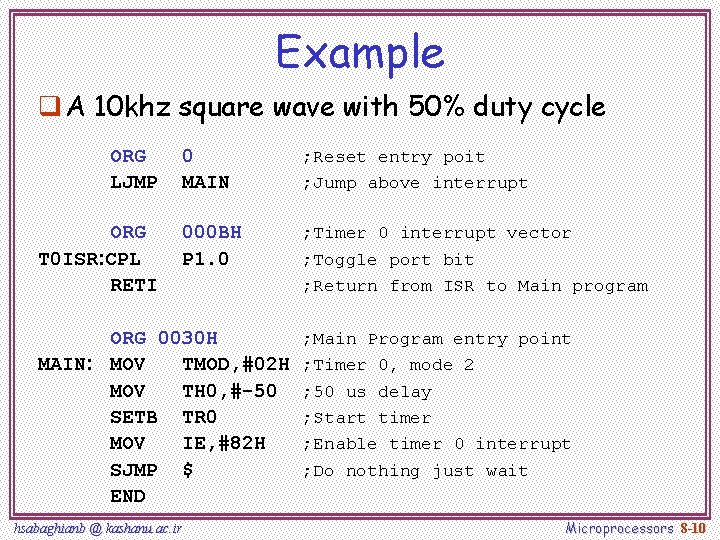

Example q A 10 khz square wave with 50% duty cycle ORG LJMP ORG T 0 ISR: CPL RETI 0 MAIN ; Reset entry poit ; Jump above interrupt 000 BH P 1. 0 ; Timer 0 interrupt vector ; Toggle port bit ; Return from ISR to Main program ORG 0030 H MAIN: MOV TMOD, #02 H MOV TH 0, #-50 SETB TR 0 MOV IE, #82 H SJMP $ END hsabaghianb @ kashanu. ac. ir ; Main Program entry point ; Timer 0, mode 2 ; 50 us delay ; Start timer ; Enable timer 0 interrupt ; Do nothing just wait Microprocessors 8 -10

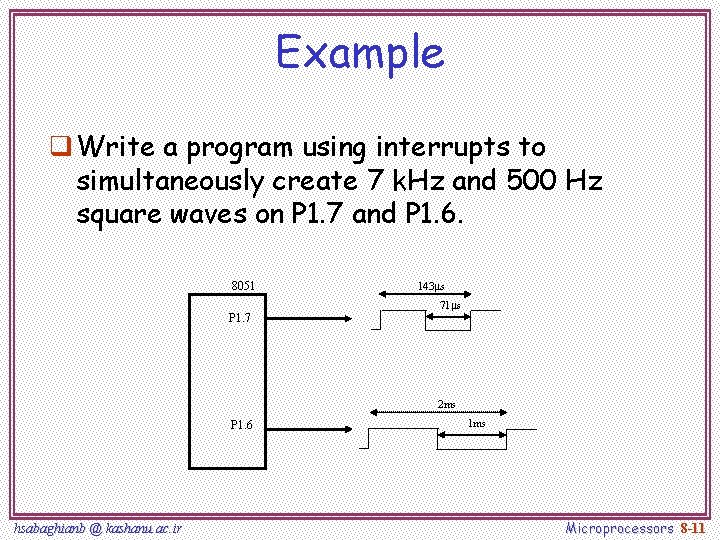

Example q Write a program using interrupts to simultaneously create 7 k. Hz and 500 Hz square waves on P 1. 7 and P 1. 6. 8051 P 1. 7 143 s 71 s 2 ms P 1. 6 hsabaghianb @ kashanu. ac. ir 1 ms Microprocessors 8 -11

ORG LJMP ORG MAIN: MOV SETB MOV SJMP T 0 ISR: CPL RETI T 1 ISR: CLR MOV SETB CPL RETI END 0 MAIN 000 BH T 0 ISR 001 BH T 1 ISR 0030 H TMOD, #12 H TH 0, #-71 TR 0 TF 1 IE, #8 AH $ P 1. 7 Solution 8051 P 1. 7 143 s 71 s 2 ms P 1. 6 1 ms TR 1 TH 1, #HIGH(-1000) TL 1, #LOW(-1000) TR 1 P 1. 6 hsabaghianb @ kashanu. ac. ir Microprocessors 8 -12

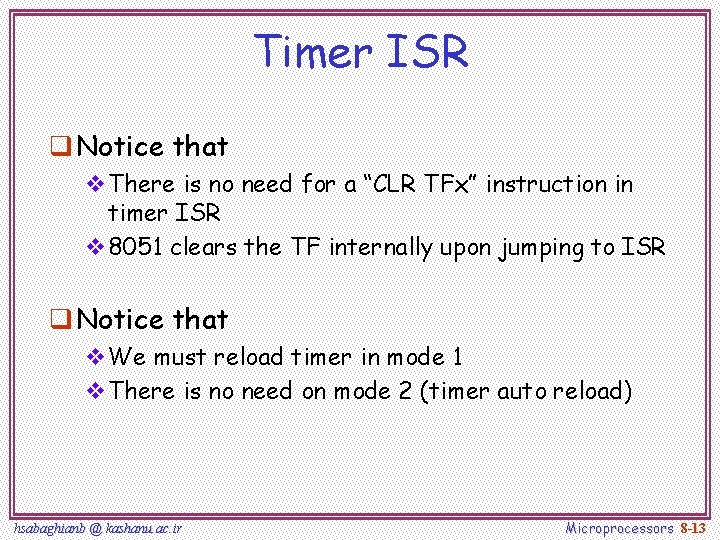

Timer ISR q Notice that v. There is no need for a “CLR TFx” instruction in timer ISR v 8051 clears the TF internally upon jumping to ISR q Notice that v. We must reload timer in mode 1 v. There is no need on mode 2 (timer auto reload) hsabaghianb @ kashanu. ac. ir Microprocessors 8 -13

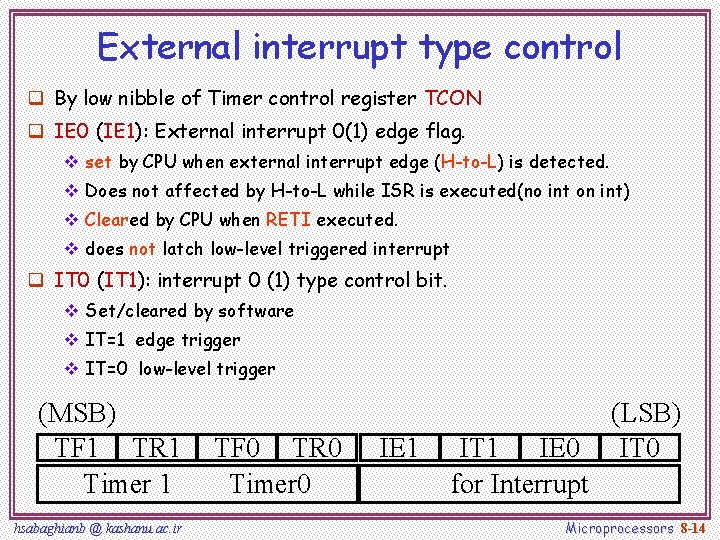

External interrupt type control q By low nibble of Timer control register TCON q IE 0 (IE 1): External interrupt 0(1) edge flag. v set by CPU when external interrupt edge (H-to-L) is detected. v Does not affected by H-to-L while ISR is executed(no int on int) v Cleared by CPU when RETI executed. v does not latch low-level triggered interrupt q IT 0 (IT 1): interrupt 0 (1) type control bit. v Set/cleared by software v IT=1 edge trigger v IT=0 low-level trigger (MSB) TF 1 TR 1 Timer 1 hsabaghianb @ kashanu. ac. ir TF 0 TR 0 Timer 0 IE 1 IT 1 IE 0 for Interrupt (LSB) IT 0 Microprocessors 8 -14

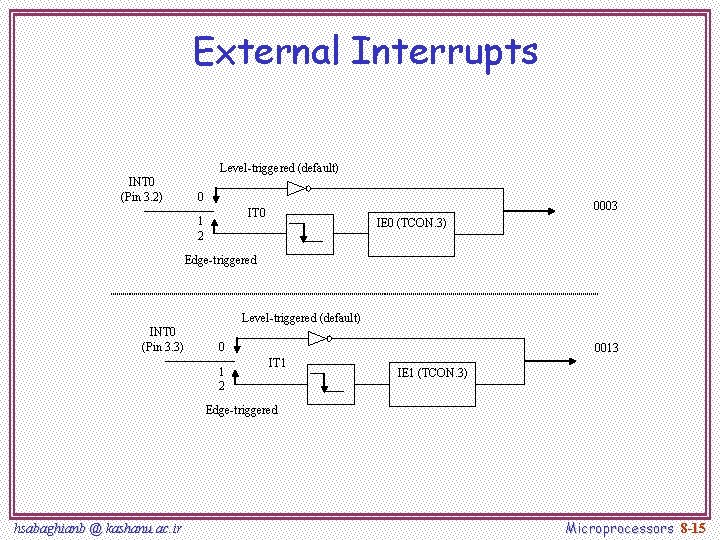

External Interrupts Level-triggered (default) INT 0 (Pin 3. 2) 0 0003 IT 0 1 2 IE 0 (TCON. 3) Edge-triggered Level-triggered (default) INT 0 (Pin 3. 3) 0 1 2 0013 IT 1 IE 1 (TCON. 3) Edge-triggered hsabaghianb @ kashanu. ac. ir Microprocessors 8 -15

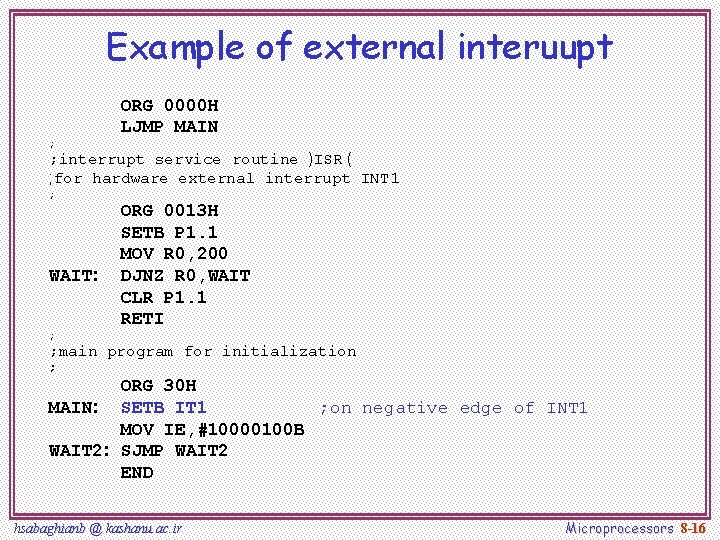

Example of external interuupt ORG 0000 H LJMP MAIN ; ; interrupt service routine )ISR ( ; for hardware external interrupt INT 1 ; WAIT: ORG 0013 H SETB P 1. 1 MOV R 0, 200 DJNZ R 0, WAIT CLR P 1. 1 RETI ; ; main program for initialization ; ORG 30 H MAIN: SETB IT 1 ; on negative edge of INT 1 MOV IE, #10000100 B WAIT 2: SJMP WAIT 2 END hsabaghianb @ kashanu. ac. ir Microprocessors 8 -16

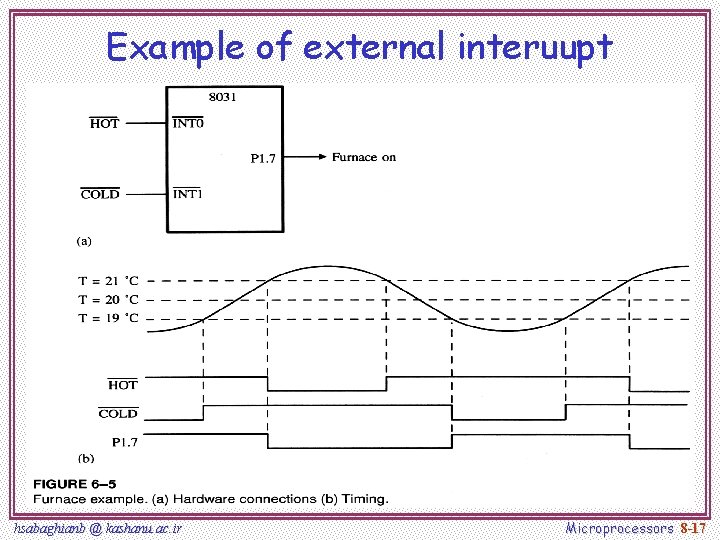

Example of external interuupt hsabaghianb @ kashanu. ac. ir Microprocessors 8 -17

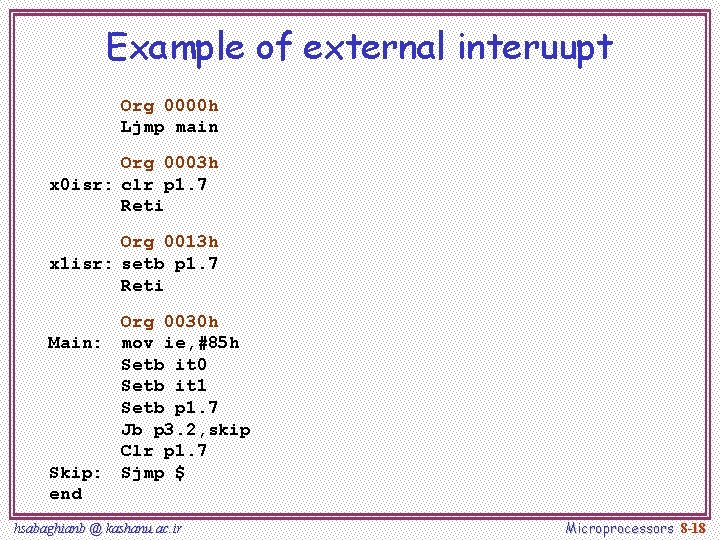

Example of external interuupt Org 0000 h Ljmp main Org 0003 h x 0 isr: clr p 1. 7 Reti Org 0013 h x 1 isr: setb p 1. 7 Reti Main: Skip: end Org 0030 h mov ie, #85 h Setb it 0 Setb it 1 Setb p 1. 7 Jb p 3. 2, skip Clr p 1. 7 Sjmp $ hsabaghianb @ kashanu. ac. ir Microprocessors 8 -18

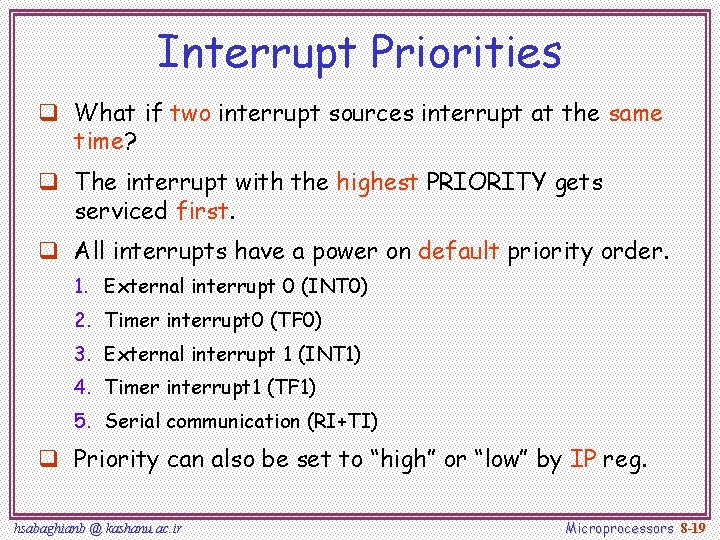

Interrupt Priorities q What if two interrupt sources interrupt at the same time? q The interrupt with the highest PRIORITY gets serviced first. q All interrupts have a power on default priority order. 1. External interrupt 0 (INT 0) 2. Timer interrupt 0 (TF 0) 3. External interrupt 1 (INT 1) 4. Timer interrupt 1 (TF 1) 5. Serial communication (RI+TI) q Priority can also be set to “high” or “low” by IP reg. hsabaghianb @ kashanu. ac. ir Microprocessors 8 -19

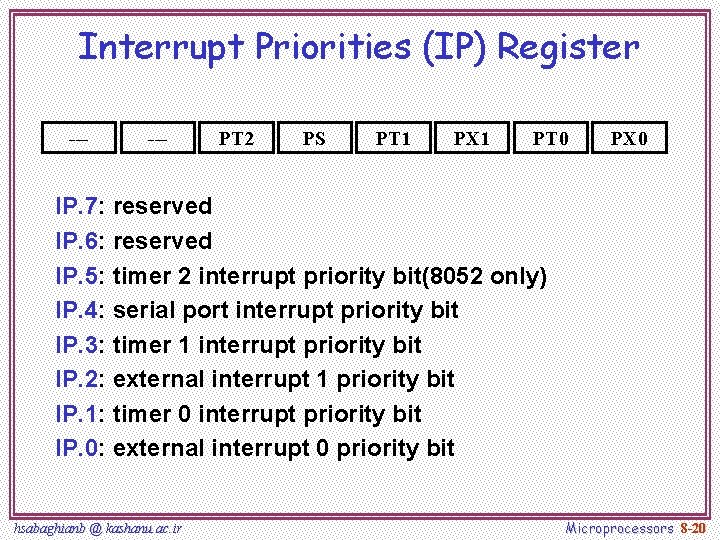

Interrupt Priorities (IP) Register --- PT 2 PS PT 1 PX 1 PT 0 PX 0 IP. 7: reserved IP. 6: reserved IP. 5: timer 2 interrupt priority bit(8052 only) IP. 4: serial port interrupt priority bit IP. 3: timer 1 interrupt priority bit IP. 2: external interrupt 1 priority bit IP. 1: timer 0 interrupt priority bit IP. 0: external interrupt 0 priority bit hsabaghianb @ kashanu. ac. ir Microprocessors 8 -20

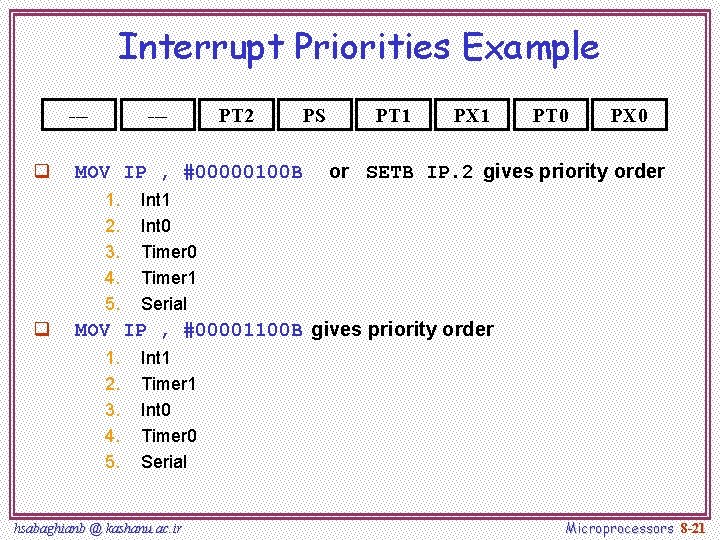

Interrupt Priorities Example --- q --- MOV IP , #00000100 B 1. 2. 3. 4. 5. q PT 2 PS PT 1 PX 1 PT 0 PX 0 or SETB IP. 2 gives priority order Int 1 Int 0 Timer 1 Serial MOV IP , #00001100 B gives priority order 1. 2. 3. 4. 5. Int 1 Timer 1 Int 0 Timer 0 Serial hsabaghianb @ kashanu. ac. ir Microprocessors 8 -21

Interrupt inside an interrupt --- PT 2 PS PT 1 PX 1 PT 0 PX 0 q A high-priority interrupt can interrupt a low-priority interrupy q All interrupt are latched internally q Low-priority interrupt wait until 8051 has finished servicing the high-priority interrupt hsabaghianb @ kashanu. ac. ir Microprocessors 8 -22

- Slides: 22