ROM m1 bit Address A 0 A 1

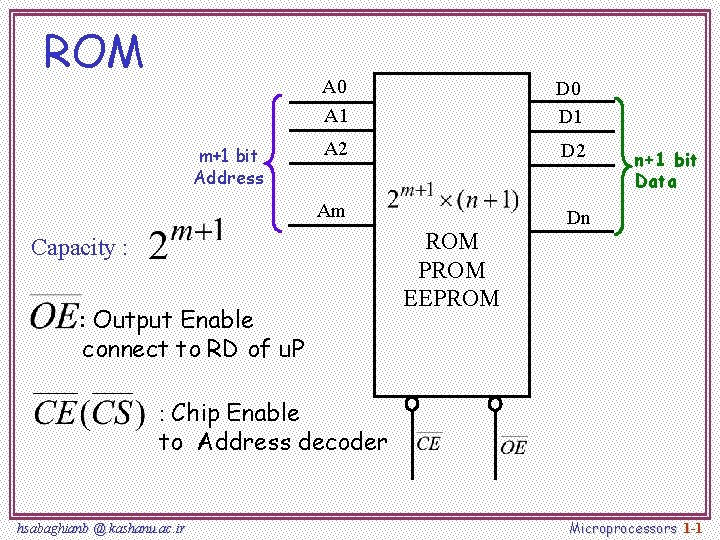

ROM m+1 bit Address A 0 A 1 D 0 D 1 A 2 D 2 Am Dn Capacity : : Output Enable connect to RD of u. P ROM PROM EEPROM n+1 bit Data : Chip Enable to Address decoder hsabaghianb @ kashanu. ac. ir Microprocessors 1 -1

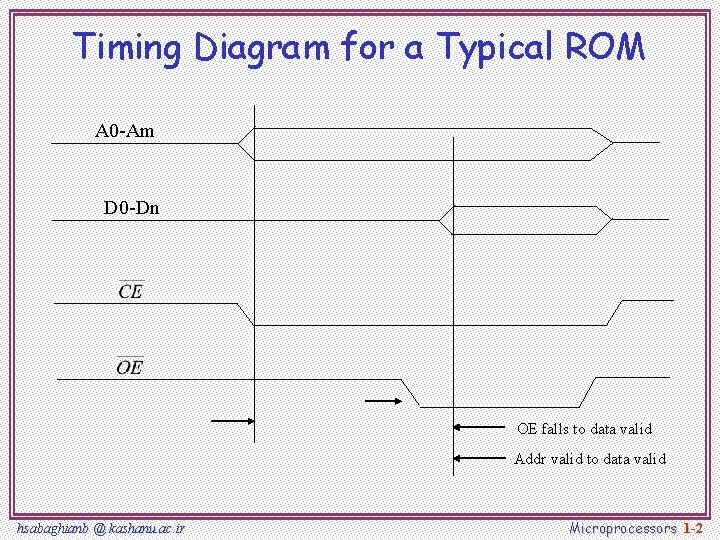

Timing Diagram for a Typical ROM A 0 -Am D 0 -Dn OE falls to data valid Addr valid to data valid hsabaghianb @ kashanu. ac. ir Microprocessors 1 -2

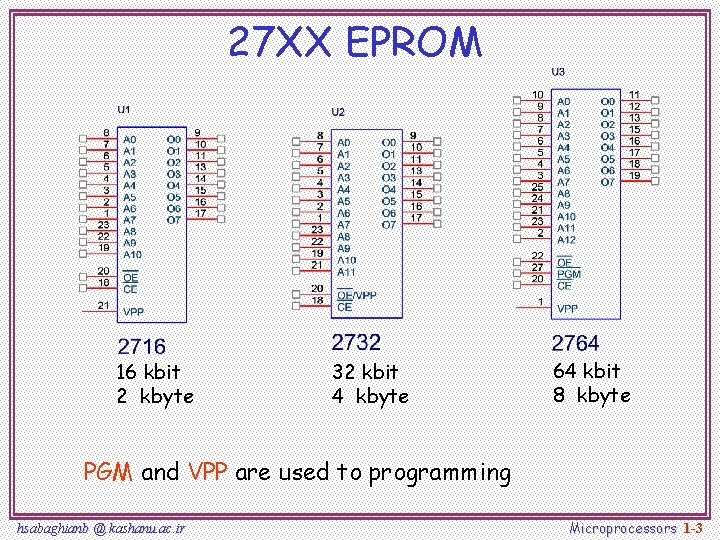

27 XX EPROM 16 kbit 2 kbyte 32 kbit 4 kbyte 64 kbit 8 kbyte PGM and VPP are used to programming hsabaghianb @ kashanu. ac. ir Microprocessors 1 -3

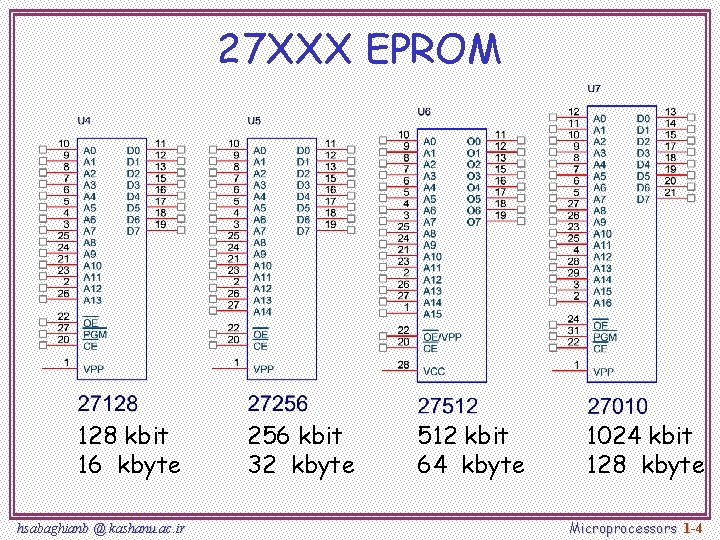

27 XXX EPROM 128 kbit 16 kbyte hsabaghianb @ kashanu. ac. ir 256 kbit 32 kbyte 512 kbit 64 kbyte 1024 kbit 128 kbyte Microprocessors 1 -4

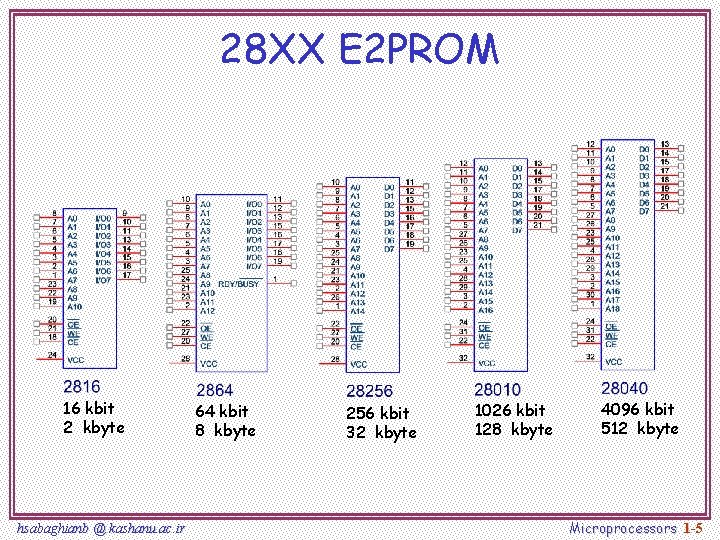

28 XX E 2 PROM 16 kbit 2 kbyte hsabaghianb @ kashanu. ac. ir 64 kbit 8 kbyte 256 kbit 32 kbyte 1026 kbit 128 kbyte 4096 kbit 512 kbyte Microprocessors 1 -5

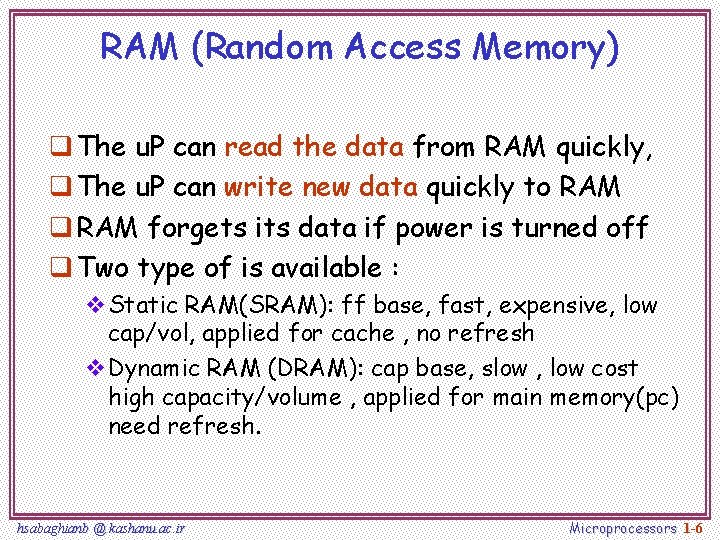

RAM (Random Access Memory) q The u. P can read the data from RAM quickly, q The u. P can write new data quickly to RAM q RAM forgets its data if power is turned off q Two type of is available : v. Static RAM(SRAM): ff base, fast, expensive, low cap/vol, applied for cache , no refresh v. Dynamic RAM (DRAM): cap base, slow , low cost high capacity/volume , applied for main memory(pc) need refresh. hsabaghianb @ kashanu. ac. ir Microprocessors 1 -6

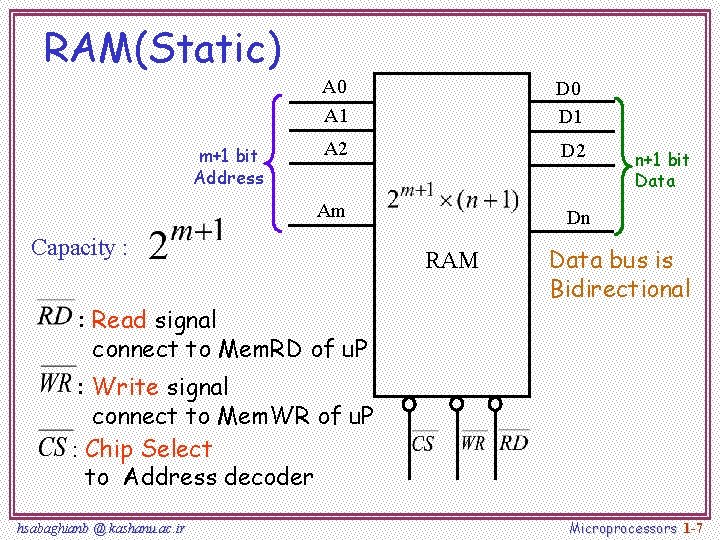

RAM(Static) m+1 bit Address A 0 A 1 D 0 D 1 A 2 D 2 Am Dn Capacity : : Read signal connect to Mem. RD of u. P RAM n+1 bit Data bus is Bidirectional : Write signal connect to Mem. WR of u. P : Chip Select to Address decoder hsabaghianb @ kashanu. ac. ir Microprocessors 1 -7

Z 80 CPU Pin Assignment hsabaghianb @ kashanu. ac. ir Microprocessors 1 -8

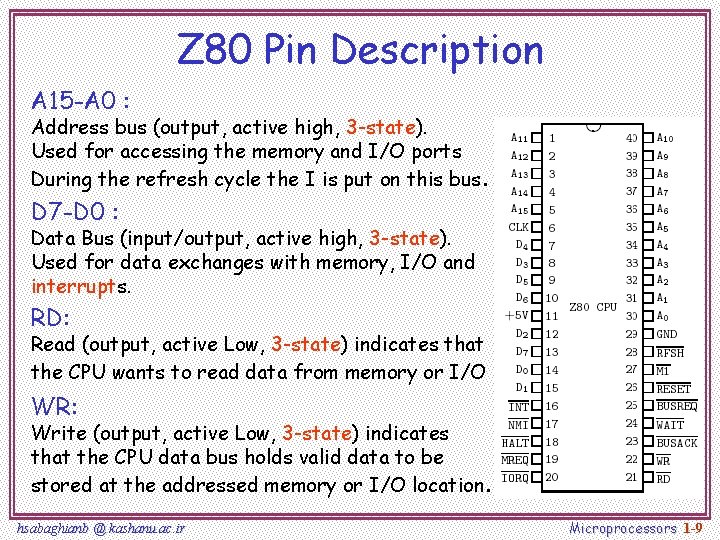

Z 80 Pin Description A 15 -A 0 : Address bus (output, active high, 3 -state). Used for accessing the memory and I/O ports During the refresh cycle the I is put on this bus. D 7 -D 0 : Data Bus (input/output, active high, 3 -state). Used for data exchanges with memory, I/O and interrupts. RD: Read (output, active Low, 3 -state) indicates that the CPU wants to read data from memory or I/O WR: Write (output, active Low, 3 -state) indicates that the CPU data bus holds valid data to be stored at the addressed memory or I/O location. hsabaghianb @ kashanu. ac. ir Microprocessors 1 -9

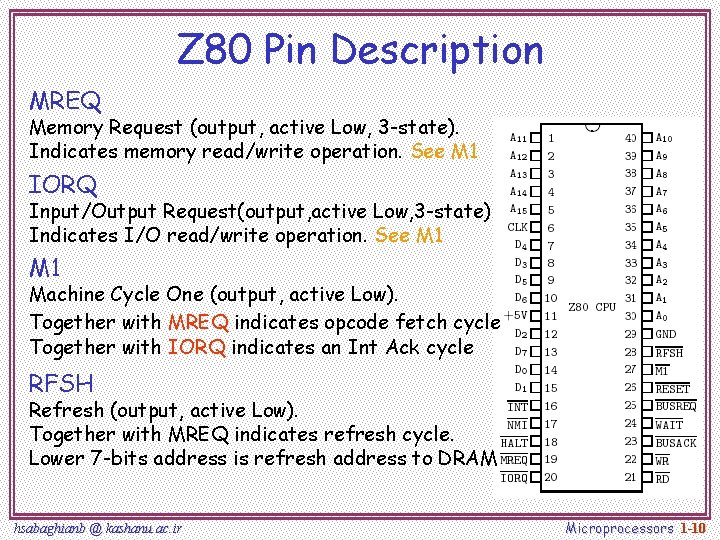

Z 80 Pin Description MREQ Memory Request (output, active Low, 3 -state). Indicates memory read/write operation. See M 1 IORQ Input/Output Request(output, active Low, 3 -state) Indicates I/O read/write operation. See M 1 Machine Cycle One (output, active Low). Together with MREQ indicates opcode fetch cycle Together with IORQ indicates an Int Ack cycle RFSH Refresh (output, active Low). Together with MREQ indicates refresh cycle. Lower 7 -bits address is refresh address to DRAM hsabaghianb @ kashanu. ac. ir Microprocessors 1 -10

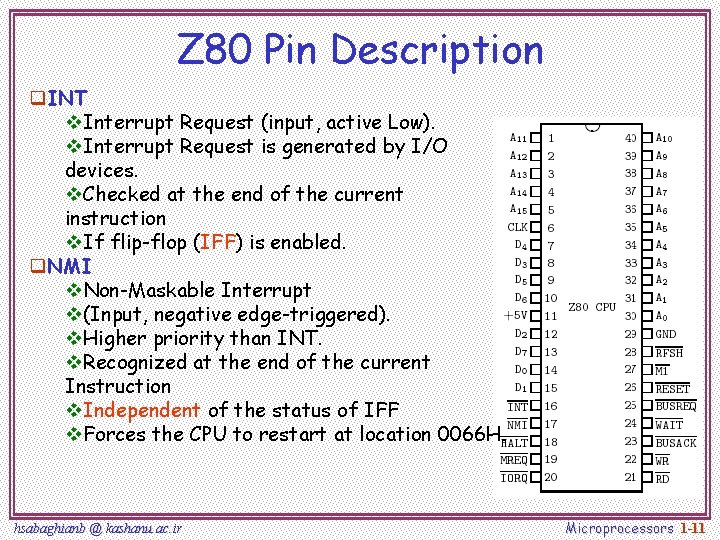

Z 80 Pin Description q. INT v. Interrupt Request (input, active Low). v. Interrupt Request is generated by I/O devices. v. Checked at the end of the current instruction v. If flip-flop (IFF) is enabled. q. NMI v. Non-Maskable Interrupt v(Input, negative edge-triggered). v. Higher priority than INT. v. Recognized at the end of the current Instruction v. Independent of the status of IFF v. Forces the CPU to restart at location 0066 H. hsabaghianb @ kashanu. ac. ir Microprocessors 1 -11

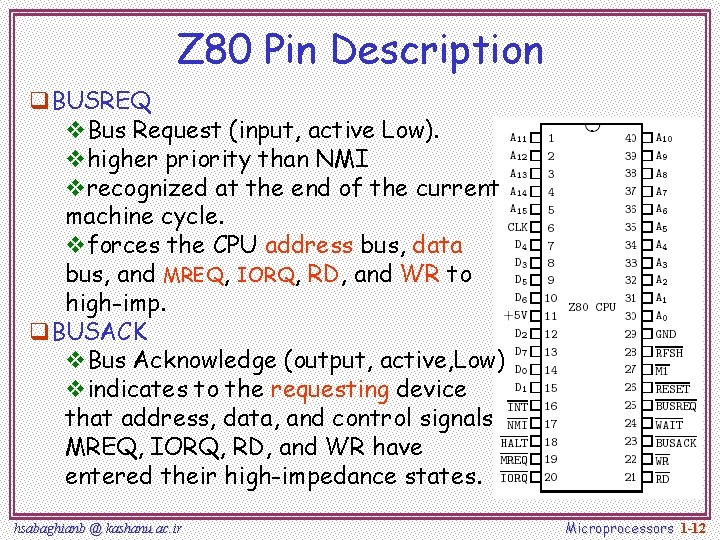

Z 80 Pin Description q. BUSREQ v. Bus Request (input, active Low). vhigher priority than NMI vrecognized at the end of the current machine cycle. vforces the CPU address bus, data bus, and MREQ, IORQ, RD, and WR to high-imp. q. BUSACK v. Bus Acknowledge (output, active, Low) vindicates to the requesting device that address, data, and control signals MREQ, IORQ, RD, and WR have entered their high-impedance states. hsabaghianb @ kashanu. ac. ir Microprocessors 1 -12

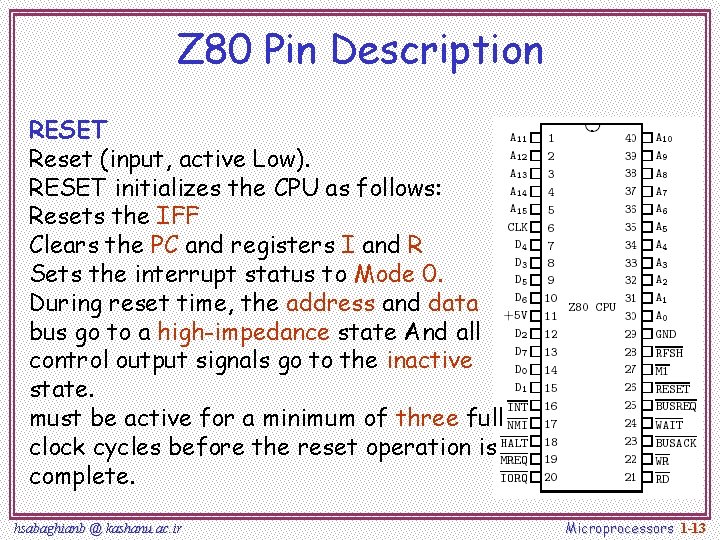

Z 80 Pin Description RESET Reset (input, active Low). RESET initializes the CPU as follows: Resets the IFF Clears the PC and registers I and R Sets the interrupt status to Mode 0. During reset time, the address and data bus go to a high-impedance state And all control output signals go to the inactive state. must be active for a minimum of three full clock cycles before the reset operation is complete. hsabaghianb @ kashanu. ac. ir Microprocessors 1 -13

Z 80 CPU hsabaghianb @ kashanu. ac. ir Microprocessors 1 -14

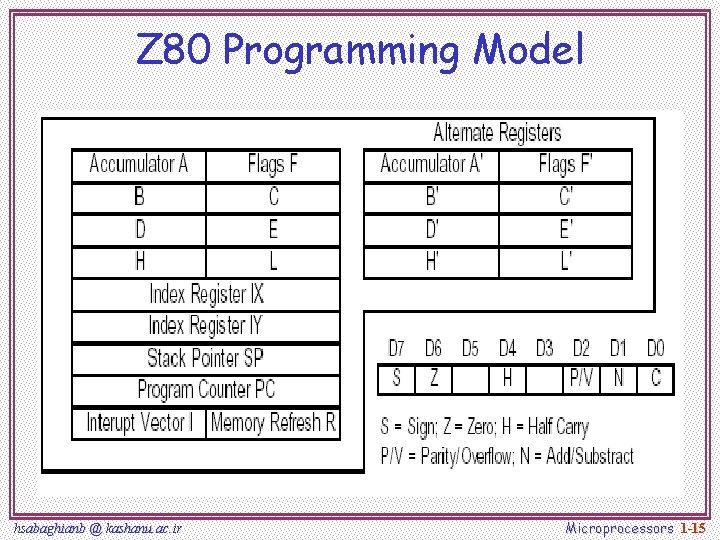

Z 80 Programming Model hsabaghianb @ kashanu. ac. ir Microprocessors 1 -15

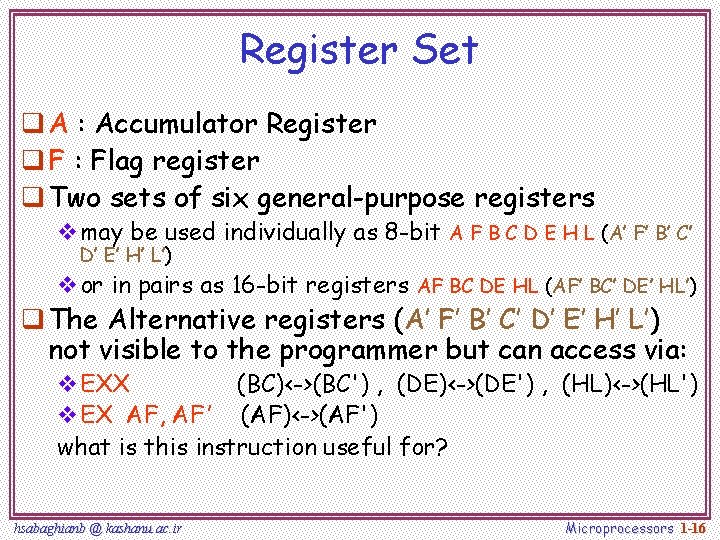

Register Set q A : Accumulator Register q F : Flag register q Two sets of six general-purpose registers vmay be used individually as 8 -bit A F B C D E H L (A’ F’ B’ C’ D’ E’ H’ L’) vor in pairs as 16 -bit registers AF BC DE HL (AF’ BC’ DE’ HL’) q The Alternative registers (A’ F’ B’ C’ D’ E’ H’ L’) not visible to the programmer but can access via: v. EXX (BC)<->(BC') , (DE)<->(DE') , (HL)<->(HL') v. EX AF, AF ’ (AF)<->(AF') what is this instruction useful for? hsabaghianb @ kashanu. ac. ir Microprocessors 1 -16

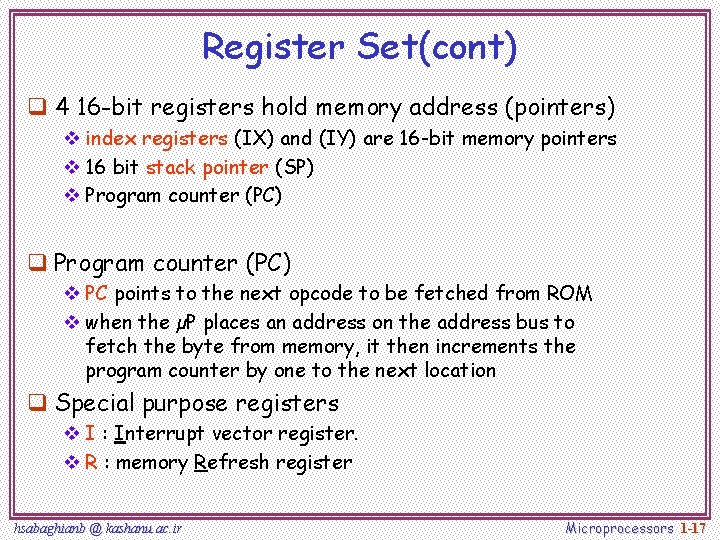

Register Set(cont) q 4 16 -bit registers hold memory address (pointers) v index registers (IX) and (IY) are 16 -bit memory pointers v 16 bit stack pointer (SP) v Program counter (PC) q Program counter (PC) v PC points to the next opcode to be fetched from ROM v when the µP places an address on the address bus to fetch the byte from memory, it then increments the program counter by one to the next location q Special purpose registers v I : Interrupt vector register. v R : memory Refresh register hsabaghianb @ kashanu. ac. ir Microprocessors 1 -17

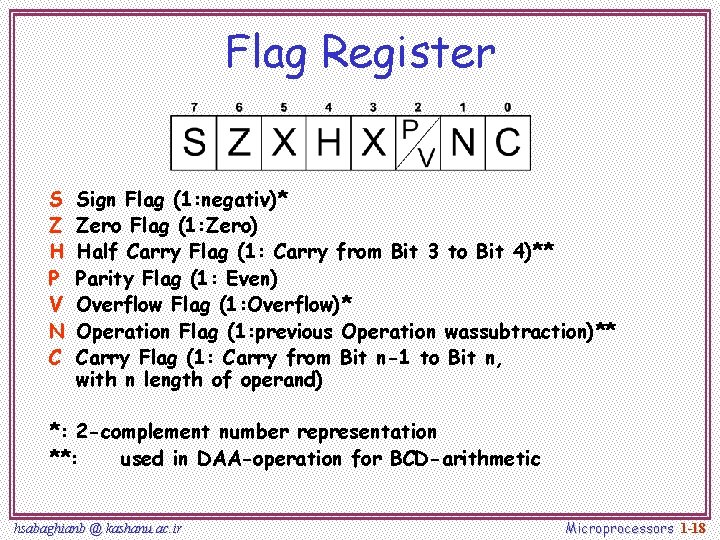

Flag Register S Z H P V N C Sign Flag (1: negativ)* Zero Flag (1: Zero) Half Carry Flag (1: Carry from Bit 3 to Bit 4)** Parity Flag (1: Even) Overflow Flag (1: Overflow)* Operation Flag (1: previous Operation wassubtraction)** Carry Flag (1: Carry from Bit n-1 to Bit n, with n length of operand) *: 2 -complement number representation **: used in DAA-operation for BCD-arithmetic hsabaghianb @ kashanu. ac. ir Microprocessors 1 -18

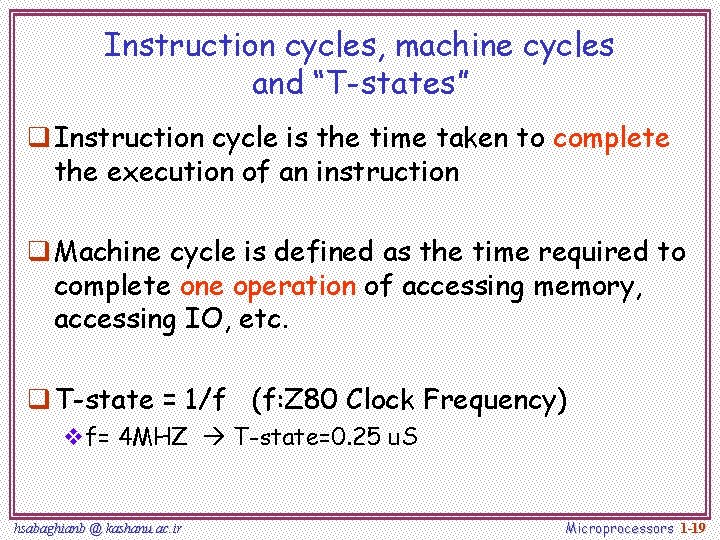

Instruction cycles, machine cycles and “T-states” q Instruction cycle is the time taken to complete the execution of an instruction q Machine cycle is defined as the time required to complete one operation of accessing memory, accessing IO, etc. q T-state = 1/f (f: Z 80 Clock Frequency) vf= 4 MHZ T-state=0. 25 u. S hsabaghianb @ kashanu. ac. ir Microprocessors 1 -19

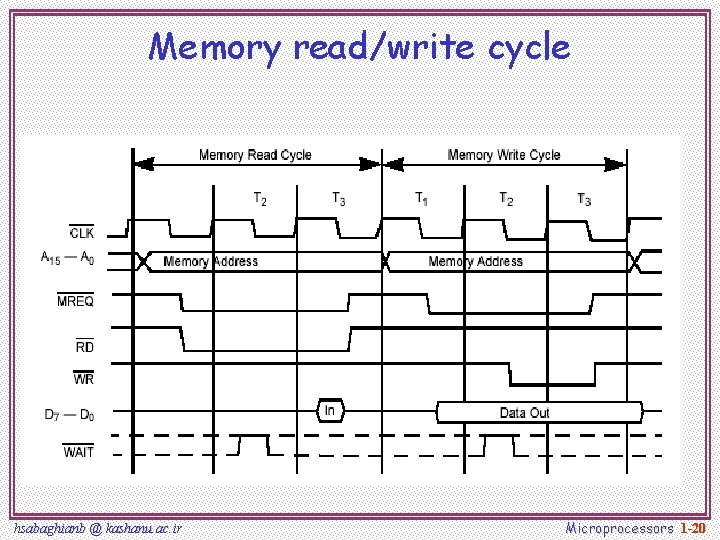

Memory read/write cycle hsabaghianb @ kashanu. ac. ir Microprocessors 1 -20

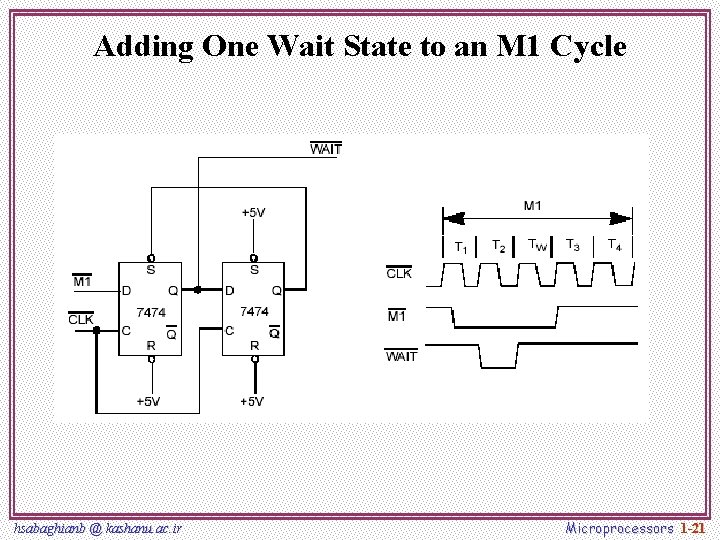

Adding One Wait State to an M 1 Cycle hsabaghianb @ kashanu. ac. ir Microprocessors 1 -21

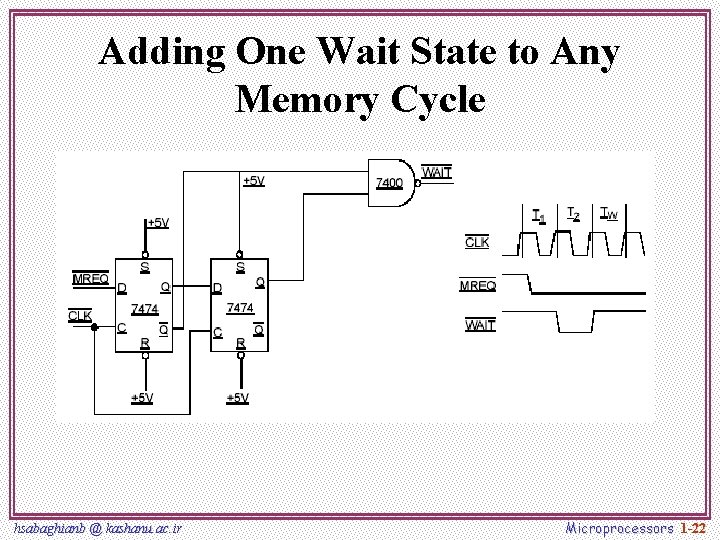

Adding One Wait State to Any Memory Cycle hsabaghianb @ kashanu. ac. ir Microprocessors 1 -22

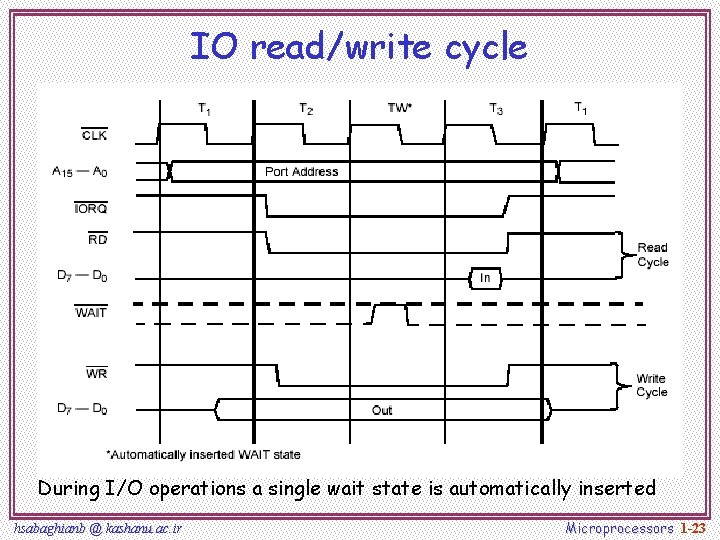

IO read/write cycle During I/O operations a single wait state is automatically inserted hsabaghianb @ kashanu. ac. ir Microprocessors 1 -23

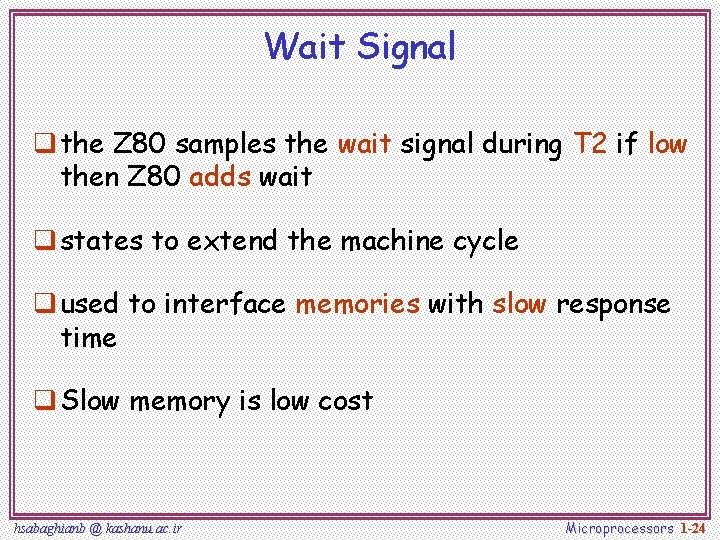

Wait Signal q the Z 80 samples the wait signal during T 2 if low then Z 80 adds wait q states to extend the machine cycle q used to interface memories with slow response time q Slow memory is low cost hsabaghianb @ kashanu. ac. ir Microprocessors 1 -24

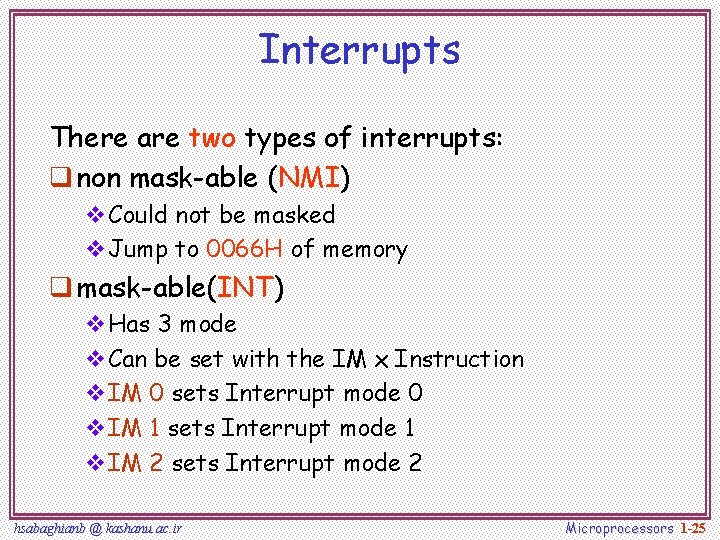

Interrupts There are two types of interrupts: q non mask-able (NMI) v. Could not be masked v. Jump to 0066 H of memory q mask-able(INT) v. Has 3 mode v. Can be set with the IM x Instruction v. IM 0 sets Interrupt mode 0 v. IM 1 sets Interrupt mode 1 v. IM 2 sets Interrupt mode 2 hsabaghianb @ kashanu. ac. ir Microprocessors 1 -25

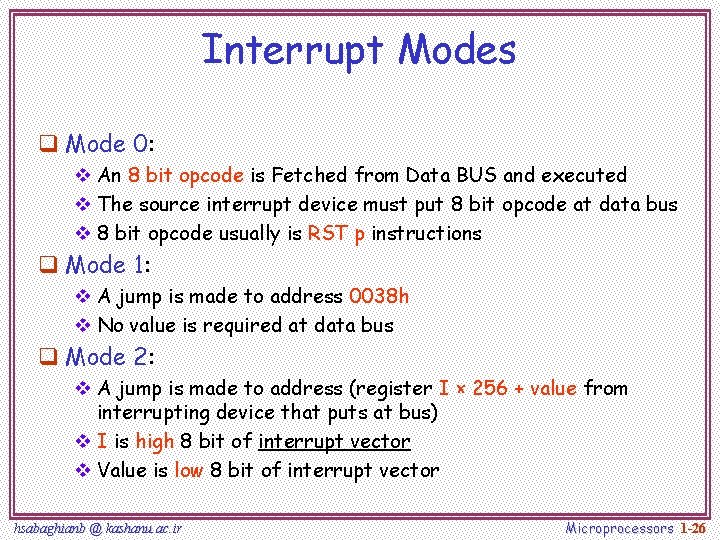

Interrupt Modes q Mode 0: v An 8 bit opcode is Fetched from Data BUS and executed v The source interrupt device must put 8 bit opcode at data bus v 8 bit opcode usually is RST p instructions q Mode 1: v A jump is made to address 0038 h v No value is required at data bus q Mode 2: v A jump is made to address (register I × 256 + value from interrupting device that puts at bus) v I is high 8 bit of interrupt vector v Value is low 8 bit of interrupt vector hsabaghianb @ kashanu. ac. ir Microprocessors 1 -26

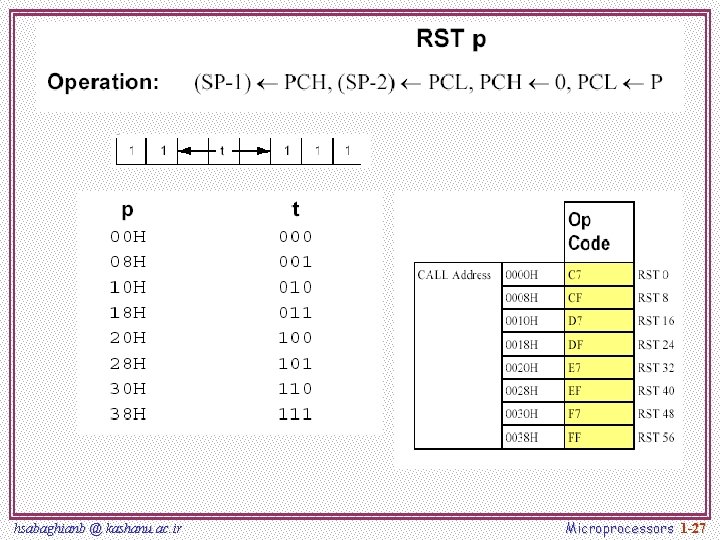

hsabaghianb @ kashanu. ac. ir Microprocessors 1 -27

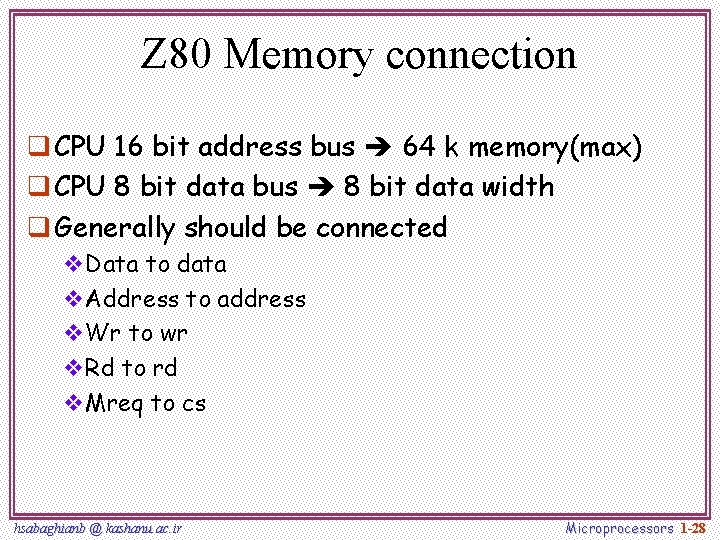

Z 80 Memory connection q CPU 16 bit address bus 64 k memory(max) q CPU 8 bit data bus 8 bit data width q Generally should be connected v. Data to data v. Address to address v. Wr to wr v. Rd to rd v. Mreq to cs hsabaghianb @ kashanu. ac. ir Microprocessors 1 -28

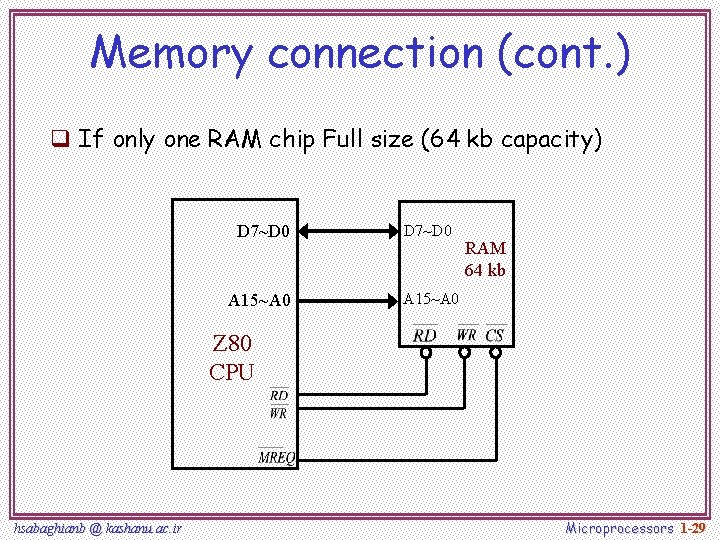

Memory connection (cont. ) q If only one RAM chip Full size (64 kb capacity) D 7~D 0 A 15~A 0 RAM 64 kb Z 80 CPU hsabaghianb @ kashanu. ac. ir Microprocessors 1 -29

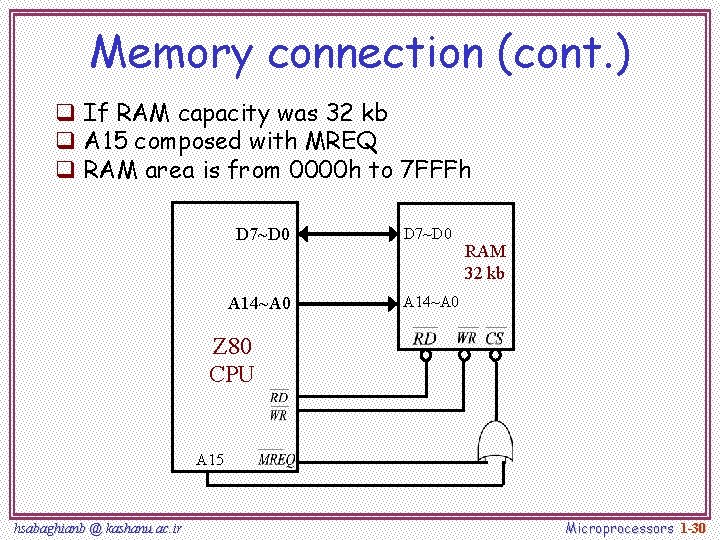

Memory connection (cont. ) q If RAM capacity was 32 kb q A 15 composed with MREQ q RAM area is from 0000 h to 7 FFFh D 7~D 0 A 14~A 0 RAM 32 kb Z 80 CPU A 15 hsabaghianb @ kashanu. ac. ir Microprocessors 1 -30

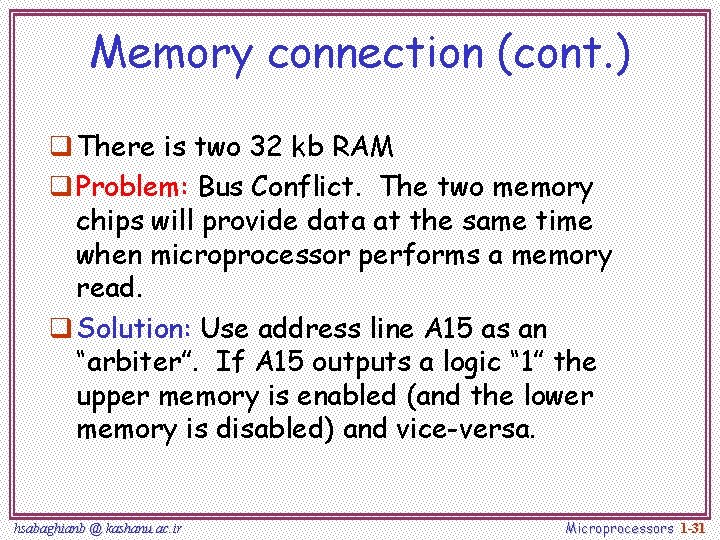

Memory connection (cont. ) q There is two 32 kb RAM q Problem: Bus Conflict. The two memory chips will provide data at the same time when microprocessor performs a memory read. q Solution: Use address line A 15 as an “arbiter”. If A 15 outputs a logic “ 1” the upper memory is enabled (and the lower memory is disabled) and vice-versa. hsabaghianb @ kashanu. ac. ir Microprocessors 1 -31

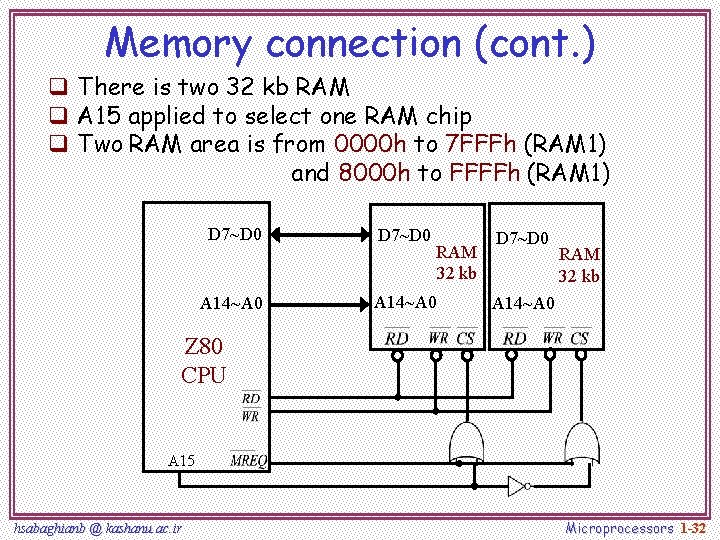

Memory connection (cont. ) q There is two 32 kb RAM q A 15 applied to select one RAM chip q Two RAM area is from 0000 h to 7 FFFh (RAM 1) and 8000 h to FFFFh (RAM 1) D 7~D 0 A 14~A 0 RAM 32 kb D 7~D 0 RAM 32 kb A 14~A 0 Z 80 CPU A 15 hsabaghianb @ kashanu. ac. ir Microprocessors 1 -32

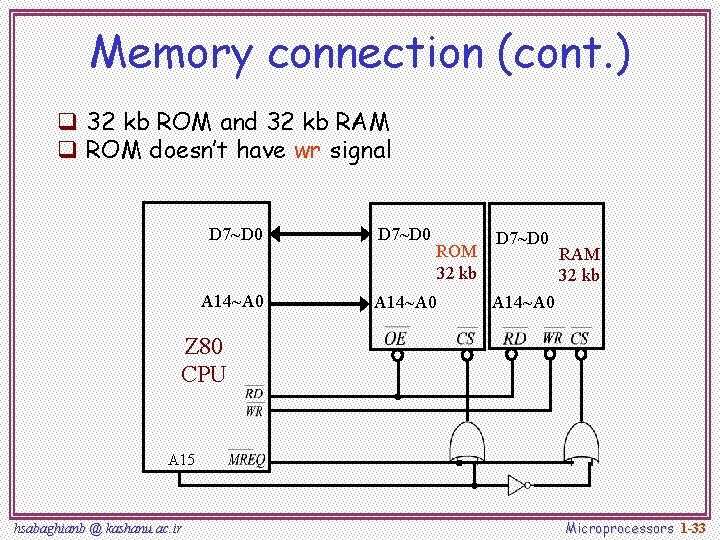

Memory connection (cont. ) q 32 kb ROM and 32 kb RAM q ROM doesn’t have wr signal D 7~D 0 A 14~A 0 ROM 32 kb D 7~D 0 RAM 32 kb A 14~A 0 Z 80 CPU A 15 hsabaghianb @ kashanu. ac. ir Microprocessors 1 -33

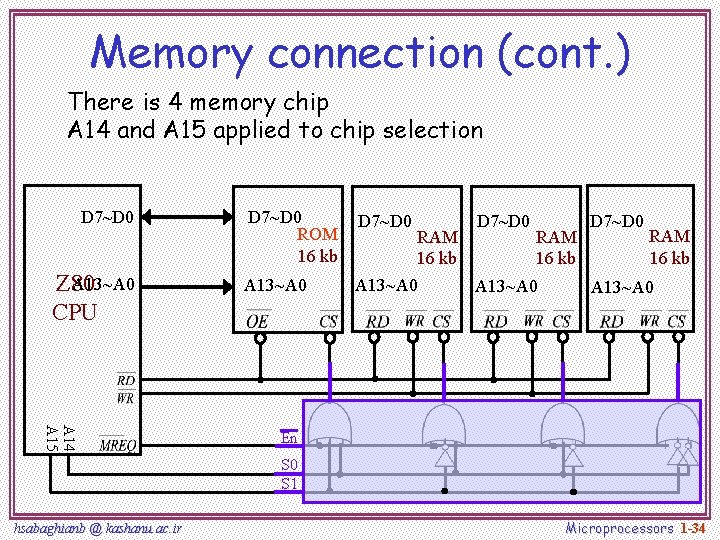

Memory connection (cont. ) There is 4 memory chip A 14 and A 15 applied to chip selection D 7~D 0 A 13~A 0 Z 80 CPU D 7~D 0 ROM 16 kb D 7~D 0 A 13~A 0 RAM 16 kb D 7~D 0 RAM 16 kb A 13~A 0 A 14 A 15 En S 0 S 1 hsabaghianb @ kashanu. ac. ir Microprocessors 1 -34

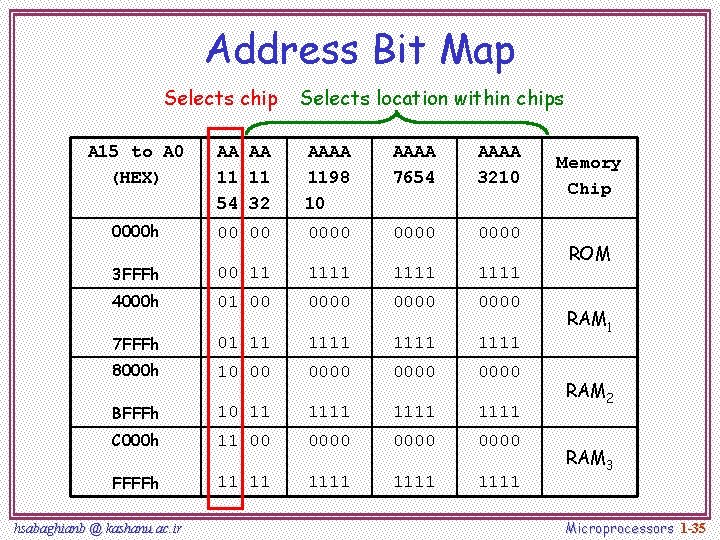

Address Bit Map Selects chip Selects location within chips A 15 to A 0 (HEX) AA AA 11 11 54 32 AAAA 1198 10 AAAA 7654 AAAA 3210 0000 h 00 00 0000 3 FFFh 00 11 1111 4000 h 01 00 0000 7 FFFh 01 11 1111 8000 h 10 00 0000 BFFFh 10 11 1111 C 000 h 11 00 0000 FFFFh 11 11 1111 hsabaghianb @ kashanu. ac. ir Memory Chip ROM RAM 1 RAM 2 RAM 3 Microprocessors 1 -35

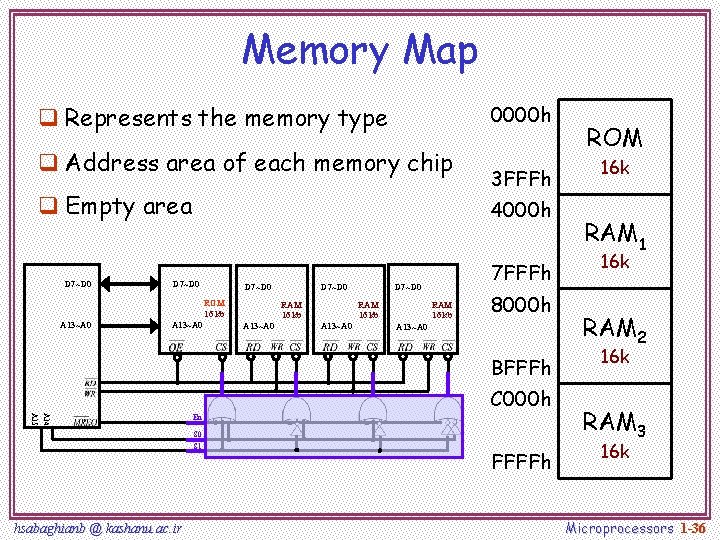

Memory Map q Represents the memory type 0000 h q Address area of each memory chip q Empty area D 7~D 0 4000 h D 7~D 0 ROM 16 kb A 13~A 0 3 FFFh A 13~A 0 D 7~D 0 RAM 16 kb A 13~A 0 7 FFFh 8000 h A 13~A 0 BFFFh C 000 h A 14 A 15 En S 0 S 1 hsabaghianb @ kashanu. ac. ir FFFFh ROM 16 k RAM 1 16 k RAM 2 16 k RAM 3 16 k Microprocessors 1 -36

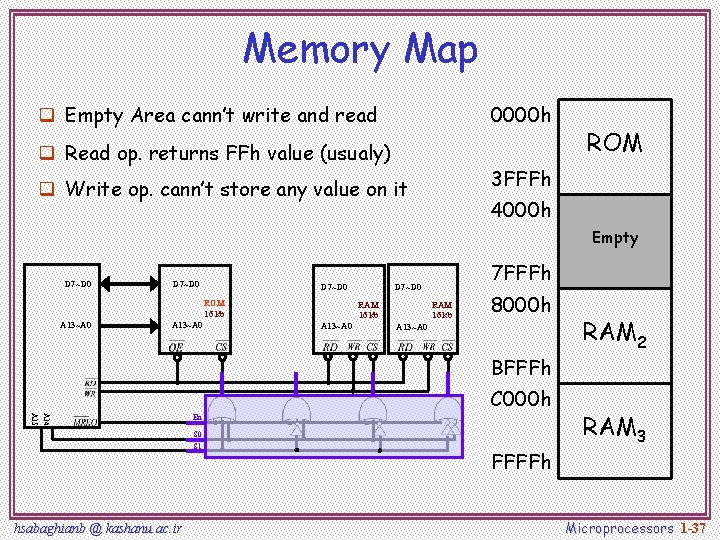

Memory Map 0000 h q Empty Area cann’t write and read q Read op. returns FFh value (usualy) ROM 3 FFFh q Write op. cann’t store any value on it 4000 h Empty D 7~D 0 ROM 16 kb A 13~A 0 RAM 16 kb A 13~A 0 7 FFFh D 7~D 0 8000 h A 13~A 0 RAM 2 BFFFh C 000 h A 14 A 15 En S 0 S 1 hsabaghianb @ kashanu. ac. ir RAM 3 FFFFh Microprocessors 1 -37

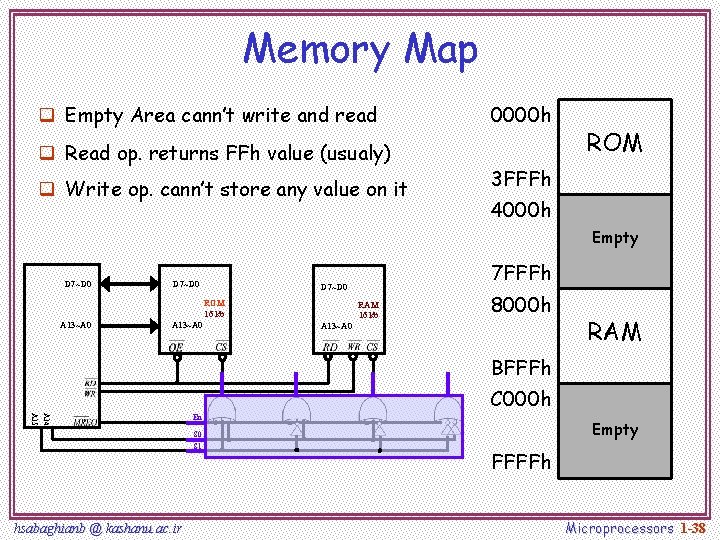

Memory Map q Empty Area cann’t write and read q Read op. returns FFh value (usualy) q Write op. cann’t store any value on it 0000 h ROM 3 FFFh 4000 h Empty D 7~D 0 ROM 16 kb A 13~A 0 7 FFFh D 7~D 0 RAM 16 kb 8000 h A 13~A 0 RAM BFFFh C 000 h A 14 A 15 En S 0 S 1 hsabaghianb @ kashanu. ac. ir Empty FFFFh Microprocessors 1 -38

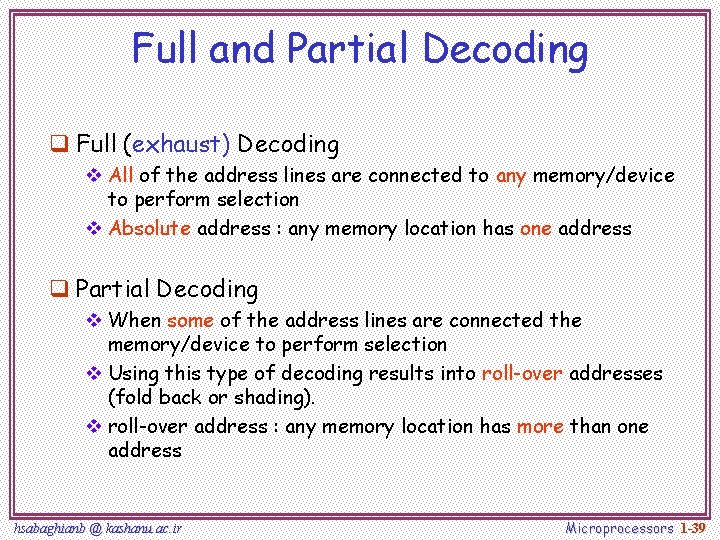

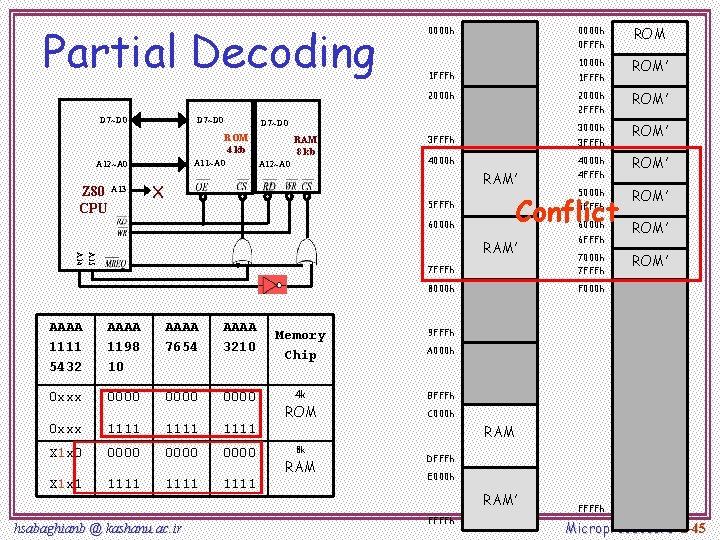

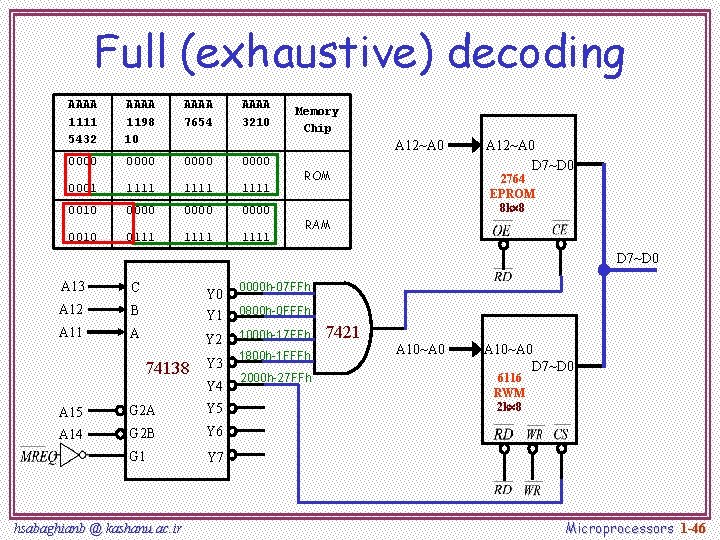

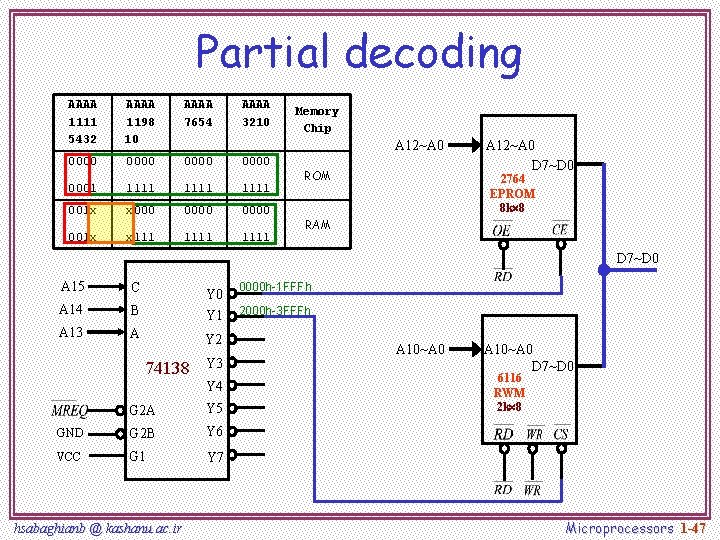

Full and Partial Decoding q Full (exhaust) Decoding v All of the address lines are connected to any memory/device to perform selection v Absolute address : any memory location has one address q Partial Decoding v When some of the address lines are connected the memory/device to perform selection v Using this type of decoding results into roll-over addresses (fold back or shading). v roll-over address : any memory location has more than one address hsabaghianb @ kashanu. ac. ir Microprocessors 1 -39

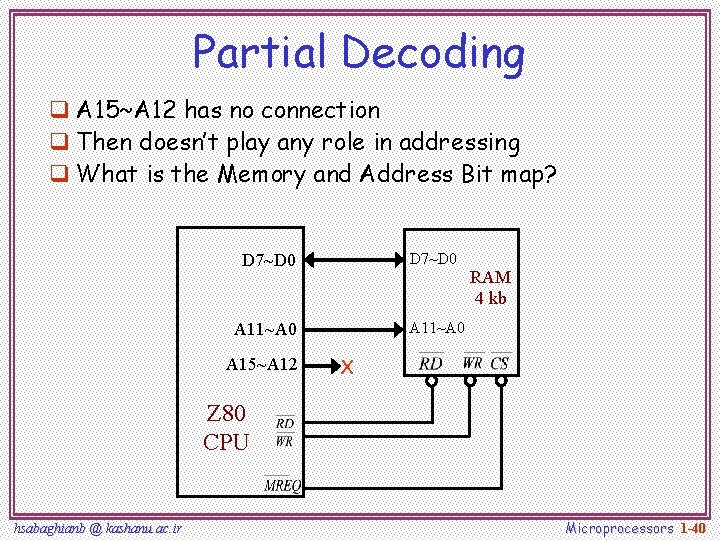

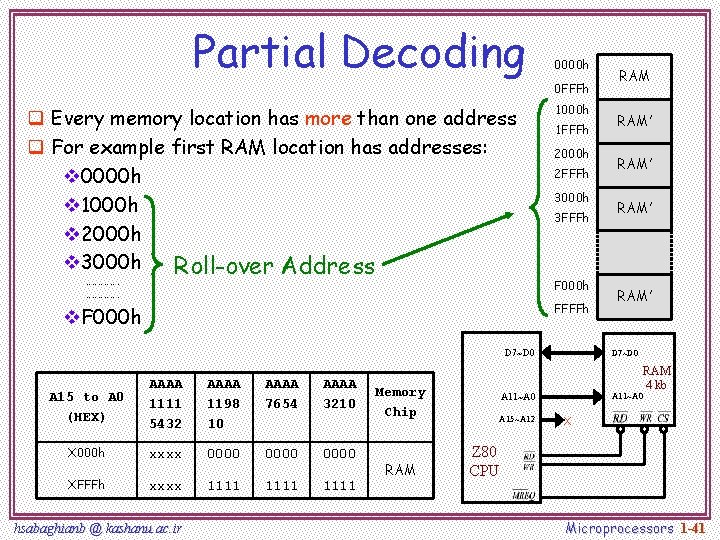

Partial Decoding q A 15~A 12 has no connection q Then doesn’t play any role in addressing q What is the Memory and Address Bit map? D 7~D 0 A 11~A 0 A 15~A 12 RAM 4 kb X Z 80 CPU hsabaghianb @ kashanu. ac. ir Microprocessors 1 -40

Partial Decoding q Every memory location has more than one address q For example first RAM location has addresses: v 0000 h v 1000 h v 2000 h v 3000 h Roll-over Address ……………. 0000 h 0 FFFh 1000 h 1 FFFh 2000 h 2 FFFh 3000 h 3 FFFh F 000 h FFFFh v. F 000 h D 7~D 0 A 15 to A 0 (HEX) AAAA 1111 5432 AAAA 1198 10 AAAA 7654 X 000 h xxxx 0000 XFFFh xxxx 1111 hsabaghianb @ kashanu. ac. ir AAAA 3210 Memory Chip RAM’ RAM’ D 7~D 0 A 11~A 0 A 15~A 12 RAM 4 kb X Z 80 CPU Microprocessors 1 -41

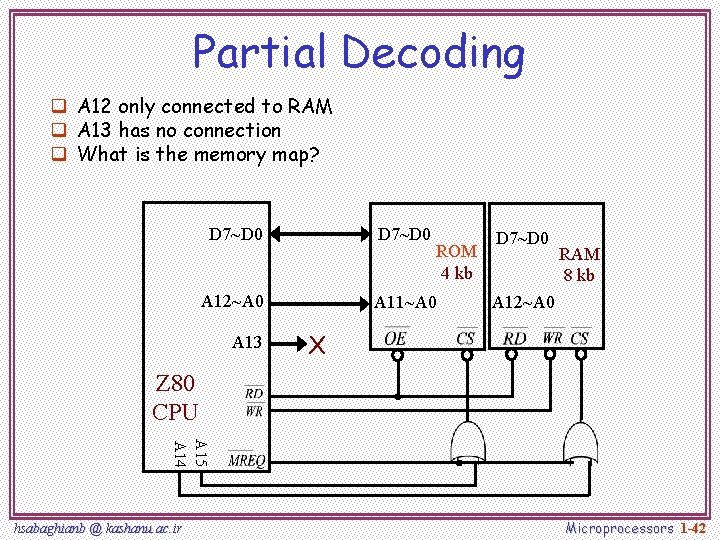

Partial Decoding q A 12 only connected to RAM q A 13 has no connection q What is the memory map? D 7~D 0 A 12~A 0 A 11~A 0 A 13 ROM 4 kb D 7~D 0 RAM 8 kb A 12~A 0 X Z 80 CPU A 15 A 14 hsabaghianb @ kashanu. ac. ir Microprocessors 1 -42

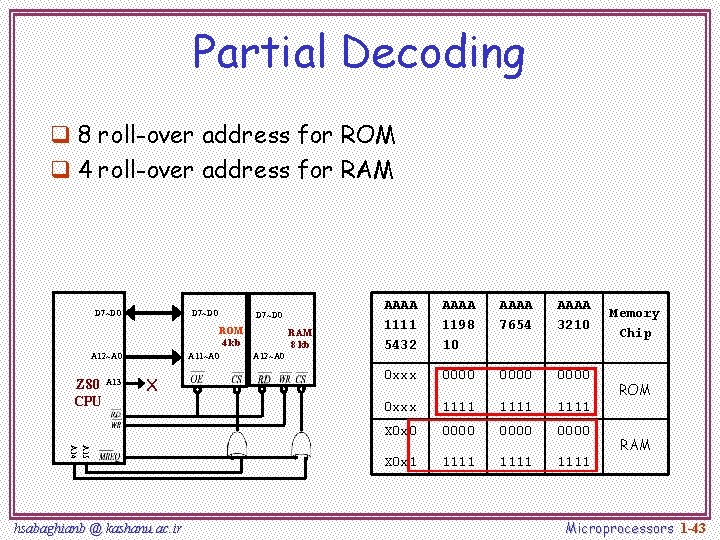

Partial Decoding q 8 roll-over address for ROM q 4 roll-over address for RAM D 7~D 0 ROM 4 kb A 11~A 0 A 12~A 0 Z 80 A 13 CPU X A 15 A 14 hsabaghianb @ kashanu. ac. ir RAM 8 kb A 12~A 0 AAAA 1111 5432 AAAA 1198 10 AAAA 7654 AAAA 3210 0 xxx 0000 0 xxx 1111 X 0 x 0 0000 X 0 x 1 1111 Memory Chip ROM RAM Microprocessors 1 -43

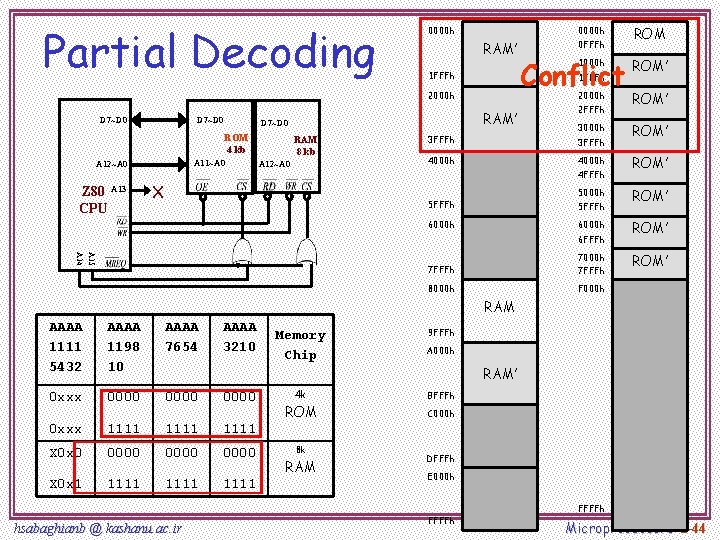

Partial Decoding 0000 h RAM’ 1 FFFh D 7~D 0 ROM 4 kb A 11~A 0 A 12~A 0 Z 80 A 13 CPU 2000 h RAM’ D 7~D 0 RAM 8 kb A 12~A 0 Conflict 1000 h 1 FFFh 2000 h D 7~D 0 0 FFFh 3 FFFh 2 FFFh 3000 h 3 FFFh 4000 h 4 FFFh X 5000 h 5 FFFh 6000 h 6 FFFh A 15 A 14 7 FFFh 7000 h 7 FFFh 8000 h F 000 h ROM’ ROM’ RAM AAAA 1111 5432 AAAA 1198 10 AAAA 7654 0 xxx 0000 AAAA 3210 Memory Chip 9 FFFh A 000 h RAM’ 0000 0 xxx 1111 X 0 x 0 0000 X 0 x 1 1111 hsabaghianb @ kashanu. ac. ir 4 k BFFFh ROM C 000 h 8 k RAM DFFFh E 000 h FFFFh Microprocessors 1 -44

Partial Decoding 0000 h 0 FFFh 1000 h 1 FFFh 2000 h D 7~D 0 2 FFFh D 7~D 0 ROM 4 kb A 11~A 0 A 12~A 0 Z 80 A 13 CPU 2000 h RAM 8 kb A 12~A 0 3000 h 3 FFFh 4000 h RAM’ X 5 FFFh 6000 h A 15 A 14 AAAA 1198 10 AAAA 7654 AAAA 3210 0 xxx 0000 0 xxx 1111 X 1 x 0 0000 X 1 x 1 1111 hsabaghianb @ kashanu. ac. ir Memory Chip 5000 h Conflict 5 FFFh 6000 h RAM’ AAAA 1111 5432 4 FFFh 6 FFFh 7000 h 7 FFFh 8000 h F 000 h ROM’ ROM’ 9 FFFh A 000 h 4 k BFFFh ROM C 000 h RAM 8 k RAM DFFFh E 000 h RAM’ FFFFh Microprocessors 1 -45

Full (exhaustive) decoding AAAA 1111 5432 AAAA 1198 10 AAAA 7654 AAAA 3210 0000 0001 1111 0010 0000 0010 0111 1111 Memory Chip A 12~A 0 ROM A 12~A 0 D 7~D 0 2764 EPROM 8 k 8 RAM D 7~D 0 A 13 C Y 0 0000 h-07 FFh A 12 B Y 1 0800 h-0 FFFh A 11 A Y 2 1000 h-17 FFh 74138 Y 3 Y 4 A 15 G 2 A Y 5 A 14 G 2 B Y 6 G 1 Y 7 hsabaghianb @ kashanu. ac. ir 1800 h-1 FFFh 2000 h-27 FFh 7421 A 10~A 0 D 7~D 0 6116 RWM 2 k 8 Microprocessors 1 -46

Partial decoding AAAA 1111 5432 AAAA 1198 10 AAAA 7654 AAAA 3210 0000 0001 1111 001 x x 0000 001 x x 1111 Memory Chip A 12~A 0 ROM A 12~A 0 D 7~D 0 2764 EPROM 8 k 8 RAM D 7~D 0 A 15 C Y 0 0000 h-1 FFFh A 14 B Y 1 2000 h-3 FFFh A 13 A Y 2 74138 Y 3 Y 4 G 2 A Y 5 GND G 2 B Y 6 VCC G 1 Y 7 hsabaghianb @ kashanu. ac. ir A 10~A 0 D 7~D 0 6116 RWM 2 k 8 Microprocessors 1 -47

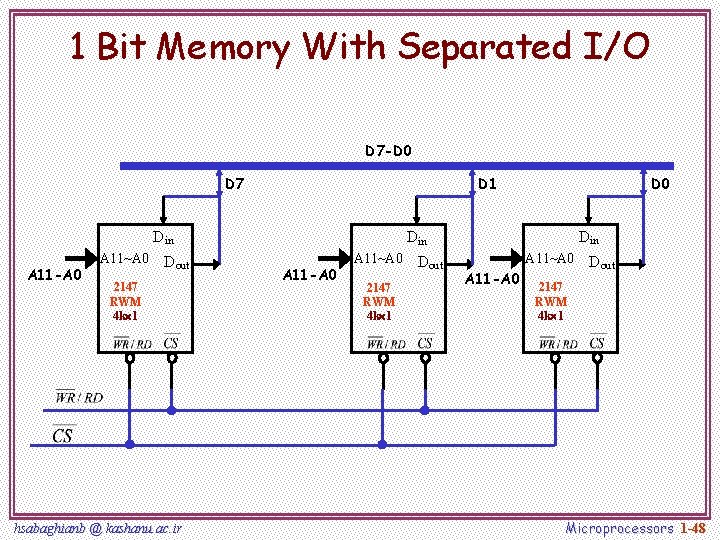

1 Bit Memory With Separated I/O D 7 -D 0 D 7 D 1 Din A 11 -A 0 A 11~A 0 Dout 2147 RWM 4 k 1 hsabaghianb @ kashanu. ac. ir D 0 Din A 11 -A 0 A 11~A 0 2147 RWM 4 k 1 Dout A 11~A 0 A 11 -A 0 Dout 2147 RWM 4 k 1 Microprocessors 1 -48

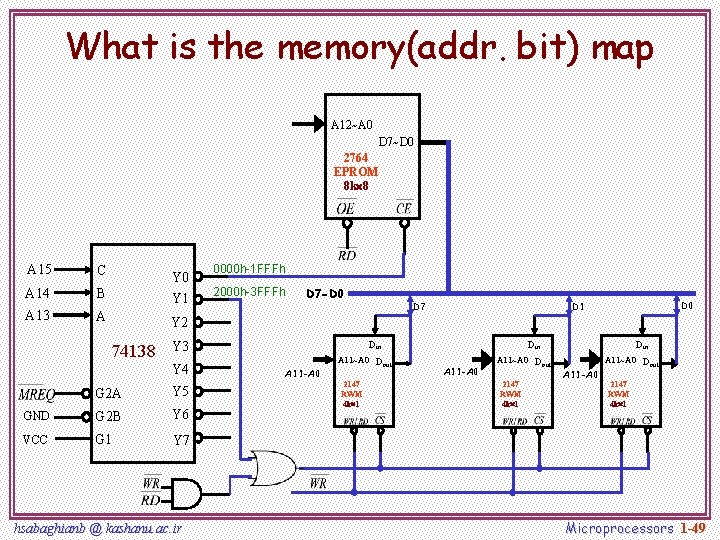

What is the memory(addr. bit) map A 12~A 0 D 7~D 0 2764 EPROM 8 k 8 A 15 C Y 0 A 14 B Y 1 A 13 A Y 2 74138 0000 h-1 FFFh 2000 h-3 FFFh D 7 -D 0 G 2 A Y 5 GND G 2 B Y 6 VCC G 1 Y 7 hsabaghianb @ kashanu. ac. ir A 11 -A 0 A 11~A 0 Dout 2147 RWM 4 k 1 D 0 D 1 Din Y 3 Y 4 D 7 Din A 11 -A 0 A 11~A 0 Dout 2147 RWM 4 k 1 Microprocessors 1 -49

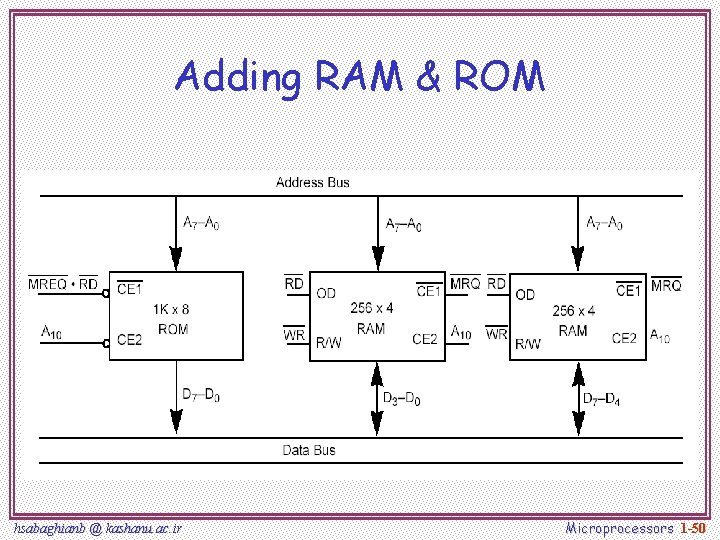

Adding RAM & ROM hsabaghianb @ kashanu. ac. ir Microprocessors 1 -50

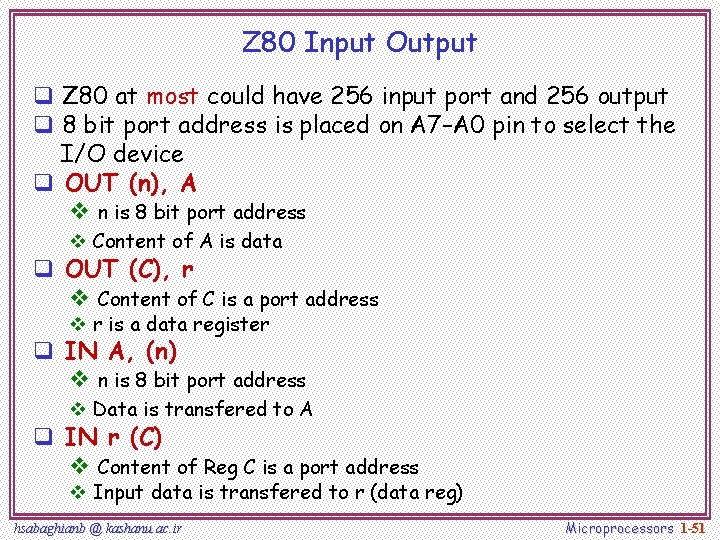

Z 80 Input Output q Z 80 at most could have 256 input port and 256 output q 8 bit port address is placed on A 7–A 0 pin to select the I/O device q OUT (n), A v n is 8 bit port address v Content of A is data q OUT (C), r v Content of C is a port address v r is a data register q IN A, (n) v n is 8 bit port address v Data is transfered to A q IN r (C) v Content of Reg C is a port address v Input data is transfered to r (data reg) hsabaghianb @ kashanu. ac. ir Microprocessors 1 -51

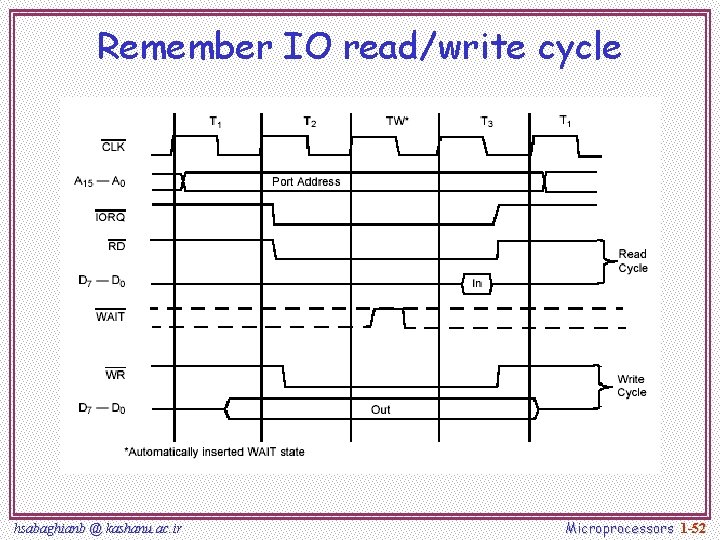

Remember IO read/write cycle hsabaghianb @ kashanu. ac. ir Microprocessors 1 -52

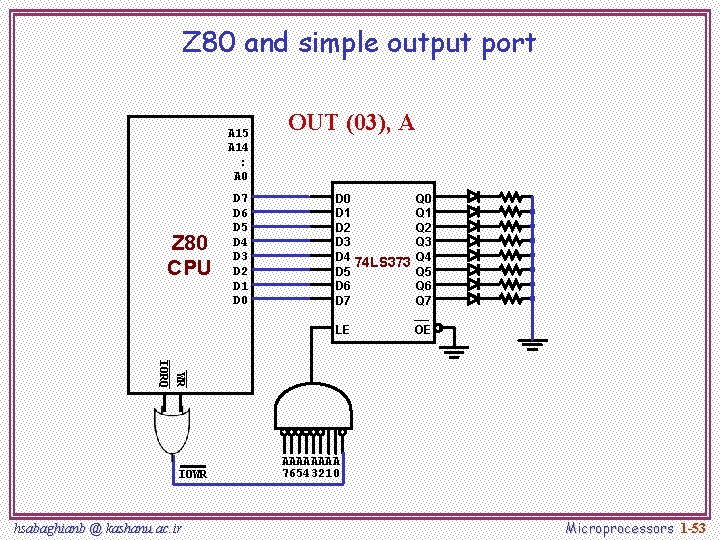

Z 80 and simple output port A 15 A 14 : A 0 Z 80 CPU D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 OUT (03), A D 0 Q 0 D 1 Q 1 D 2 Q 2 D 3 Q 3 D 4 74 LS 373 Q 4 D 5 Q 5 D 6 Q 6 D 7 Q 7 LE OE WR IORQ IOWR hsabaghianb @ kashanu. ac. ir AAAA 7654 3210 Microprocessors 1 -53

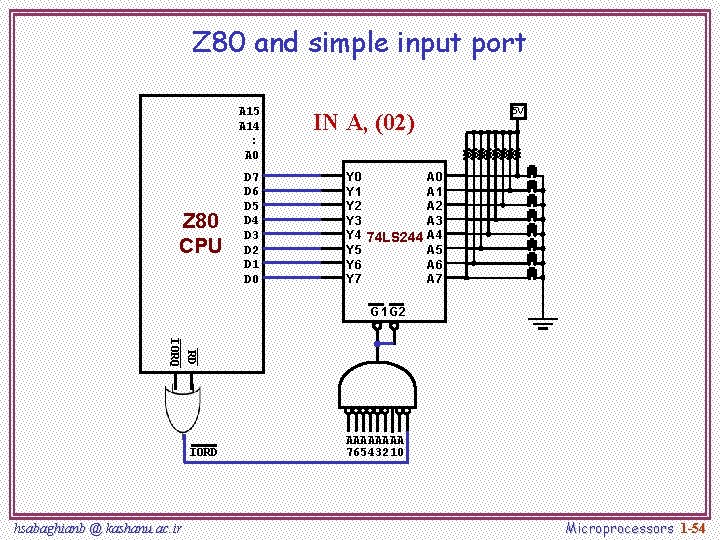

Z 80 and simple input port A 15 A 14 : A 0 Z 80 CPU D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 IN A, (02) 5 V Y 0 A 0 Y 1 A 1 Y 2 A 2 Y 3 A 3 Y 4 74 LS 244 A 4 Y 5 A 5 Y 6 A 6 Y 7 A 7 G 1 G 2 RD IORQ IORD hsabaghianb @ kashanu. ac. ir AAAA 7654 3210 Microprocessors 1 -54

- Slides: 54