Xilinx Logi Core Animation and Connect 6 game

- Slides: 13

Xilinx Logi. Core Animation and Connect 6 game development on Remote FPGA Student - Stephen Conway Supervisor - Fearghal Morgan Co-Supervisor – Martin Glavin

Overview Logi. Core Background & Generation Goals (Phase 1 & Phase 2) Phase 1: Animate Xilinx Logi. Core Modules Phase 2: Implement Connect 6 game on Remote FPGA lab Tasks Completed (Phase 1) Future Work (Phase 2) Summary

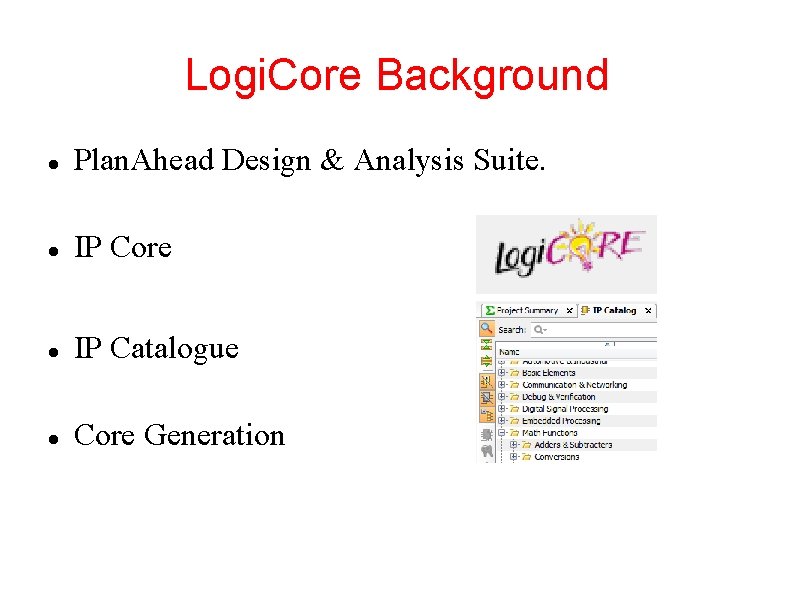

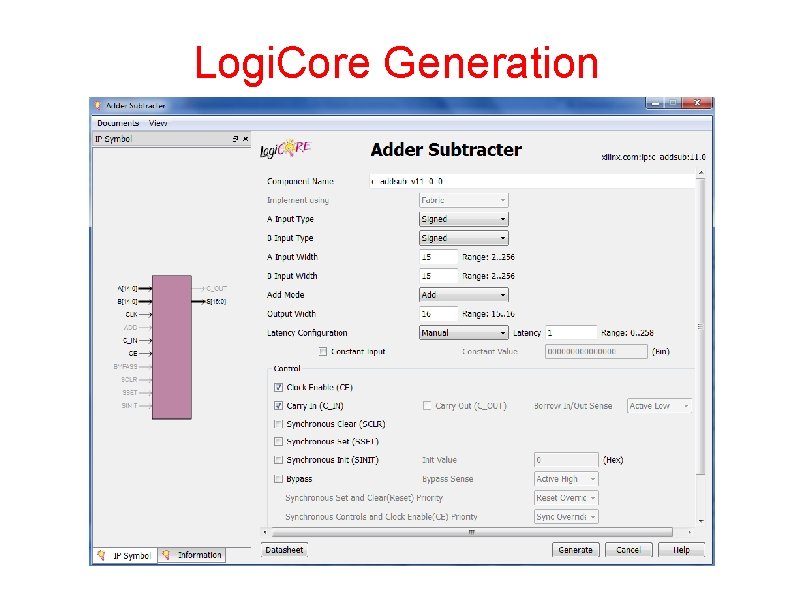

Logi. Core Background Plan. Ahead Design & Analysis Suite. IP Core IP Catalogue Core Generation

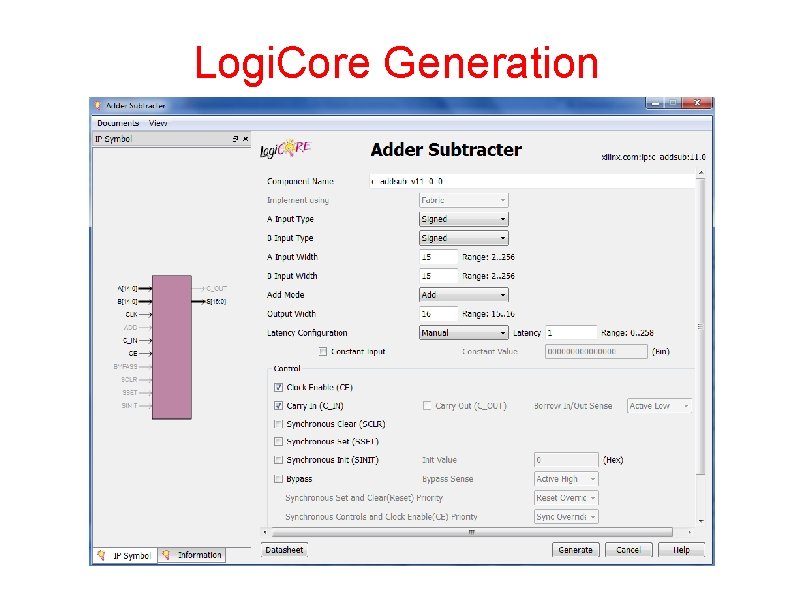

Logi. Core Generation

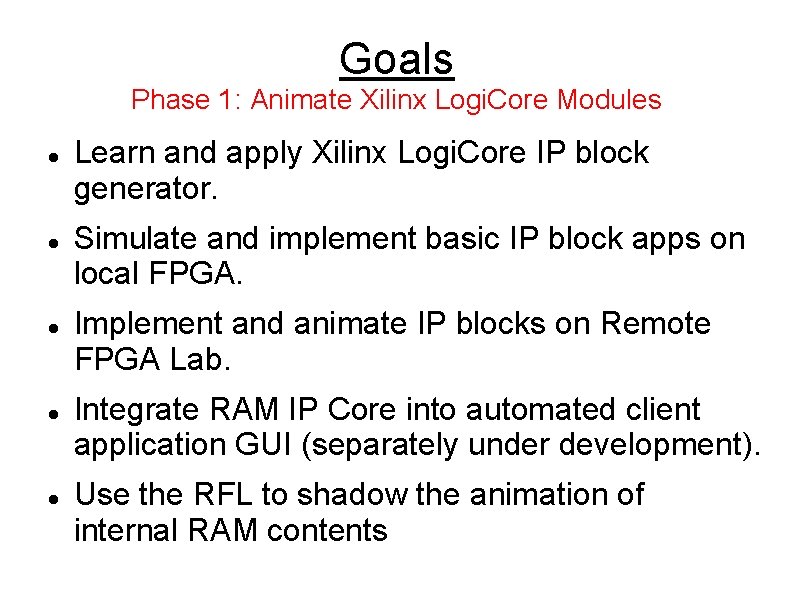

Goals Phase 1: Animate Xilinx Logi. Core Modules Learn and apply Xilinx Logi. Core IP block generator. Simulate and implement basic IP block apps on local FPGA. Implement and animate IP blocks on Remote FPGA Lab. Integrate RAM IP Core into automated client application GUI (separately under development). Use the RFL to shadow the animation of internal RAM contents

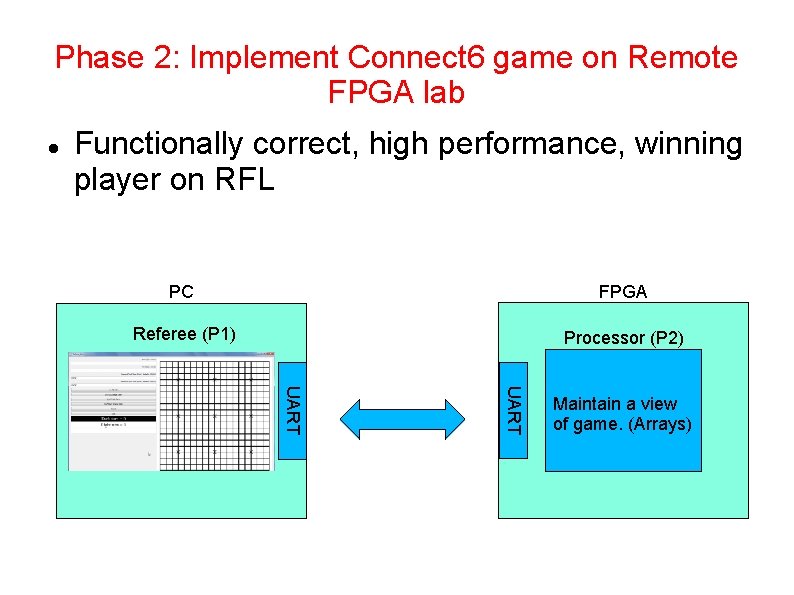

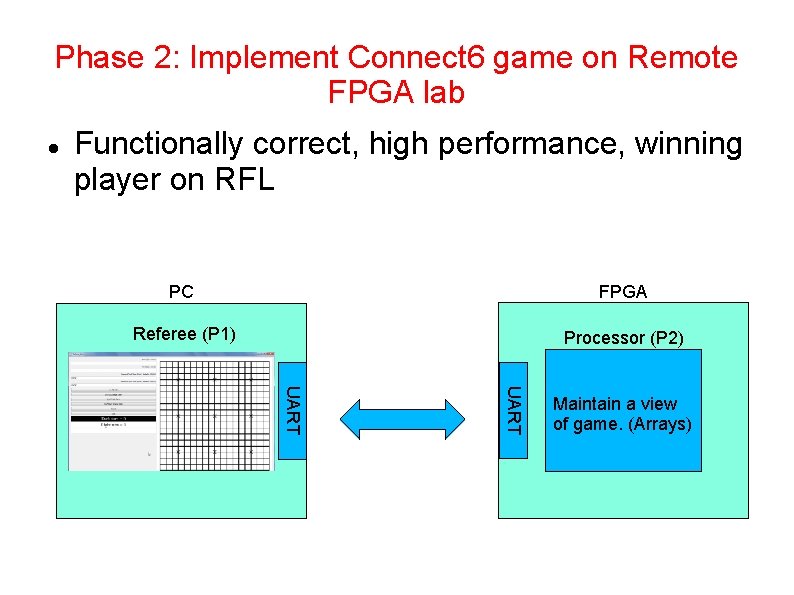

Phase 2: Implement Connect 6 game on Remote FPGA lab Functionally correct, high performance, winning player on RFL PC FPGA Referee (P 1) Processor (P 2) UART Maintain a view of game. (Arrays)

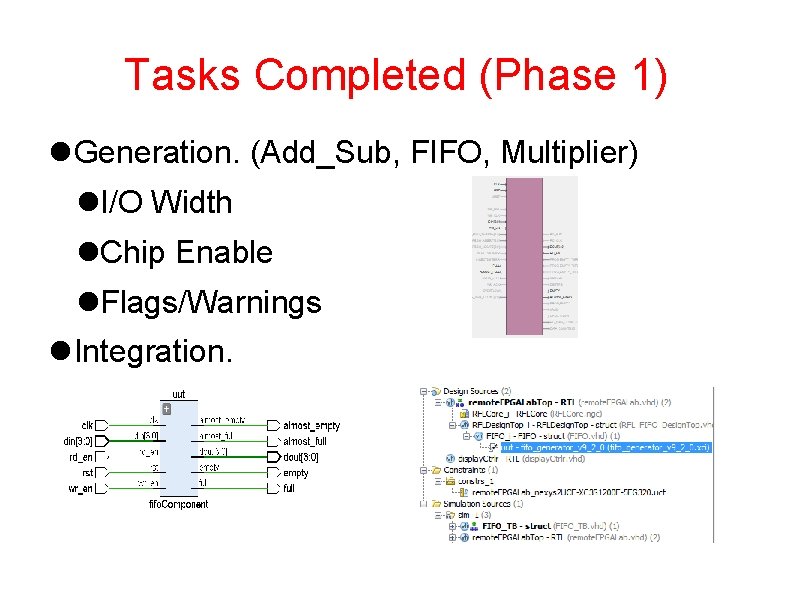

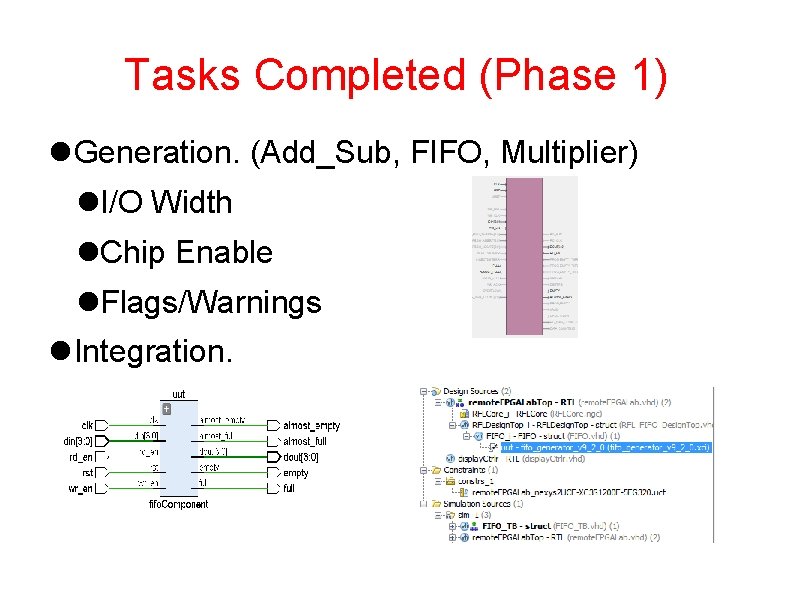

Tasks Completed (Phase 1) Generation. (Add_Sub, FIFO, Multiplier) I/O Width Chip Enable Flags/Warnings Integration.

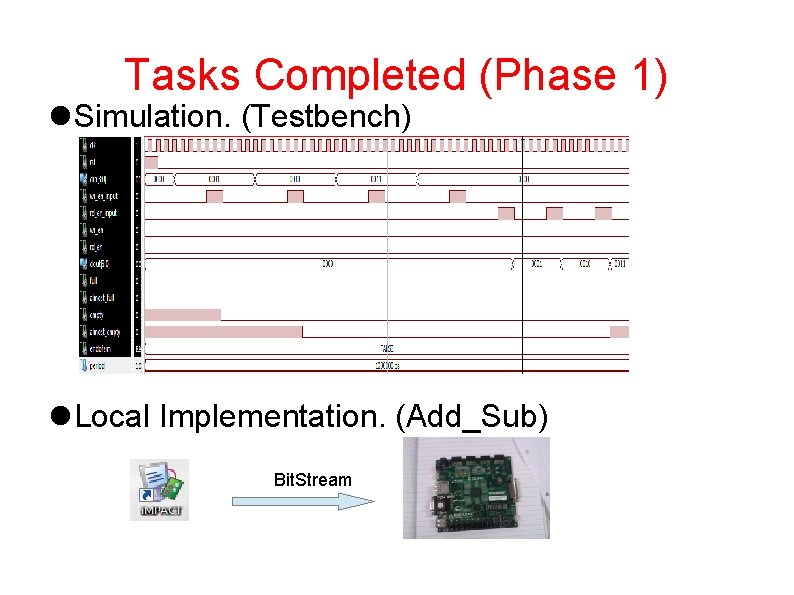

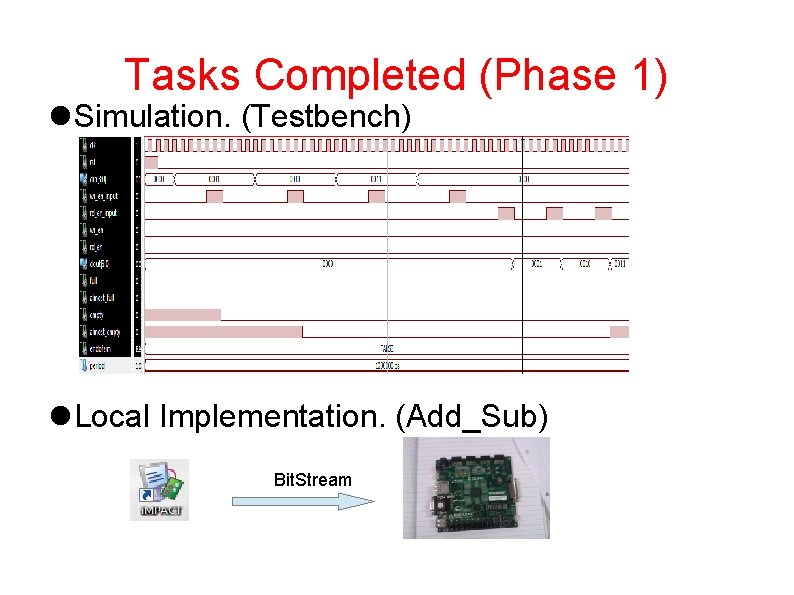

Tasks Completed (Phase 1) Simulation. (Testbench) Local Implementation. (Add_Sub) Bit. Stream

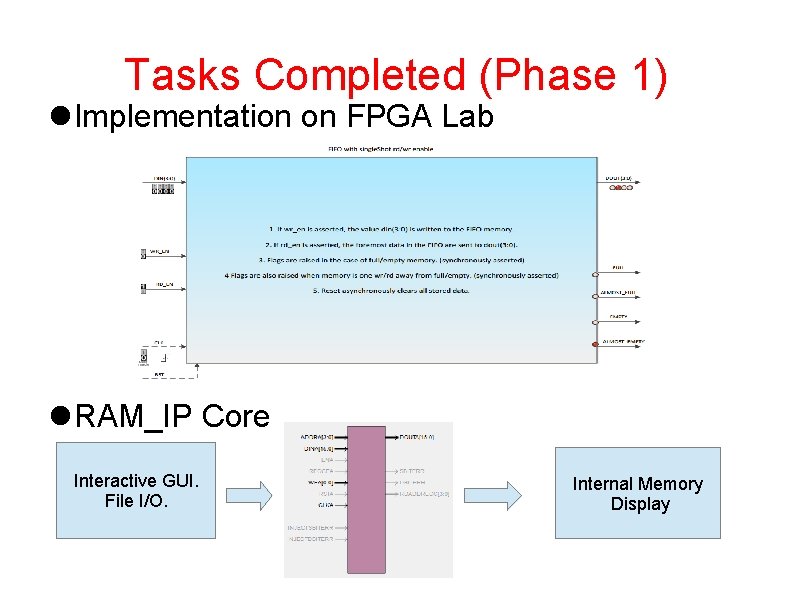

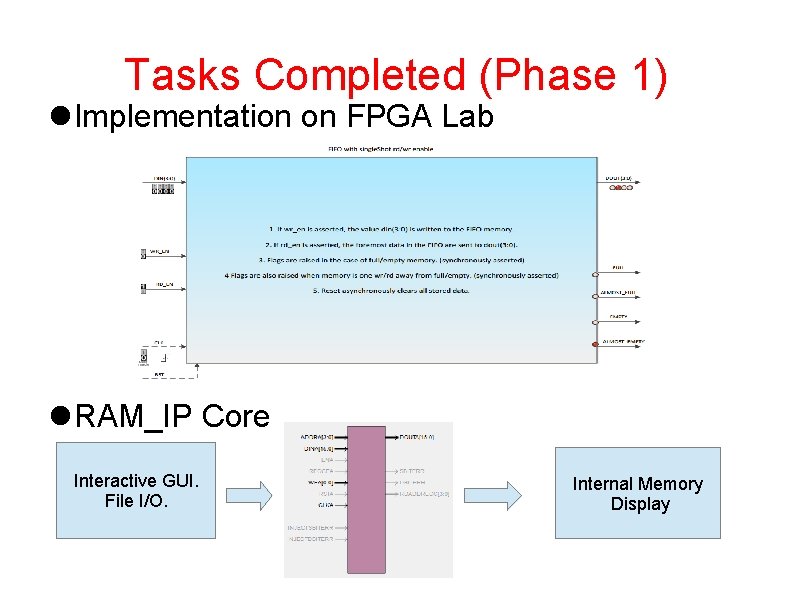

Tasks Completed (Phase 1) Implementation on FPGA Lab RAM_IP Core Interactive GUI. File I/O. Internal Memory Display

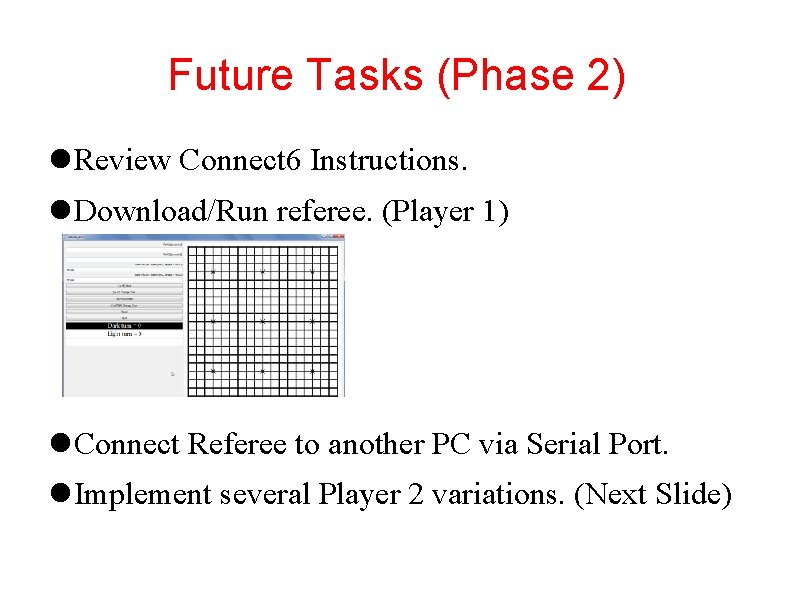

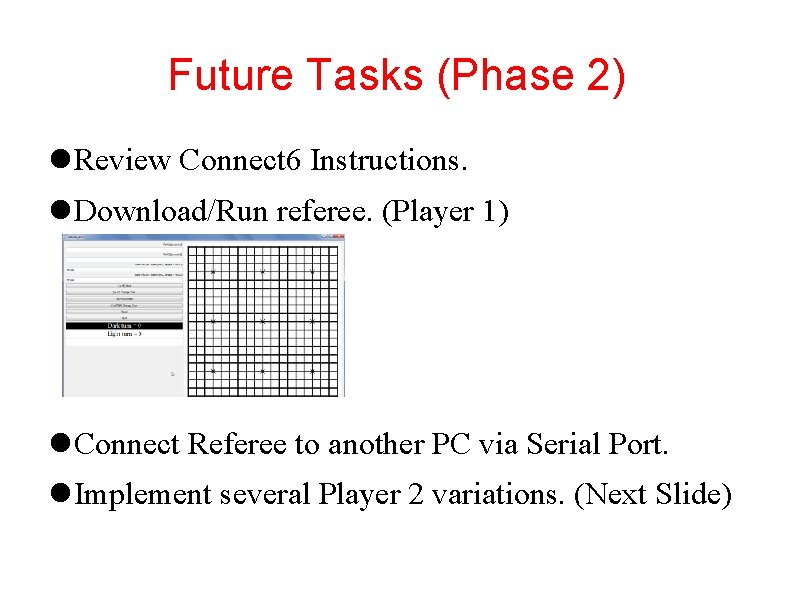

Future Tasks (Phase 2) Review Connect 6 Instructions. Download/Run referee. (Player 1) Connect Referee to another PC via Serial Port. Implement several Player 2 variations. (Next Slide)

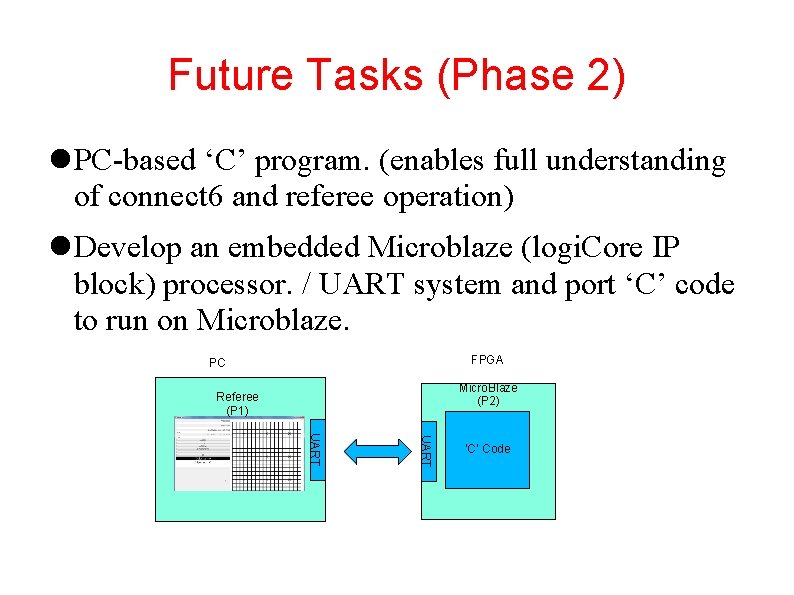

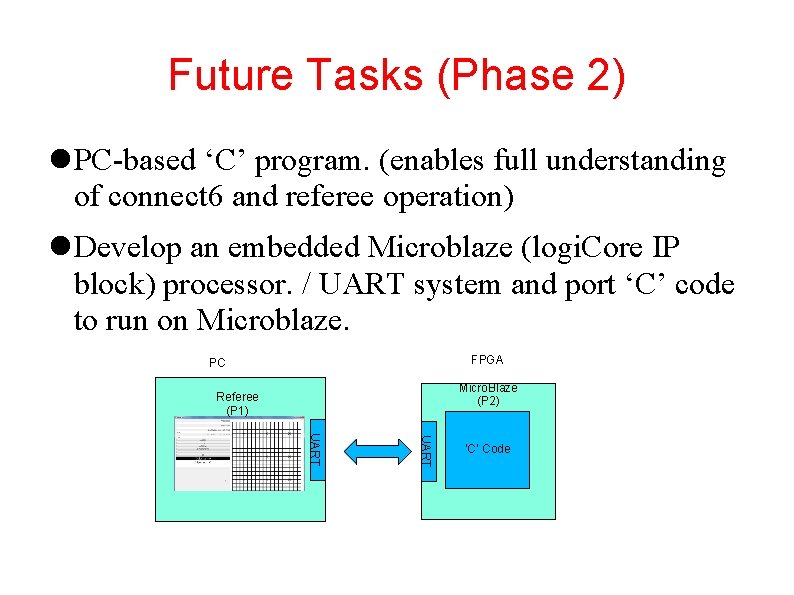

Future Tasks (Phase 2) PC-based ‘C’ program. (enables full understanding of connect 6 and referee operation) Develop an embedded Microblaze (logi. Core IP block) processor. / UART system and port ‘C’ code to run on Microblaze. FPGA PC Micro. Blaze (P 2) Referee (P 1) UART ‘C’ Code

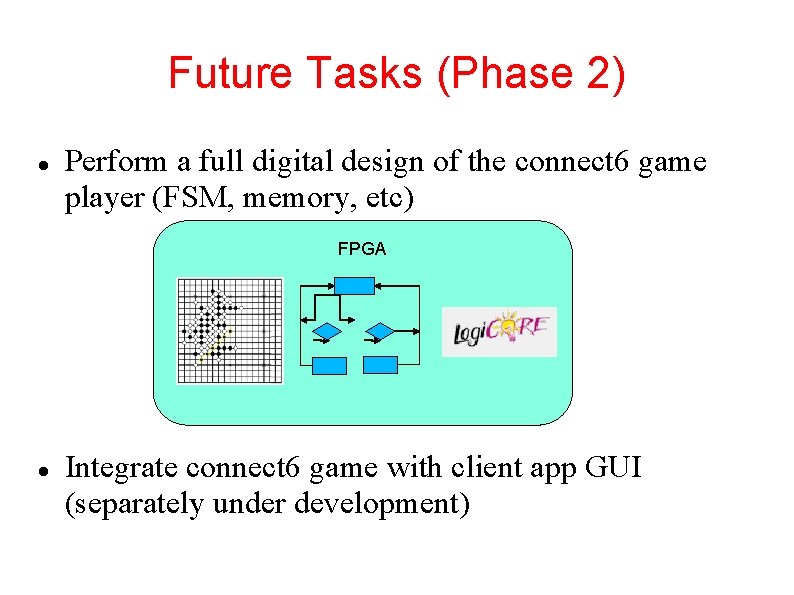

Future Tasks (Phase 2) Perform a full digital design of the connect 6 game player (FSM, memory, etc) FPGA Integrate connect 6 game with client app GUI (separately under development)

Summary Logi. Core Background & Generation Goals (Phase 1 & Phase 2) Phase 1: Animate Xilinx Logi. Core Modules Phase 2: Implement Connect 6 game on Remote FPGA lab Tasks Completed (Phase 1) Future Work (Phase 2) Questions?