Unidade Central de Processamento Sistemas Digitais CInUFPE Como

![Instruções Ty, Tx, Tz Tula CLRLD = [ 0, 1, 0, x] ADD = Instruções Ty, Tx, Tz Tula CLRLD = [ 0, 1, 0, x] ADD =](https://slidetodoc.com/presentation_image_h2/96458355035b1209fc18d18c2cd8931d/image-7.jpg)

- Slides: 23

Unidade Central de Processamento Sistemas Digitais CIn-UFPE

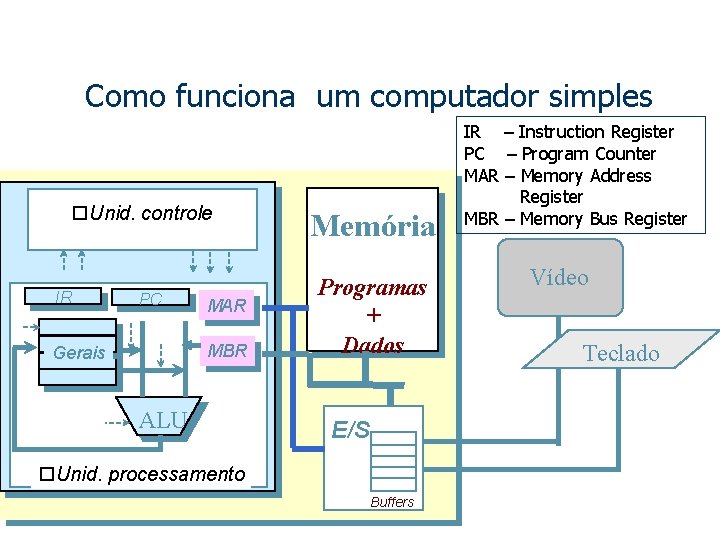

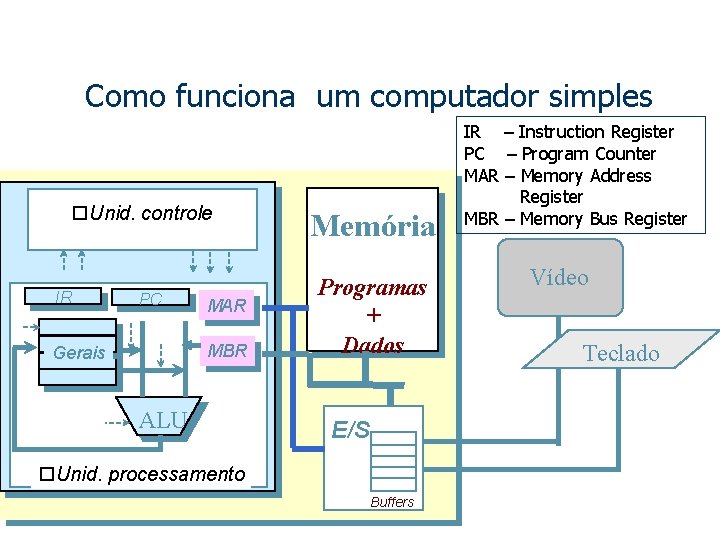

Como funciona um computador simples o. Unid. controle IR PC MAR MBR Gerais ALU Memória Programas + Dados E/S o. Unid. processamento Buffers IR – Instruction Register PC – Program Counter MAR – Memory Address Register MBR – Memory Bus Register Vídeo Teclado

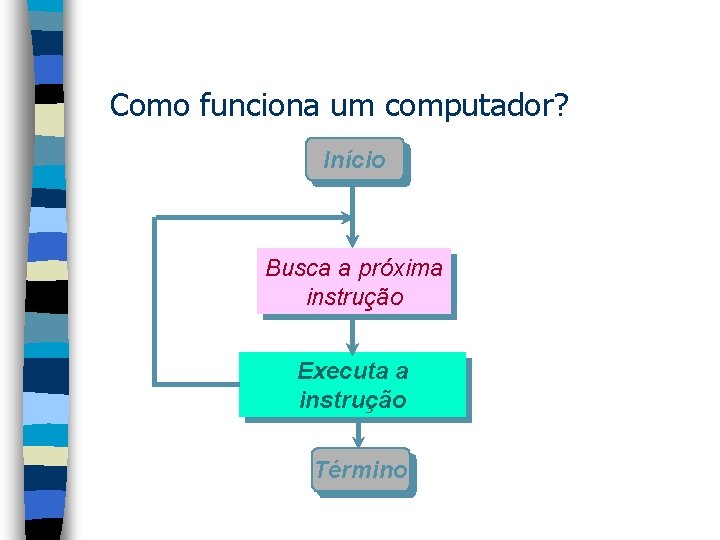

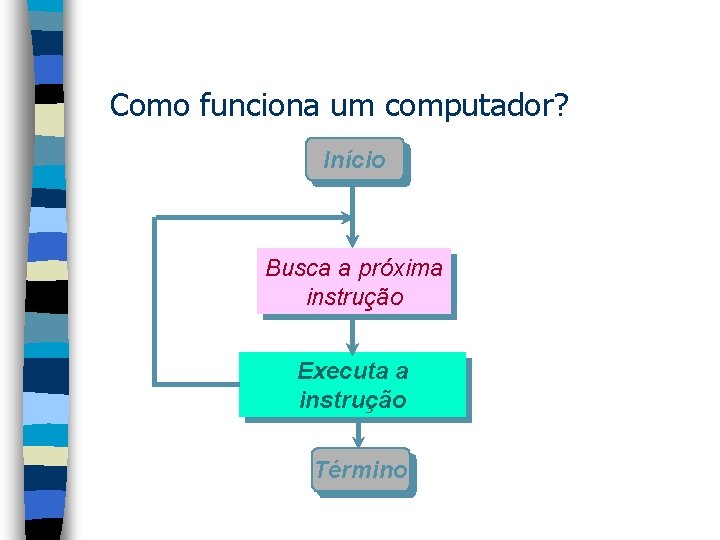

Como funciona um computador? Início Busca a próxima instrução Executa a instrução Término

Executando um programa Busca instrução Decodifica instrução Incrementa PC Busca operando Executa instrução Armazena resultado

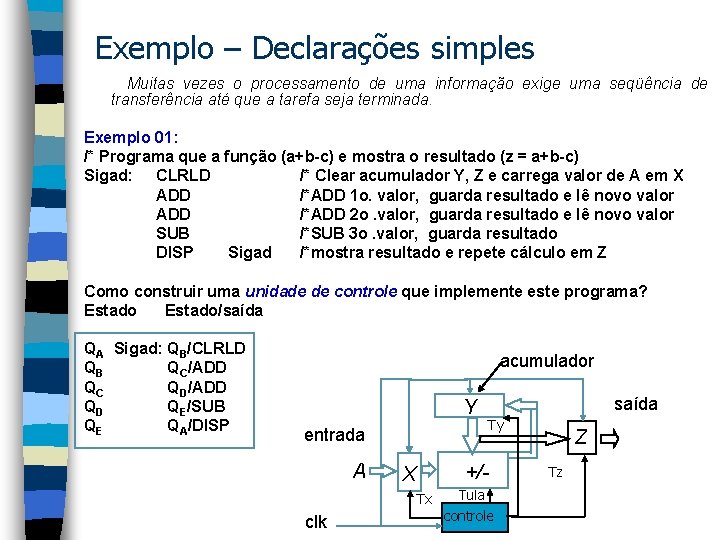

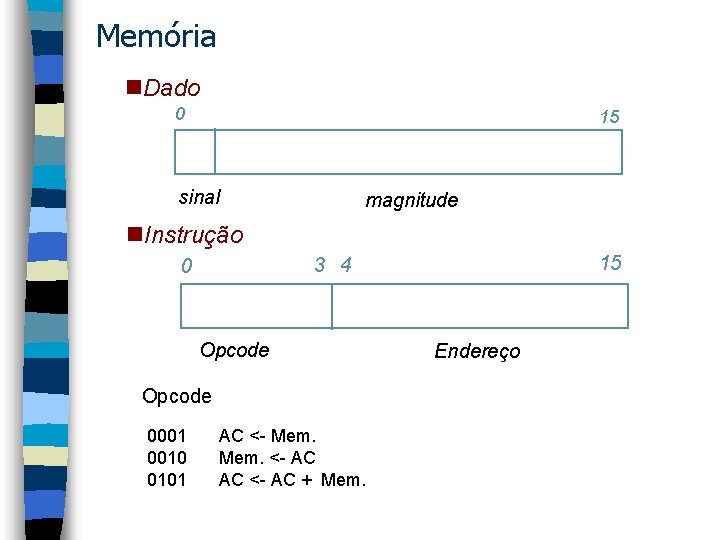

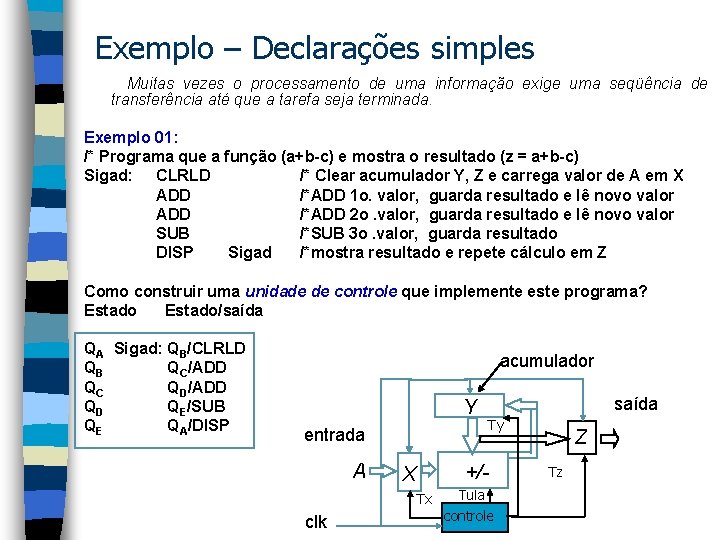

Exemplo – Declarações simples Muitas vezes o processamento de uma informação exige uma seqüência de transferência até que a tarefa seja terminada. Exemplo 01: /* Programa que a função (a+b-c) e mostra o resultado (z = a+b-c) Sigad: CLRLD /* Clear acumulador Y, Z e carrega valor de A em X ADD /*ADD 1 o. valor, guarda resultado e lê novo valor ADD /*ADD 2 o. valor, guarda resultado e lê novo valor SUB /*SUB 3 o. valor, guarda resultado DISP Sigad /*mostra resultado e repete cálculo em Z Como construir uma unidade de controle que implemente este programa? Estado/saída QA Sigad: QB/CLRLD QB QC/ADD QC QD/ADD QD QE/SUB QE QA/DISP acumulador Y entrada A Ty +/- X Tx clk saída Tula controle Z Tz

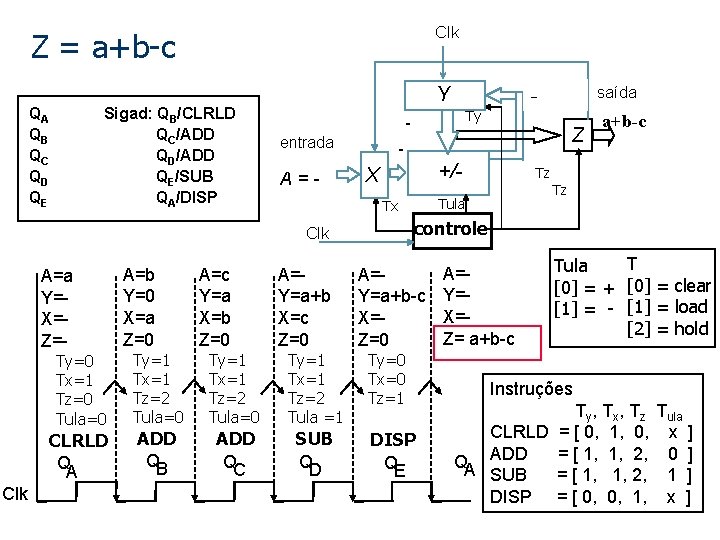

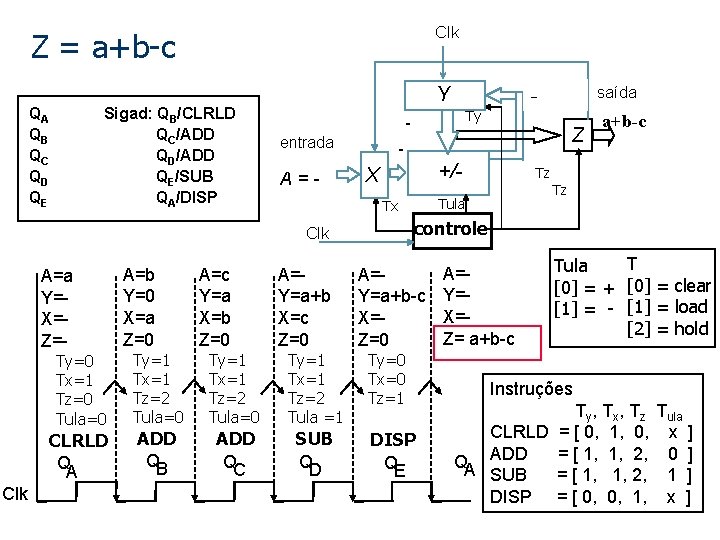

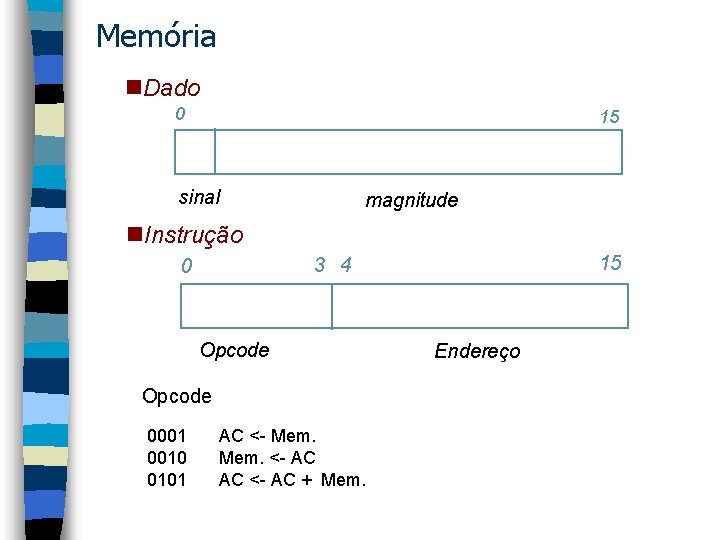

Clk Z = a+b-c QA QB QC QD QE Sigad: QB/CLRLD QC/ADD QD/ADD QE/SUB QA/DISP entrada AA == b ca -a Ty=0 Tx=1 Tz=0 Tula=0 CLRLD QA Clk A=b Y=0 X=a Z=0 A=c Y=a X=b Z=0 Ty=1 Tx=1 Tz=2 Tula=0 Ty=1 Tx=1 Tz=2 Tula =1 ADD QB ADD QC SUB QD Z +/- X saída 0 -a+b-c Tz Tz Tula Tx A=Y=a+b X=c Z=0 Ty -a+b 0 aa+b-c ab-c- controle Clk A=a Y=X=Z=- -aa+b-c +b Y A=Y=a+b-c X=Z=0 Ty=0 Tx=0 Tz=1 DISP QE A=Y=X=Z= a+b-c T Tula [0] = + [0] = clear [1] = - [1] = load [2] = hold Instruções Ty, Tx, Tz Tula CLRLD = [ 0, 1, 0, x ] = [ 1, 1, 2, 0 ] QA ADD SUB = [ 1, 1, 2, 1 ] DISP = [ 0, 0, 1, x ]

![Instruções Ty Tx Tz Tula CLRLD 0 1 0 x ADD Instruções Ty, Tx, Tz Tula CLRLD = [ 0, 1, 0, x] ADD =](https://slidetodoc.com/presentation_image_h2/96458355035b1209fc18d18c2cd8931d/image-7.jpg)

Instruções Ty, Tx, Tz Tula CLRLD = [ 0, 1, 0, x] ADD = [ 1, 1, 2, 0] SUB = [ 1, 1, 2, 1] DISP = [ 0, 0, 1, x] Contador de programa memória Y Z = a+b-c entrada memória A clk Contador Memória: do Programa Instruções (PC) 00 01 02 03 04 05 saída Ty +/- X Tx Inst |dados Execução de um progama Z cpu memória Tz cpu Tula controle memória Z=a+b-c cpu end(dados) [0, 1, 0, x] CLRLD end+0(a) [1, 1, 2, 0] ADD end+1(b) [1, 1, 2, 0] ADD end+2(c) [1, 1, 2, 1] SUB [0, 0, 1, x] DISP ------- X = -; Y=-; X = a; Y=0; X = b; Y=a; X = c ; Y= a+b; X = -; Y= a+b-c; Z= -; Z= 0; Z =0; Z =a+b-c;

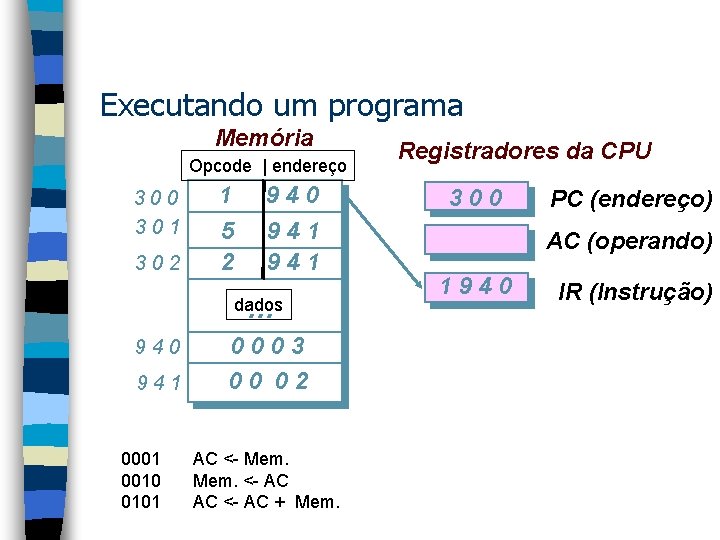

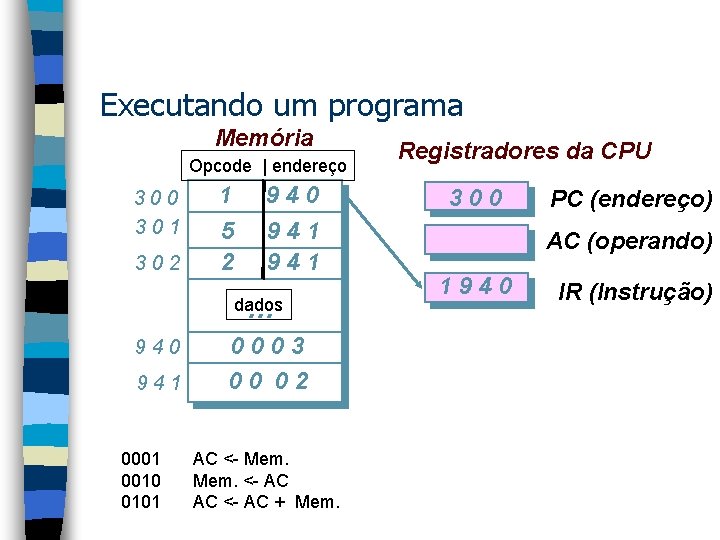

Memória n. Dado 0 15 sinal magnitude n. Instrução Opcode 0001 0010 0101 15 3 4 0 AC <- Mem. <- AC AC <- AC + Mem. Endereço

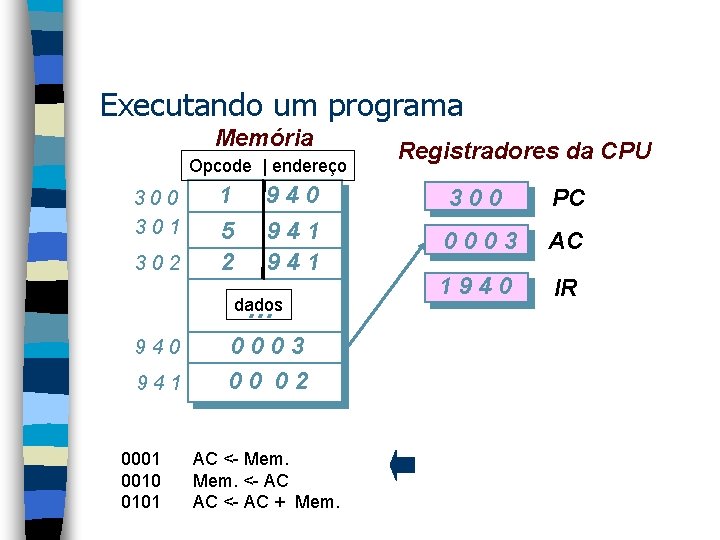

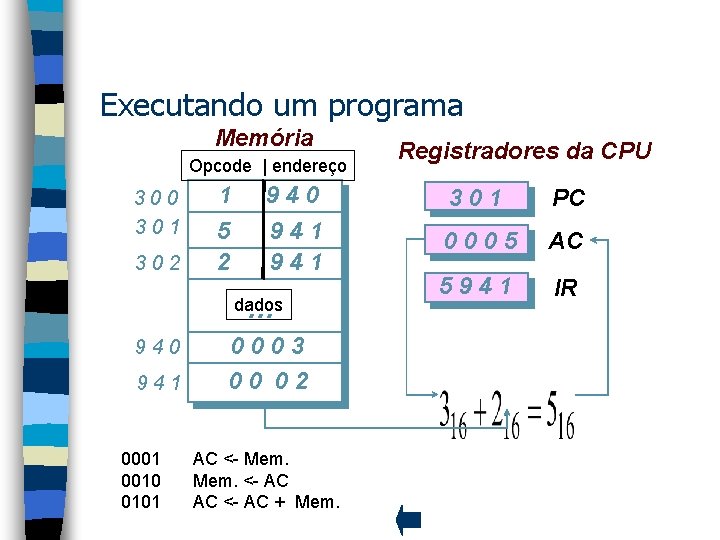

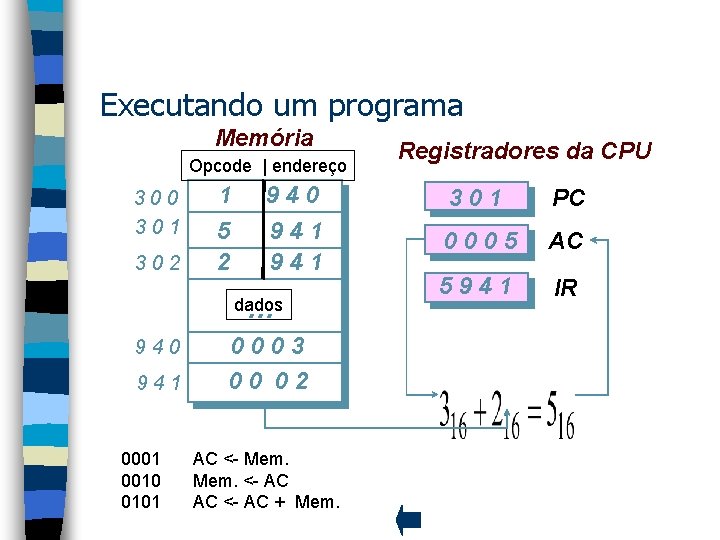

Executando um programa Memória Opcode | endereço 300 301 302 1 5 2 940 941 . . . dados 940 941 0001 0010 0101 0003 00 02 AC <- Mem. <- AC AC <- AC + Mem. Registradores da CPU 300 PC (endereço) AC (operando) 1940 IR (Instrução)

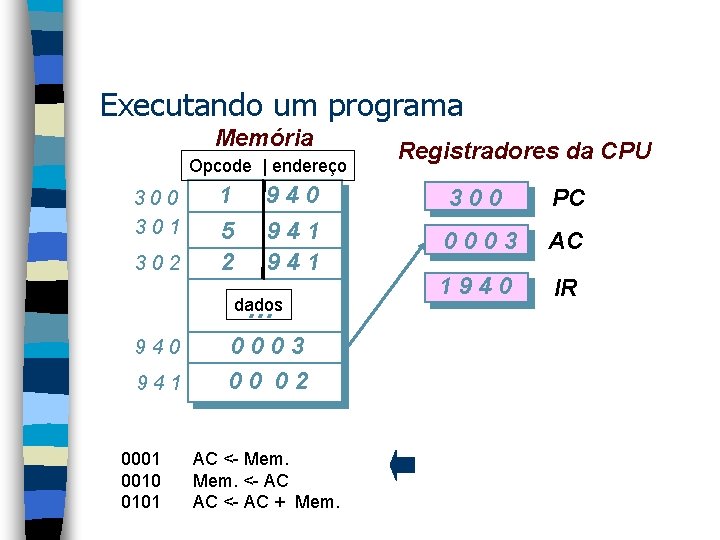

Executando um programa Memória Opcode | endereço 300 301 302 1 5 2 940 941 . . . dados 940 941 0001 0010 0101 0003 00 02 AC <- Mem. <- AC AC <- AC + Mem. Registradores da CPU 300 PC 0003 AC 1940 IR

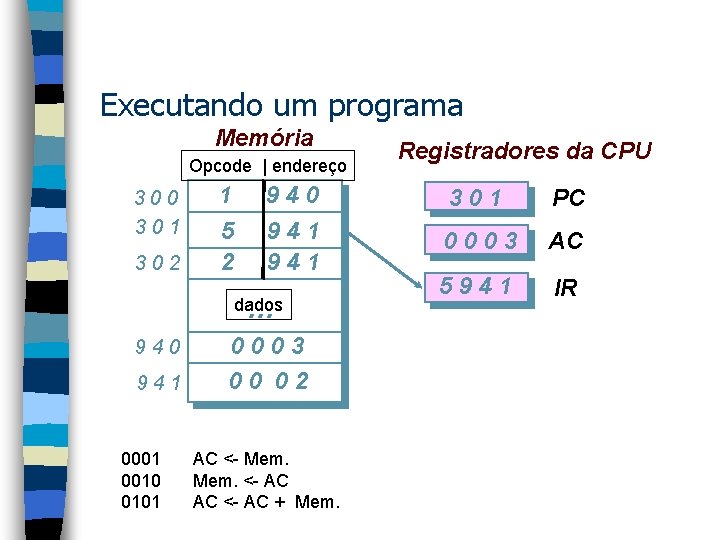

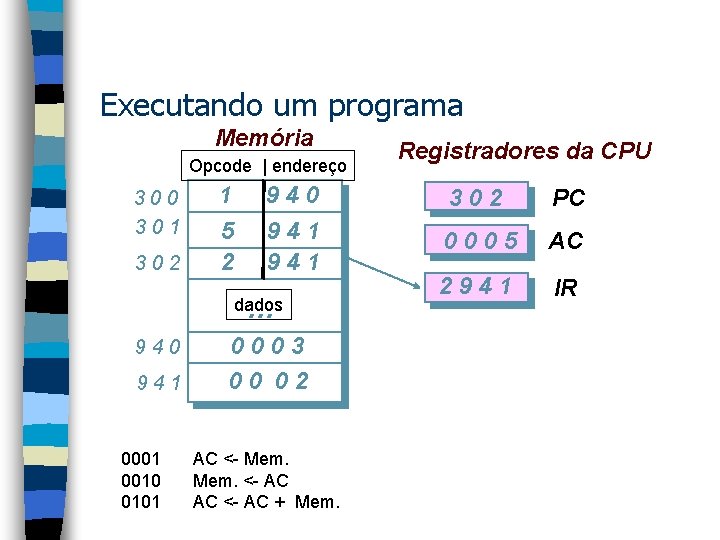

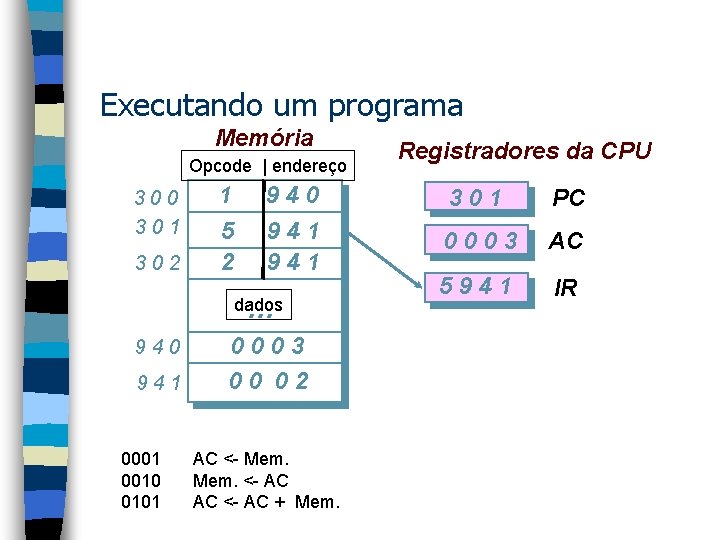

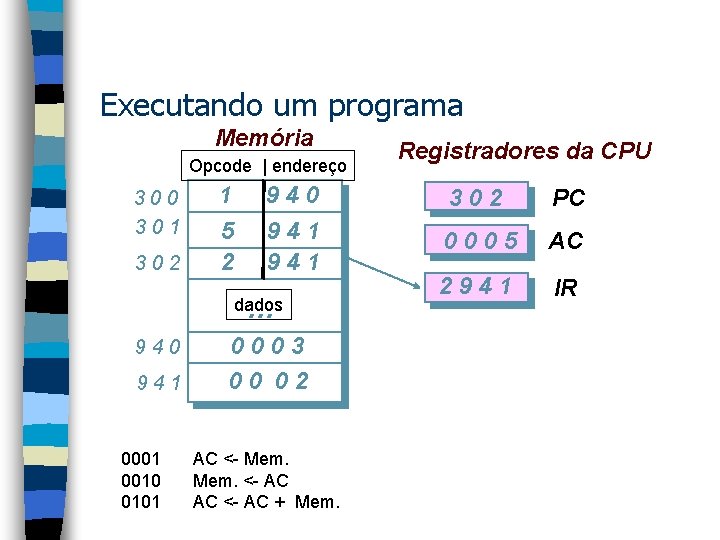

Executando um programa Memória Opcode | endereço 300 301 302 1 5 2 940 941 . . . dados 940 941 0001 0010 0101 0003 00 02 AC <- Mem. <- AC AC <- AC + Mem. Registradores da CPU 301 PC 0003 AC 5941 IR

Executando um programa Memória Opcode | endereço 300 301 302 1 5 2 940 941 . . . dados 940 941 0001 0010 0101 0003 00 02 AC <- Mem. <- AC AC <- AC + Mem. Registradores da CPU 301 PC 0005 AC 5941 IR

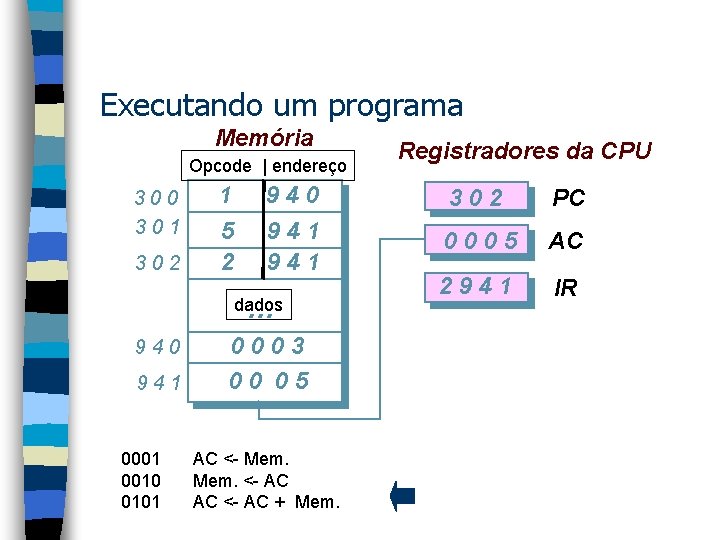

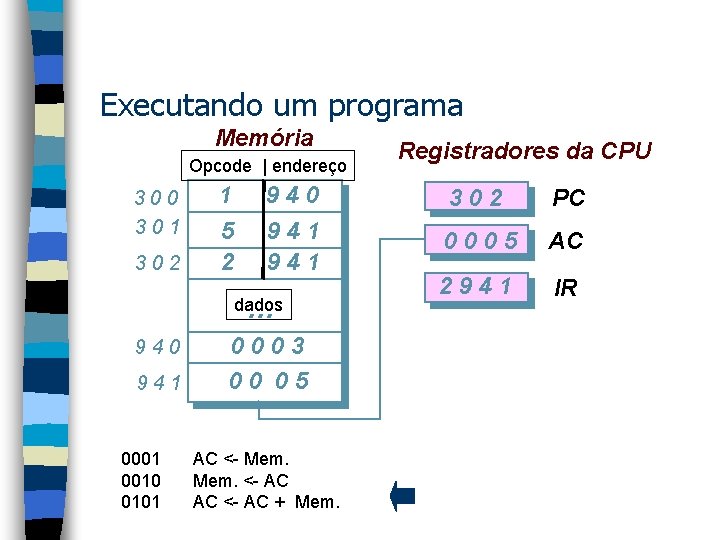

Executando um programa Memória Opcode | endereço 300 301 302 1 5 2 940 941 . . . dados 940 941 0001 0010 0101 0003 00 02 AC <- Mem. <- AC AC <- AC + Mem. Registradores da CPU 302 PC 0005 AC 2941 IR

Executando um programa Memória Opcode | endereço 300 301 302 1 5 2 940 941 . . . dados 940 941 0001 0010 0101 0003 00 05 AC <- Mem. <- AC AC <- AC + Mem. Registradores da CPU 302 PC 0005 AC 2941 IR

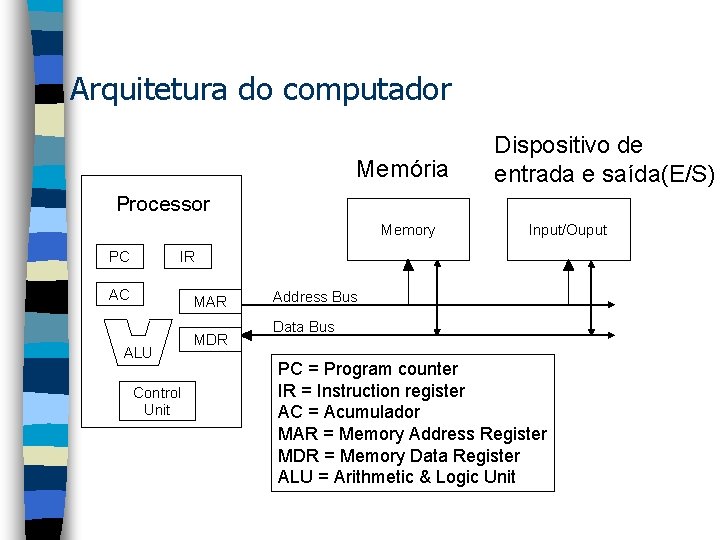

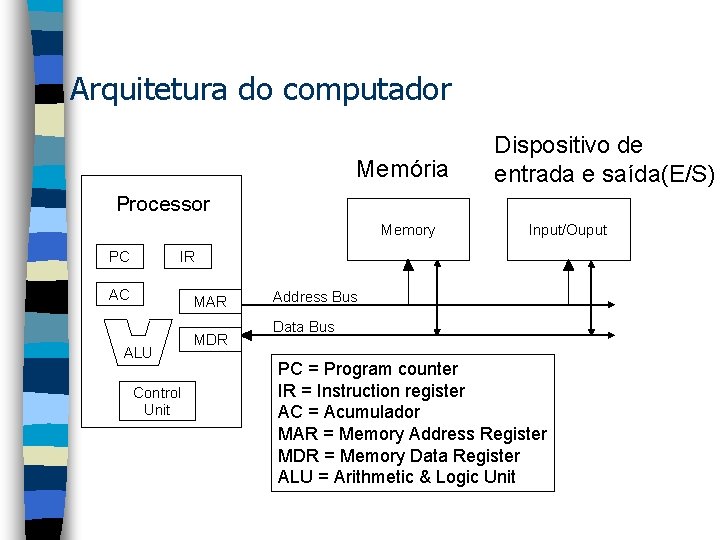

Arquitetura do computador Memória Dispositivo de entrada e saída(E/S) Processor Memory PC Input/Ouput IR AC MAR ALU Control Unit MDR Address Bus Data Bus PC = Program counter IR = Instruction register AC = Acumulador MAR = Memory Address Register MDR = Memory Data Register ALU = Arithmetic & Logic Unit

Arquitetura do computador n n n PC - program counter – indica a próxima instrução a ser executada. IR - Instruction register – recebe a instrução a ser decodificada pela CPU. AC – Acumulador (registrador auxiliar). Guarda temporariamente valores sendo calculados. MAR – Registrador que indica a próxima posição de memória a ser referenciada. Conectado ao barramento de endereços. MDR – Registrador usado para receber ou transmitir dados. Conectado ao barramento de dados. ALU (ULA) – Unidade Lógica

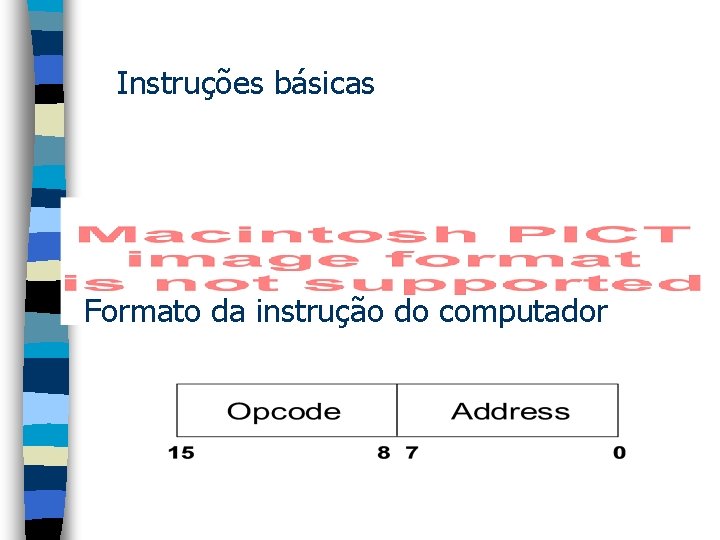

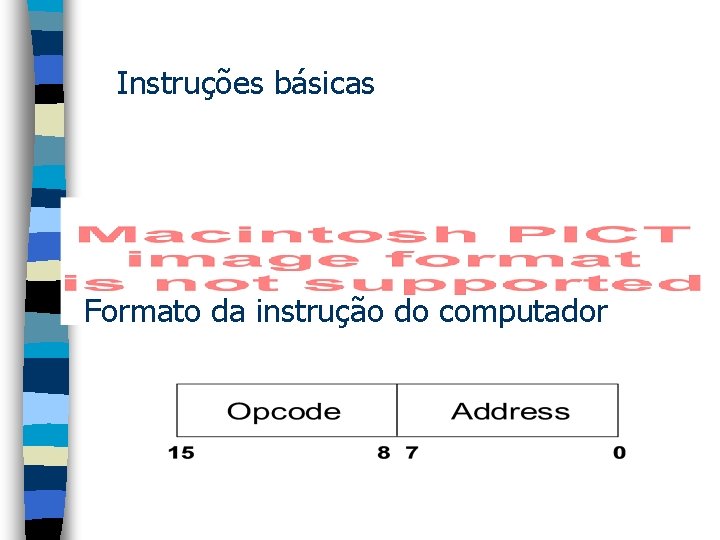

Instruções básicas Formato da instrução do computador

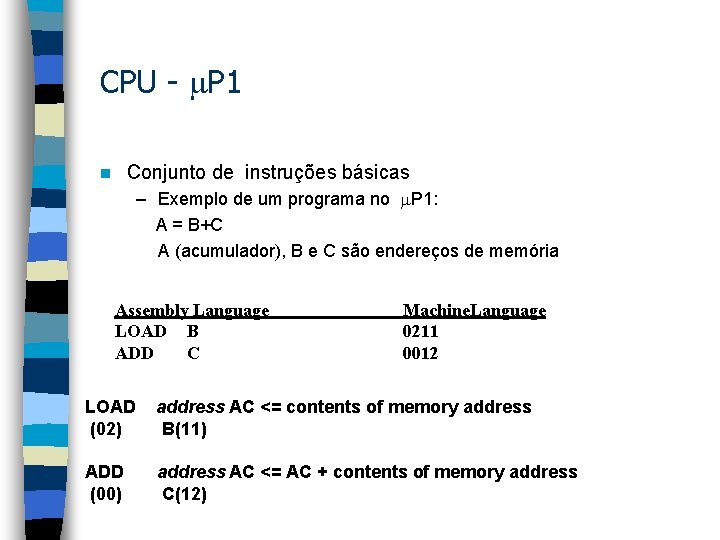

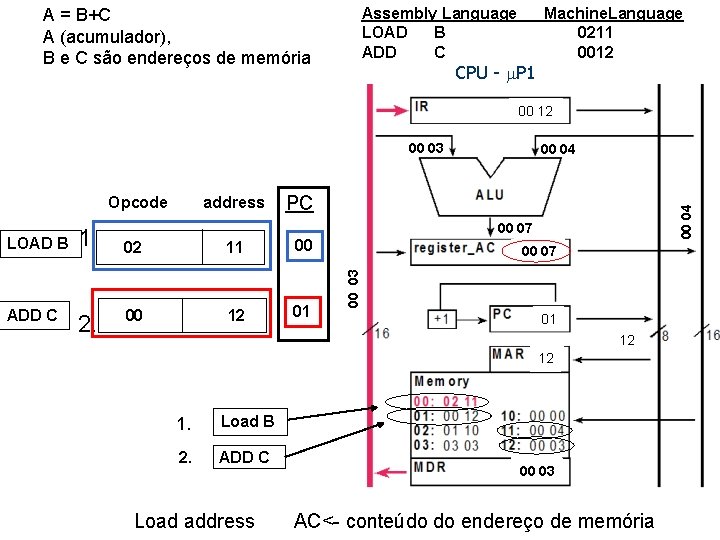

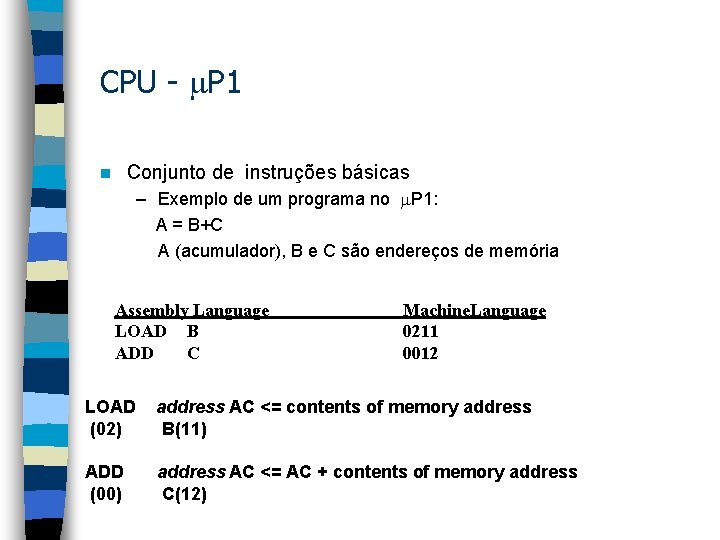

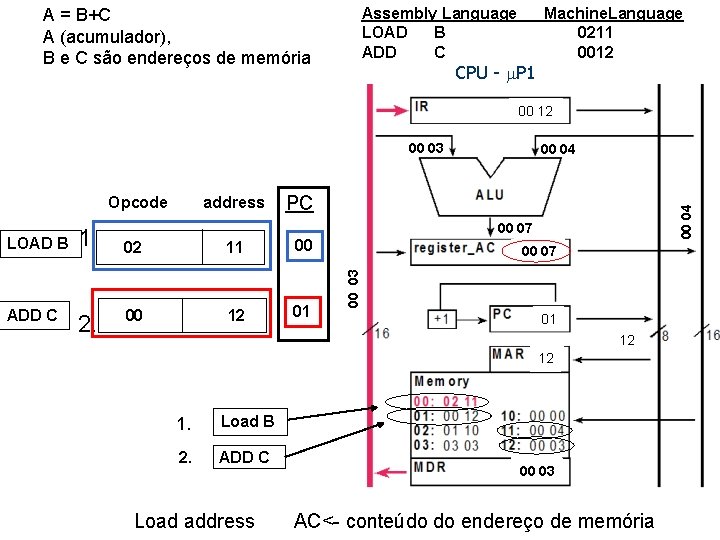

CPU - P 1 Conjunto de instruções básicas n – Exemplo de um programa no P 1: A = B+C A (acumulador), B e C são endereços de memória Assembly Language LOAD B ADD C Machine. Language 0211 0012 LOAD (02) address AC <= contents of memory address B(11) ADD (00) address AC <= AC + contents of memory address C(12)

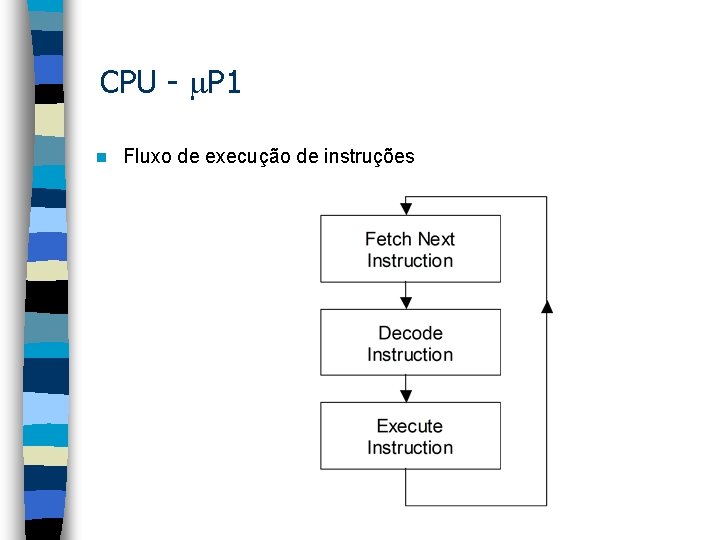

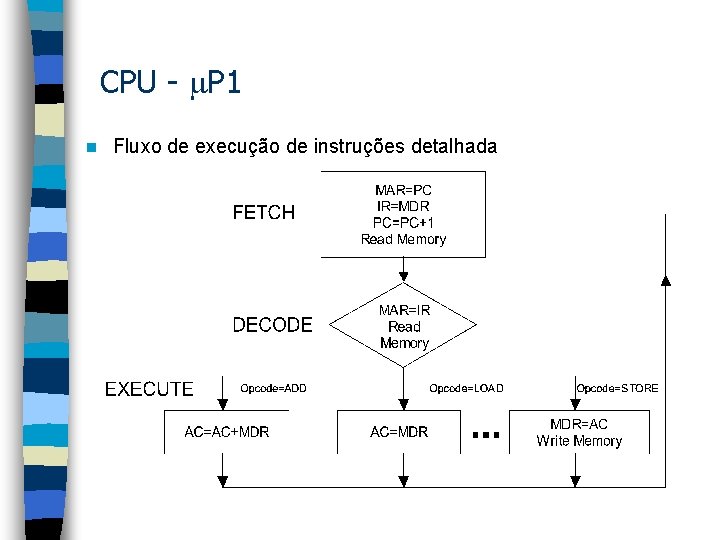

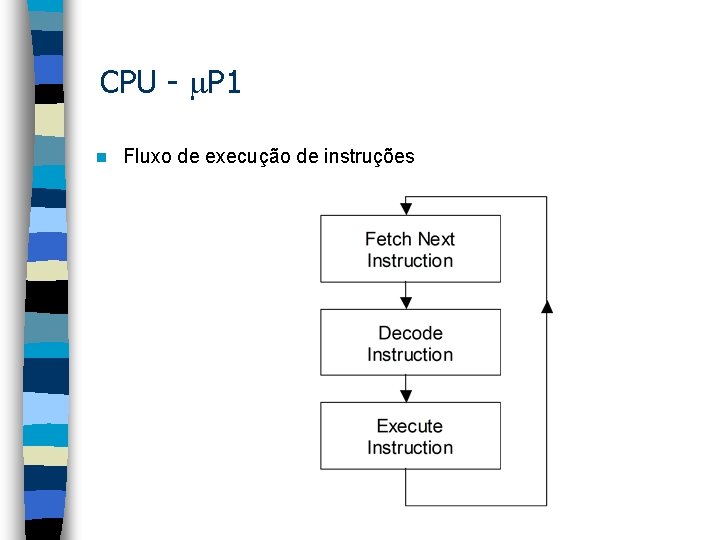

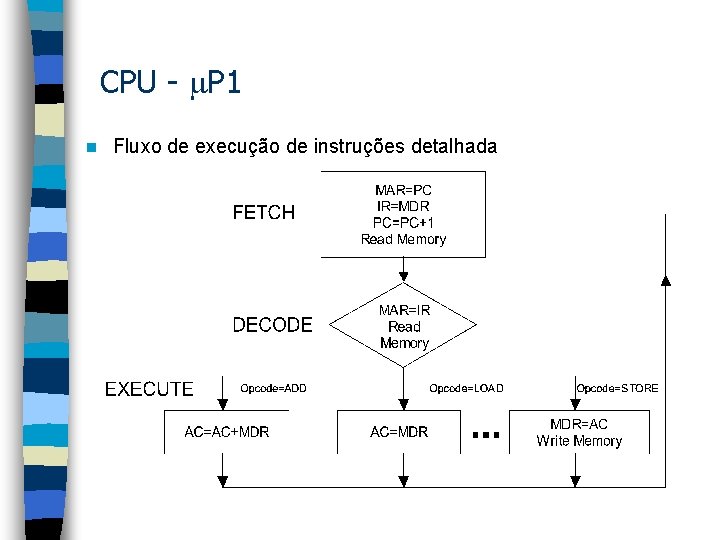

CPU - P 1 n Fluxo de execução de instruções

CPU - P 1 n Fluxo de execução de instruções detalhada

A = B+C A (acumulador), B e C são endereços de memória Assembly Language LOAD B ADD C CPU - P 1 Machine. Language 0211 0012 02 00 12 11 00 03 ADD C 2. PC 00 07 02 11 00 00 12 01 00 07 00 04 03 00 04 02 12 11 LOAD B 1. address 00 04 Opcode 00 04 01 01 11 12 12 11 01 1. Load B 2. ADD C Load address 00 03 0212 00 11 04 AC<- conteúdo do endereço de memória

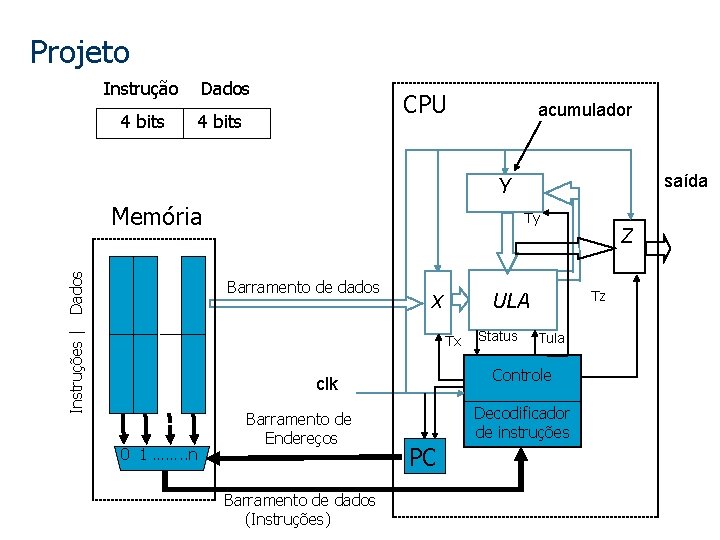

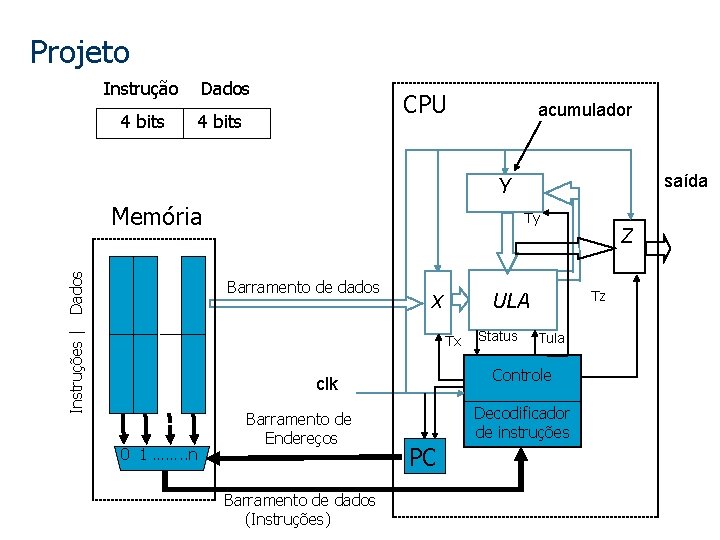

Projeto Instrução 4 bits Dados CPU 4 bits acumulador saída Y Instruções | Dados Memória Ty Barramento de dados Tx 0 1 ……. . n Barramento de dados (Instruções) Status Tula Controle clk Barramento de Endereços Tz ULA X Decodificador de instruções PC Z

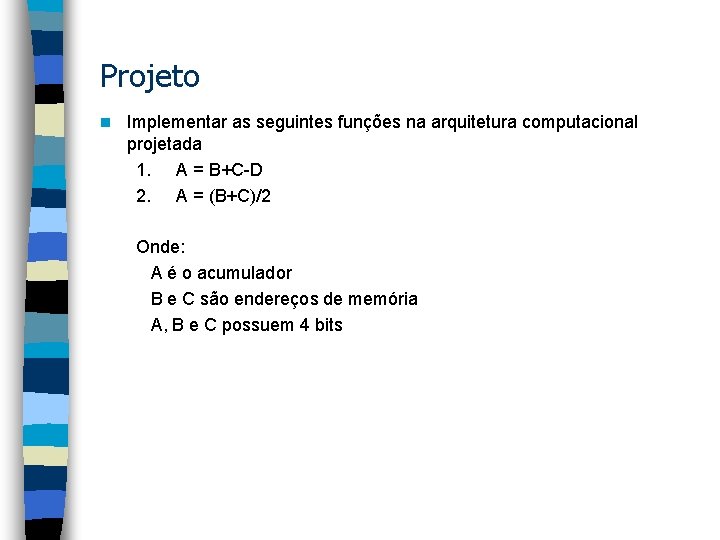

Projeto n Implementar as seguintes funções na arquitetura computacional projetada 1. A = B+C-D 2. A = (B+C)/2 Onde: A é o acumulador B e C são endereços de memória A, B e C possuem 4 bits