Sistemas Digitais Aula 11 1 Projeto de sistemas

![Instruções Ty, Tx, Tz Tula CLRLD = [ 0, 1, 0, x] ADD = Instruções Ty, Tx, Tz Tula CLRLD = [ 0, 1, 0, x] ADD =](https://slidetodoc.com/presentation_image_h2/cdd98a705e7cddb8f1ec0383a7fdd306/image-17.jpg)

![Clk QA Sigad: QB/CLRLD QB QC/LDXY QC QD/ GT Case: QD if = STATUS=[0] Clk QA Sigad: QB/CLRLD QB QC/LDXY QC QD/ GT Case: QD if = STATUS=[0]](https://slidetodoc.com/presentation_image_h2/cdd98a705e7cddb8f1ec0383a7fdd306/image-19.jpg)

- Slides: 27

Sistemas Digitais Aula 11 1

Projeto de sistemas digitais n Unidade de Processamento da Informação – Transferência de Informação – Operação sobre a informação n Unidade de Controle – Determina a seqüência de operação a ser realizada Entrada de controle Status Unidade de processamento da Informação Saída Controle Saída de controle 2

Unidade de Procesamento da Informação n Componentes – Lógica Combinacional – Registradores internos – Circuito de temporização Registrador T 1 REG T 1 Entrada X 1 Xn clock Lógica Combinacional (+, -, >, <, . . . ) e Registradores T 0 T 1 Status Controle Unidade de controle Saída Z 1 Zk Máquina de estados 3

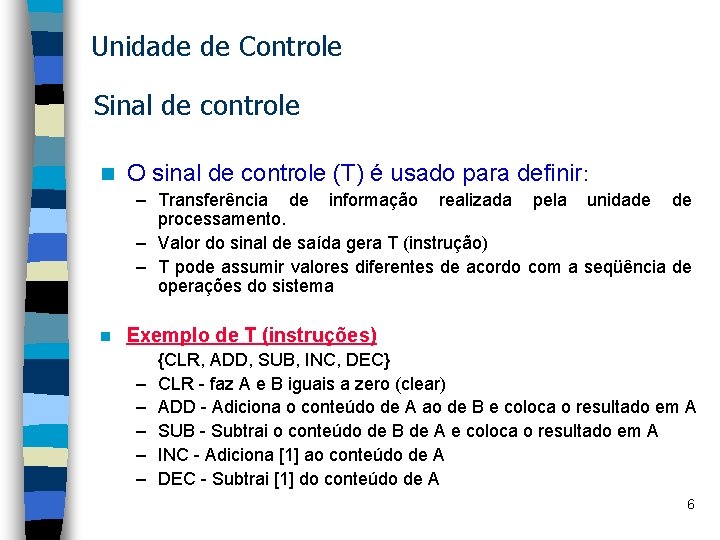

Expressões de próximo estado na unidade de Processamento n Registradores - > FLIP-FLOP Master/Slave – valor corrente ou estado corrente do registrador é o valor armazenado no registrador quando o pulso de transferência é aplicado. – Enquanto o pulso de transferência estiver “ON”, a saída do registrador mantém o valor corrente. – Quando o pulso de transferência for removido (carga na descida do relógio), o registrador passará a conter o próximo estado definido pelas entradas. n Equação de próximo estado Qi <- Fi (X 1, . . , Xk, Q 1. . . . , Qm, T) X - Valor do sinal de entrada Q - estado atual T - sinal de controle n Equação de saída – Zi : = Gj (X 1, . . , Xk , Q 1, . . . . , Qm , T) 4

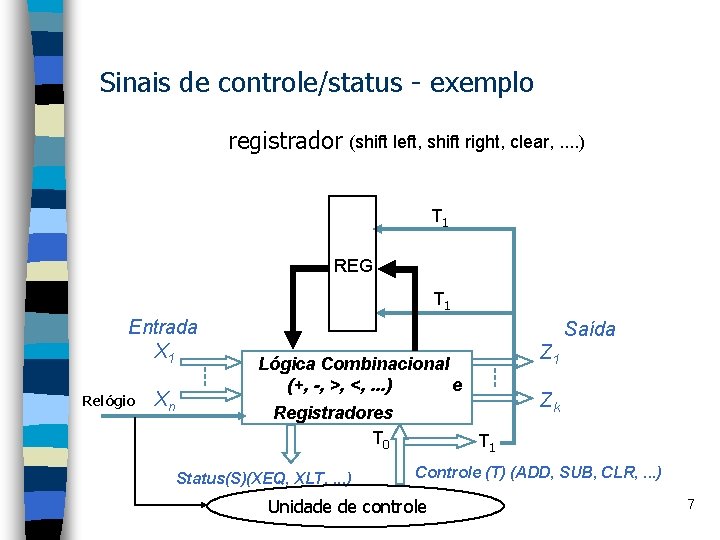

Unidade de Controle - status É um sinal de entrada que informa a FSM alguma condição de teste n O Status permite alterar a seqüência de computação n – Si : = Xi (X 1 , . . , Xk , Q 1 , . . . . Qm ) O sinal de status não é função de T n O sinal de status S só alcança um estado permanente depois que a entrada X alcançar um estado permanente. n A unidade de controle pode usar o valor corrente de S na determinação do valor corrente do sinal de controle T. n O sinal de transferência, descida ou subida do relógio, é aplicado apenas quando a unidade de controle teve tempo suficiente para gerar o sinal de controle T, após a recepção do valor corrente de S. n Exemplo de sinais de Status O sinal de status pertence ao conjunto {XGT, XEQ, XNEQ, XGEQ, XLT} n – Onde XGT XEQ XNEQ XLT X maior que [0] X igual a [0] X diferente de [0] X menor que [0] 5

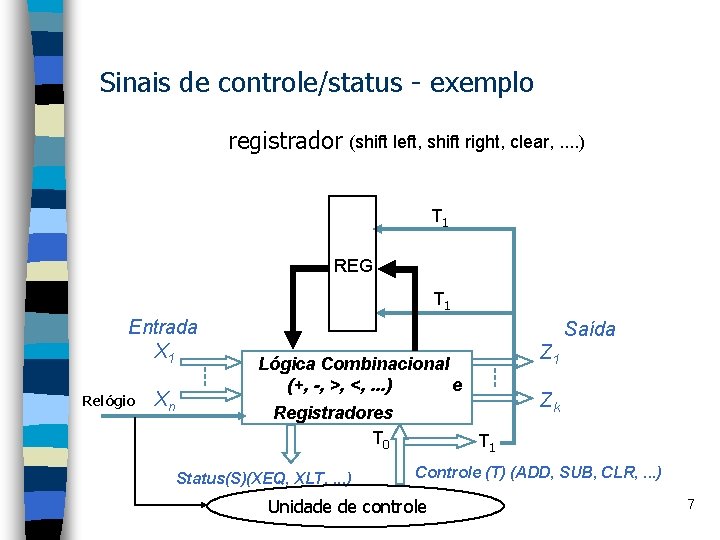

Unidade de Controle Sinal de controle n O sinal de controle (T) é usado para definir: – Transferência de informação realizada pela unidade de processamento. – Valor do sinal de saída gera T (instrução) – T pode assumir valores diferentes de acordo com a seqüência de operações do sistema n Exemplo de T (instruções) – – – {CLR, ADD, SUB, INC, DEC} CLR - faz A e B iguais a zero (clear) ADD - Adiciona o conteúdo de A ao de B e coloca o resultado em A SUB - Subtrai o conteúdo de B de A e coloca o resultado em A INC - Adiciona [1] ao conteúdo de A DEC - Subtrai [1] do conteúdo de A 6

Sinais de controle/status - exemplo registrador (shift left, shift right, clear, . . ) T 1 REG T 1 Entrada X 1 Relógio Xn Saída Z 1 Lógica Combinacional (+, -, >, <, . . . ) e Registradores T 0 Status(S)(XEQ, XLT, . . . ) Zk T 1 Controle (T) (ADD, SUB, CLR, . . . ) Unidade de controle 7

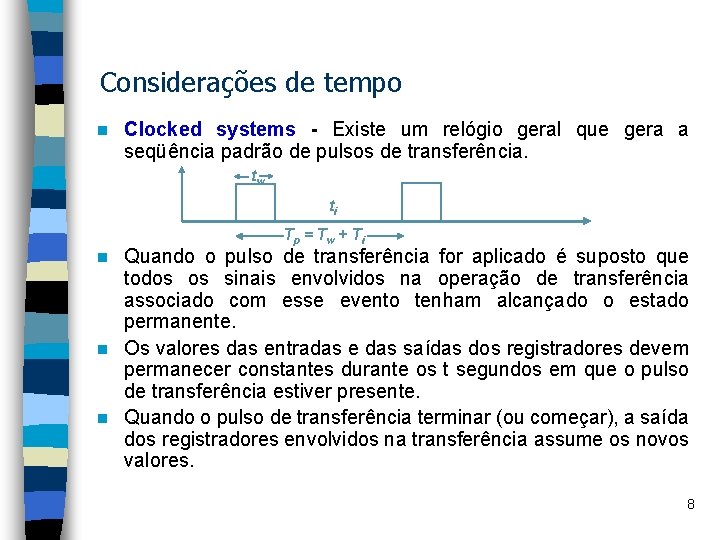

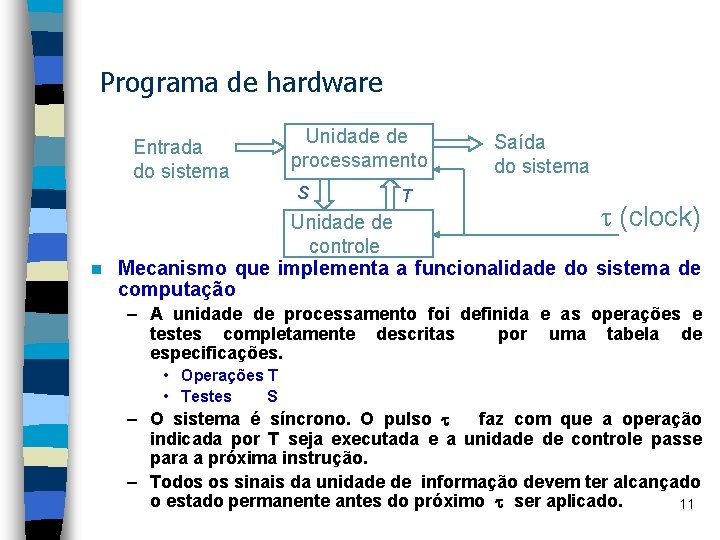

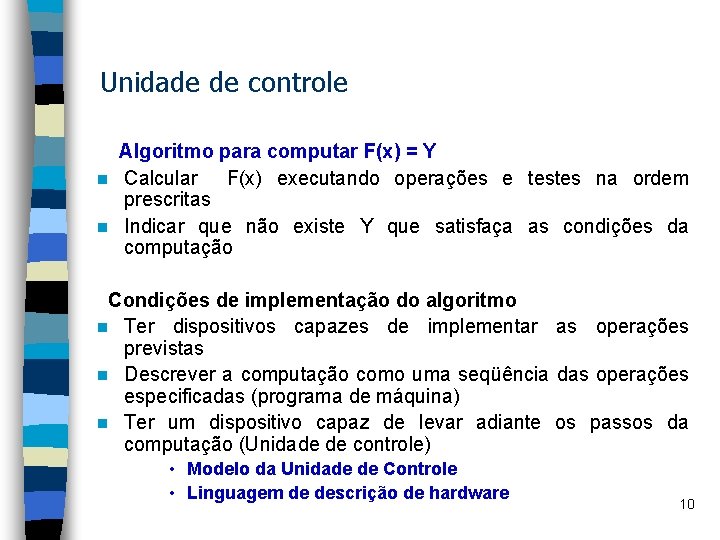

Considerações de tempo n Clocked systems - Existe um relógio geral que gera a seqüência padrão de pulsos de transferência. tw ti Tp = T w + T i Quando o pulso de transferência for aplicado é suposto que todos os sinais envolvidos na operação de transferência associado com esse evento tenham alcançado o estado permanente. n Os valores das entradas e das saídas dos registradores devem permanecer constantes durante os t segundos em que o pulso de transferência estiver presente. n Quando o pulso de transferência terminar (ou começar), a saída dos registradores envolvidos na transferência assume os novos valores. n 8

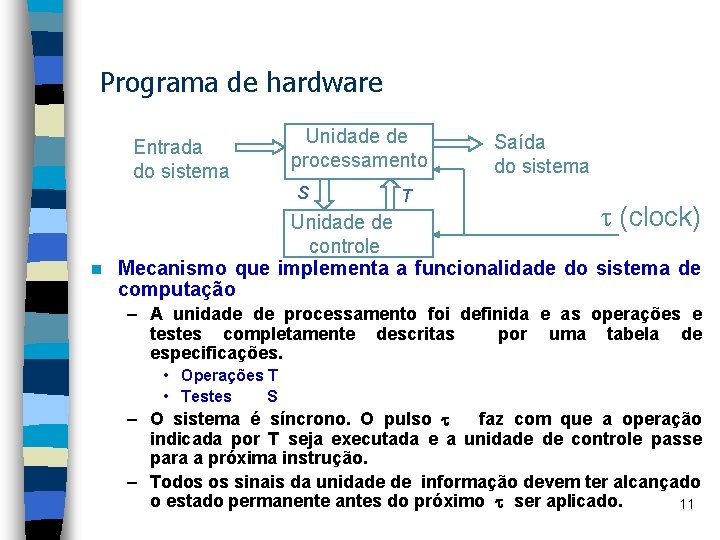

Relação de tempo entre os diferentes sinais na unidade de processamento da informação X X X Saída do registrador alcança novo valor Muda a entrada Muda o status (S) Muda o sinal de controle T (instrução) Registrador de controle (sinais estáveis) Prepara a Saída Pulso de transferência 9

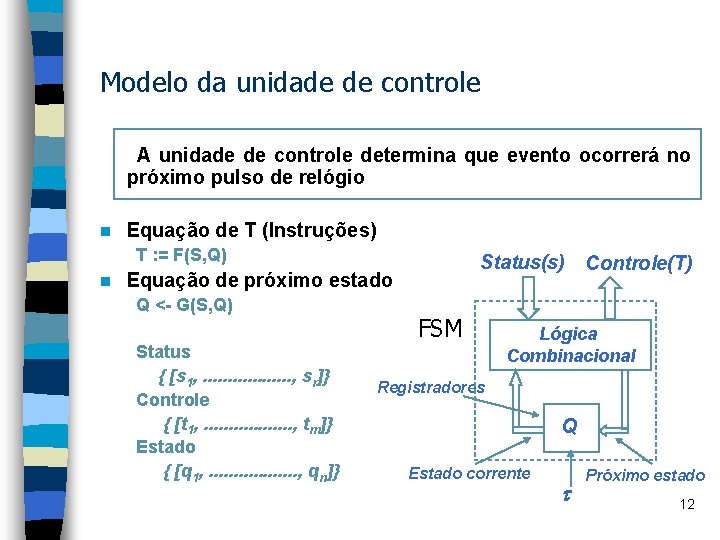

Unidade de controle Algoritmo para computar F(x) = Y n Calcular F(x) executando operações e testes na ordem prescritas n Indicar que não existe Y que satisfaça as condições da computação Condições de implementação do algoritmo n Ter dispositivos capazes de implementar as operações previstas n Descrever a computação como uma seqüência das operações especificadas (programa de máquina) n Ter um dispositivo capaz de levar adiante os passos da computação (Unidade de controle) • Modelo da Unidade de Controle • Linguagem de descrição de hardware 10

Programa de hardware Entrada do sistema Unidade de processamento S Saída do sistema T t (clock) Unidade de controle n Mecanismo que implementa a funcionalidade do sistema de computação – A unidade de processamento foi definida e as operações e testes completamente descritas por uma tabela de especificações. • Operações T • Testes S – O sistema é síncrono. O pulso t faz com que a operação indicada por T seja executada e a unidade de controle passe para a próxima instrução. – Todos os sinais da unidade de informação devem ter alcançado o estado permanente antes do próximo t ser aplicado. 11

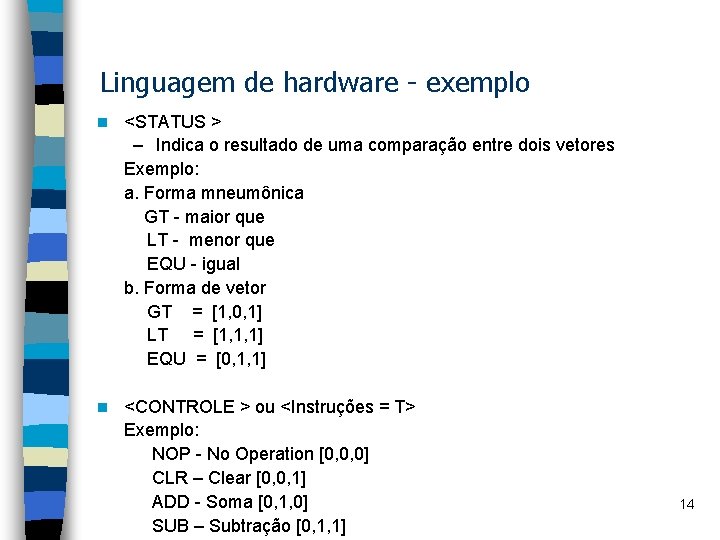

Modelo da unidade de controle A unidade de controle determina que evento ocorrerá no próximo pulso de relógio n Equação de T (Instruções) T : = F(S, Q) n Status(s) Equação de próximo estado Q <- G(S, Q) Status { [s 1, . . . . , sr]} Controle { [t 1, . . . . , tm]} Estado { [q 1, . . . . , qn]} FSM Controle(T) Lógica Combinacional Registradores Q Estado corrente t Próximo estado 12

Processo de programação 1. Informação de entrada 2. Realizar uma seqüência de operações 3. Testar e decidir o que fazer nos próximos passos 4. Repetir uma seqüência de passos até que certas tarefas computacionais sejam realizadas 5. Informações de saída n Programa de hardware Tabela de especificação -> Linguagem Operações -> Controle T (instrução) Testes -> Status S n Projeto – Definir a tarefa computacional a ser realizada – Definir a unidade de processamento da informação – Definir o algoritmo para implementar a computação – Criar a tabela de estado da unidade de controle – Implementar e testar o hardware 13

Linguagem de hardware - exemplo n <STATUS > – Indica o resultado de uma comparação entre dois vetores Exemplo: a. Forma mneumônica GT - maior que LT - menor que EQU - igual b. Forma de vetor GT = [1, 0, 1] LT = [1, 1, 1] EQU = [0, 1, 1] n <CONTROLE > ou <Instruções = T> Exemplo: NOP - No Operation [0, 0, 0] CLR – Clear [0, 0, 1] ADD - Soma [0, 1, 0] SUB – Subtração [0, 1, 1] 14

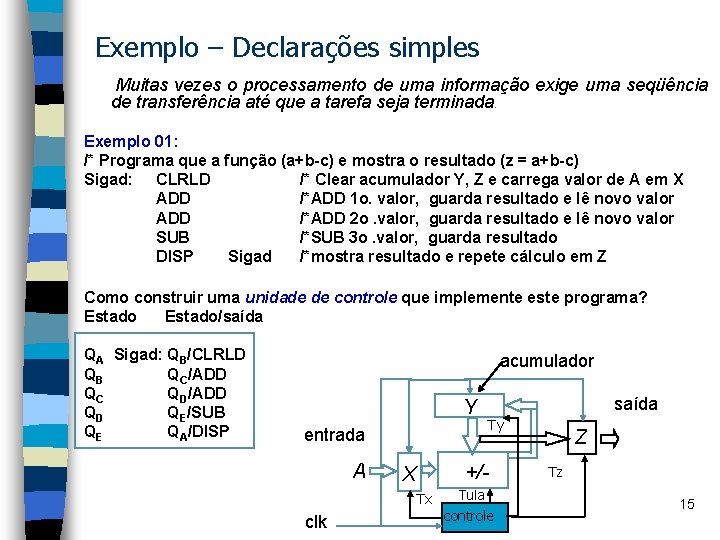

Exemplo – Declarações simples Muitas vezes o processamento de uma informação exige uma seqüência de transferência até que a tarefa seja terminada. Exemplo 01: /* Programa que a função (a+b-c) e mostra o resultado (z = a+b-c) Sigad: CLRLD /* Clear acumulador Y, Z e carrega valor de A em X ADD /*ADD 1 o. valor, guarda resultado e lê novo valor ADD /*ADD 2 o. valor, guarda resultado e lê novo valor SUB /*SUB 3 o. valor, guarda resultado DISP Sigad /*mostra resultado e repete cálculo em Z Como construir uma unidade de controle que implemente este programa? Estado/saída QA Sigad: QB/CLRLD QB QC/ADD QC QD/ADD QD QE/SUB QE QA/DISP acumulador Y entrada A Ty +/- X Tx clk saída Tula controle Z Tz 15

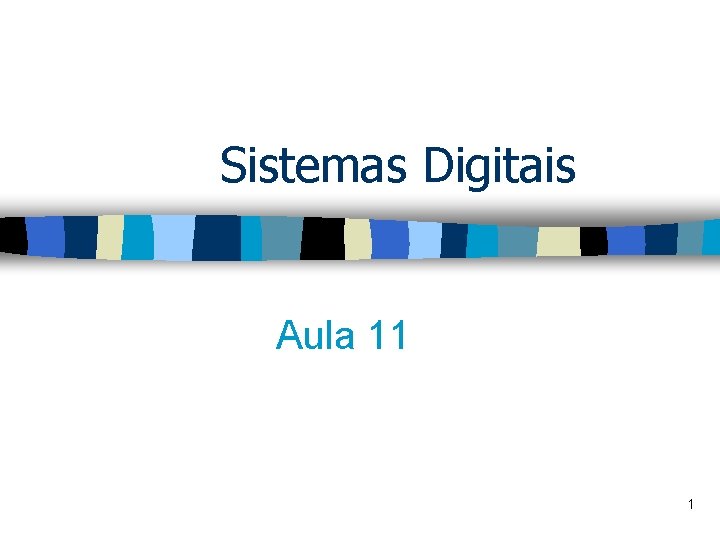

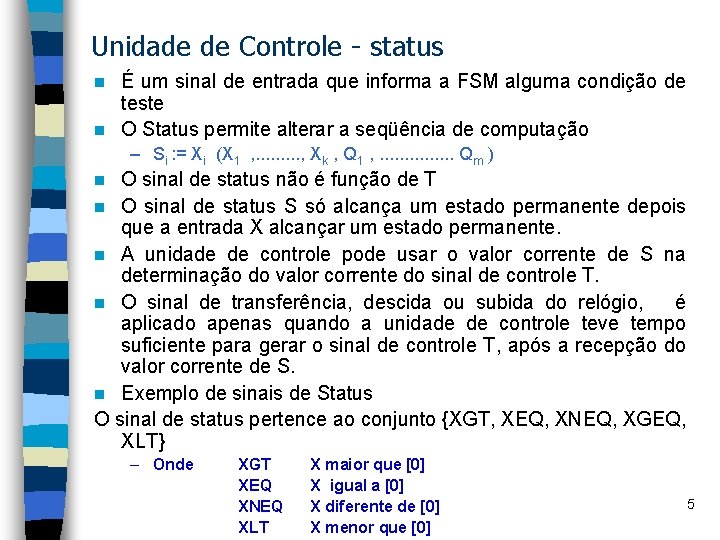

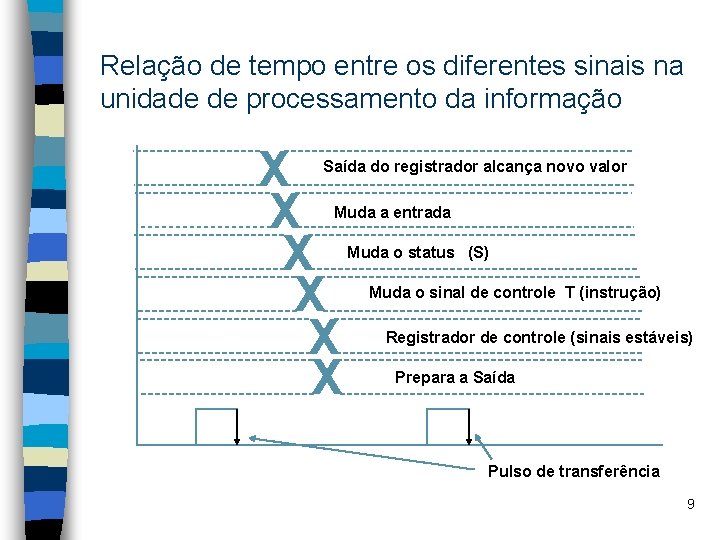

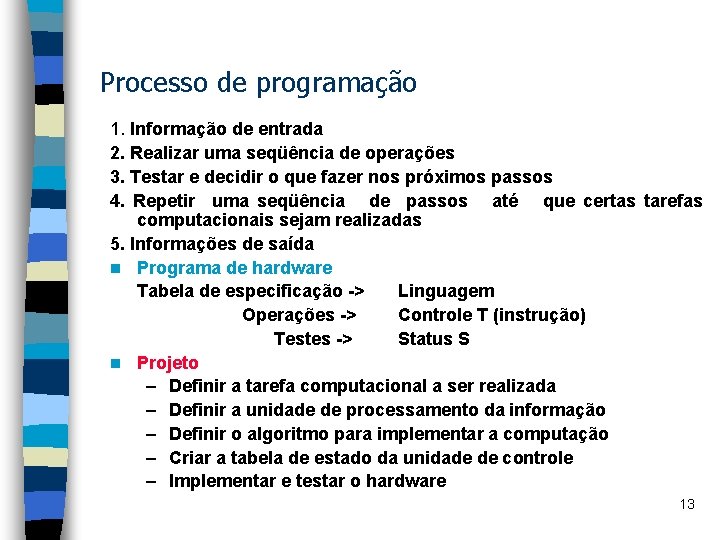

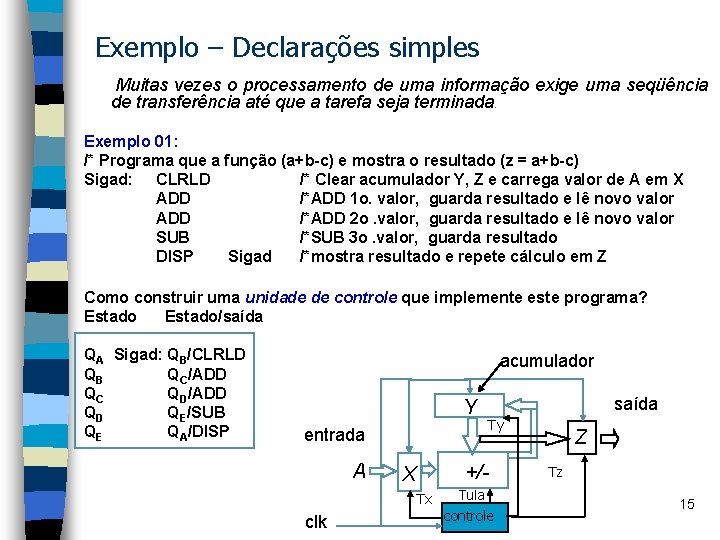

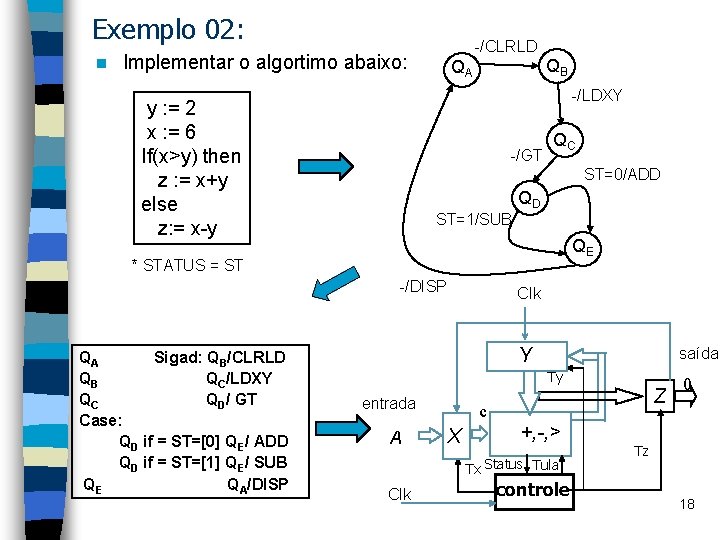

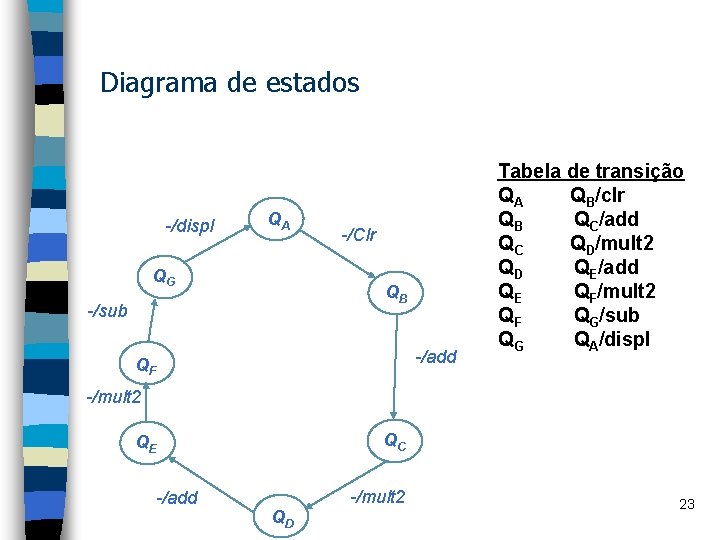

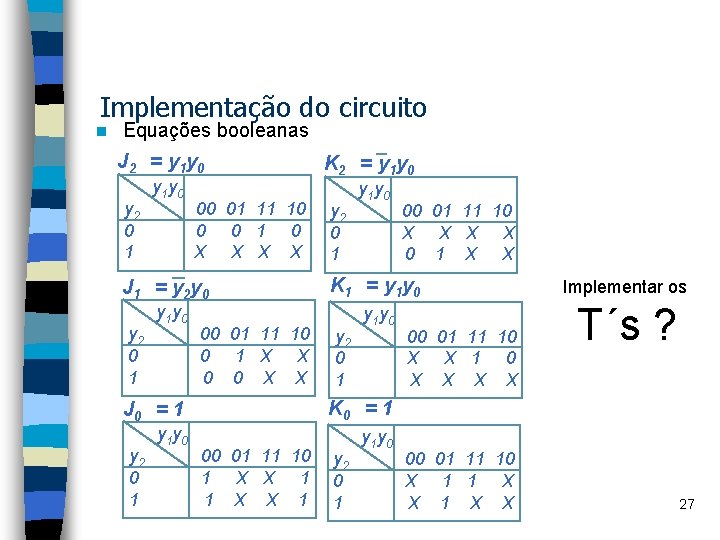

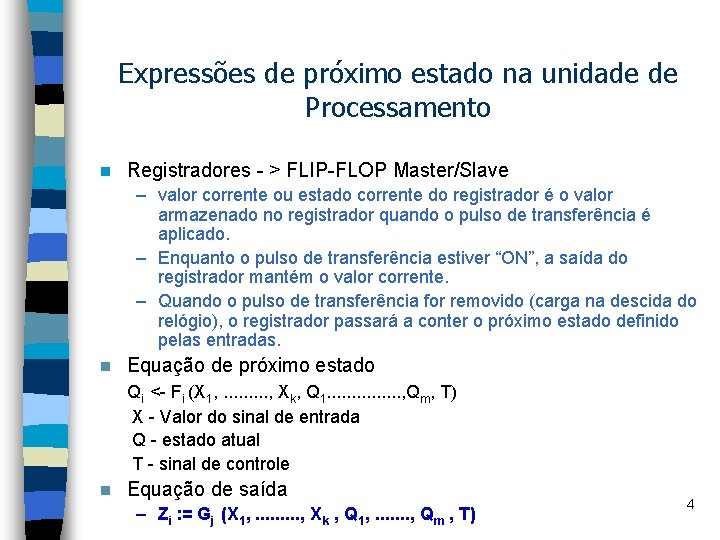

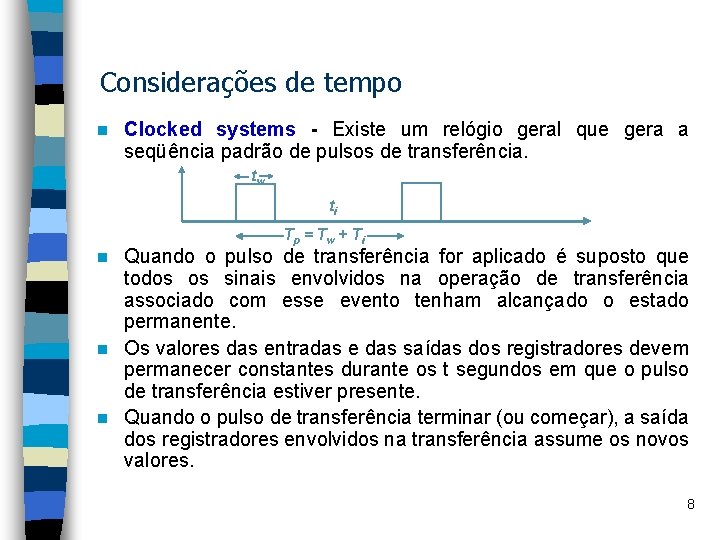

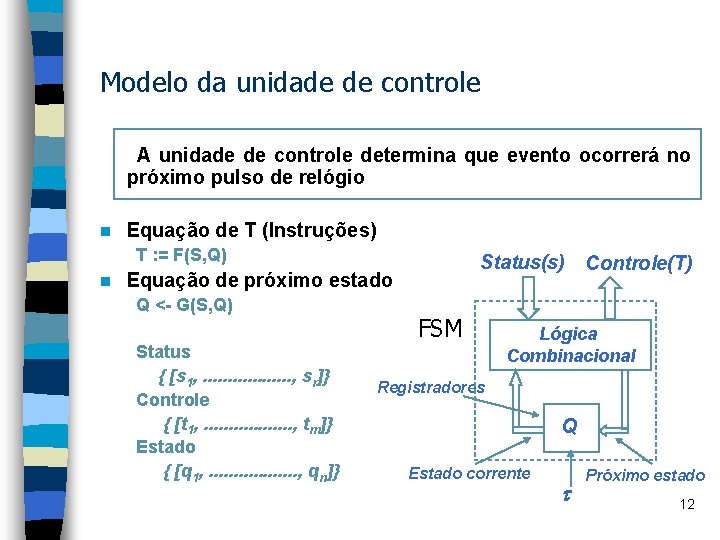

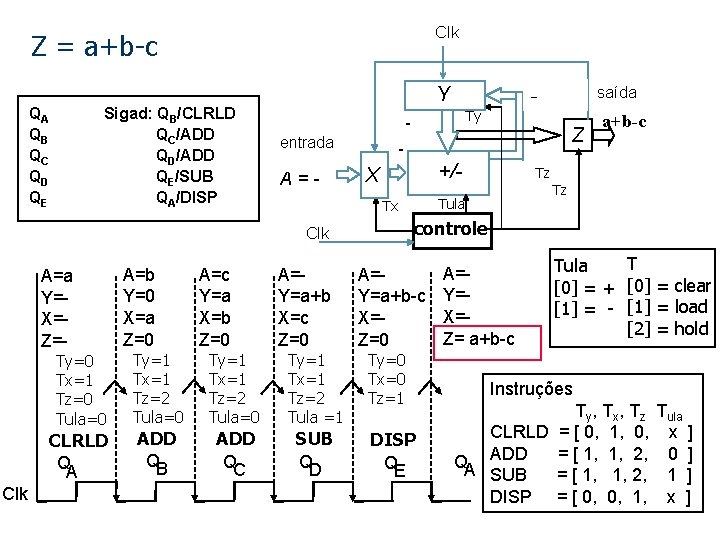

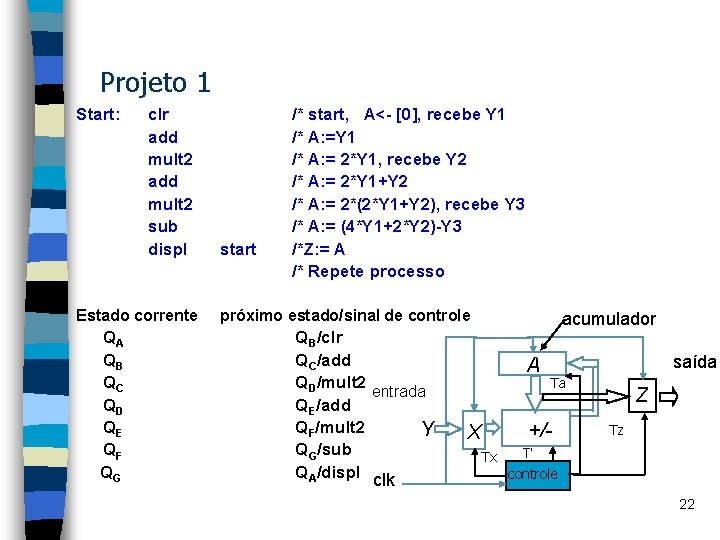

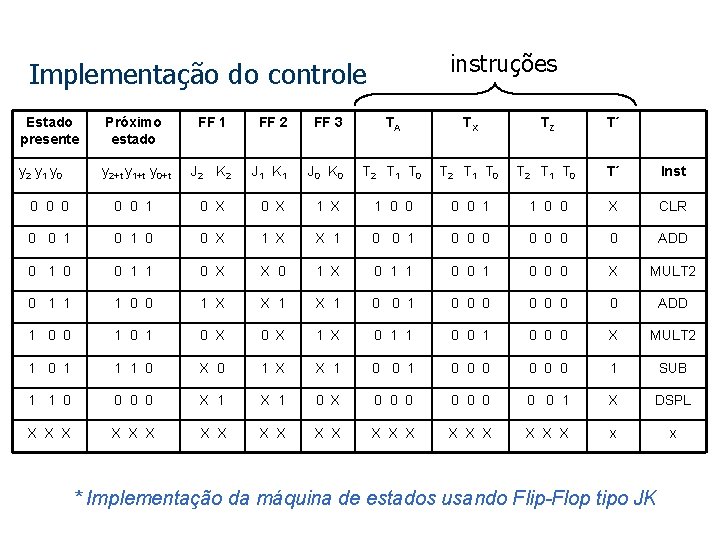

Clk Z = a+b-c QA QB QC QD QE Sigad: QB/CLRLD QC/ADD QD/ADD QE/SUB QA/DISP entrada AA == b ca -a Ty=0 Tx=1 Tz=0 Tula=0 CLRLD QA Clk A=b Y=0 X=a Z=0 A=c Y=a X=b Z=0 Ty=1 Tx=1 Tz=2 Tula=0 Ty=1 Tx=1 Tz=2 Tula =1 ADD QB ADD QC SUB QD Z +/- X saída 0 -a+b-c Tz Tz Tula Tx A=Y=a+b X=c Z=0 Ty -a+b 0 aa+b-c ab-c- controle Clk A=a Y=X=Z=- -aa+b-c +b Y A=Y=a+b-c X=Z=0 Ty=0 Tx=0 Tz=1 DISP QE A=Y=X=Z= a+b-c T Tula [0] = + [0] = clear [1] = - [1] = load [2] = hold Instruções Ty, Tx, Tz Tula CLRLD = [ 0, 1, 0, x ] = [ 1, 1, 2, 0 ] QA ADD SUB = [ 1, 1, 2, 1 ] DISP = [ 0, 0, 1, x ]

![Instruções Ty Tx Tz Tula CLRLD 0 1 0 x ADD Instruções Ty, Tx, Tz Tula CLRLD = [ 0, 1, 0, x] ADD =](https://slidetodoc.com/presentation_image_h2/cdd98a705e7cddb8f1ec0383a7fdd306/image-17.jpg)

Instruções Ty, Tx, Tz Tula CLRLD = [ 0, 1, 0, x] ADD = [ 1, 1, 2, 0] SUB = [ 1, 1, 2, 1] DISP = [ 0, 0, 1, x] Contador de programa memória Y Z = a+b-c entrada memória A clk Contador Memória: do Programa Instruções (PC) 00 01 02 03 04 05 saída Ty +/- X Tx Inst |dados Execução de um progama Z cpu memória Tz cpu Tula controle memória Z=a+b-c cpu end(dados) [0, 1, 0, x] CLRLD end+0(a) [1, 1, 2, 0] ADD end+1(b) [1, 1, 2, 0] ADD end+2(c) [1, 1, 2, 1] SUB [0, 0, 1, x] DISP ------- X = -; Y=-; X = a; Y=0; X = b; Y=a; X = c ; Y= a+b; X = -; Y= a+b-c; Z= -; Z= 0; Z =0; Z =a+b-c;

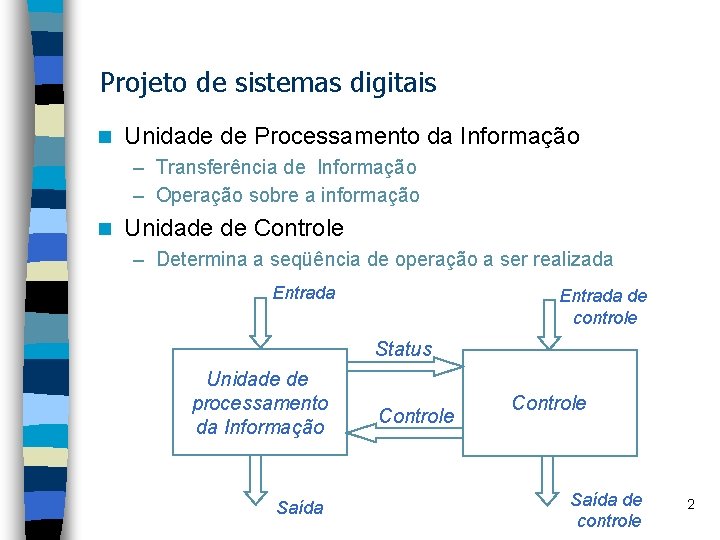

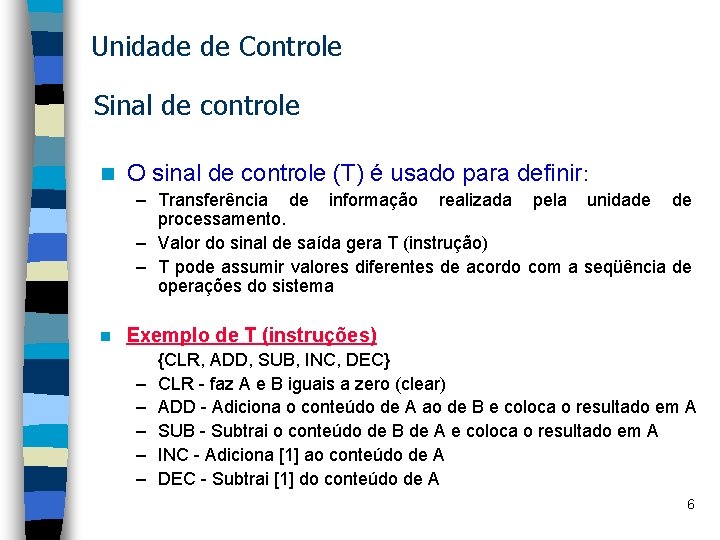

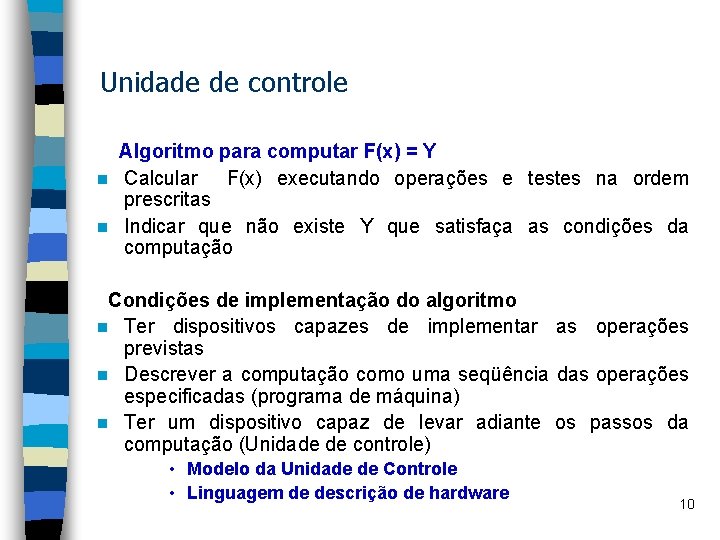

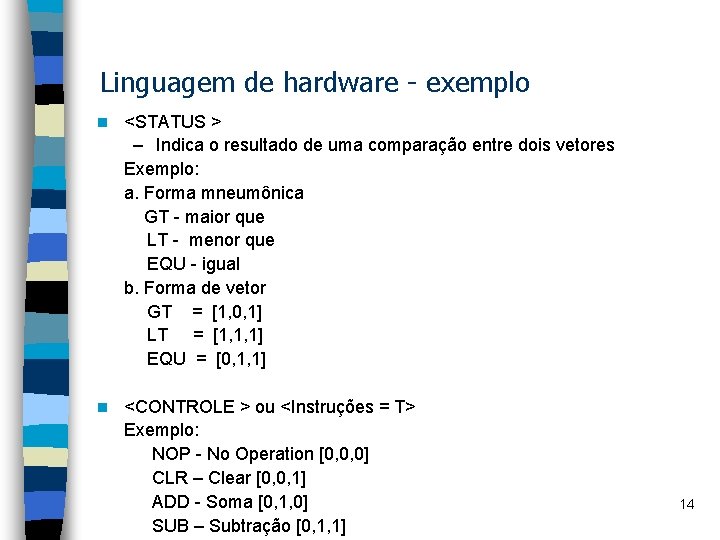

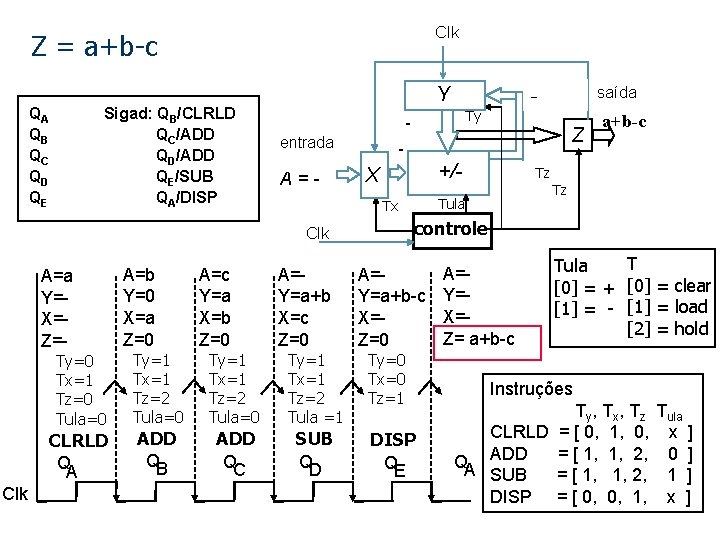

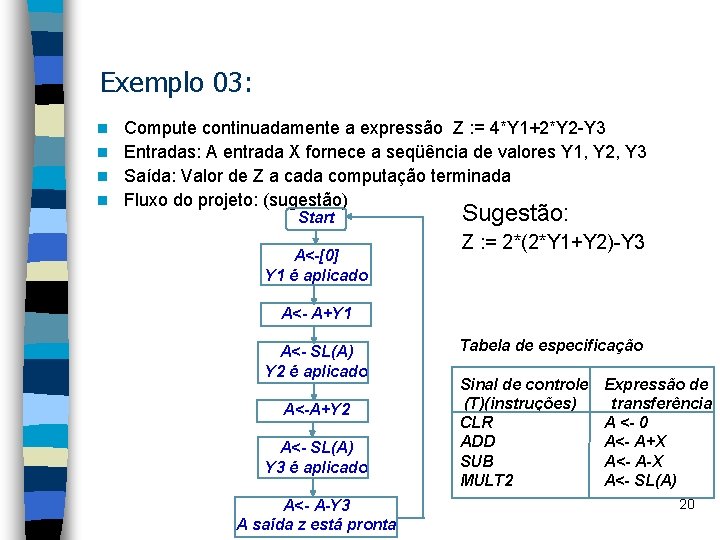

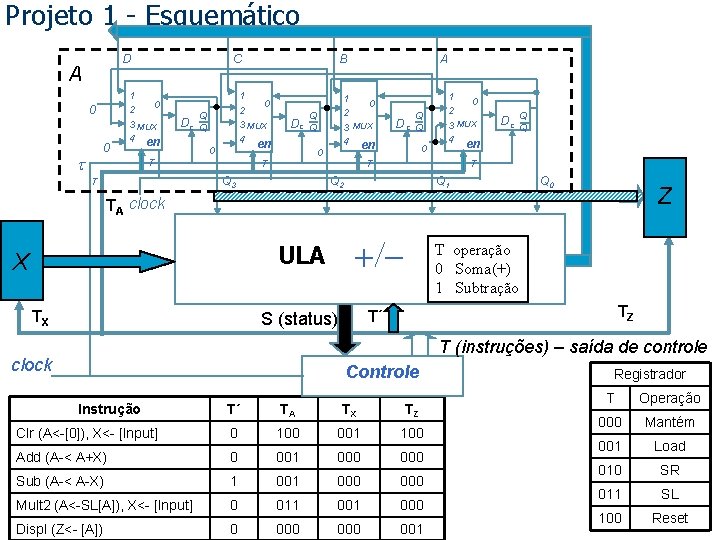

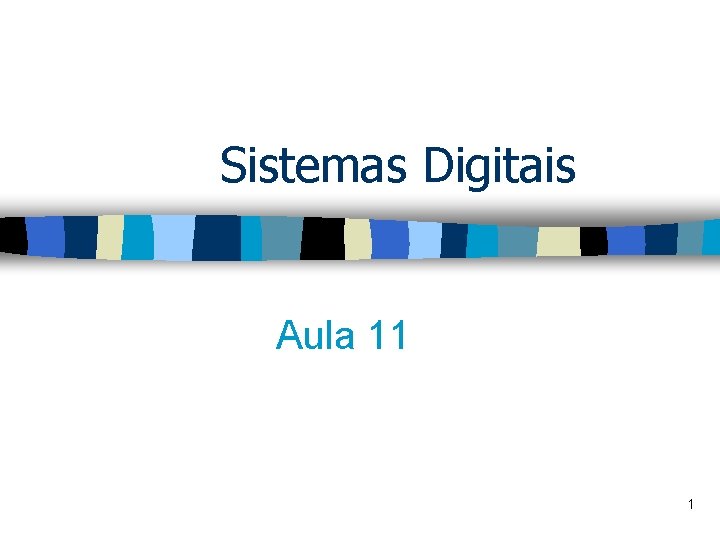

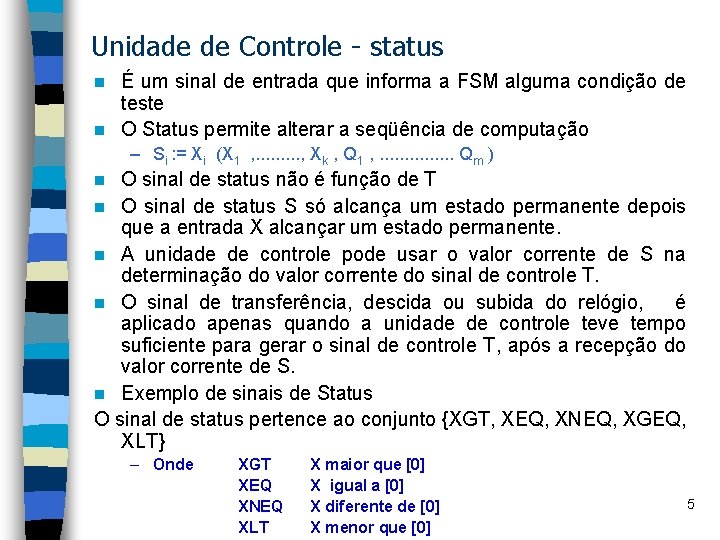

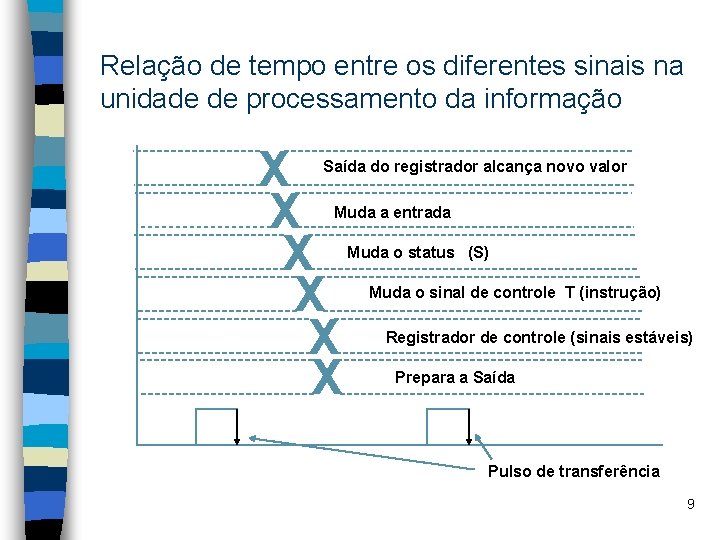

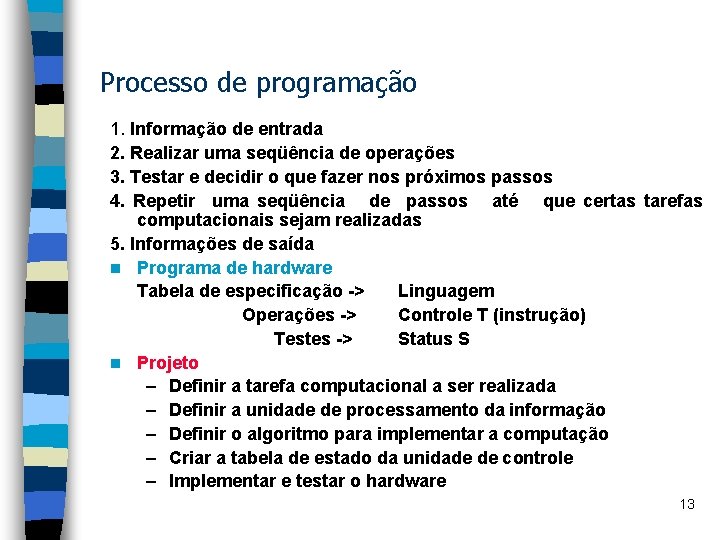

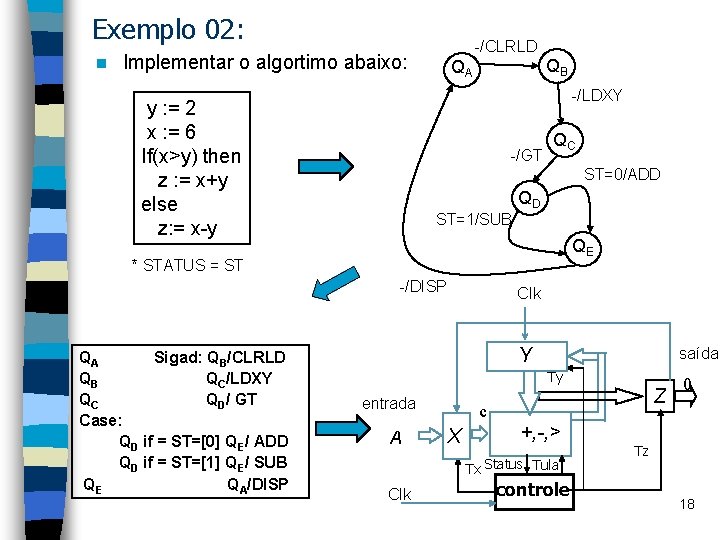

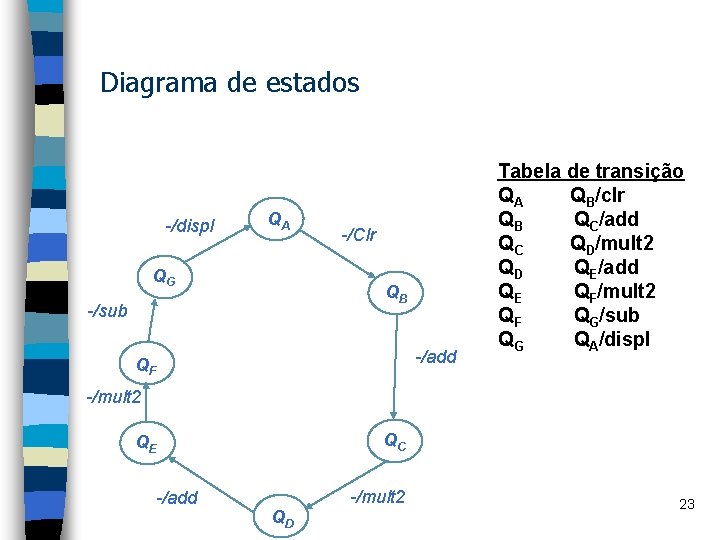

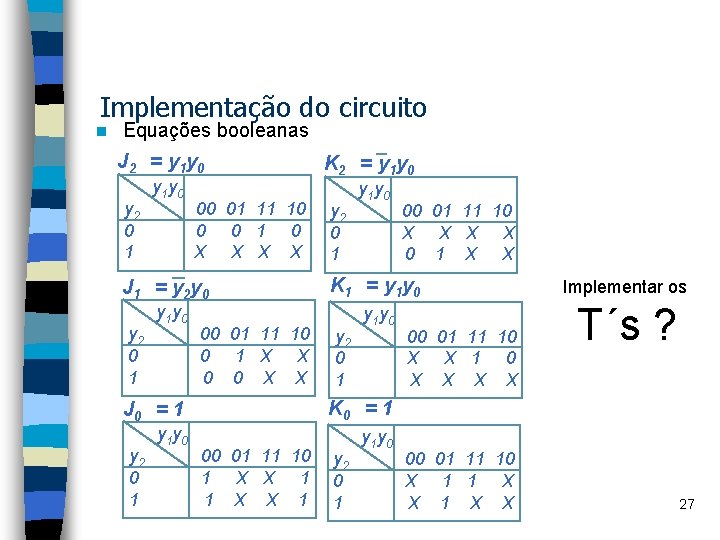

Exemplo 02: n -/CLRLD Implementar o algortimo abaixo: QB QA -/LDXY y : = 2 x : = 6 If(x>y) then z : = x+y else z: = x-y -/GT QC ST=0/ADD ST=1/SUB QD QE * STATUS = ST -/DISP QA Sigad: QB/CLRLD QB QC/LDXY QC QD/ GT Case: QD if = ST=[0] QE/ ADD QD if = ST=[1] QE/ SUB QE QA/DISP Clk Y saída Ty entrada A ab-c X +, -, > Tx Status Tula Clk Z controle 0 - Tz 18

![Clk QA Sigad QBCLRLD QB QCLDXY QC QD GT Case QD if STATUS0 Clk QA Sigad: QB/CLRLD QB QC/LDXY QC QD/ GT Case: QD if = STATUS=[0]](https://slidetodoc.com/presentation_image_h2/cdd98a705e7cddb8f1ec0383a7fdd306/image-19.jpg)

Clk QA Sigad: QB/CLRLD QB QC/LDXY QC QD/ GT Case: QD if = STATUS=[0] QF/ ADD QD if = STATUS=[1] QF/ SUB QE QA/DISP Y - entrada A saída Ty Z ab-c +, -, > X Tz Tx Status Tula controle Clk A=2 Y=X=Z=Ty=0 Tx=1 Tz=0 ST=x Tula=0 CLRLD QA Clk A=6 Y=0 X=2 Z=0 Ty=1 Tx=1 Tz=2 ST=x Tula=0 LDXY QB A=c Y=2 X=6 Z=0 Ty=2 Tx=2 Tz=2 ST=x Tula=2 GT QC A=Y=2 X=6 Z=0 Ty=1 Tx=2 Tz=2 ST=1 A=Y=6+2 X=Z=0 A=Y=X=Z=8 Ty=0 Tx=0 Tz=1 Tula =0 ADD DISP QD QE 0 - T Tula [0] = + [0] = clear [1] = - [1] = load [2] = > [2] = hold Instruções QA Ty, Tx, Tz Tula CLRLD = [ 0, 1, 0, x ] LDXY = [1, 1, 2, 0 ] ADD = [ 1, 1, 2, 0 ] SUB = [ 1, 1, 2, 1 ] DISP = [ 0, 0, 1, x ]

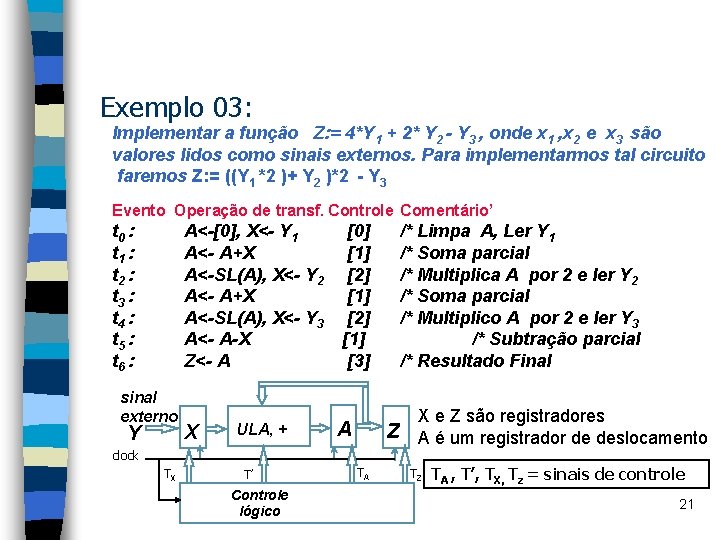

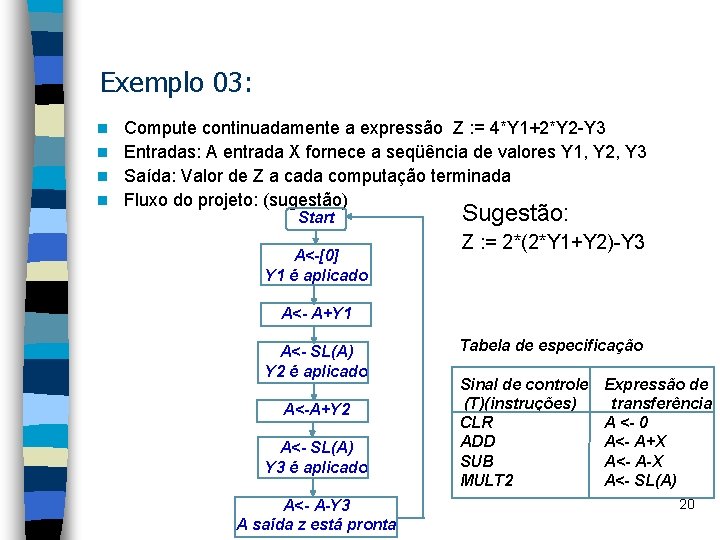

Exemplo 03: Compute continuadamente a expressão Z : = 4*Y 1+2*Y 2 -Y 3 n Entradas: A entrada X fornece a seqüência de valores Y 1, Y 2, Y 3 n Saída: Valor de Z a cada computação terminada n Fluxo do projeto: (sugestão) n Start A<-[0] Y 1 é aplicado Sugestão: Z : = 2*(2*Y 1+Y 2)-Y 3 A<- A+Y 1 A<- SL(A) Y 2 é aplicado A<-A+Y 2 A<- SL(A) Y 3 é aplicado A<- A-Y 3 A saída z está pronta Tabela de especificação Sinal de controle (T)(instruções) CLR ADD SUB MULT 2 Expressão de transferência A <- 0 A<- A+X A<- A-X A<- SL(A) 20

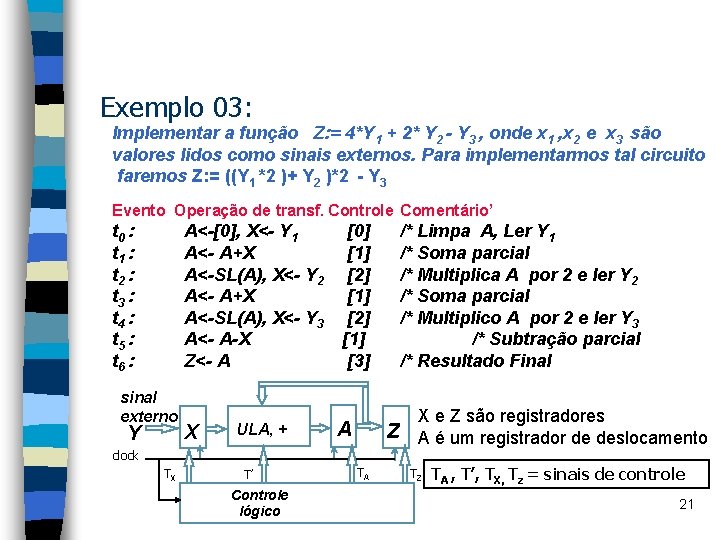

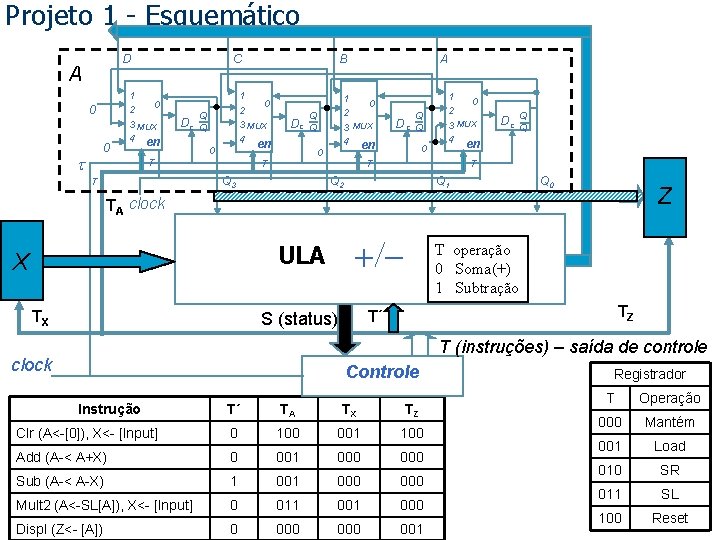

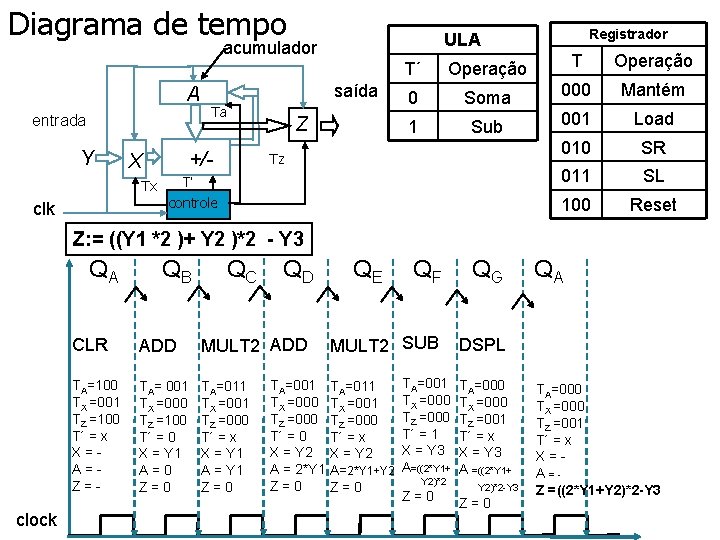

Exemplo 03: Implementar a função Z: = 4*Y 1 + 2* Y 2 - Y 3 , onde x 1 , x 2 e x 3 são valores lidos como sinais externos. Para implementarmos tal circuito faremos Z: = ((Y 1 *2 )+ Y 2 )*2 - Y 3 Evento Operação de transf. Controle Comentário’ t 0 : t 1 : t 2 : t 3 : t 4 : t 5 : t 6 : A<-[0], X<- Y 1 A<- A+X A<-SL(A), X<- Y 2 A<- A+X A<-SL(A), X<- Y 3 A<- A-X Z<- A sinal externo Y X ULA, + [0] [1] [2] [1] [3] A /* Limpa A, Ler Y 1 /* Soma parcial /* Multiplica A por 2 e ler Y 2 /* Soma parcial /* Multiplico A por 2 e ler Y 3 /* Subtração parcial /* Resultado Final Z X e Z são registradores A é um registrador de deslocamento clock TX T’ Controle lógico TA TZ TA , T’, TX, Tz = sinais de controle 21

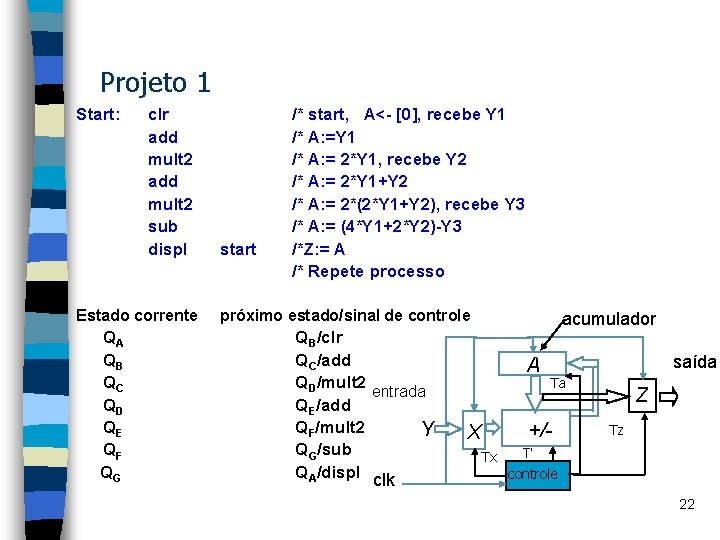

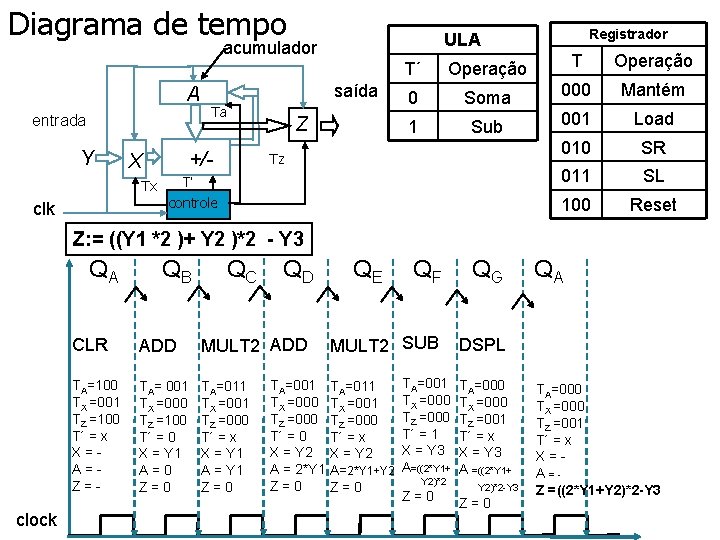

Projeto 1 Start: clr add mult 2 sub displ Estado corrente QA QB QC QD QE QF QG start /* start, A<- [0], recebe Y 1 /* A: = 2*Y 1, recebe Y 2 /* A: = 2*Y 1+Y 2 /* A: = 2*(2*Y 1+Y 2), recebe Y 3 /* A: = (4*Y 1+2*Y 2)-Y 3 /*Z: = A /* Repete processo próximo estado/sinal de controle QB/clr QC/add QD/mult 2 entrada QE/add QF/mult 2 Y QG/sub QA/displ clk acumulador A saída Ta +/- X Tx Z Tz T’ controle 22

Diagrama de estados -/displ QA QG -/Clr QB -/sub -/add QF Tabela de transição QA QB/clr QB QC/add QC QD/mult 2 QD QE/add QE QF/mult 2 QF QG/sub QG QA/displ -/mult 2 QC QE -/add -/mult 2 QD 23

Projeto 1 - Esquemático D A 0 0 t C 1 0 2 3 MUX 4 en B 1 0 2 3 MUX 4 Q Dc Q T Q 0 Q Dc. Q 0 1 0 2 3 MUX 4 en Dc Q Q T T T Q 3 T 1 0 2 3 MUX 4 en Dc Q en 0 A Q 2 Q 1 Q 0 Z TA clock X TX ULA +/- S (status) T´ T operação 0 Soma(+) 1 Subtração TZ T (instruções) – saída de controle clock Controle Instrução T´ TA TX TZ Clr (A<-[0]), X<- [Input] 0 100 001 100 Add (A-< A+X) 0 001 000 Sub (A-< A-X) 1 000 000 Mult 2 (A<-SL[A]), X<- [Input] 0 011 000 Displ (Z<- [A]) 0 000 001 Registrador T Operação 000 Mantém 001 Load 010 SR 011 SL 100 Reset

Diagrama de tempo acumulador A entrada Y saída Ta +/- X Z T´ Operação T Operação 0 Soma 000 Mantém 1 Sub 001 Load 010 SR 011 SL 100 Reset Tz T’ Tx controle clk Registrador ULA Z: = ((Y 1 *2 )+ Y 2 )*2 - Y 3 QA clock QB QC QD CLR ADD MULT 2 ADD TA=100 TX =001 TZ =100 T´ = x X=A=Z=- TA= 001 TX =000 TZ =100 T´ = 0 X = Y 1 A=0 Z=0 TA=011 TX =001 TZ =000 T´ = x X = Y 1 A = Y 1 Z=0 TA=001 TX =000 TZ =000 T´ = 0 X = Y 2 A = 2*Y 1 Z=0 QE QF QG MULT 2 SUB DSPL TA=011 TX =001 TZ =000 T´ = x X = Y 2 A=2*Y 1+Y 2 Z=0 TA=001 TX =000 TZ =000 T´ = 1 X = Y 3 A=((2*Y 1+ Y 2)*2 Z=0 TA=000 TX =000 TZ =001 T´ = x X = Y 3 A =((2*Y 1+ Y 2)*2 -Y 3 Z=0 QA TA=000 TX =000 TZ =001 T´ = x X=A =Z =((2*Y 1+Y 2)*2 -Y 3

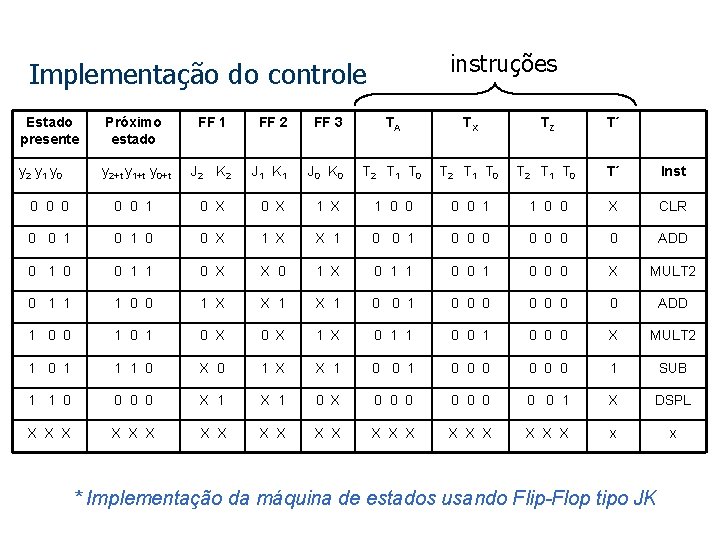

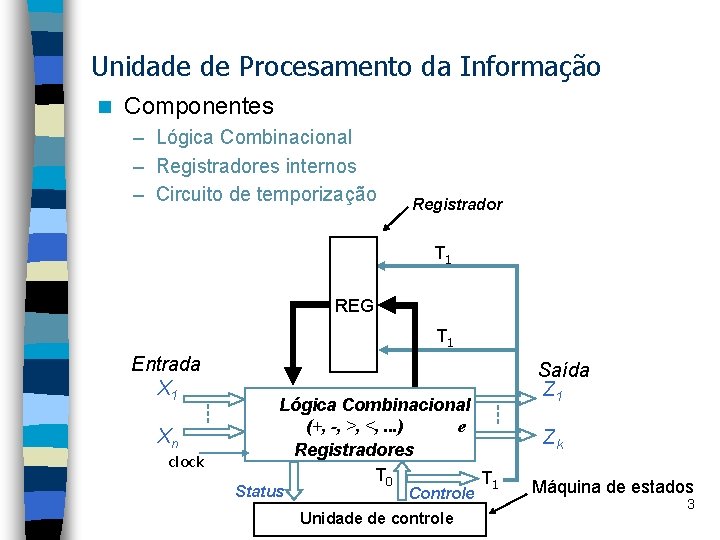

instruções Implementação do controle Estado presente Próximo estado FF 1 FF 2 FF 3 TA TX TZ T´ y 2 y 1 y 0 y 2+t y 1+t y 0+t J 2 K 2 J 1 K 1 J 0 K 0 T 2 T 1 T 0 T´ Inst 0 0 0 1 0 X 1 X 1 0 0 1 1 0 0 X CLR 0 0 1 0 0 X 1 X X 1 0 0 0 0 0 ADD 0 1 0 0 1 1 0 X X 0 1 1 0 0 0 X MULT 2 0 1 1 1 0 0 1 X X 1 0 0 0 0 ADD 1 0 0 1 0 X 1 X 0 1 1 0 0 0 X MULT 2 1 0 1 1 1 0 X 0 1 X X 1 0 0 0 0 1 SUB 1 1 0 0 X 1 0 X 0 0 0 0 1 X DSPL X X X X X X x x * Implementação da máquina de estados usando Flip-Flop tipo JK

Implementação do circuito n Equações booleanas J 2 = y 1 y 0 y 2 0 1 y 1 y 0 00 01 11 10 0 0 1 0 X X J 1 = y 2 y 0 y 2 0 1 y 1 y 0 00 01 11 10 0 1 X X 0 0 X X K 2 = y 1 y 0 y 2 0 1 y 1 y 0 K 1 = y 1 y 0 Implementar os y 1 y 0 T´s ? y 2 0 1 J 0 = 1 K 0 = 1 y 1 y 0 y 2 0 1 00 01 11 10 1 X X 1 00 01 11 10 X X 0 1 X X y 2 0 1 00 01 11 10 X X 1 0 X X 00 01 11 10 X 1 1 X X 27