Topics n Basics of registertransfer design data paths

Topics n Basics of register-transfer design: – data paths and controllers. n High-level synthesis. FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

Register-transfer design A register-transfer system is a sequential machine. n Register-transfer design is structural— complex combinations of state machines may not be easily described solely by a large state transition graph. n Register-transfer design concentrates on functionality, not details of logic design. n FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

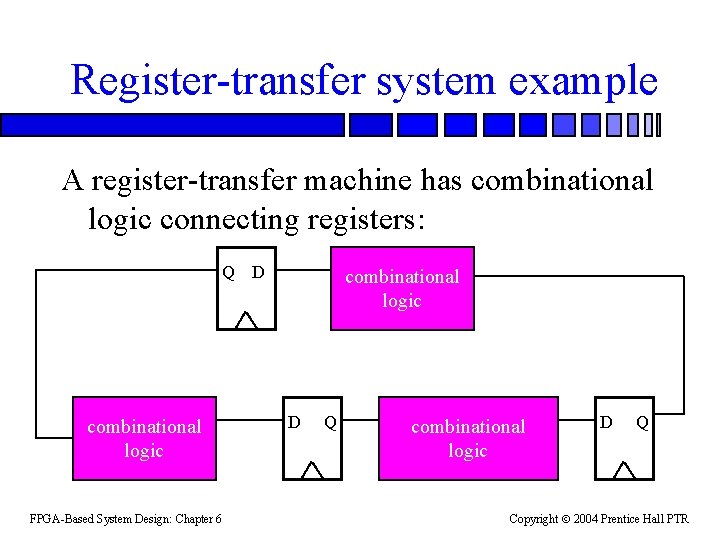

Register-transfer system example A register-transfer machine has combinational logic connecting registers: Q D combinational logic FPGA-Based System Design: Chapter 6 combinational logic D Q Copyright 2004 Prentice Hall PTR

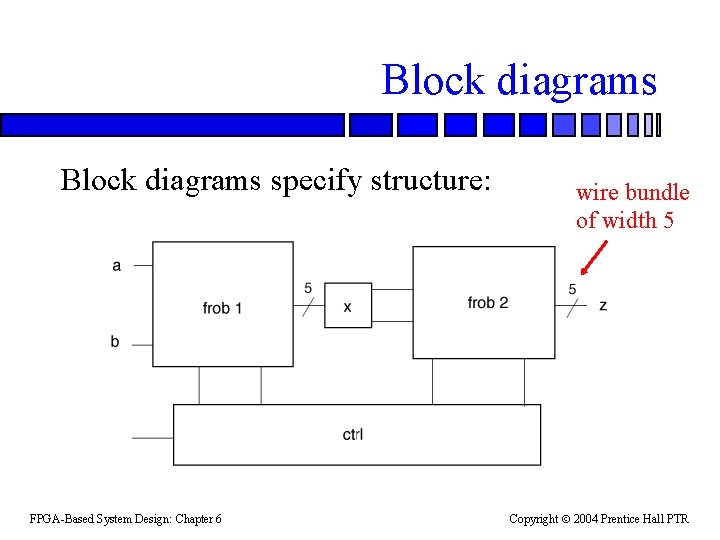

Block diagrams specify structure: FPGA-Based System Design: Chapter 6 wire bundle of width 5 Copyright 2004 Prentice Hall PTR

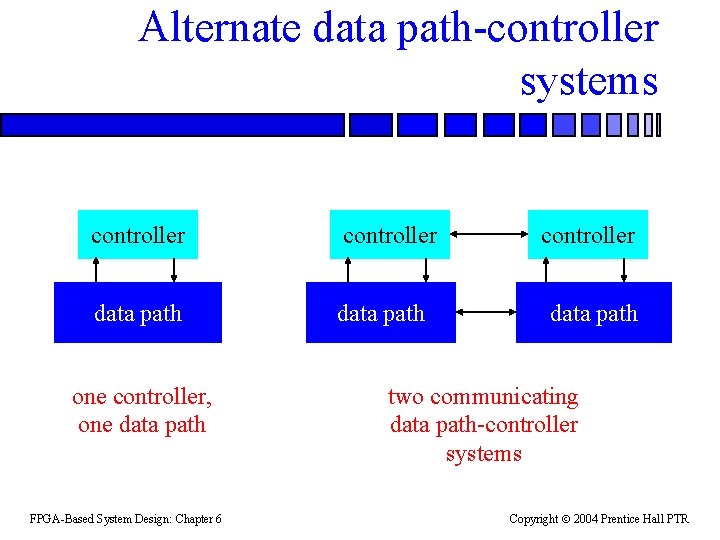

Data path-controller systems n One good way to structure a system is as a data path and a controller: – data path executes regular operations (arithmetic, etc. ), holds registers with dataoriented state; – controller evaluates irregular functions, sets control signals for data path. FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

Data and control are equivalent n We can rewrite control into data and visa versa: – control: if i 1 = ‘ 0’ then o 1 <= a; else o 1 <= b; end if; – data: o 1 <= ((i 1 = ‘ 0’) and a) or ((i 1 = ‘ 1’) and b); n Data/control distinction is useful but not fundamental. FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

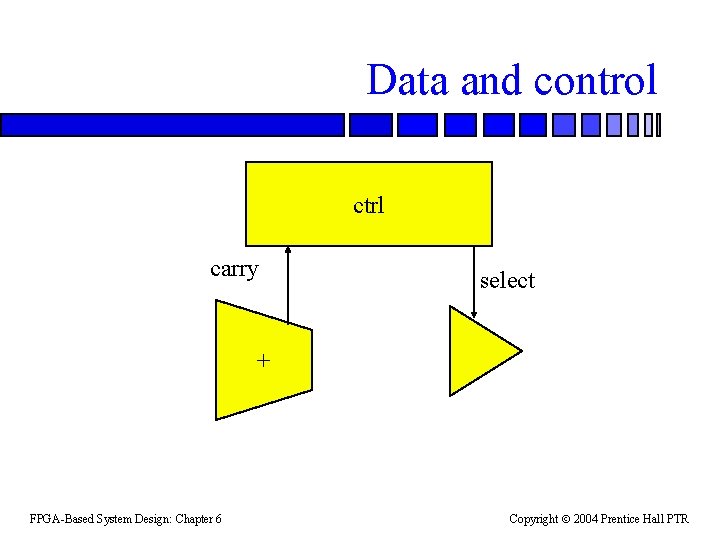

Data and control ctrl carry select + FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

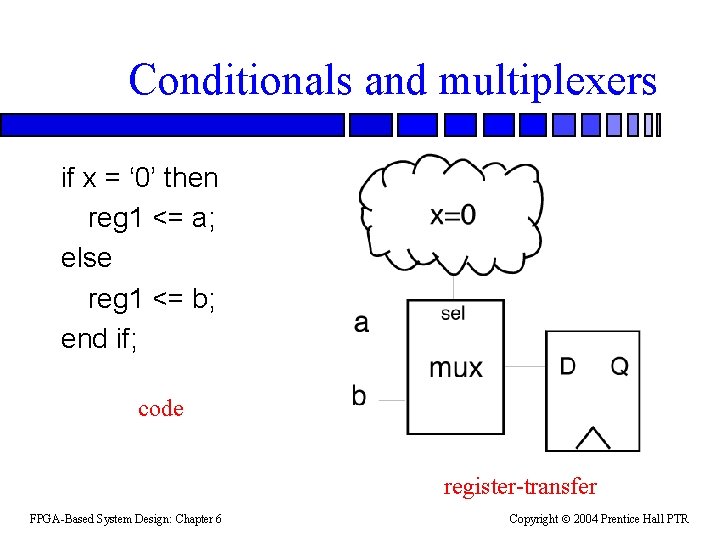

Data operators n Arithmetic operations are easy to spot in hardware description languages: – x <= a + b; Multiplexers are implied by conditionals. Must evaluate entire program to determine which sources of data for registers. n Multiplexers also come from sharing adders, etc. n FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

Conditionals and multiplexers if x = ‘ 0’ then reg 1 <= a; else reg 1 <= b; end if; code register-transfer FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

Alternate data path-controller systems controller data path one controller, one data path FPGA-Based System Design: Chapter 6 controller data path two communicating data path-controller systems Copyright 2004 Prentice Hall PTR

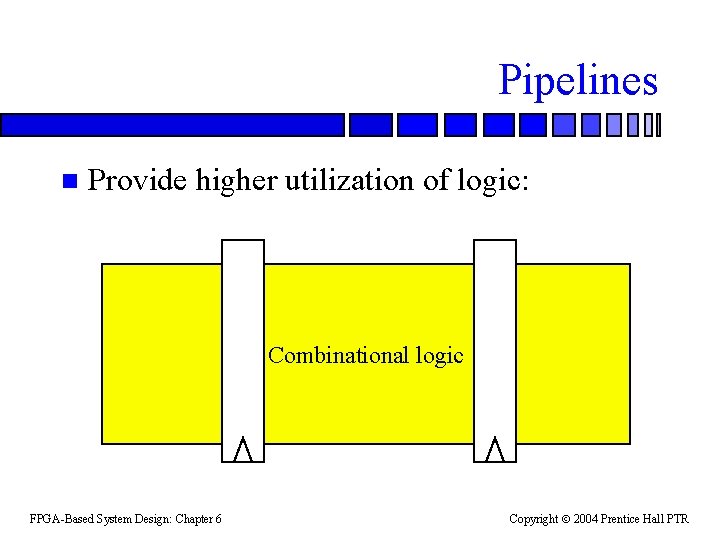

Pipelines n Provide higher utilization of logic: Combinational logic FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

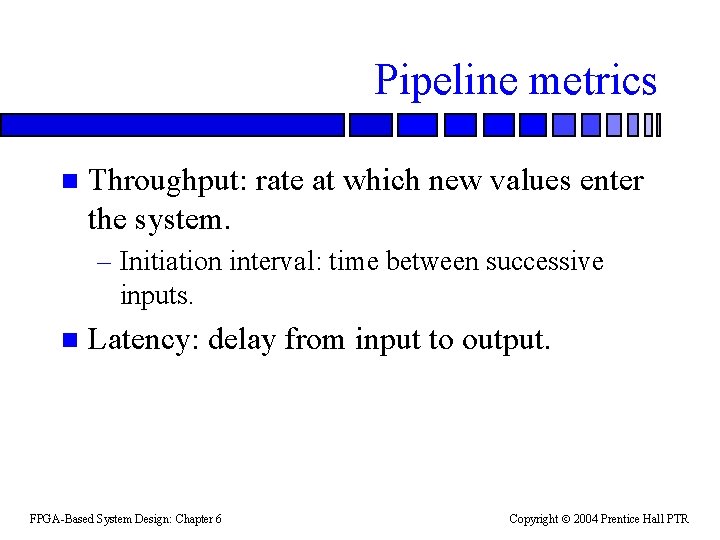

Pipeline metrics n Throughput: rate at which new values enter the system. – Initiation interval: time between successive inputs. n Latency: delay from input to output. FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

Simple pipelines Pure pipelines have no control. n Choose latency, throughput. n Choose register locations with retiming. n Overhead: n – Setup, hold times. – Power. FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

Complex pipelines Actions in pipeline depend on data or external events. n Actions on pipe: n – Stall values. – Abort operation. – Bypass values. FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

High-level synthesis Sequential operation is not the most abstract description of behavior. n We can describe behavior without assigning operations to particular clock cycles. n High-level synthesis (behavioral synthesis) transforms an unscheduled behavior into a register-transfer behavior. n FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

Tasks in high-level synthesis Scheduling: determines clock cycle on which each operation will occur. n Allocation: chooses which function units will execute which operations. n FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

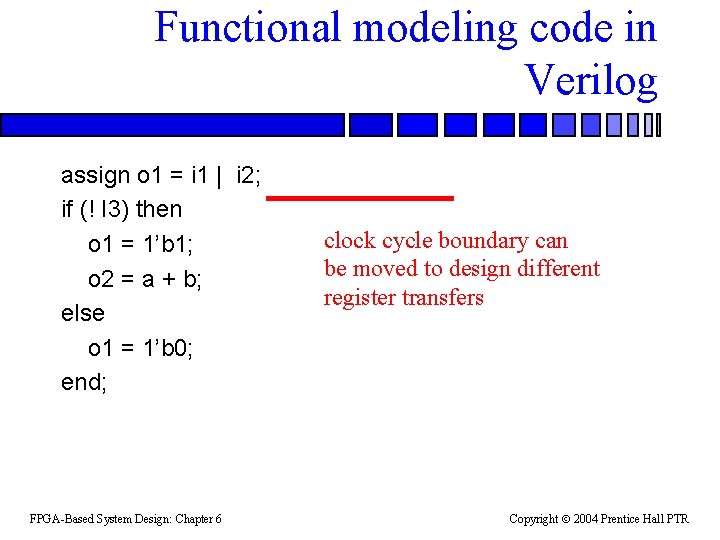

Functional modeling code in Verilog assign o 1 = i 1 | i 2; if (! I 3) then o 1 = 1’b 1; o 2 = a + b; else o 1 = 1’b 0; end; FPGA-Based System Design: Chapter 6 clock cycle boundary can be moved to design different register transfers Copyright 2004 Prentice Hall PTR

Data dependencies n Data dependencies describe relationships between operations: – x <= a + b; value of x depends on a, b n High-level synthesis must preserve data dependencies. FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

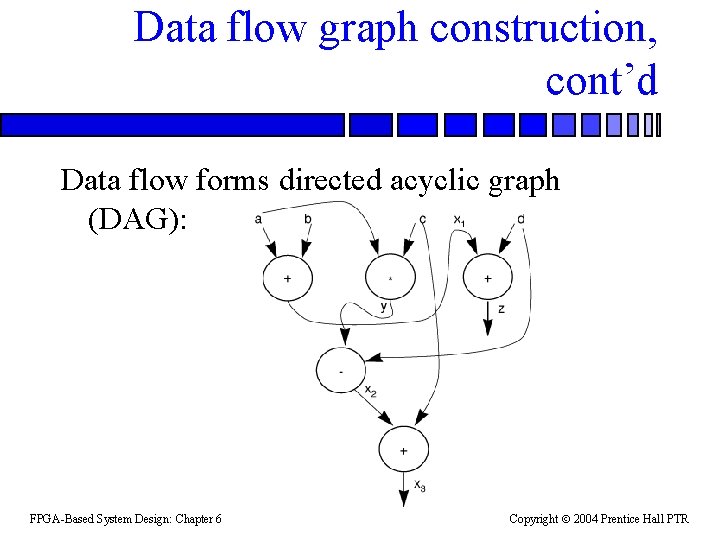

Data flow graph (DFG) models data dependencies. n Does not require that operations be performed in a particular order. n Models operations in a basic block of a functional model—no conditionals. n Requires single-assignment form. n FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

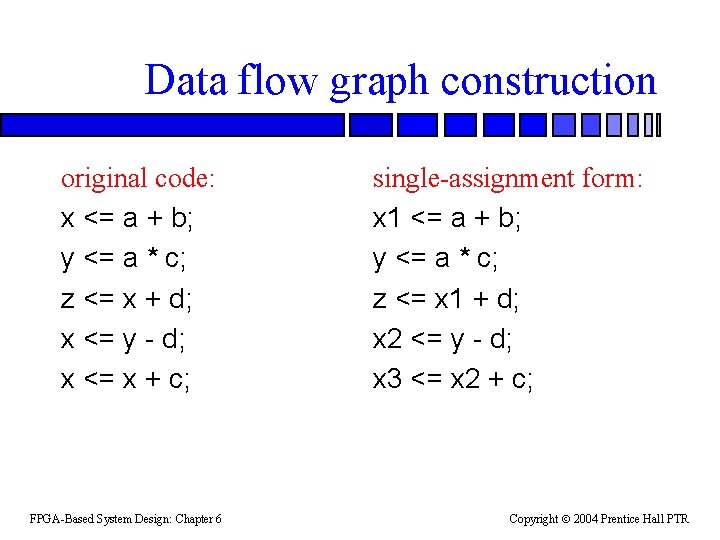

Data flow graph construction original code: x <= a + b; y <= a * c; z <= x + d; x <= y - d; x <= x + c; FPGA-Based System Design: Chapter 6 single-assignment form: x 1 <= a + b; y <= a * c; z <= x 1 + d; x 2 <= y - d; x 3 <= x 2 + c; Copyright 2004 Prentice Hall PTR

Data flow graph construction, cont’d Data flow forms directed acyclic graph (DAG): FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

Goals of scheduling and allocation Preserve behavior—at end of execution, should have received all outputs, be in proper state (ignoring exact times of events). n Utilize hardware efficiently. n Obtain acceptable performance. n FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

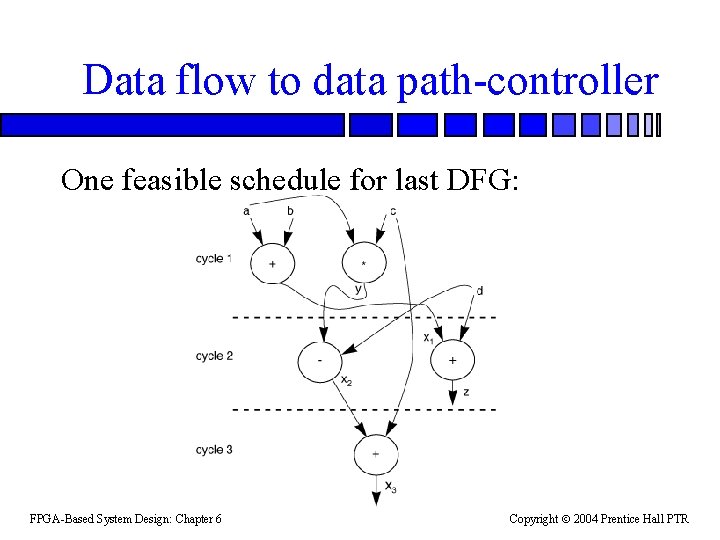

Data flow to data path-controller One feasible schedule for last DFG: FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

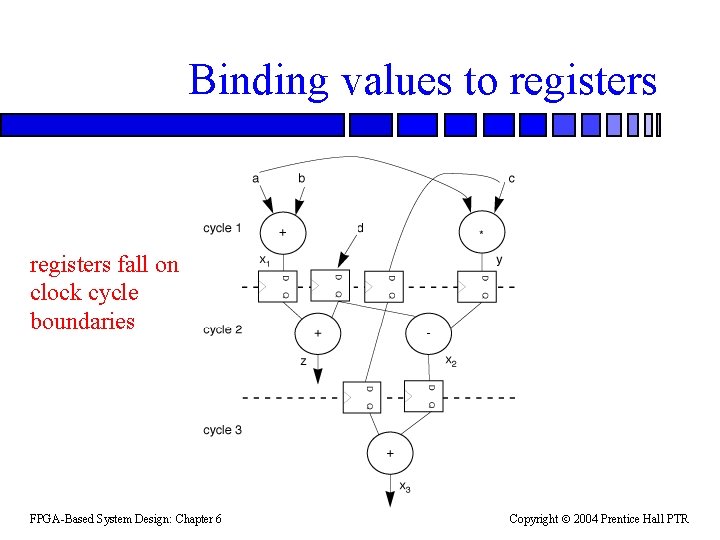

Binding values to registers fall on clock cycle boundaries FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

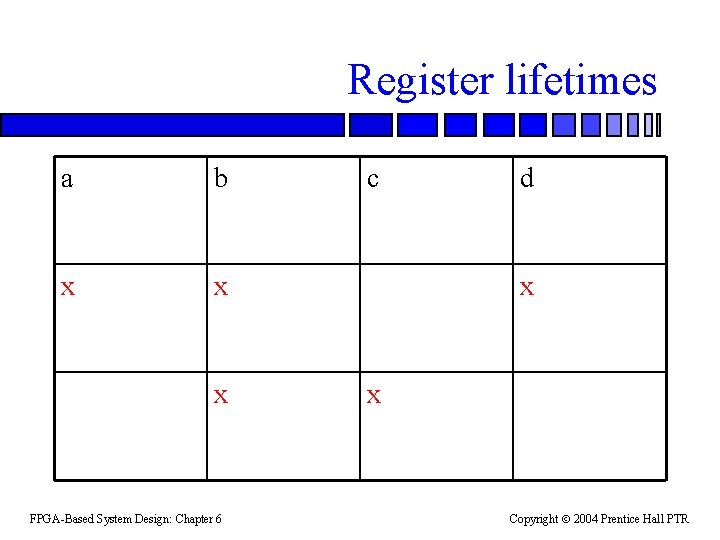

Register lifetimes a b x x x FPGA-Based System Design: Chapter 6 c d x x Copyright 2004 Prentice Hall PTR

Allocation creates multiplexers n Same unit used for different values at different times. – Function units. – Registers. n Multiplexer controls which value has access to the unit. FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

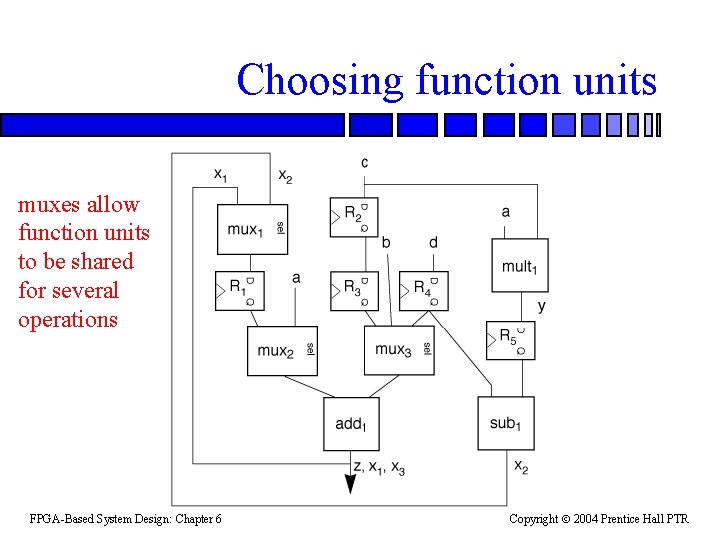

Choosing function units muxes allow function units to be shared for several operations FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

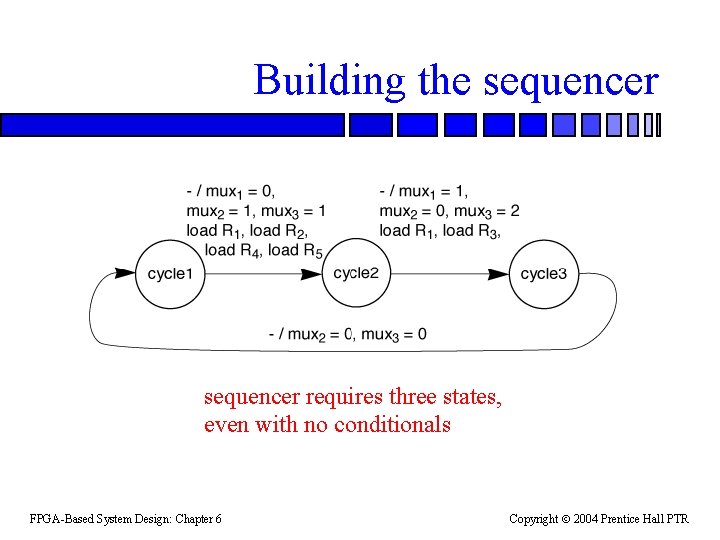

Building the sequencer requires three states, even with no conditionals FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

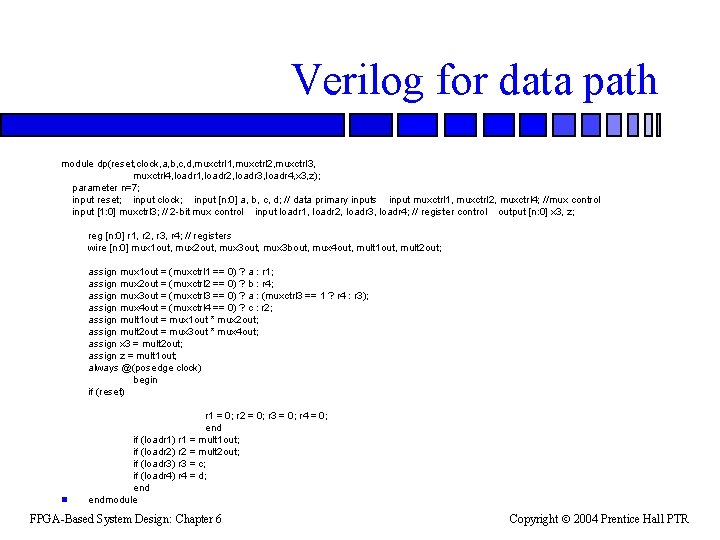

Verilog for data path module dp(reset, clock, a, b, c, d, muxctrl 1, muxctrl 2, muxctrl 3, muxctrl 4, loadr 1, loadr 2, loadr 3, loadr 4, x 3, z); parameter n=7; input reset; input clock; input [n: 0] a, b, c, d; // data primary inputs input muxctrl 1, muxctrl 2, muxctrl 4; // mux control input [1: 0] muxctrl 3; // 2 -bit mux control input loadr 1, loadr 2, loadr 3, loadr 4; // register control output [n: 0] x 3, z; reg [n: 0] r 1, r 2, r 3, r 4; // registers wire [n: 0] mux 1 out, mux 2 out, mux 3 bout, mux 4 out, mult 1 out, mult 2 out; assign mux 1 out = (muxctrl 1 == 0) ? a : r 1; assign mux 2 out = (muxctrl 2 == 0) ? b : r 4; assign mux 3 out = (muxctrl 3 == 0) ? a : (muxctrl 3 == 1 ? r 4 : r 3); assign mux 4 out = (muxctrl 4 == 0) ? c : r 2; assign mult 1 out = mux 1 out * mux 2 out; assign mult 2 out = mux 3 out * mux 4 out; assign x 3 = mult 2 out; assign z = mult 1 out; always @(posedge clock) begin if (reset) n r 1 = 0; r 2 = 0; r 3 = 0; r 4 = 0; end if (loadr 1) r 1 = mult 1 out; if (loadr 2) r 2 = mult 2 out; if (loadr 3) r 3 = c; if (loadr 4) r 4 = d; endmodule FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

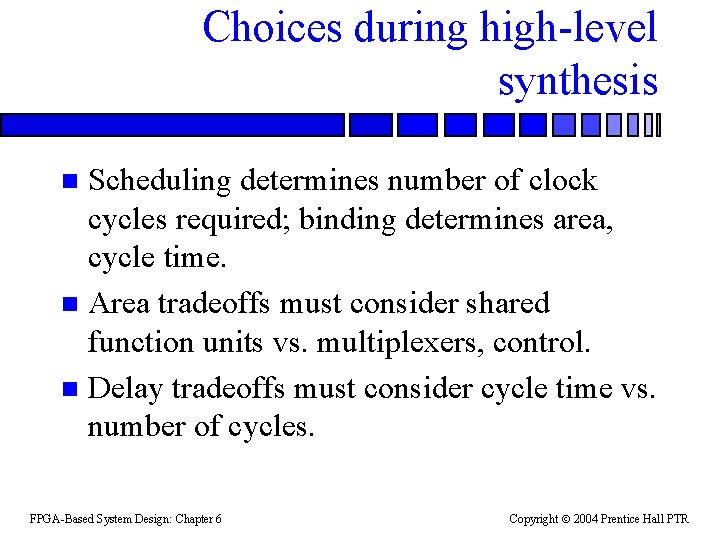

Choices during high-level synthesis Scheduling determines number of clock cycles required; binding determines area, cycle time. n Area tradeoffs must consider shared function units vs. multiplexers, control. n Delay tradeoffs must consider cycle time vs. number of cycles. n FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

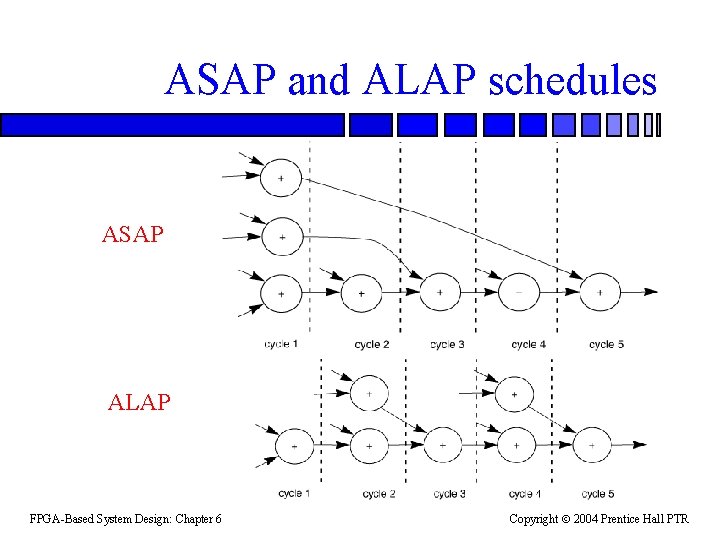

Finding schedules n Two simple schedules: – As-soon-as-possible (ASAP) schedule puts every operation as early in time as possible. – As-late-as-possible (ALAP) schedule puts every operation as late in schedule as possible. n Many schedules exist between ALAP and ASAP extremes. FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

ASAP and ALAP schedules ASAP ALAP FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

![Verilog model of ASAP schedule reg [n-1: 0] w 1 reg, w 2 reg, Verilog model of ASAP schedule reg [n-1: 0] w 1 reg, w 2 reg,](http://slidetodoc.com/presentation_image/ee99e8130552401017b349e1625aec45/image-33.jpg)

Verilog model of ASAP schedule reg [n-1: 0] w 1 reg, w 2 reg, w 6 reg 1, w 6 reg 2, w 6 reg 3, w 6 reg 4, w 3 reg 1, w 3 reg 2, w 4 reg, w 5 reg; always @(posedge clock) begin // cycle 1 w 1 reg = i 1 + i 2; w 3 reg 1 = i 4 + i 5; w 6 reg 1 = i 7 + i 8; // cycle 2 w 2 reg = w 1 reg + i 3; w 3 reg 2 = w 3 reg 1; w 6 reg 2 = w 6 reg 1; // cycle 3 w 4 reg = w 3 reg 2 + w 2 reg; w 6 reg 3 = w 6 reg 2; // cycle 4 w 5 reg = i 6 + w 4 reg; w 6 reg 4 = w 6 reg 3; // cycle 5 o 1 = w 6 reg 4 + w 5 reg; end FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

![Verilog of ALAP schedule reg [n-1: 0] w 1 reg, w 2 reg, w Verilog of ALAP schedule reg [n-1: 0] w 1 reg, w 2 reg, w](http://slidetodoc.com/presentation_image/ee99e8130552401017b349e1625aec45/image-34.jpg)

Verilog of ALAP schedule reg [n-1: 0] w 1 reg, w 2 reg, w 6 reg 2, w 6 reg 3, w 3 reg, w 4 reg, w 5 reg; always @(posedge clock) begin // cycle 1 w 1 reg = i 1 + i 2; // cycle 2 w 2 reg = w 1 reg + i 3; w 3 reg = i 4 + i 5; // cycle 3 w 4 reg = w 3 reg + w 2 reg; w 6 reg 3 = w 6 reg 2; // cycle 4 w 5 reg = i 6 + w 4 reg; w 6 reg = i 7 + i 8; // cycle 5 o 1 = w 6 reg + w 5 reg; end FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

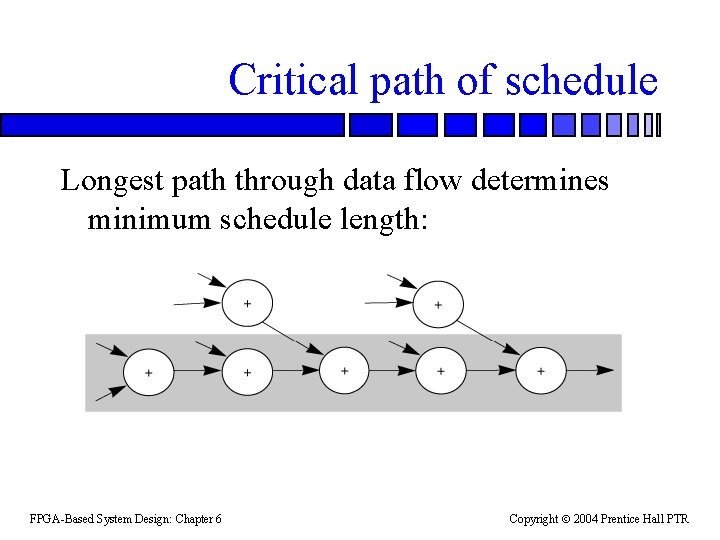

Critical path of schedule Longest path through data flow determines minimum schedule length: FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

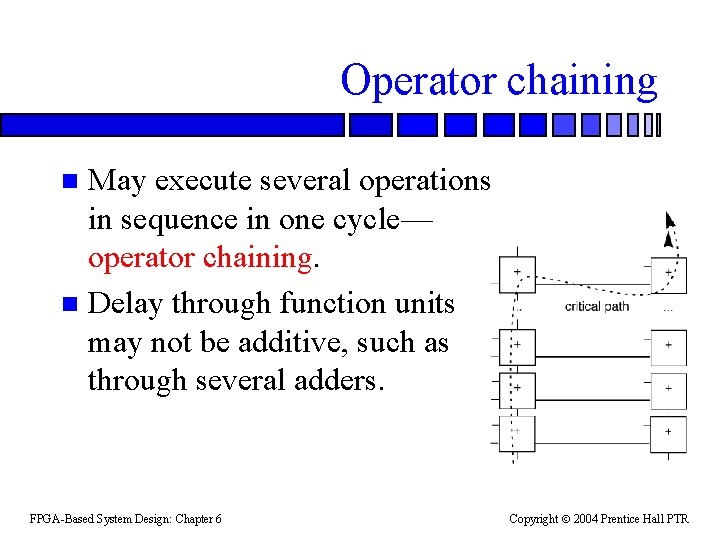

Operator chaining May execute several operations in sequence in one cycle— operator chaining. n Delay through function units may not be additive, such as through several adders. n FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

Control implementation Clock cycles are also known as control steps. n Longer schedule means more states in controller. n Cost of controller may be hard to judge from casual inspection of state transition graph. n FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

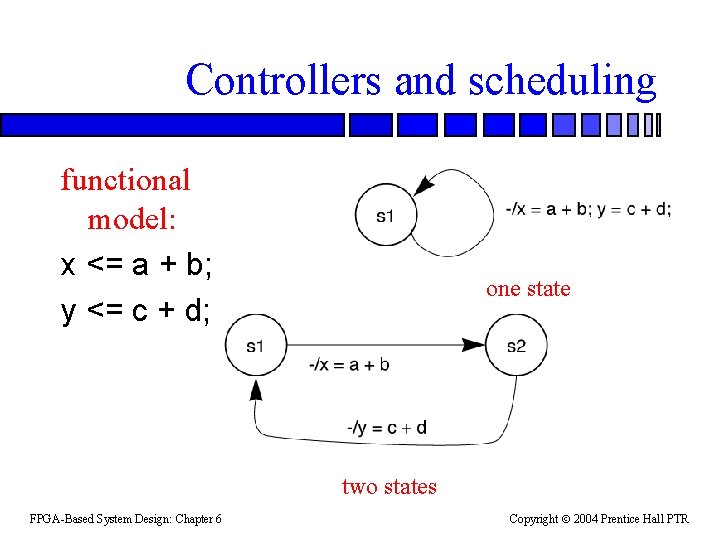

Controllers and scheduling functional model: x <= a + b; y <= c + d; one state two states FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

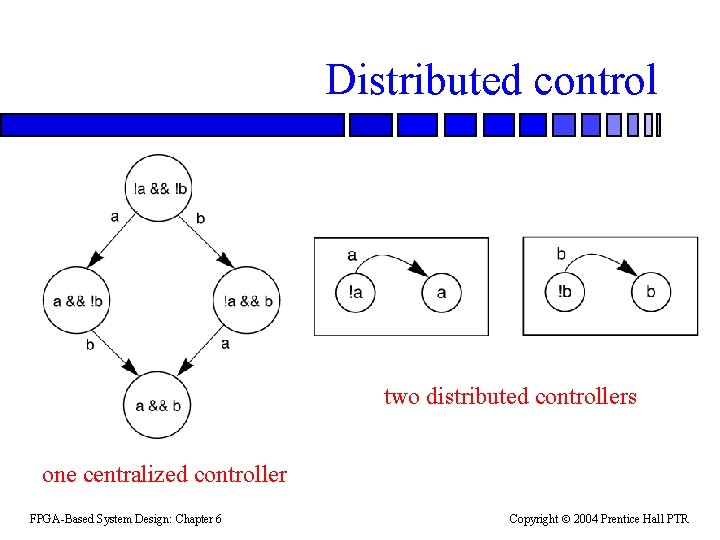

Distributed control two distributed controllers one centralized controller FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

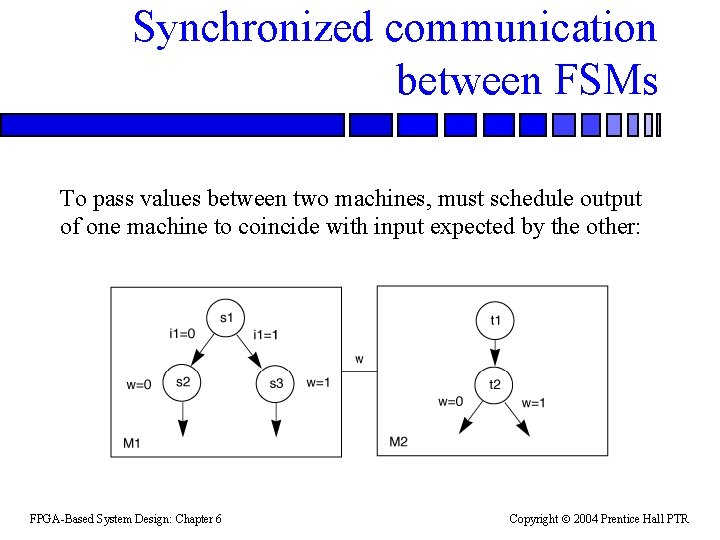

Synchronized communication between FSMs To pass values between two machines, must schedule output of one machine to coincide with input expected by the other: FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

Hardwired vs. microcoded control Hardwired control has a state register and “random logic. ” n A microcoded machine has a state register which points into a microcode memory. n Styles are equivalent; choice depends on implementation considerations. n FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

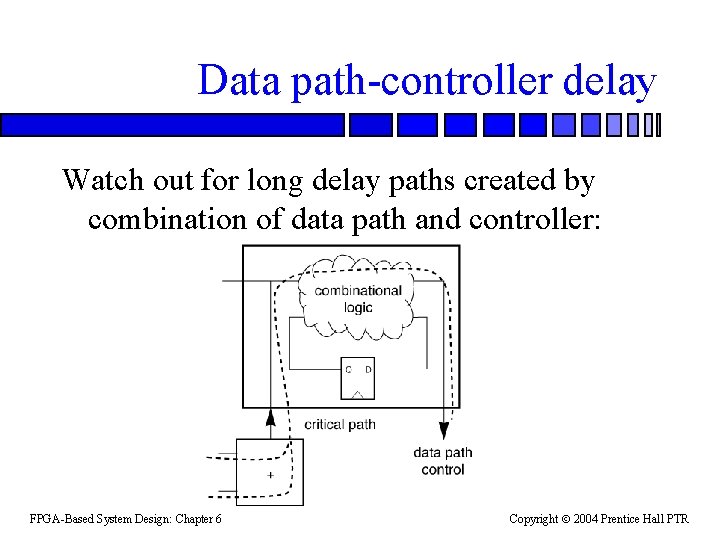

Data path-controller delay Watch out for long delay paths created by combination of data path and controller: FPGA-Based System Design: Chapter 6 Copyright 2004 Prentice Hall PTR

- Slides: 42