Power Supply Controller Architecture Yuke Tian Control Group

- Slides: 26

Power Supply Controller Architecture Yuke Tian Control Group, Accelerator Division Photon Science Directory Brookhaven National Lab EPICS Collaboration Meeting, BNL, 2010

Outline 1. NSLS-II power supply control system System overview Current regulator Power supply interface (PSI) Power supply controller (PSC) 2. NSLS-II power supply controller architecture PSC system architecture Diagnostics with DDR 2 100 Mbps serial device link Embedded microblaze Interface with PSI Remote reprogram capability 3. Progress 4. Summary EPICS Collaboration Meeting, BNL, 2010

NSLS-II power supply control system — System overview Magnets and Power Supplies in Storage Ring EPICS Collaboration Meeting, BNL, 2010

NSLS-II power supply control system — System overview • Provide 3. 8 ppm current resolution and less than 25 ppm long term stability. • Flexible setpoint for one power supply or synchronous setpoints for a group power supplies. • 10 KHz fast orbit correction operation. • Up to 10 Hz slow orbit correction operation. • Detect and set machine protection errors in 2 ms. • Build-in power supply ripple detections. • At least 10 seconds circular buffer to transient waveform recorder. • Provide at lease 1 second Booster PS synchronous ramping function. EPICS Collaboration Meeting, BNL, 2010

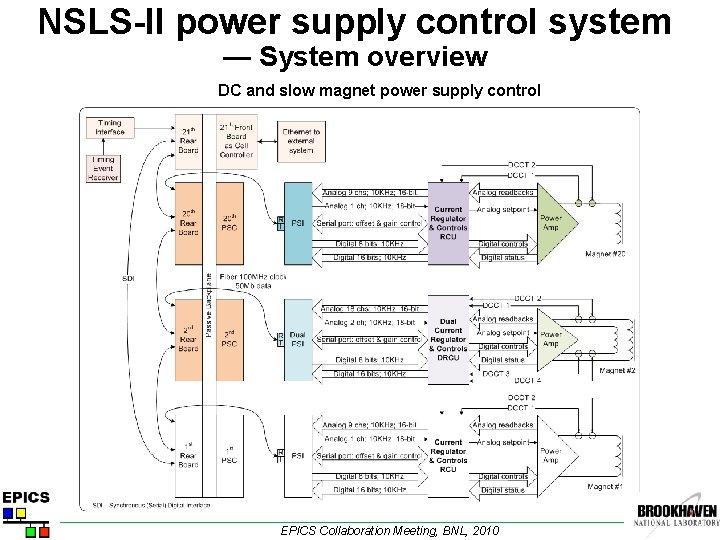

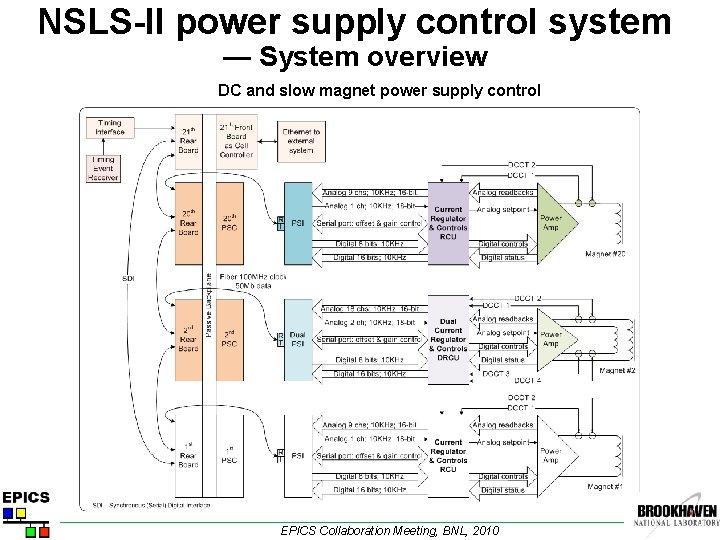

NSLS-II power supply control system — System overview DC and slow magnet power supply control EPICS Collaboration Meeting, BNL, 2010

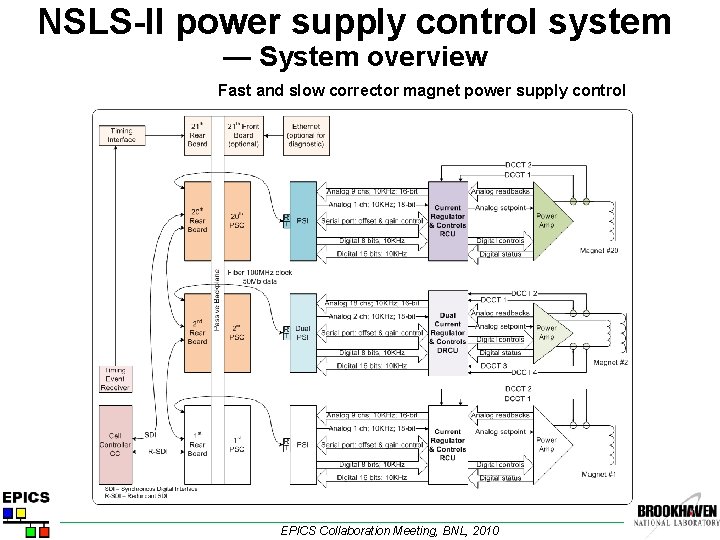

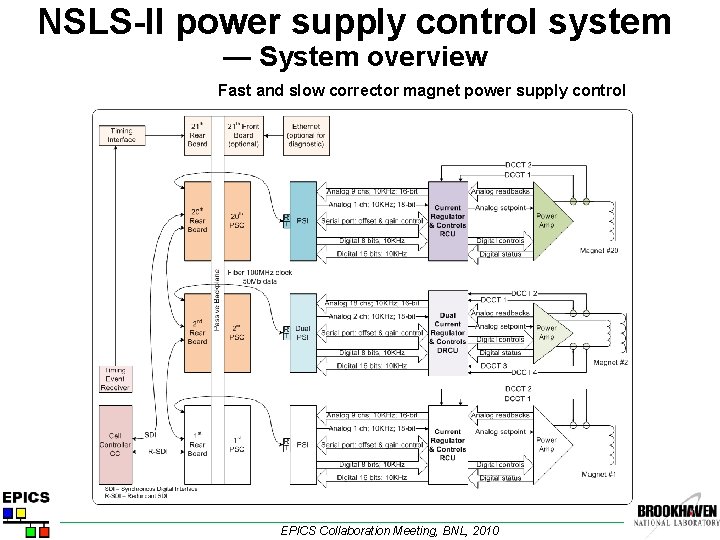

NSLS-II power supply control system — System overview Fast and slow corrector magnet power supply control EPICS Collaboration Meeting, BNL, 2010

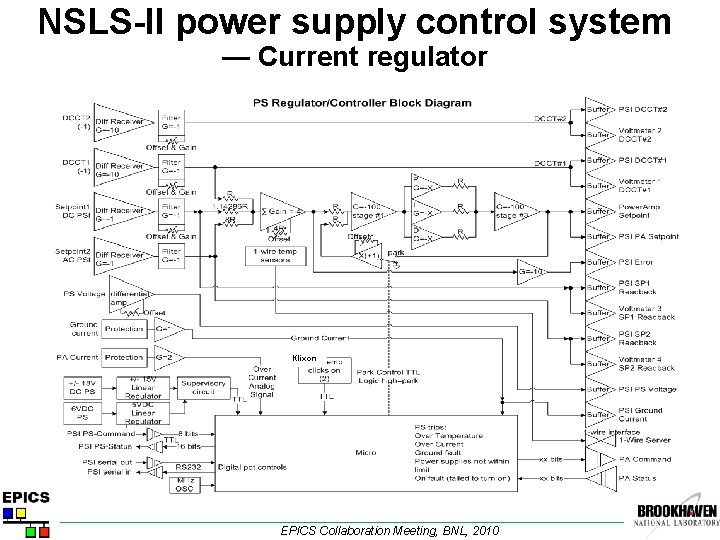

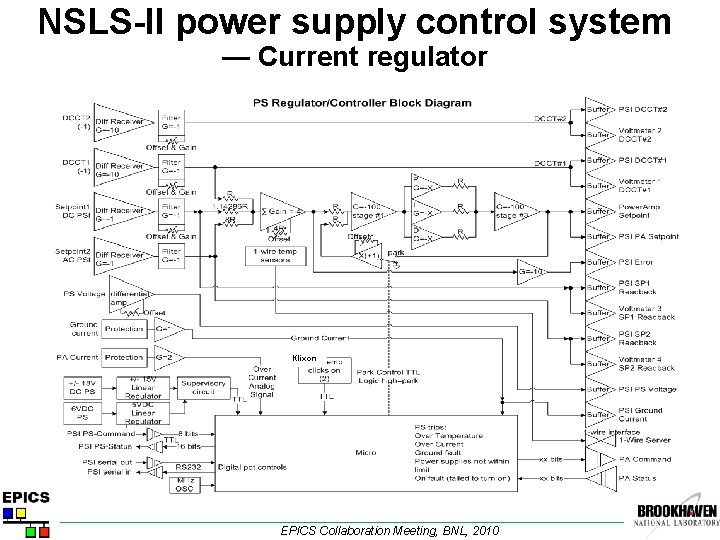

NSLS-II power supply control system — Current regulator Klixon EPICS Collaboration Meeting, BNL, 2010

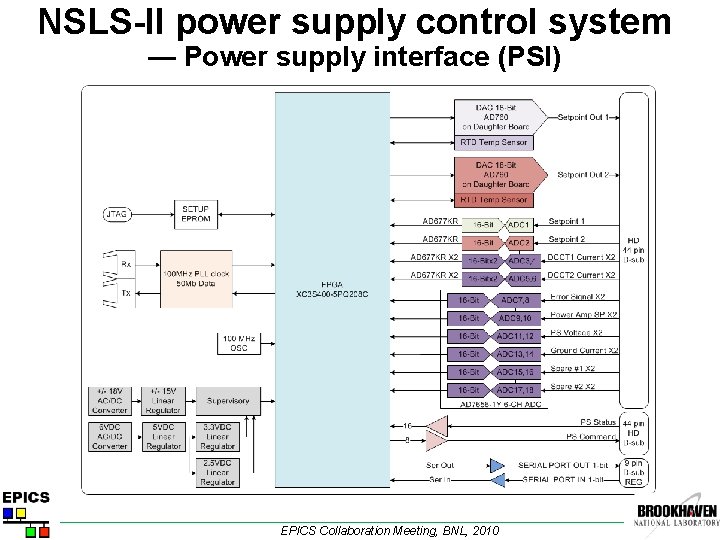

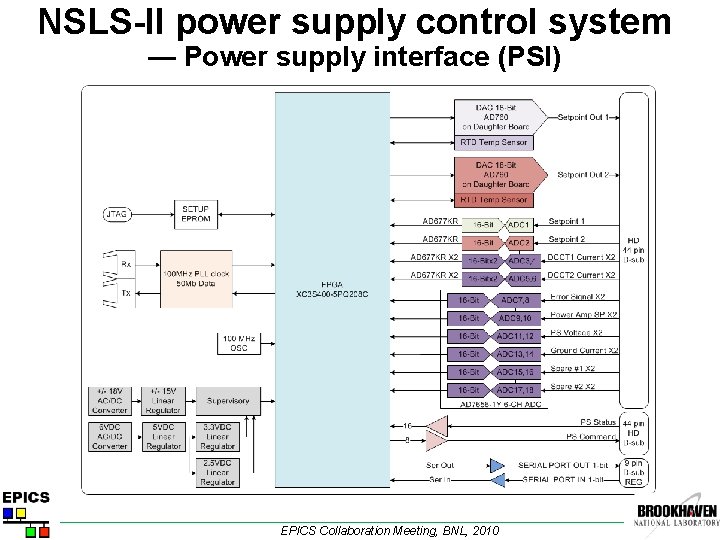

NSLS-II power supply control system — Power supply interface (PSI) EPICS Collaboration Meeting, BNL, 2010

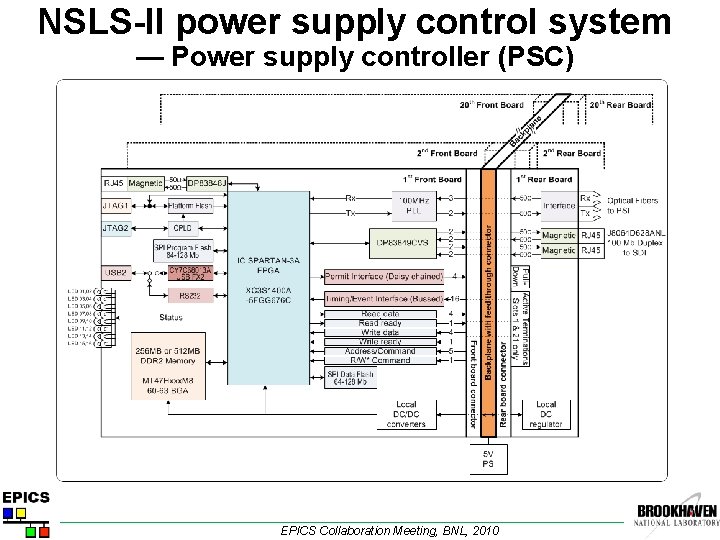

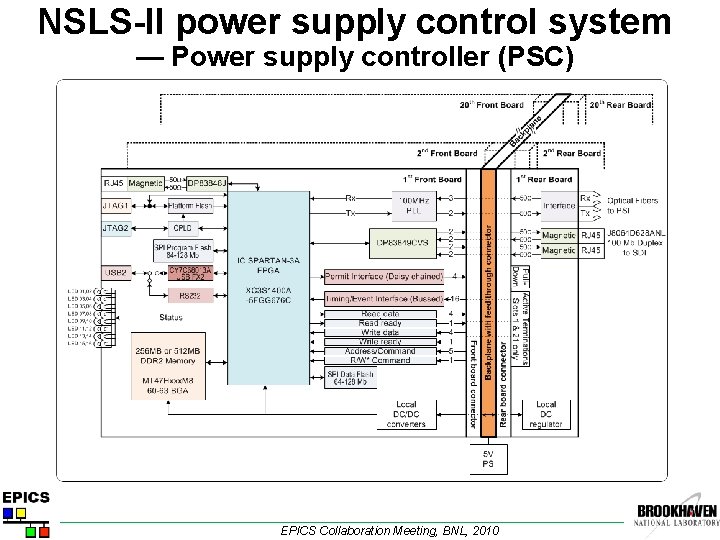

NSLS-II power supply control system — Power supply controller (PSC) EPICS Collaboration Meeting, BNL, 2010

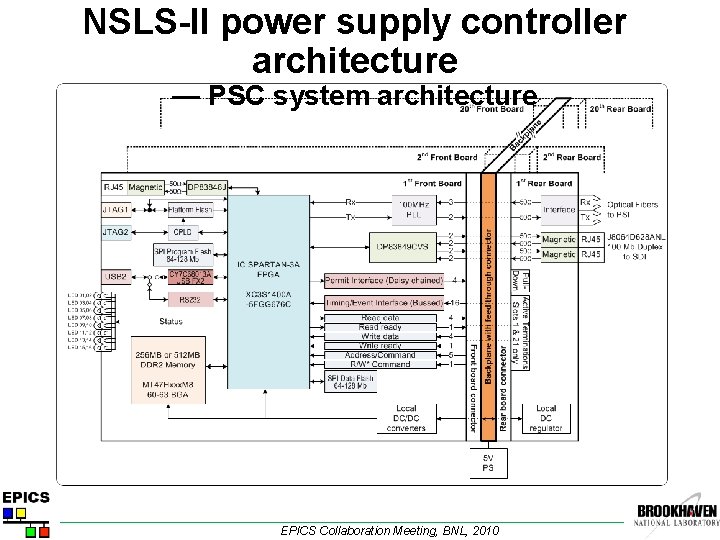

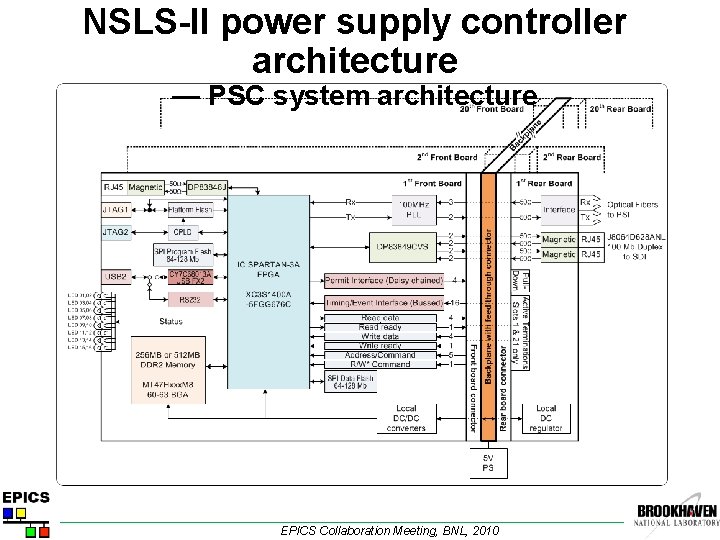

NSLS-II power supply controller architecture — PSC system architecture EPICS Collaboration Meeting, BNL, 2010

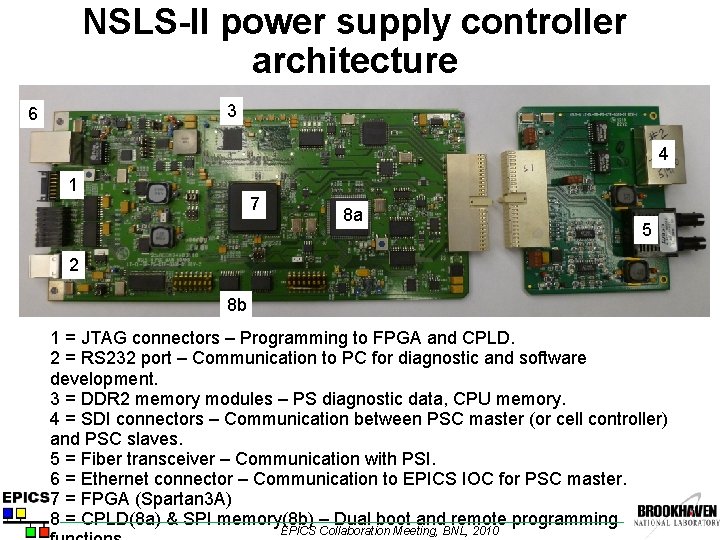

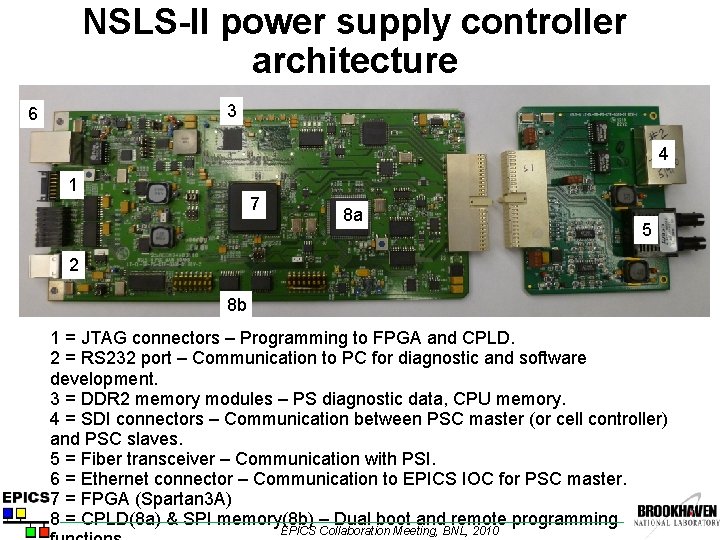

NSLS-II power supply controller architecture — PSC system architecture 3 6 4 1 7 7 a 8 a 5 2 8 b 1 = JTAG connectors – Programming to FPGA and CPLD. 2 = RS 232 port – Communication to PC for diagnostic and software development. 3 = DDR 2 memory modules – PS diagnostic data, CPU memory. 4 = SDI connectors – Communication between PSC master (or cell controller) and PSC slaves. 5 = Fiber transceiver – Communication with PSI. 6 = Ethernet connector – Communication to EPICS IOC for PSC master. 7 = FPGA (Spartan 3 A) 8 = CPLD(8 a) & SPI memory(8 b) – Dual boot and remote programming EPICS Collaboration Meeting, BNL, 2010

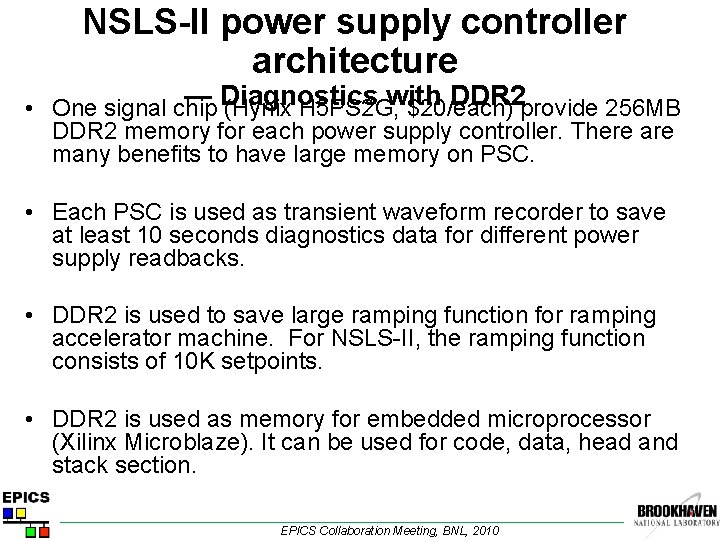

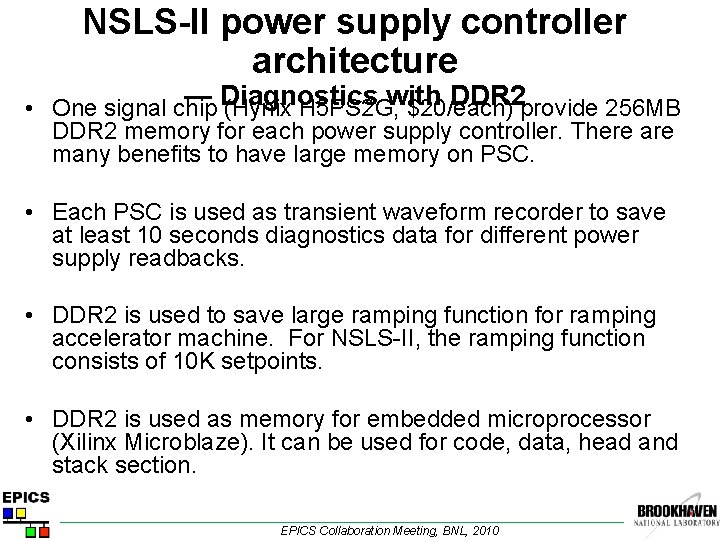

NSLS-II power supply controller architecture — Diagnostics with DDR 2 provide 256 MB • One signal chip (Hynix H 5 PS 2 G, $20/each) DDR 2 memory for each power supply controller. There are many benefits to have large memory on PSC. • Each PSC is used as transient waveform recorder to save at least 10 seconds diagnostics data for different power supply readbacks. • DDR 2 is used to save large ramping function for ramping accelerator machine. For NSLS-II, the ramping function consists of 10 K setpoints. • DDR 2 is used as memory for embedded microprocessor (Xilinx Microblaze). It can be used for code, data, head and stack section. EPICS Collaboration Meeting, BNL, 2010

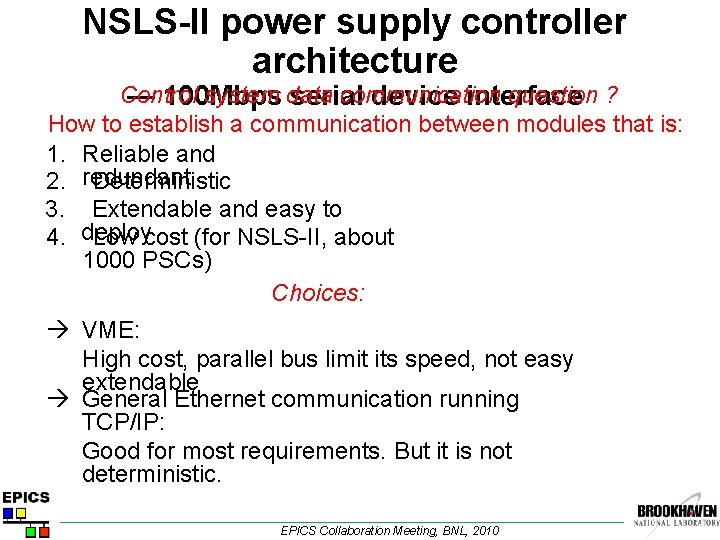

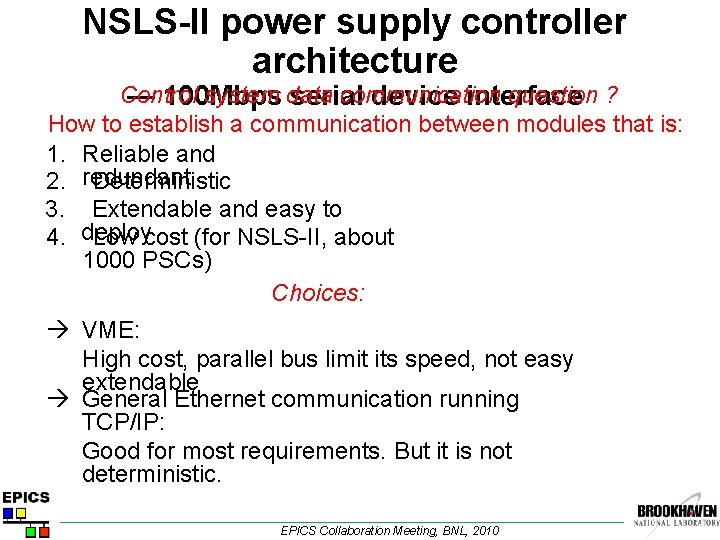

NSLS-II power supply controller architecture Control system data communication question ? — 100 Mbps serial device interface How to establish a communication between modules that is: 1. Reliable and 2. redundant Deterministic 3. Extendable and easy to 4. deploy Low cost (for NSLS-II, about 1000 PSCs) Choices: à VME: High cost, parallel bus limit its speed, not easy extendable à General Ethernet communication running TCP/IP: Good for most requirements. But it is not deterministic. EPICS Collaboration Meeting, BNL, 2010

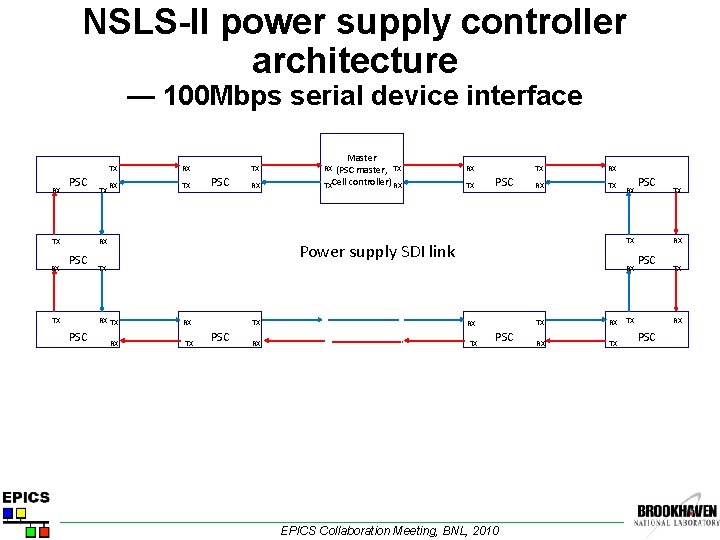

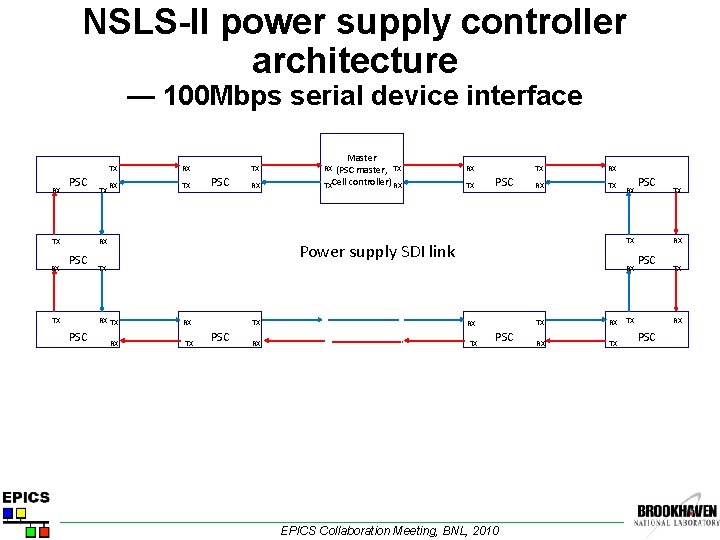

NSLS-II power supply controller architecture — 100 Mbps serial device interface RX PSC TX RX TX TX RX RX TX TX PSC RX RX PSC TX PSC Master (PSC master, TX TXCell controller) RX RX RX TX PSC TX RX RX TX Power supply SDI link TX RX RX TX PSC EPICS Collaboration Meeting, BNL, 2010 TX RX RX TX TX RX PSC

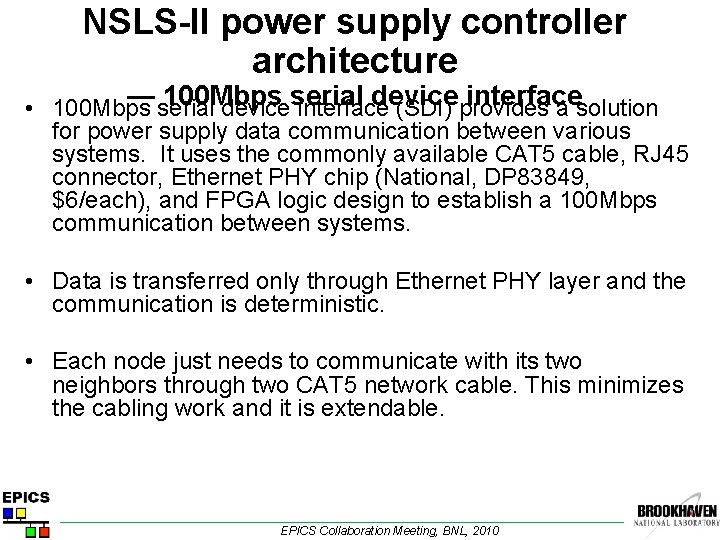

NSLS-II power supply controller architecture — serial 100 Mbps device interface • 100 Mbps deviceserial interface (SDI) provides a solution for power supply data communication between various systems. It uses the commonly available CAT 5 cable, RJ 45 connector, Ethernet PHY chip (National, DP 83849, $6/each), and FPGA logic design to establish a 100 Mbps communication between systems. • Data is transferred only through Ethernet PHY layer and the communication is deterministic. • Each node just needs to communicate with its two neighbors through two CAT 5 network cable. This minimizes the cabling work and it is extendable. EPICS Collaboration Meeting, BNL, 2010

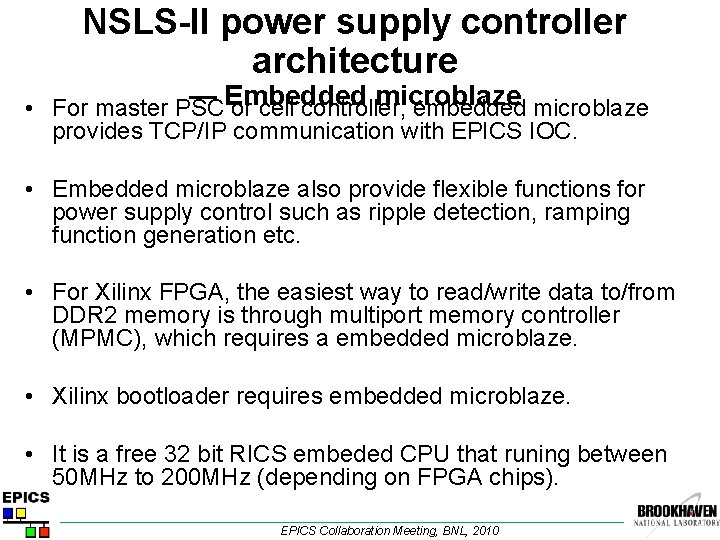

NSLS-II power supply controller architecture — Embedded microblaze • For master PSC or cell controller, embedded microblaze provides TCP/IP communication with EPICS IOC. • Embedded microblaze also provide flexible functions for power supply control such as ripple detection, ramping function generation etc. • For Xilinx FPGA, the easiest way to read/write data to/from DDR 2 memory is through multiport memory controller (MPMC), which requires a embedded microblaze. • Xilinx bootloader requires embedded microblaze. • It is a free 32 bit RICS embeded CPU that runing between 50 MHz to 200 MHz (depending on FPGA chips). EPICS Collaboration Meeting, BNL, 2010

NSLS-II power supply controller architecture — Interfacewith PSIsupply interface • NSLS-II PSC communicates power (PSI) through a low cost 50 Mbps fiber link. The fiber link provide the electrical isolation between PSC and PSI. For some accelerators, the power supply has several KV bias and fiber isolation between system is necessary. • A on board data clock recovery chip (DCR) with PLL is used to recover the receiving data and clock. All setpoints and readbacks have accociated CRC checking. EPICS Collaboration Meeting, BNL, 2010

NSLS-II power supply controller architecture Remote capability • For large— quantities of reprogram PSC, it is desirable to have the remote reprogram capability build-in so that upgrade can be done automatically. NSLS-II PSC is designed to have such function. EPICS Collaboration Meeting, BNL, 2010

Progress • All NSLS-II power supply control subsystem (PSC, PSI and current regulator) prototype design is done and tested. The production procurement (total of about $4 million) is in progress. • FPGA firmware and EPICS software development for different applications (such as Booster application, fast orbit feedback) is underway. EPICS Collaboration Meeting, BNL, 2010

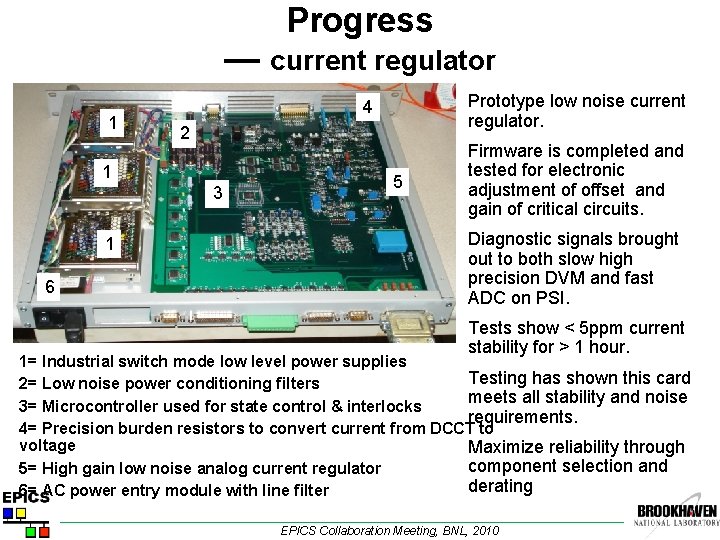

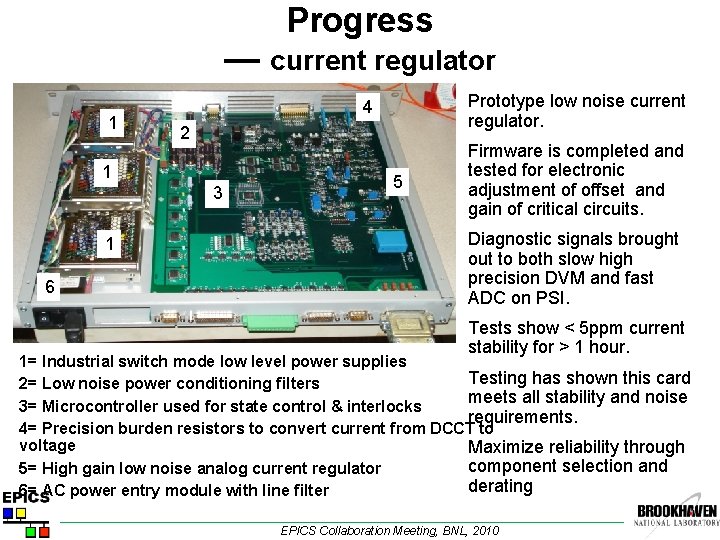

Progress — current regulator 1 2 1 3 1 6 Prototype low noise current regulator. 4 5 Firmware is completed and tested for electronic adjustment of offset and gain of critical circuits. Diagnostic signals brought out to both slow high precision DVM and fast ADC on PSI. Tests show < 5 ppm current stability for > 1 hour. 1= Industrial switch mode low level power supplies Testing has shown this card 2= Low noise power conditioning filters meets all stability and noise 3= Microcontroller used for state control & interlocks requirements. 4= Precision burden resistors to convert current from DCCT to voltage Maximize reliability through component selection and 5= High gain low noise analog current regulator derating 6= AC power entry module with line filter EPICS Collaboration Meeting, BNL, 2010

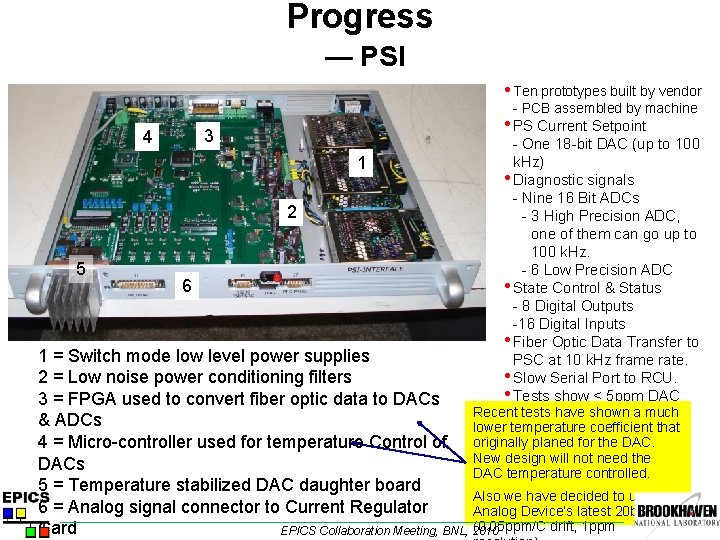

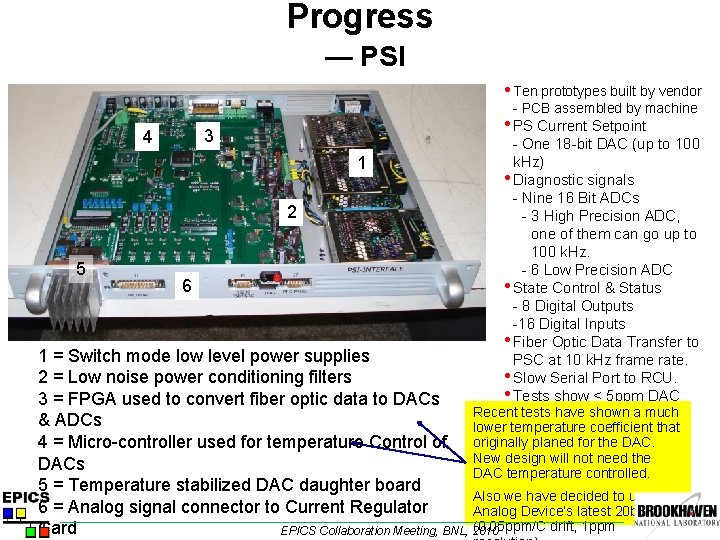

Progress — PSI • Ten prototypes built by vendor - PCB assembled by machine • PS Current Setpoint 3 4 1 2 5 6 - One 18 -bit DAC (up to 100 k. Hz) • Diagnostic signals - Nine 16 Bit ADCs - 3 High Precision ADC, one of them can go up to 100 k. Hz. - 6 Low Precision ADC • State Control & Status - 8 Digital Outputs -16 Digital Inputs • Fiber Optic Data Transfer to PSC at 10 k. Hz frame rate. • Slow Serial Port to RCU. • Tests show < 5 ppm DAC Recentstability tests have a much for shown > 1 hour. 1 = Switch mode low level power supplies 2 = Low noise power conditioning filters 3 = FPGA used to convert fiber optic data to DACs & ADCs lower temperature coefficient that 4 = Micro-controller used for temperature Control of originally planed for the DAC. New design will not need the DACs DAC temperature controlled. 5 = Temperature stabilized DAC daughter board Also we have decided to use 6 = Analog signal connector to Current Regulator Analog Device’s latest 20 bit DAC (0. 05 ppm/C drift, 1 ppm Card EPICS Collaboration Meeting, BNL, 2010

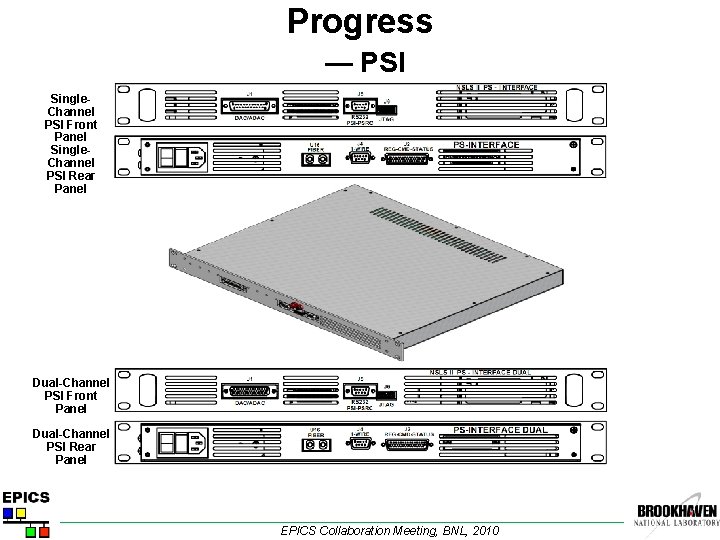

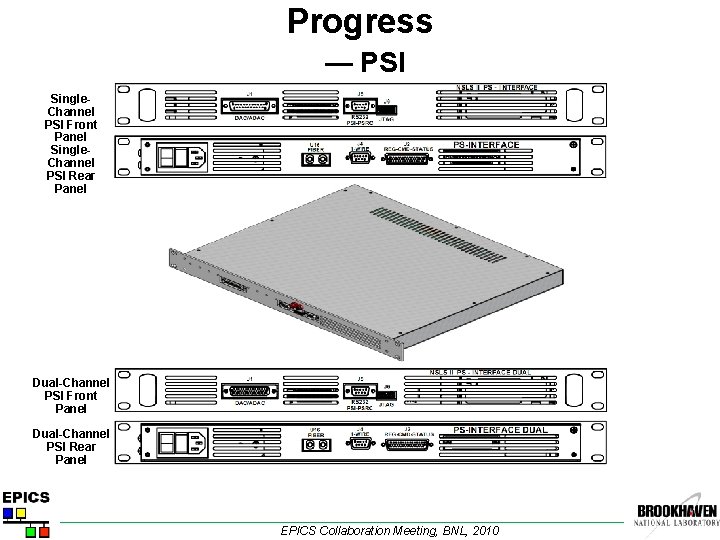

Progress — PSI Single. Channel PSI Front Panel Single. Channel PSI Rear Panel Dual-Channel PSI Front Panel Dual-Channel PSI Rear Panel EPICS Collaboration Meeting, BNL, 2010

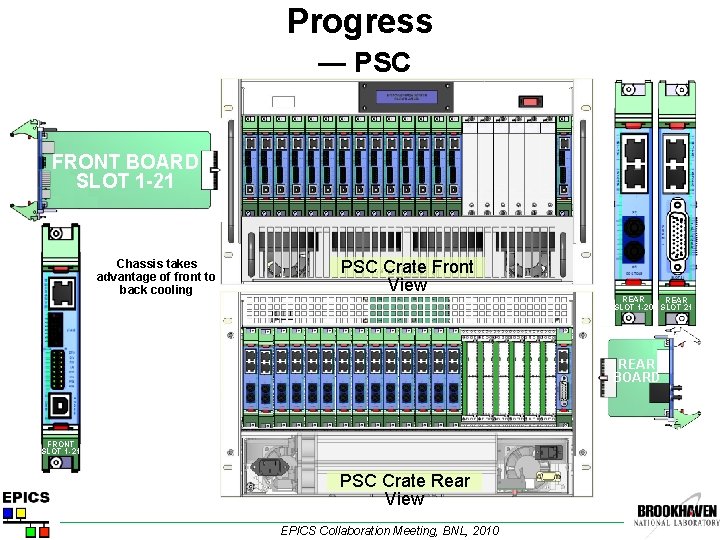

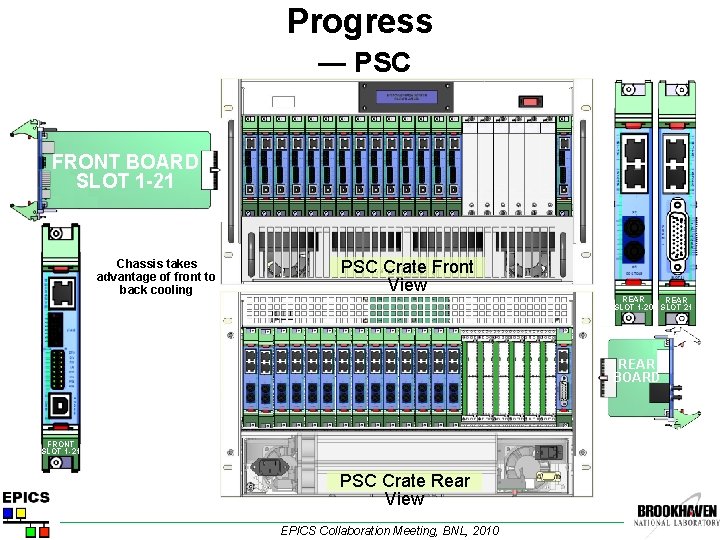

Progress — PSC FRONT BOARD SLOT 1 -21 Chassis takes advantage of front to back cooling PSC Crate Front View REAR SLOT 1 -20 SLOT 21 REAR BOARD FRONT SLOT 1 -21 PSC Crate Rear View EPICS Collaboration Meeting, BNL, 2010

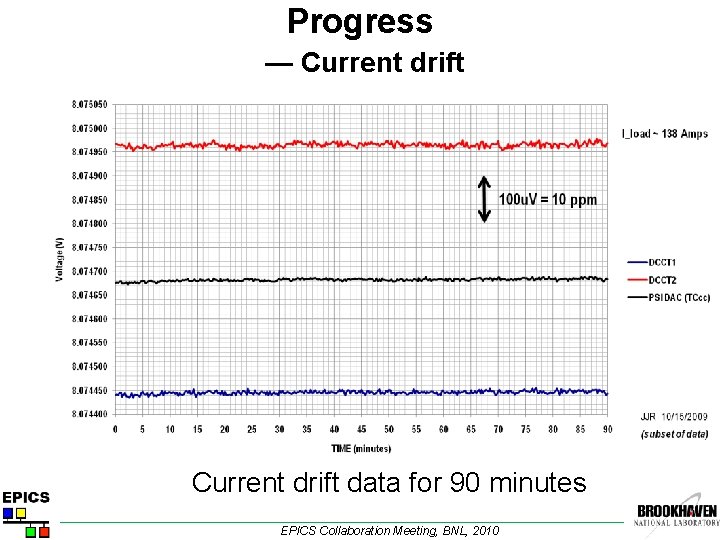

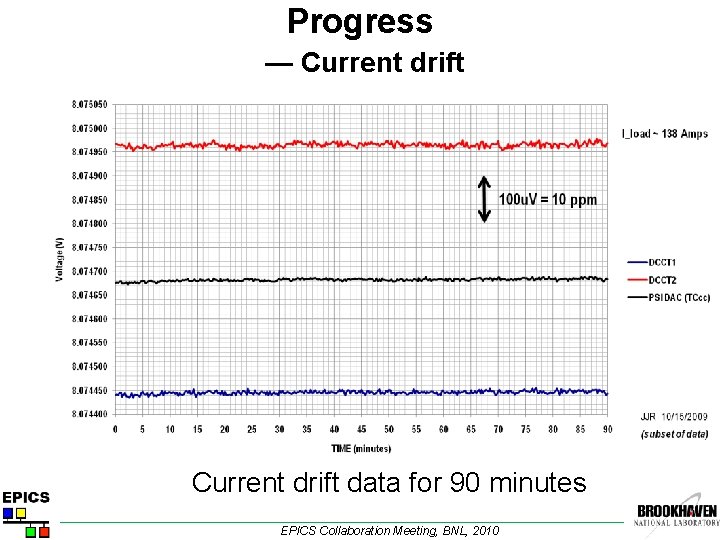

Progress — Current drift data for 90 minutes EPICS Collaboration Meeting, BNL, 2010

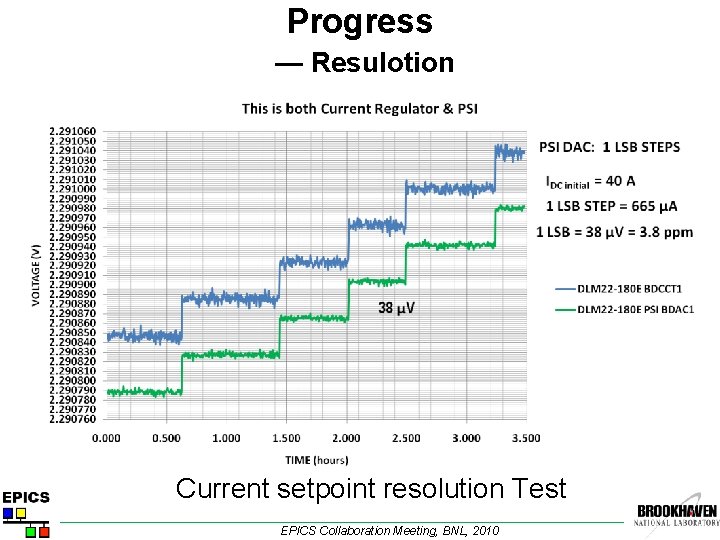

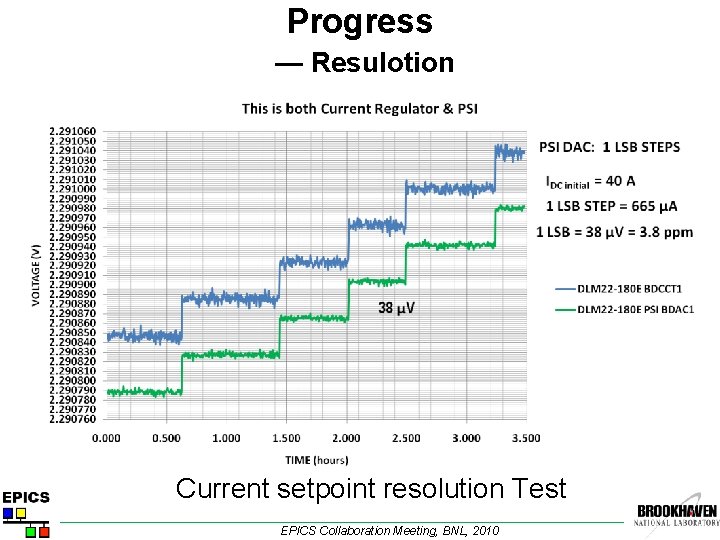

Progress — Resulotion Current setpoint resolution Test EPICS Collaboration Meeting, BNL, 2010

Summary • NSLS-II power supply control system’s performance is proven better than the requirements. It provides 1 ppm resolution and 1 ppm long term current stability. • NSLS-II PSC system is designed to have many features for power supply control and diagnostics. It is easy to integrated with other system. • NSLS-II power supply hardware, firmware and software design is fully open to the community and we welcome other facility to apply our design in their system. EPICS Collaboration Meeting, BNL, 2010