Memory Controller Topics Memory Controller Overview Memory Controller

- Slides: 19

Memory Controller Topics Memory Controller Overview Memory Controller Interface Memory Request Splitting Address Bitfields Memory Layout Example Memory Request Scheduling

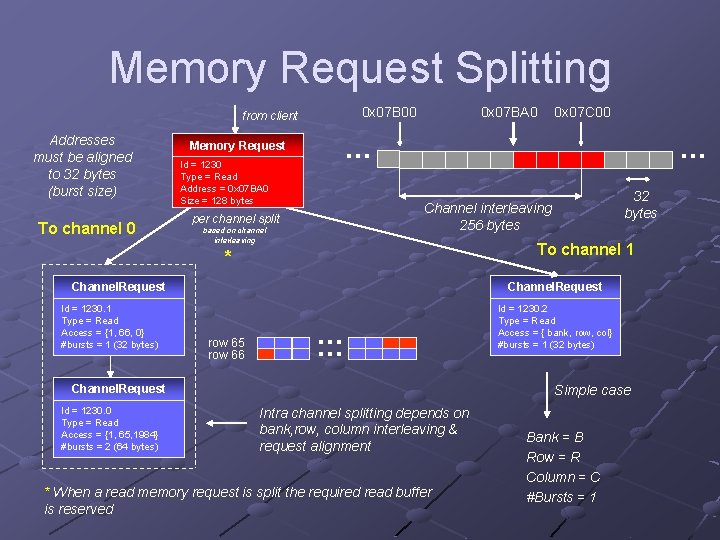

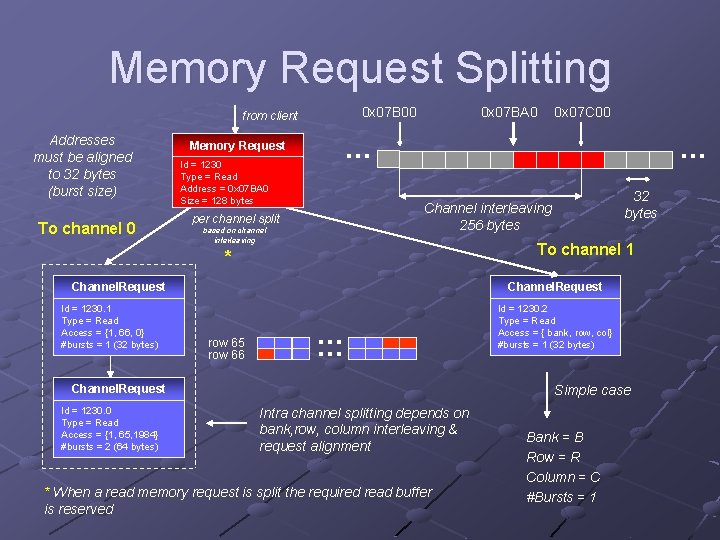

Memory Request Splitting 0 x 07 B 00 from client Addresses must be aligned to 32 bytes (burst size) To channel 0 0 x 07 BA 0 … Memory Request Id = 1230 Type = Read Address = 0 x 07 BA 0 Size = 128 bytes … per channel split based on channel interleaving To channel 1 Channel. Request row 65 row 66 … … Id = 1230. 2 Type = Read Access = { bank, row, col} #bursts = 1 (32 bytes) Simple case Channel. Request Id = 1230. 0 Type = Read Access = {1, 65, 1984} #bursts = 2 (64 bytes) 32 bytes Channel interleaving 256 bytes * Id = 1230. 1 Type = Read Access = {1, 66, 0} #bursts = 1 (32 bytes) 0 x 07 C 00 Intra channel splitting depends on bank, row, column interleaving & request alignment * When a read memory request is split the required read buffer is reserved Bank = B Row = R Column = C #Bursts = 1

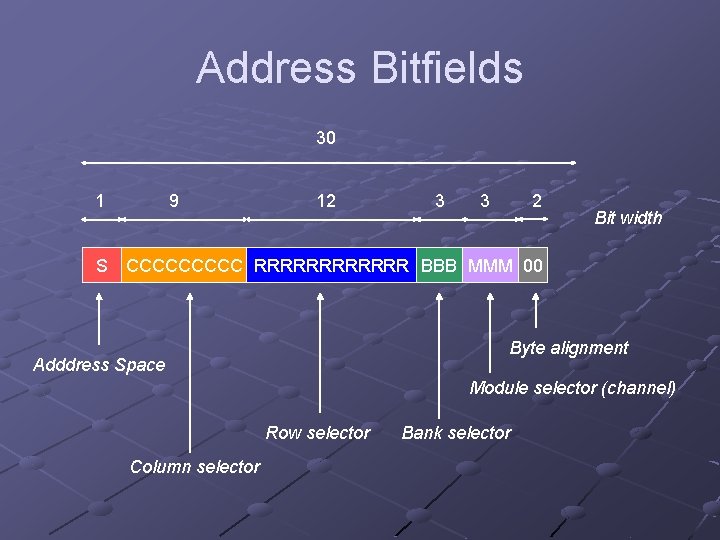

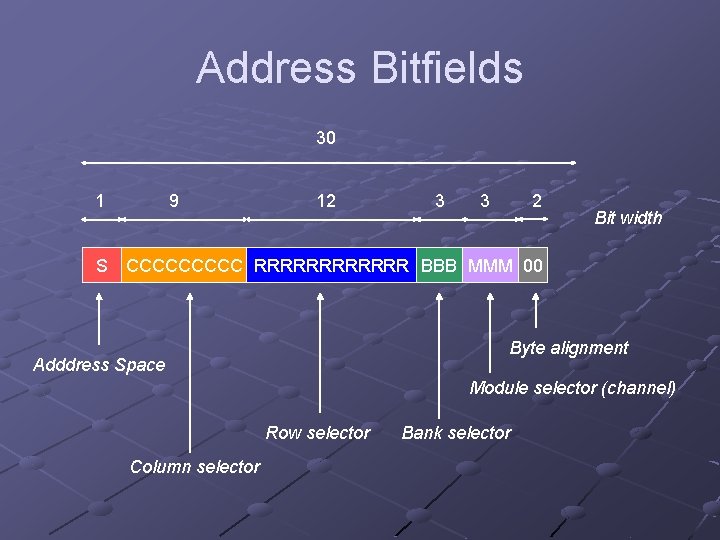

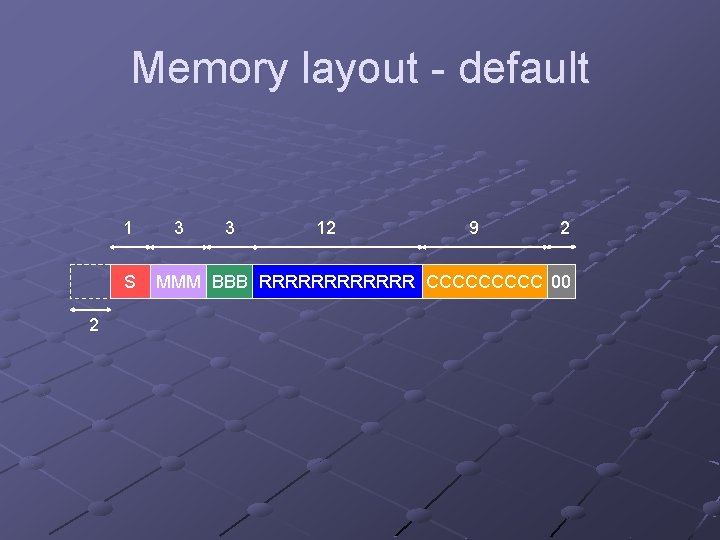

Address Bitfields 30 1 9 12 3 3 2 Bit width S CCCCC RRRRRR BBB MMM 00 Byte alignment Adddress Space Module selector (channel) Row selector Column selector Bank selector

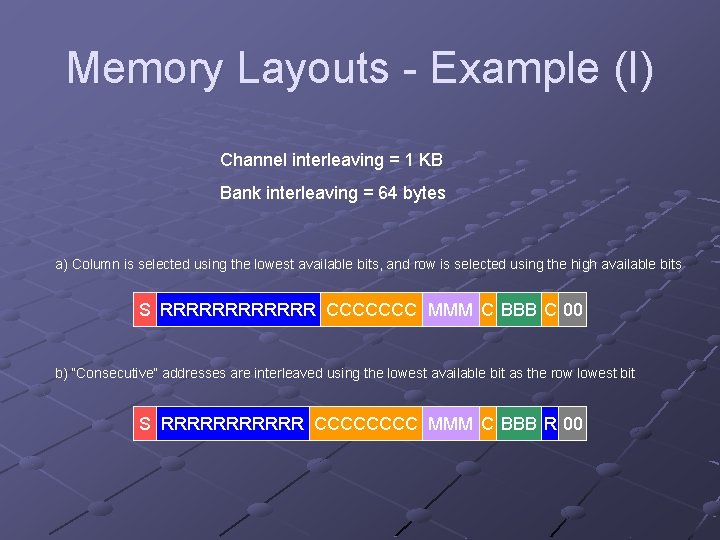

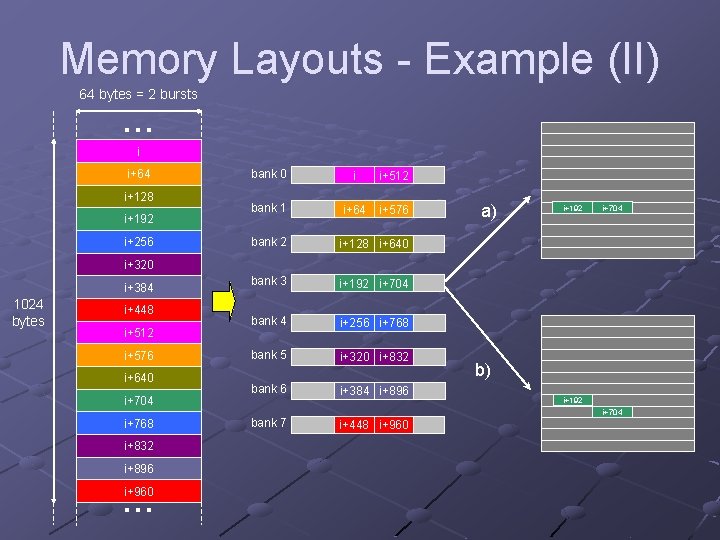

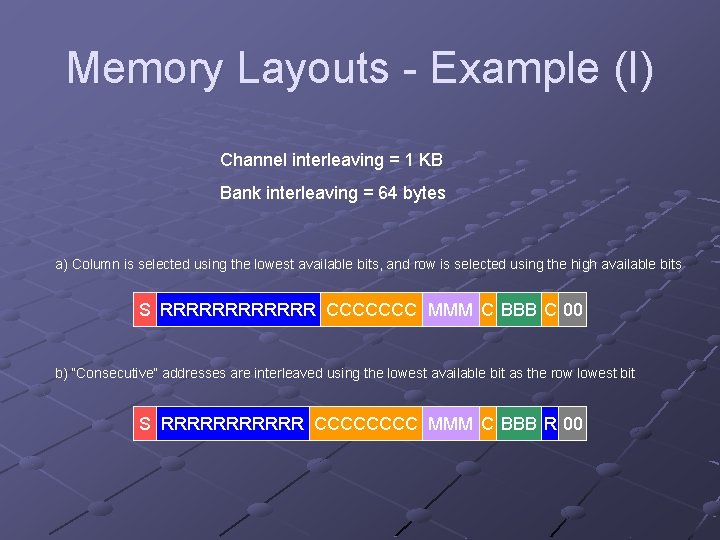

Memory Layouts - Example (I) Channel interleaving = 1 KB Bank interleaving = 64 bytes a) Column is selected using the lowest available bits, and row is selected using the high available bits S RRRRRR CCCCCCC MMM C BBB C 00 b) “Consecutive” addresses are interleaved using the lowest available bit as the row lowest bit S RRRRRR CCCC MMM C BBB R 00

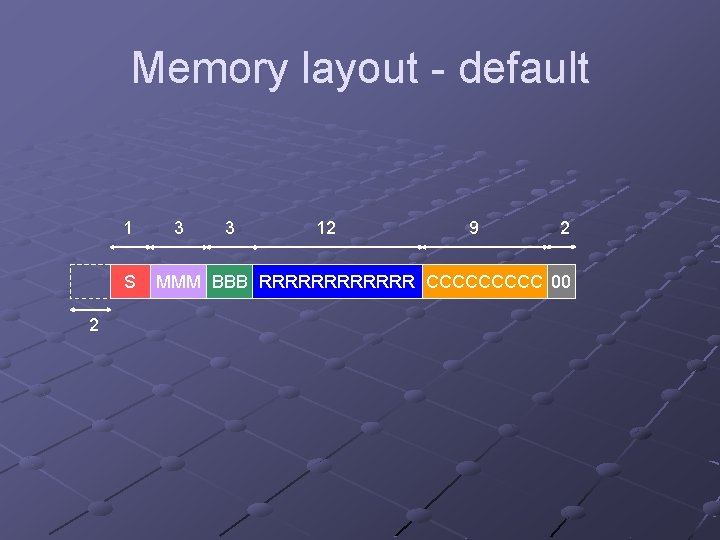

Memory layout - default 1 S 2 3 3 12 9 2 MMM BBB RRRRRR CCCCC 00

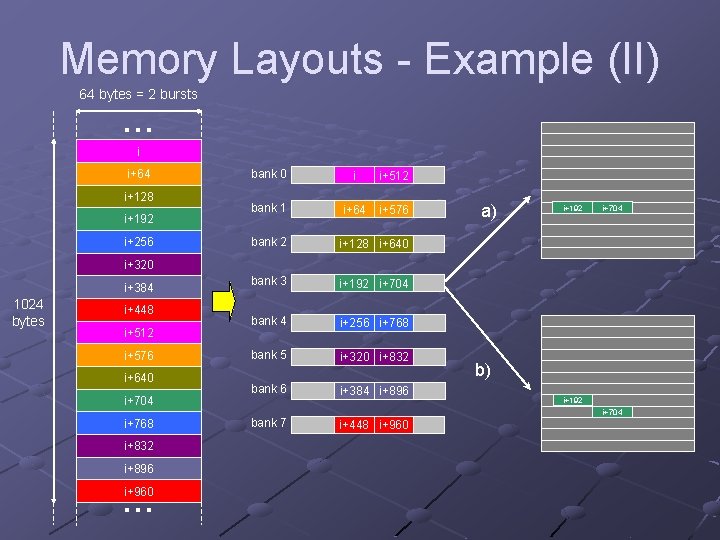

Memory Layouts - Example (II) 64 bytes = 2 bursts . . . i i+64 i+128 i+192 i+256 bank 0 i i+512 bank 1 i+64 i+576 bank 2 i+128 i+640 bank 3 i+192 i+704 bank 4 i+256 i+768 bank 5 i+320 i+832 bank 6 i+384 i+896 a) i+192 i+704 i+320 i+384 1024 bytes i+448 i+512 i+576 i+640 i+704 i+768 i+832 i+896 . . . i+960 bank 7 b) i+192 i+704 i+448 i+960

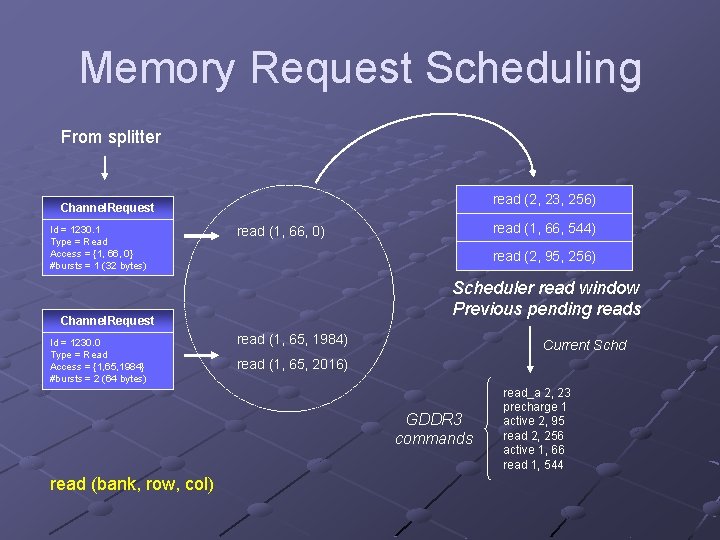

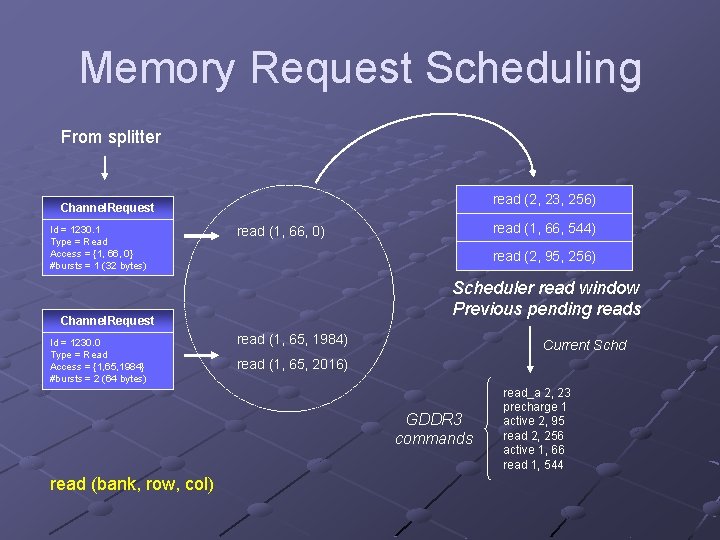

Memory Request Scheduling From splitter read (2, 23, 256) Channel. Request Id = 1230. 1 Type = Read Access = {1, 66, 0} #bursts = 1 (32 bytes) read (2, 95, 256) Scheduler read window Previous pending reads Channel. Request Id = 1230. 0 Type = Read Access = {1, 65, 1984} #bursts = 2 (64 bytes) read (1, 66, 544) read (1, 66, 0) read (1, 65, 1984) Current Schd read (1, 65, 2016) GDDR 3 commands read (bank, row, col) read_a 2, 23 precharge 1 active 2, 95 read 2, 256 active 1, 66 read 1, 544

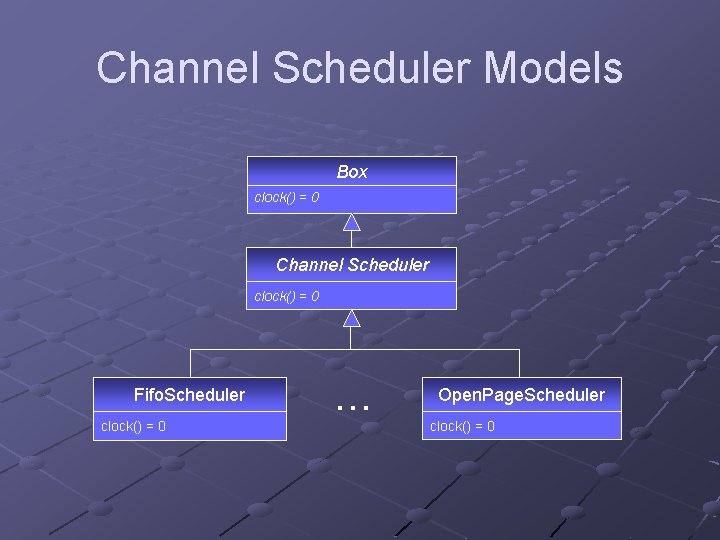

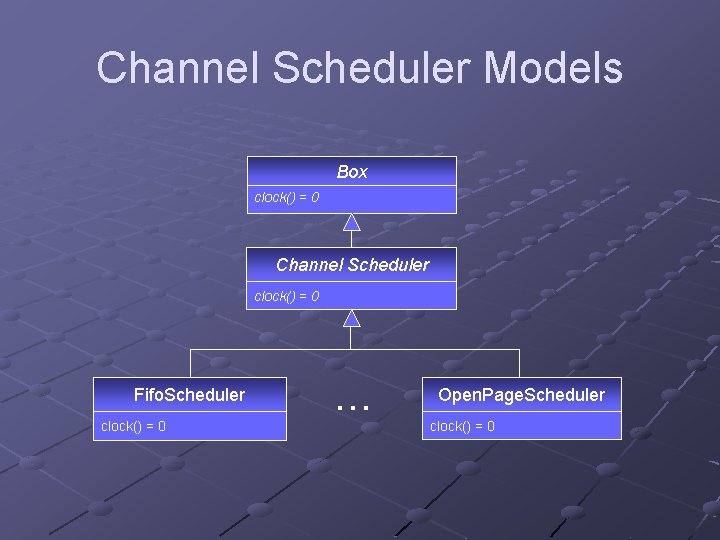

Channel Scheduler Models Box clock() = 0 Channel Scheduler clock() = 0 Fifo. Scheduler clock() = 0 … Open. Page. Scheduler clock() = 0

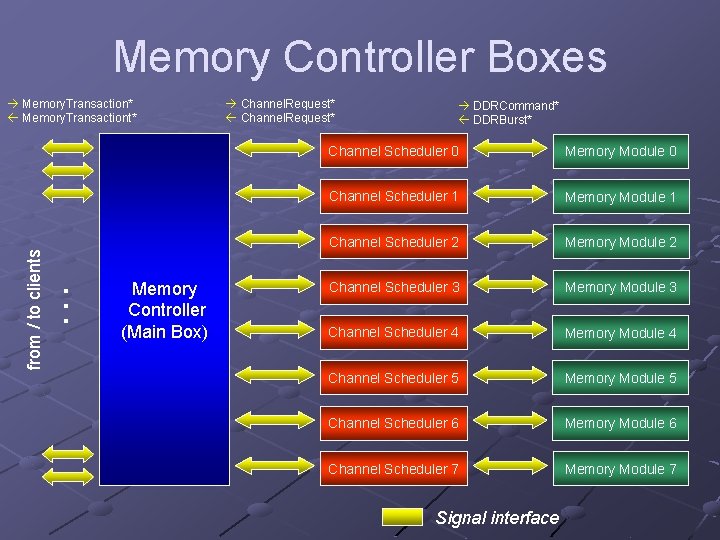

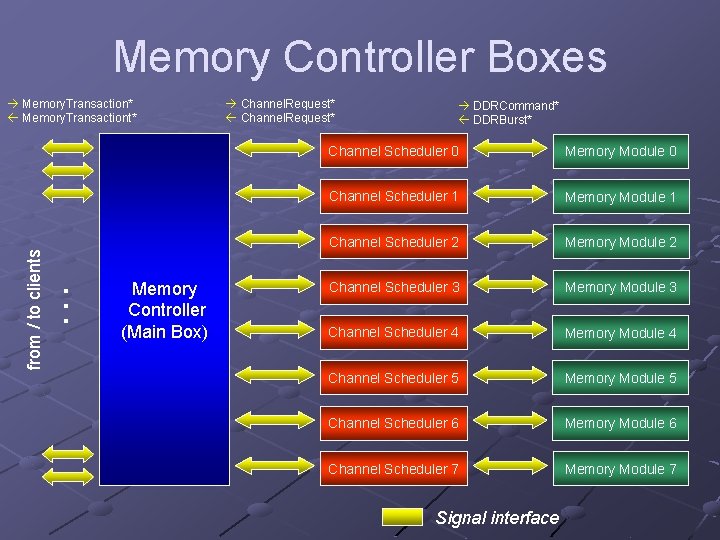

Memory Controller Boxes … from / to clients Memory. Transaction* Memory. Transactiont* Memory Controller (Main Box) Channel. Request* DDRCommand* DDRBurst* Channel Scheduler 0 Memory Module 0 Channel Scheduler 1 Memory Module 1 Channel Scheduler 2 Memory Module 2 Channel Scheduler 3 Memory Module 3 Channel Scheduler 4 Memory Module 4 Channel Scheduler 5 Memory Module 5 Channel Scheduler 6 Memory Module 6 Channel Scheduler 7 Memory Module 7 Signal interface

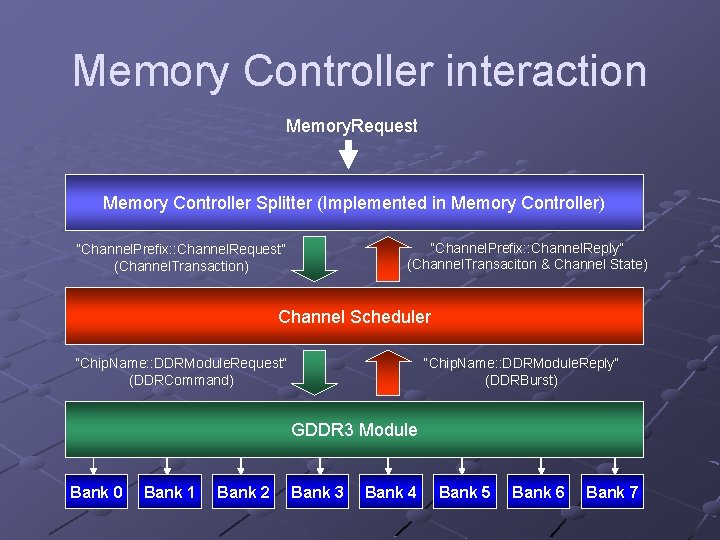

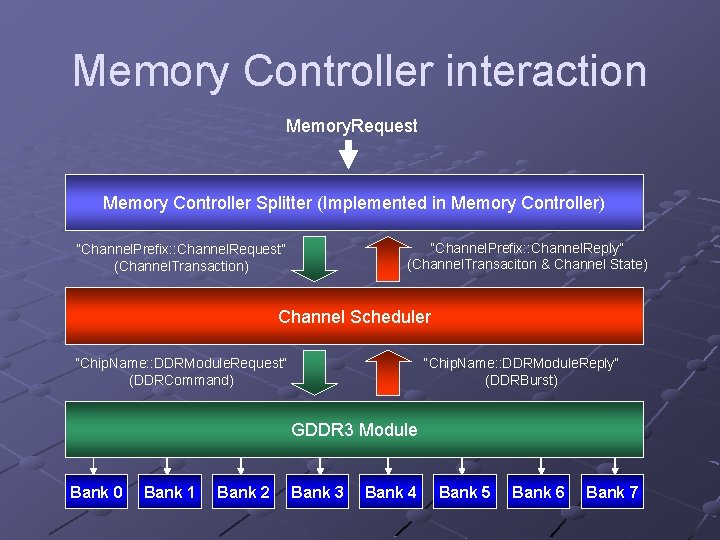

Memory Controller interaction Memory. Request Memory Controller Splitter (Implemented in Memory Controller) “Channel. Prefix: : Channel. Reply” (Channel. Transaciton & Channel State) “Channel. Prefix: : Channel. Request” (Channel. Transaction) Channel Scheduler “Chip. Name: : DDRModule. Request” (DDRCommand) “Chip. Name: : DDRModule. Reply” (DDRBurst) GDDR 3 Module Bank 0 Bank 1 Bank 2 Bank 3 Bank 4 Bank 5 Bank 6 Bank 7

Memory Controller Stages RReq Select & Split Select CTran DDR cmd . . . CTran. Answer Assembly. Req Reply

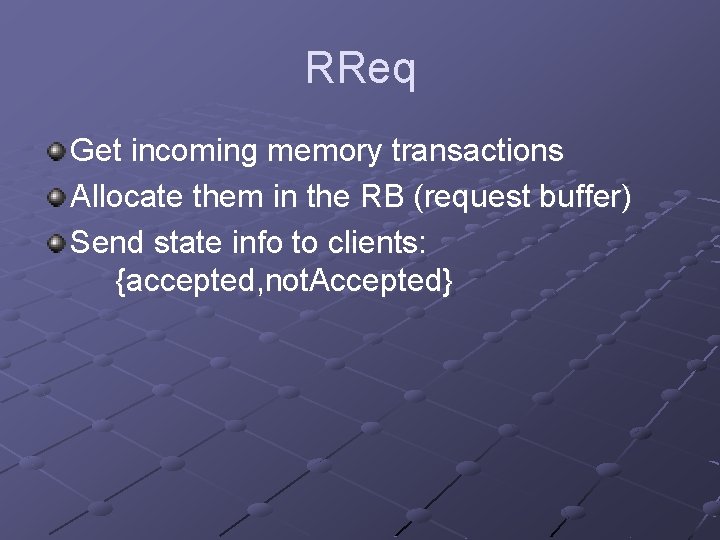

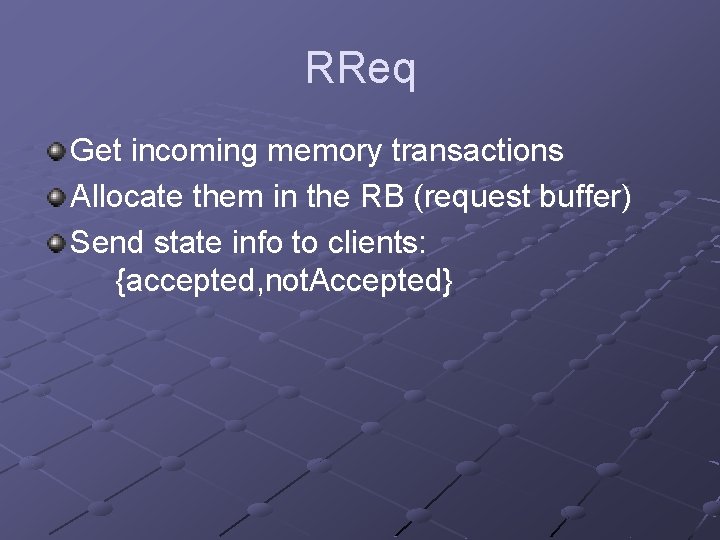

RReq Get incoming memory transactions Allocate them in the RB (request buffer) Send state info to clients: {accepted, not. Accepted}

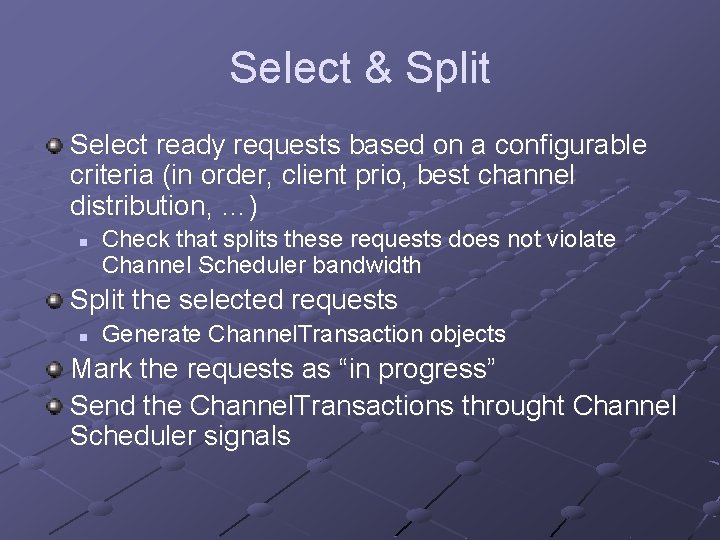

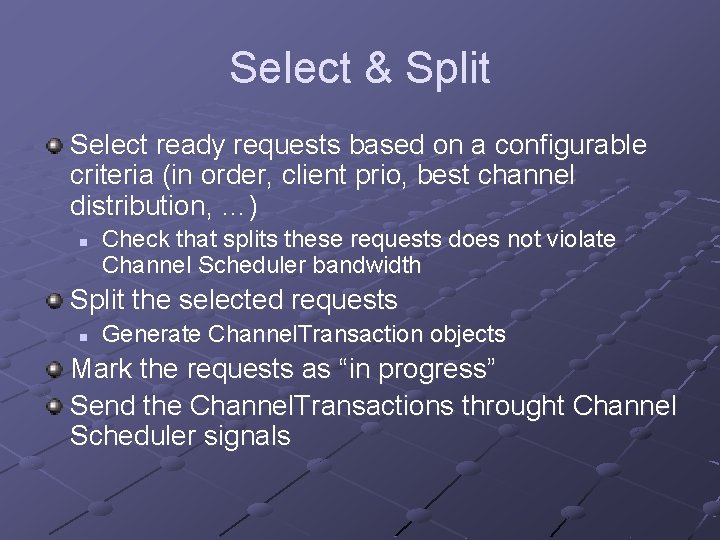

Select & Split Select ready requests based on a configurable criteria (in order, client prio, best channel distribution, …) n Check that splits these requests does not violate Channel Scheduler bandwidth Split the selected requests n Generate Channel. Transaction objects Mark the requests as “in progress” Send the Channel. Transactions throught Channel Scheduler signals

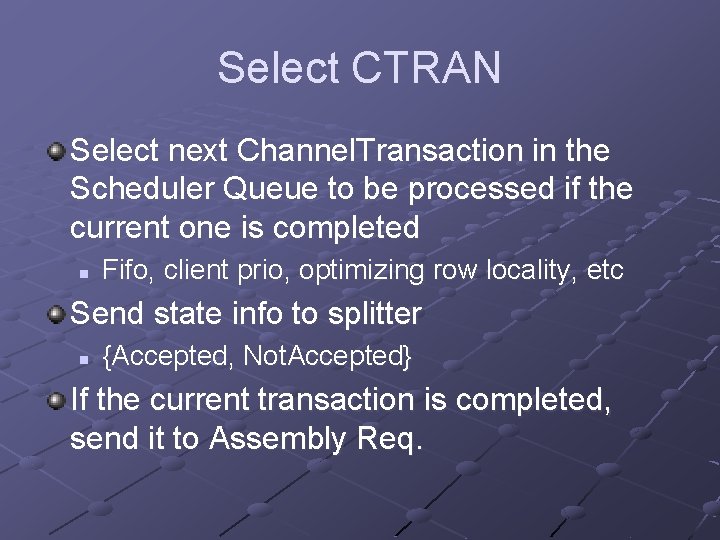

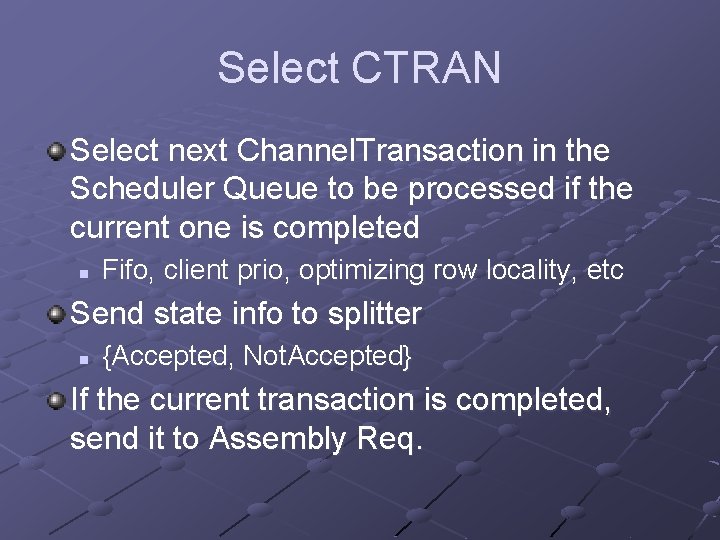

Select CTRAN Select next Channel. Transaction in the Scheduler Queue to be processed if the current one is completed n Fifo, client prio, optimizing row locality, etc Send state info to splitter n {Accepted, Not. Accepted} If the current transaction is completed, send it to Assembly Req.

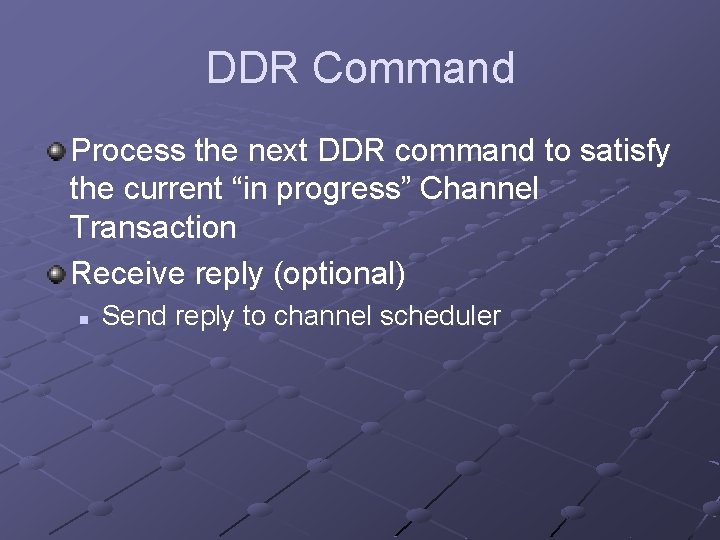

DDR Command Process the next DDR command to satisfy the current “in progress” Channel Transaction Receive reply (optional) n Send reply to channel scheduler

Assembly Req Receives completed channel transactions

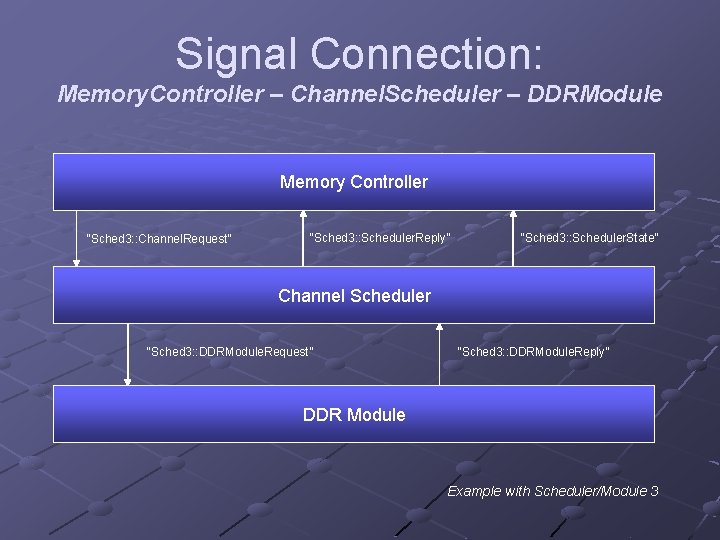

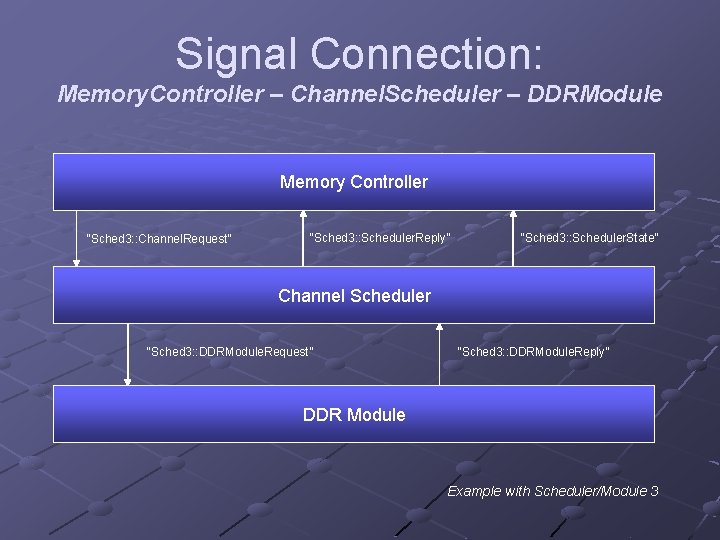

Signal Connection: Memory. Controller – Channel. Scheduler – DDRModule Memory Controller “Sched 3: : Channel. Request” “Sched 3: : Scheduler. Reply” “Sched 3: : Scheduler. State” Channel Scheduler “Sched 3: : DDRModule. Request” “Sched 3: : DDRModule. Reply” DDR Module Example with Scheduler/Module 3

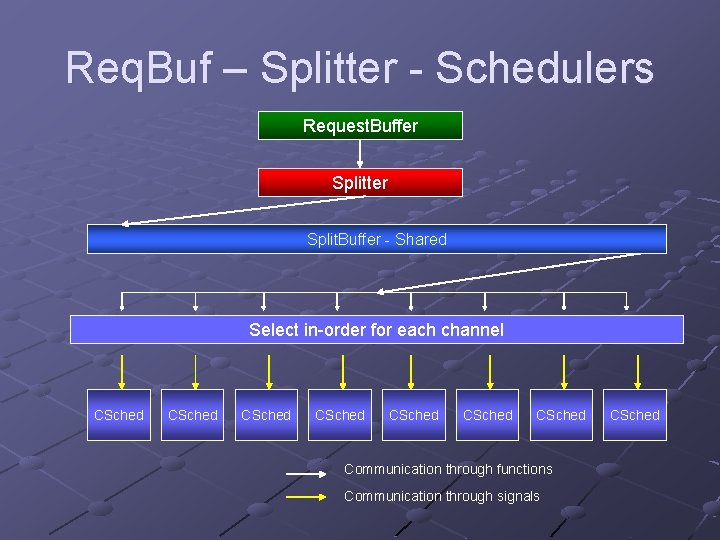

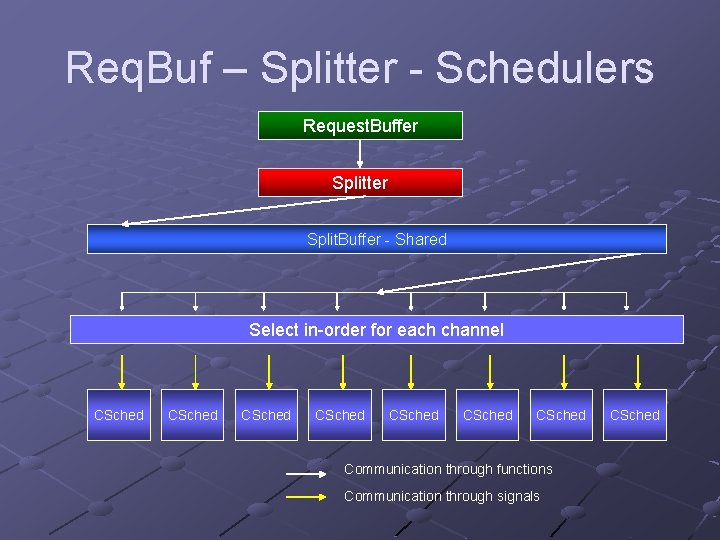

Req. Buf – Splitter - Schedulers Request. Buffer Splitter Split. Buffer - Shared Select in-order for each channel CSched CSched Communication through functions Communication through signals CSched

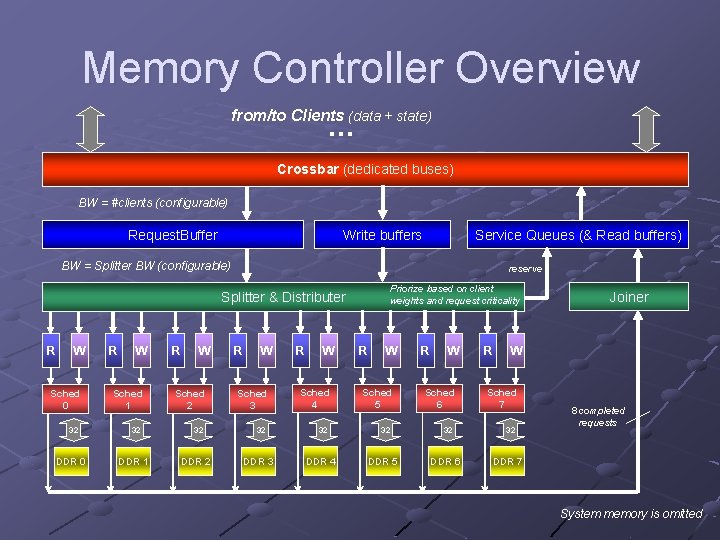

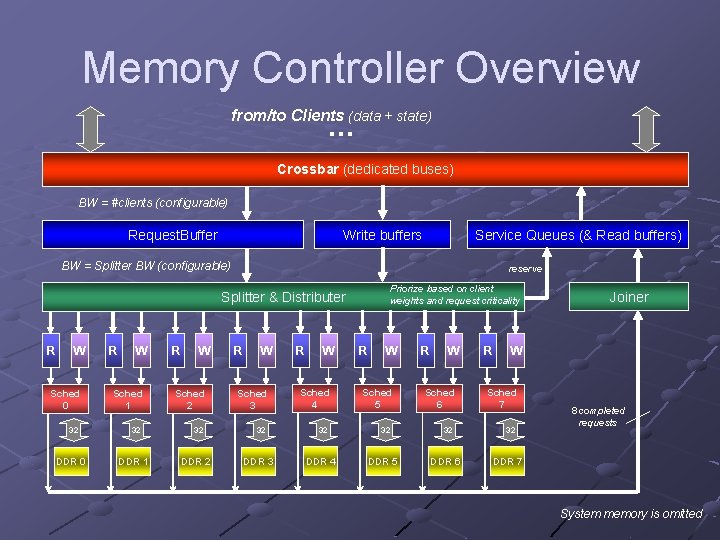

Memory Controller Overview from/to Clients (data + state) … Crossbar (dedicated buses) BW = #clients (configurable) Request. Buffer Write buffers Service Queues (& Read buffers) BW = Splitter BW (configurable) reserve Priorize based on client weights and request criticality Splitter & Distributer R W R W Sched 0 Sched 1 Sched 2 Sched 3 Sched 4 Sched 5 Sched 6 Sched 7 32 32 DDR 0 DDR 1 DDR 2 DDR 3 DDR 4 DDR 5 DDR 6 Joiner 8 completed requests DDR 7 System memory is omitted