NSLSII Power Supply Control System Yuke Tian Accelerator

- Slides: 22

NSLS-II Power Supply Control System Yuke Tian Accelerator Division Photon Science Directory Brookhaven National Lab EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

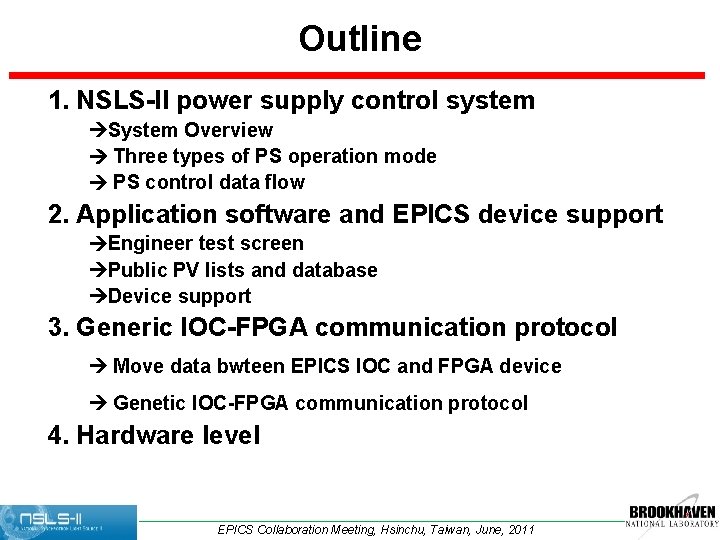

Outline 1. NSLS-II power supply control system System Overview Three types of PS operation mode PS control data flow 2. Application software and EPICS device support Engineer test screen Public PV lists and database Device support 3. Generic IOC-FPGA communication protocol Move data bwteen EPICS IOC and FPGA device Genetic IOC-FPGA communication protocol 4. Hardware level EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

System Overview Magnets and Power Supplies in Storage Ring EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

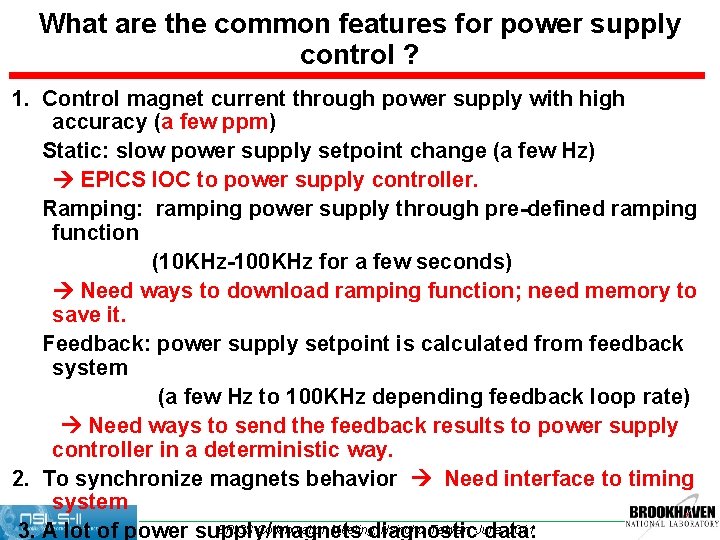

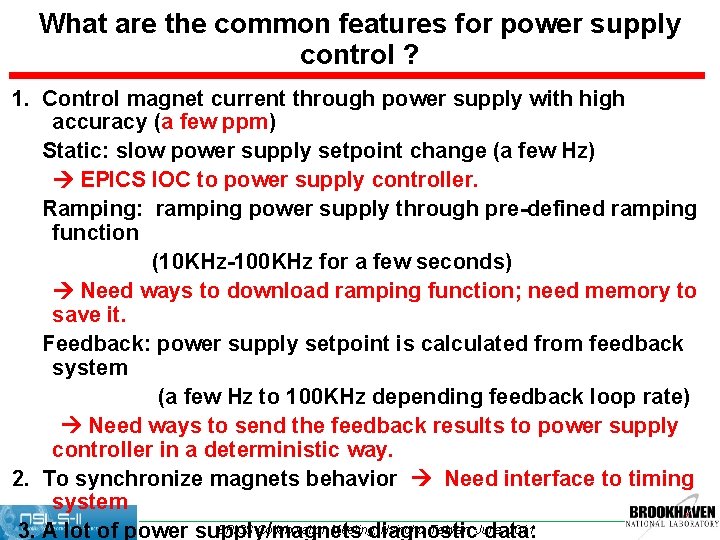

What are the common features for power supply control ? 1. Control magnet current through power supply with high accuracy (a few ppm) Static: slow power supply setpoint change (a few Hz) EPICS IOC to power supply controller. Ramping: ramping power supply through pre-defined ramping function (10 KHz-100 KHz for a few seconds) Need ways to download ramping function; need memory to save it. Feedback: power supply setpoint is calculated from feedback system (a few Hz to 100 KHz depending feedback loop rate) Need ways to send the feedback results to power supply controller in a deterministic way. 2. To synchronize magnets behavior Need interface to timing system EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011 3. A lot of power supply/magnets diagnostic data:

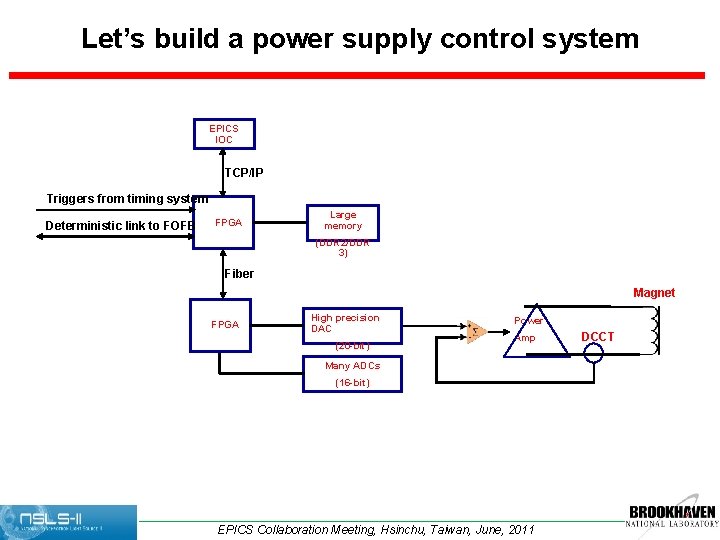

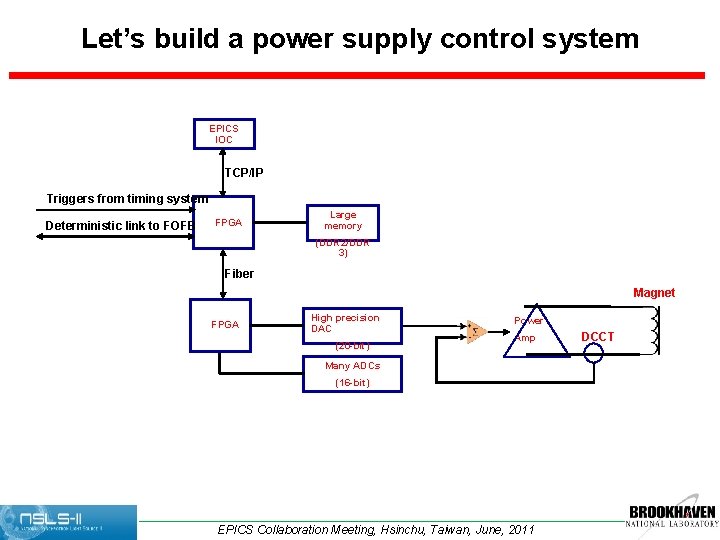

Let’s build a power supply control system EPICS IOC TCP/IP Triggers from timing system Deterministic link to FOFB FPGA Large memory (DDR 2/DDR 3) Fiber Magnet FPGA High precision DAC (20 -bit) Power Amp Many ADCs (16 -bit) EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011 DCCT

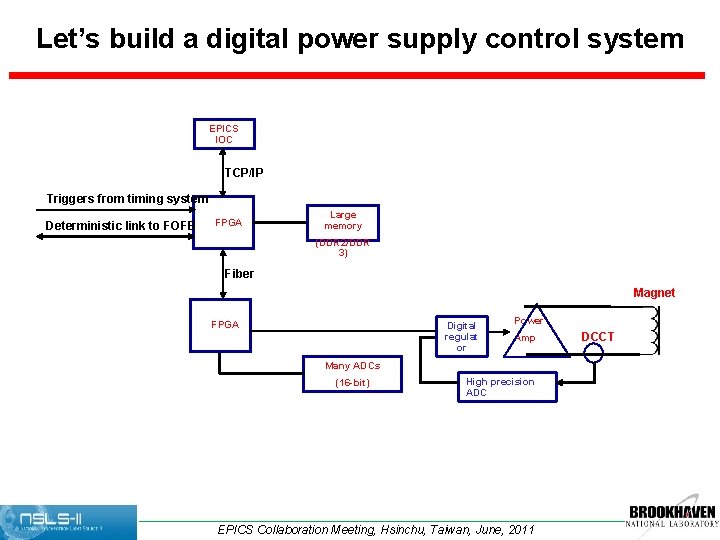

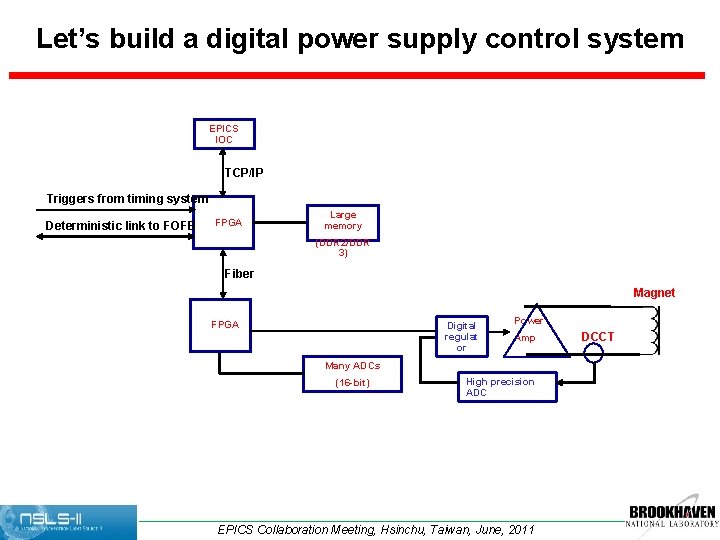

Let’s build a digital power supply control system EPICS IOC TCP/IP Triggers from timing system Deterministic link to FOFB FPGA Large memory (DDR 2/DDR 3) Fiber Magnet FPGA Digital regulat or Power Amp Many ADCs (16 -bit) High precision ADC EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011 DCCT

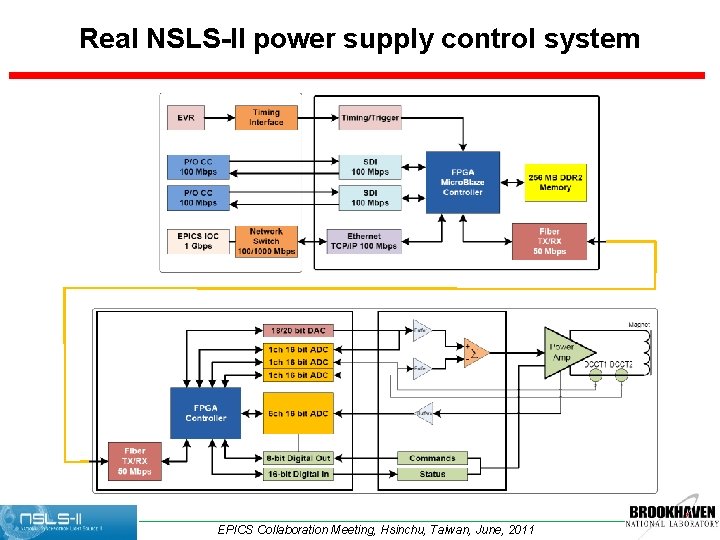

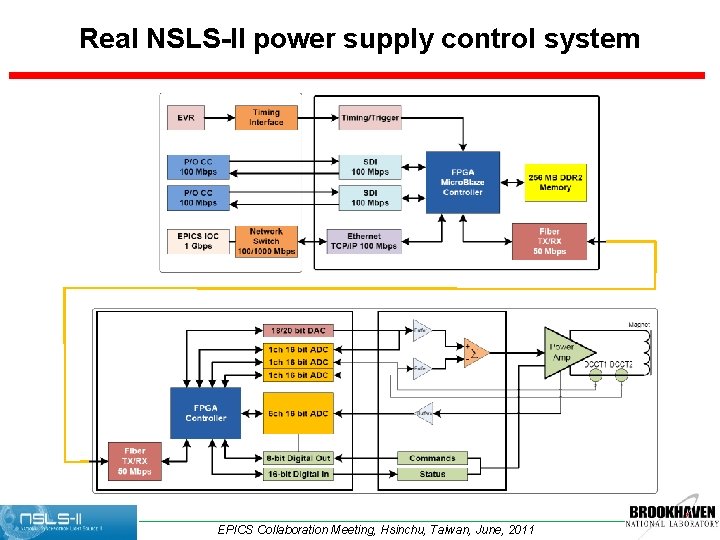

Real NSLS-II power supply control system EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

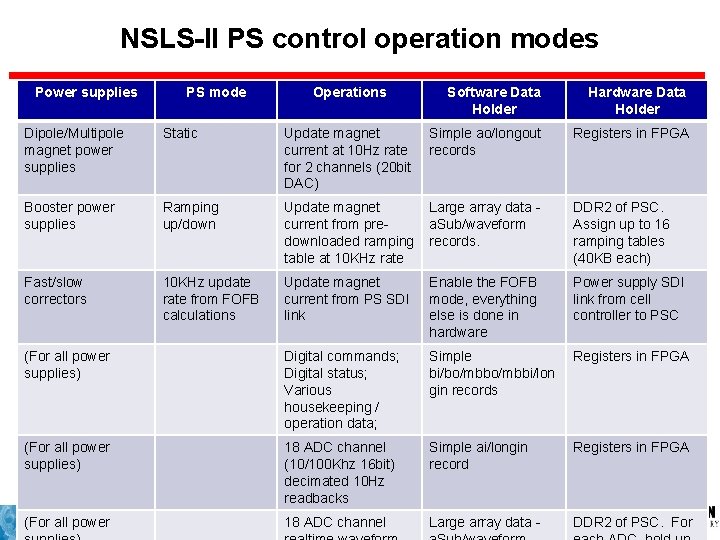

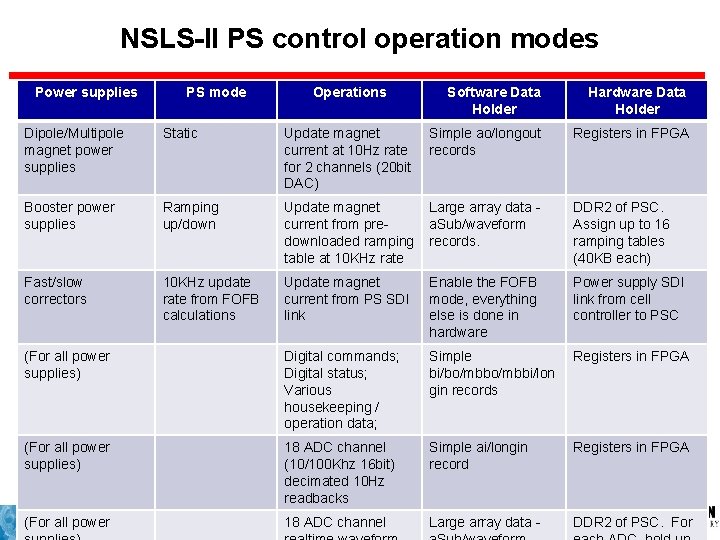

NSLS-II PS control operation modes Power supplies PS mode Operations Software Data Holder Hardware Data Holder Dipole/Multipole magnet power supplies Static Update magnet current at 10 Hz rate for 2 channels (20 bit DAC) Simple ao/longout records Registers in FPGA Booster power supplies Ramping up/down Update magnet current from predownloaded ramping table at 10 KHz rate Large array data a. Sub/waveform records. DDR 2 of PSC. Assign up to 16 ramping tables (40 KB each) Fast/slow correctors 10 KHz update rate from FOFB calculations Update magnet current from PS SDI link Enable the FOFB mode, everything else is done in hardware Power supply SDI link from cell controller to PSC (For all power supplies) Digital commands; Digital status; Various housekeeping / operation data; Simple bi/bo/mbbi/lon gin records Registers in FPGA (For all power supplies) 18 ADC channel (10/100 Khz 16 bit) decimated 10 Hz readbacks Simple ai/longin record Registers in FPGA 18 ADC channel Large array data - DDR 2 of PSC. For (For all power EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

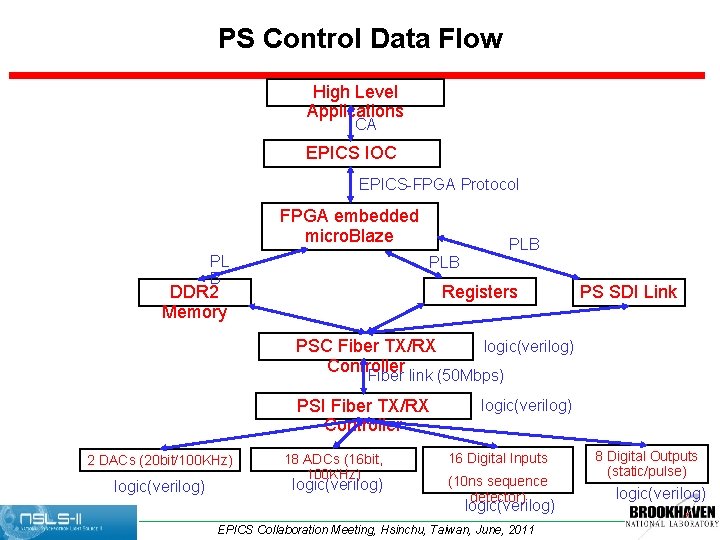

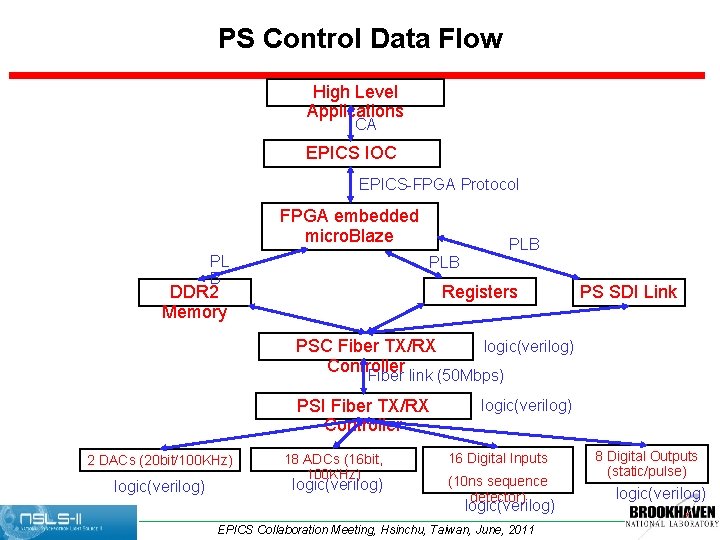

PS Control Data Flow High Level Applications CA EPICS IOC EPICS-FPGA Protocol FPGA embedded micro. Blaze PL B PLB Registers DDR 2 Memory PSC Fiber TX/RX Controller logic(verilog) PSI Fiber TX/RX Controller logic(verilog) PS SDI Link Fiber link (50 Mbps) 2 DACs (20 bit/100 KHz) logic(verilog) 18 ADCs (16 bit, 100 KHz) logic(verilog) 16 Digital Inputs (10 ns sequence detector) logic(verilog) EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011 8 Digital Outputs (static/pulse) logic(verilog)

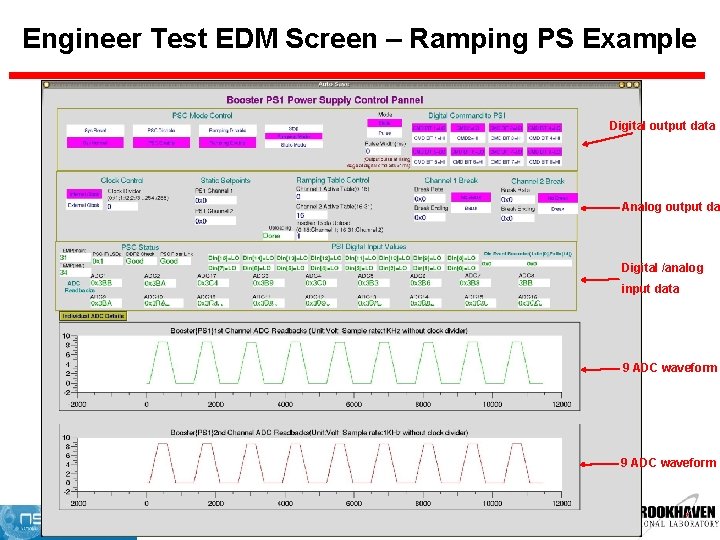

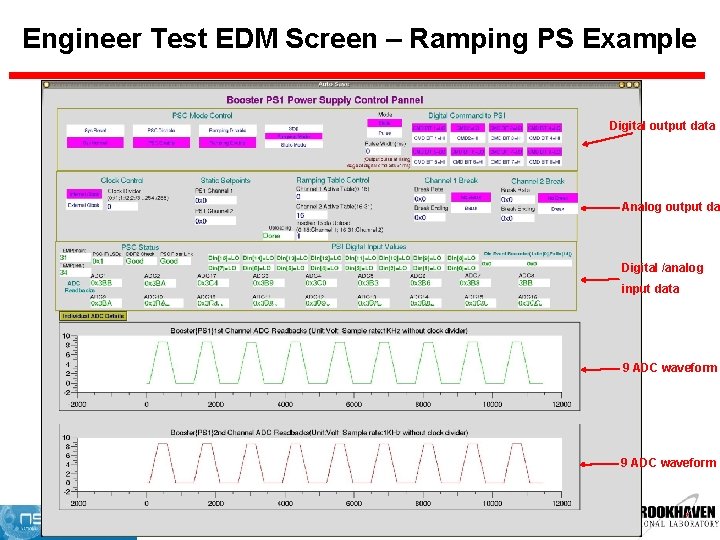

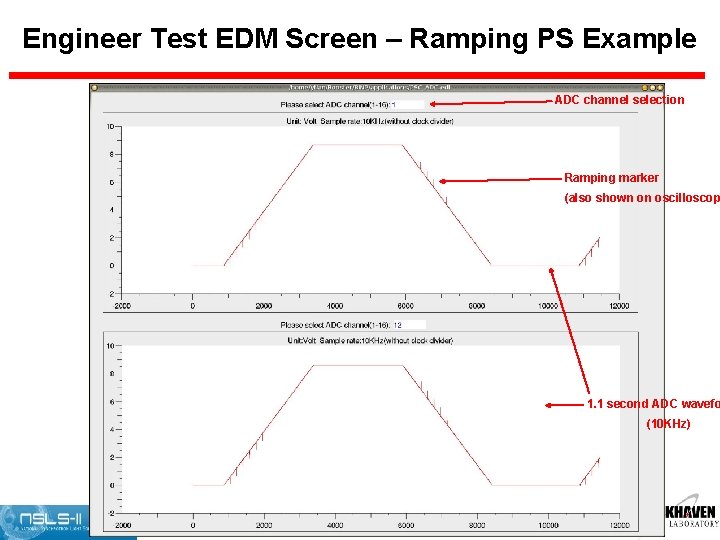

Engineer Test EDM Screen – Ramping PS Example Digital output data Analog output da Digital /analog input data 9 ADC waveform EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

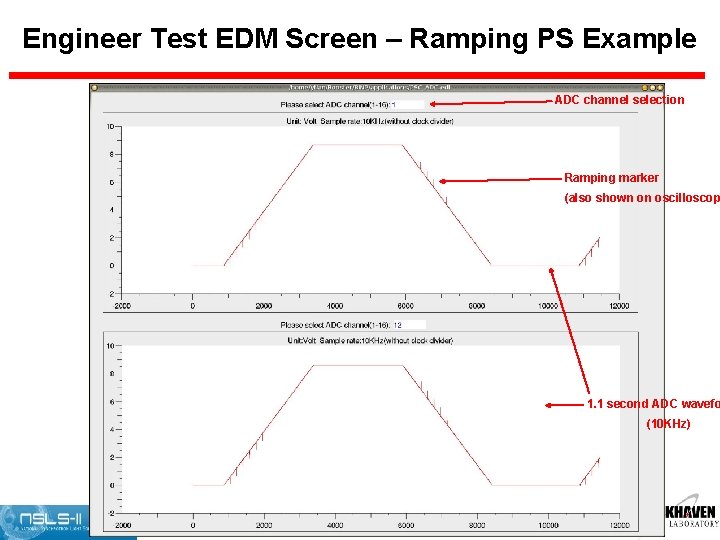

Engineer Test EDM Screen – Ramping PS Example ADC channel selection Ramping marker (also shown on oscilloscop 1. 1 second ADC wavefo (10 KHz) EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

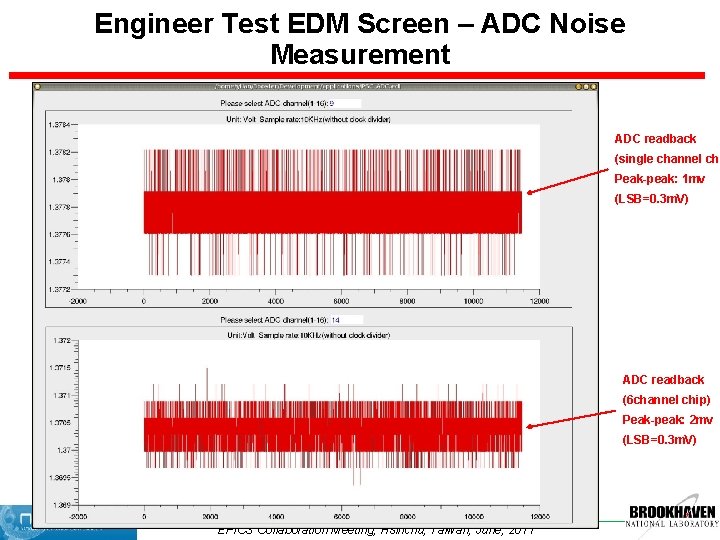

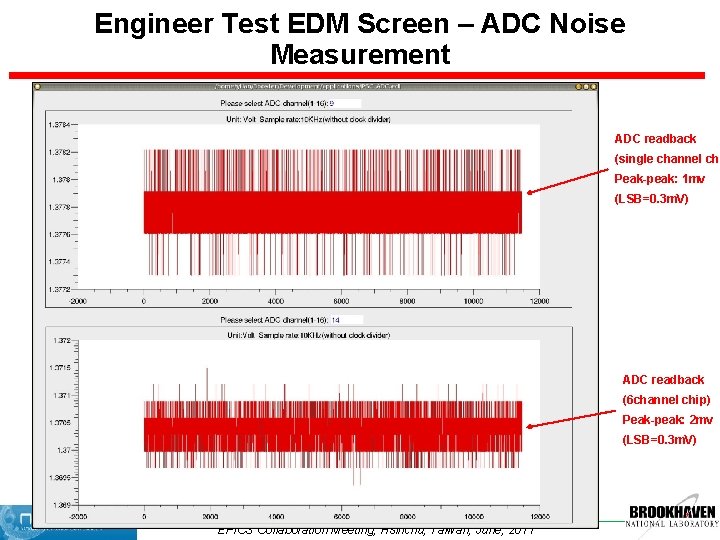

Engineer Test EDM Screen – ADC Noise Measurement ADC readback (single channel chi Peak-peak: 1 mv (LSB=0. 3 m. V) ADC readback (6 channel chip) Peak-peak: 2 mv (LSB=0. 3 m. V) EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

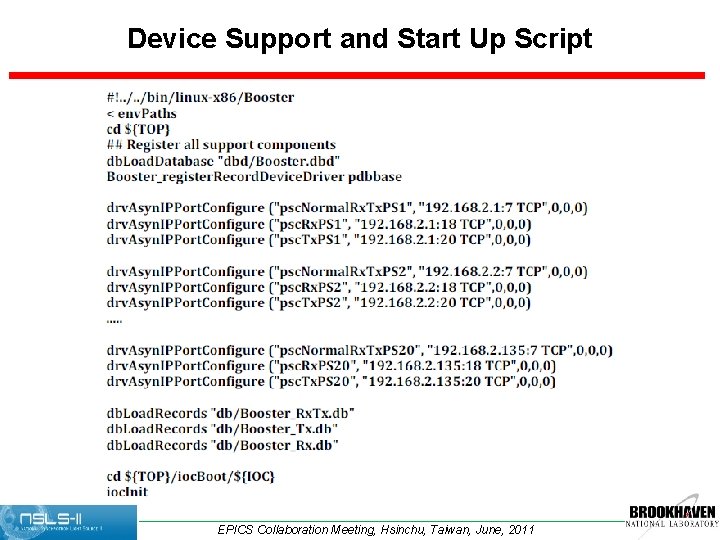

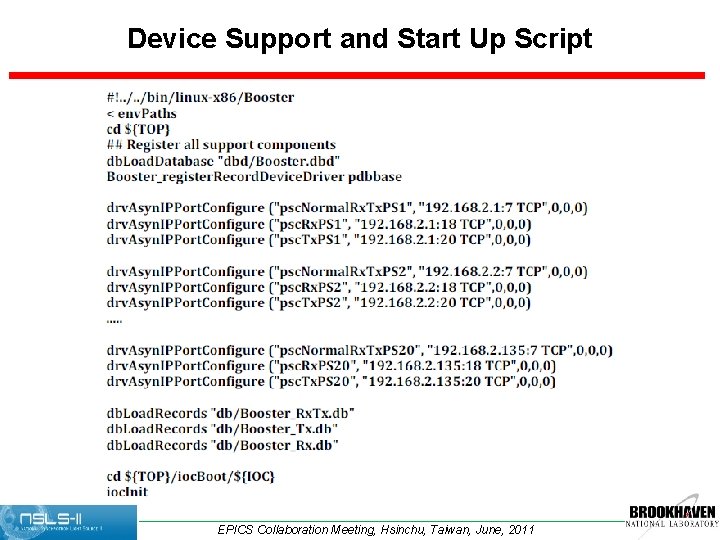

Device Support and Start Up Script EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

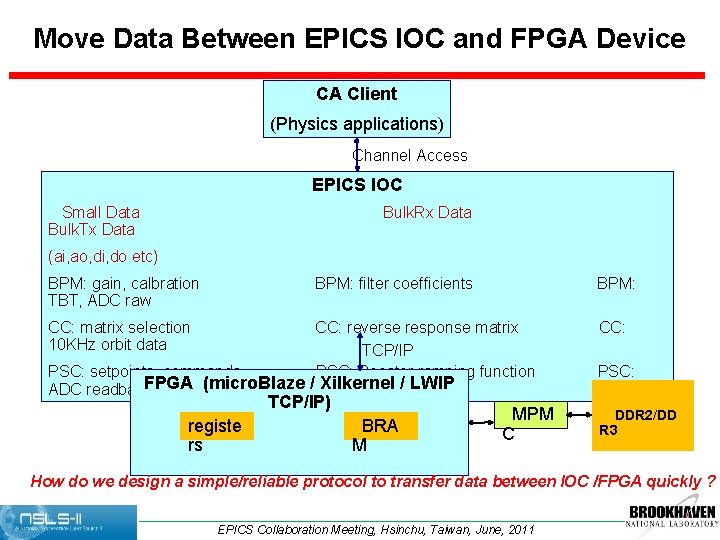

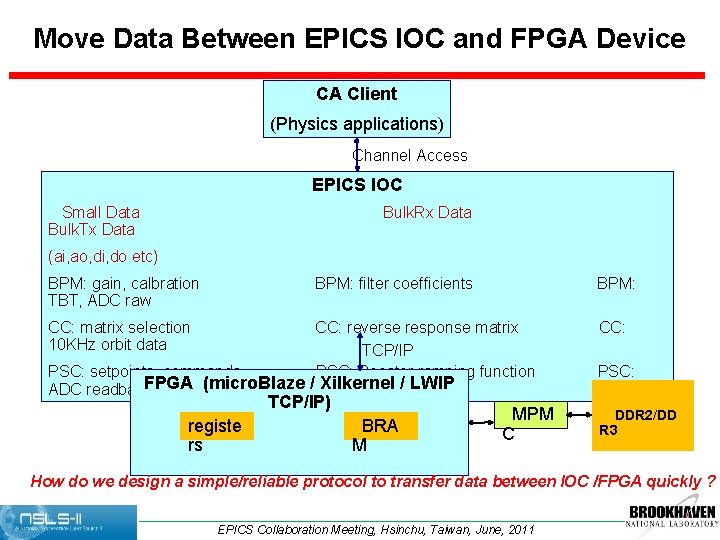

Move Data Between EPICS IOC and FPGA Device CA Client (Physics applications) Channel Access EPICS IOC Small Data Bulk. Tx Data Bulk. Rx Data (ai, ao, di, do etc) BPM: gain, calbration TBT, ADC raw BPM: filter coefficients BPM: CC: matrix selection 10 KHz orbit data CC: reverse response matrix TCP/IP PSC: Booster ramping function CC: PSC: setpoints, commands FPGA (micro. Blaze / Xilkernel / LWIP ADC readbacks TCP/IP) registe rs BRA M MPM C PSC: DDR 2/DD R 3 How do we design a simple/reliable protocol to transfer data between IOC /FPGA quickly ? EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

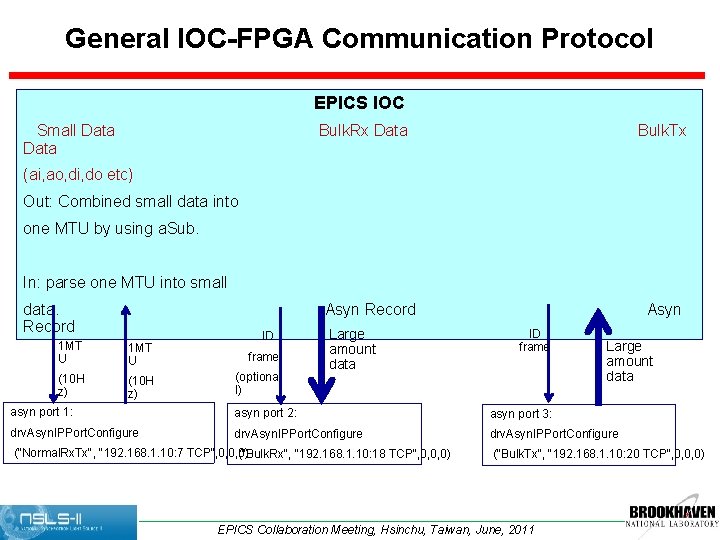

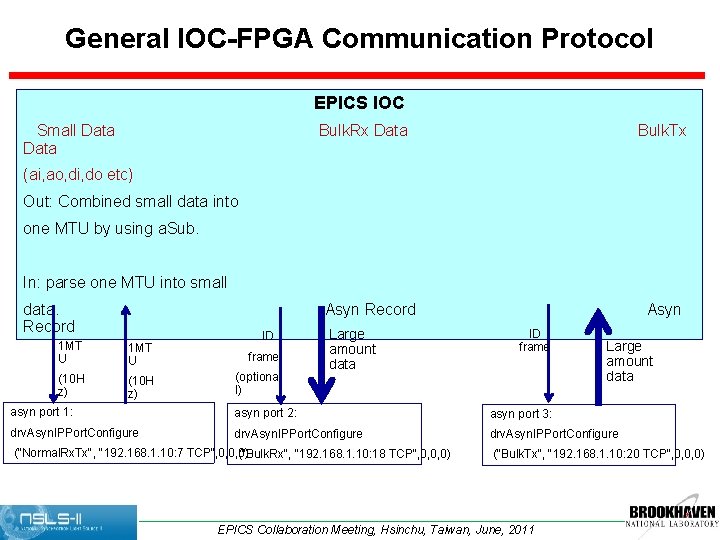

General IOC-FPGA Communication Protocol EPICS IOC Small Data Bulk. Rx Data Bulk. Tx (ai, ao, di, do etc) Out: Combined small data into one MTU by using a. Sub. In: parse one MTU into small data. Record Asyn Record ID 1 MT U frame (10 H z) (optiona l) Large amount data Asyn ID frame Large amount data asyn port 1: asyn port 2: asyn port 3: drv. Asyn. IPPort. Configure (“Normal. Rx. Tx", "192. 168. 1. 10: 7 TCP", 0, 0, 0) (“Bulk. Rx", "192. 168. 1. 10: 18 TCP", 0, 0, 0) (“Bulk. Tx", "192. 168. 1. 10: 20 TCP", 0, 0, 0) EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

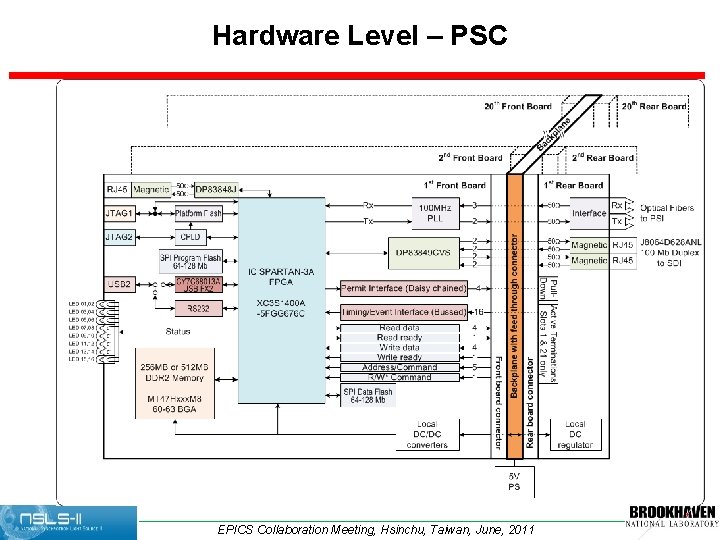

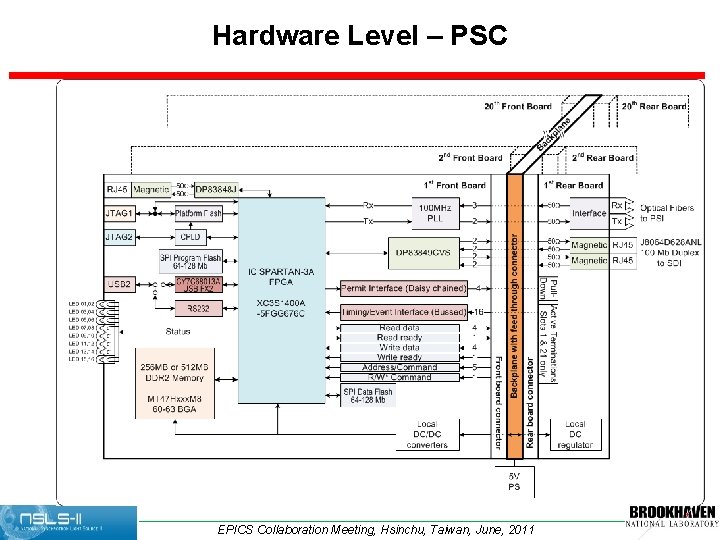

Hardware Level – PSC EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

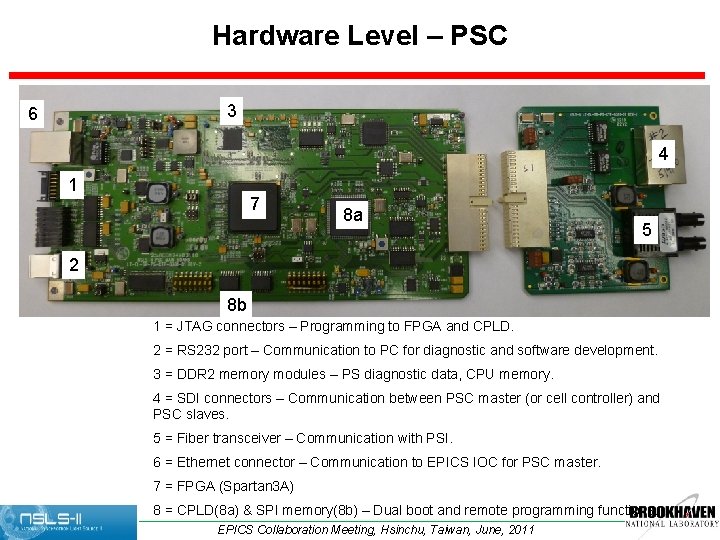

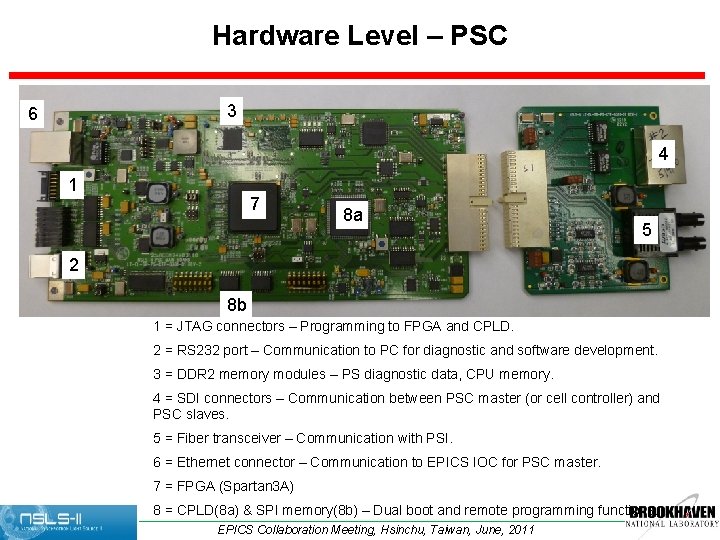

Hardware Level – PSC 3 6 4 1 7 7 a 8 a 5 2 8 b 1 = JTAG connectors – Programming to FPGA and CPLD. 2 = RS 232 port – Communication to PC for diagnostic and software development. 3 = DDR 2 memory modules – PS diagnostic data, CPU memory. 4 = SDI connectors – Communication between PSC master (or cell controller) and PSC slaves. 5 = Fiber transceiver – Communication with PSI. 6 = Ethernet connector – Communication to EPICS IOC for PSC master. 7 = FPGA (Spartan 3 A) 8 = CPLD(8 a) & SPI memory(8 b) – Dual boot and remote programming functions. EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

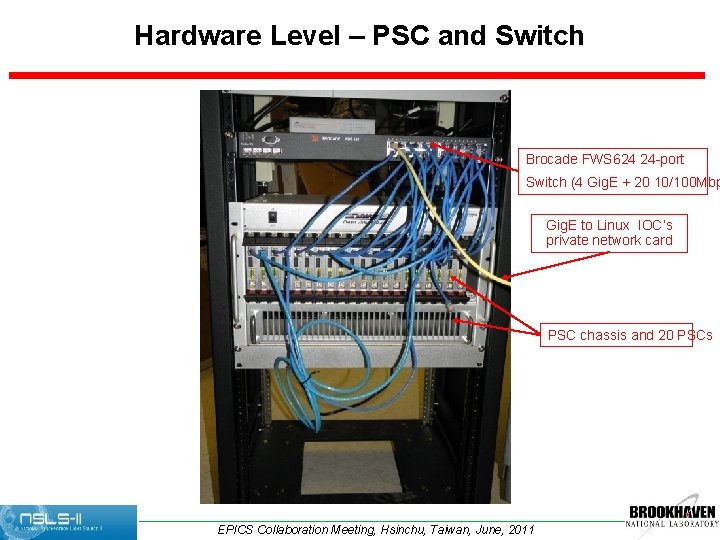

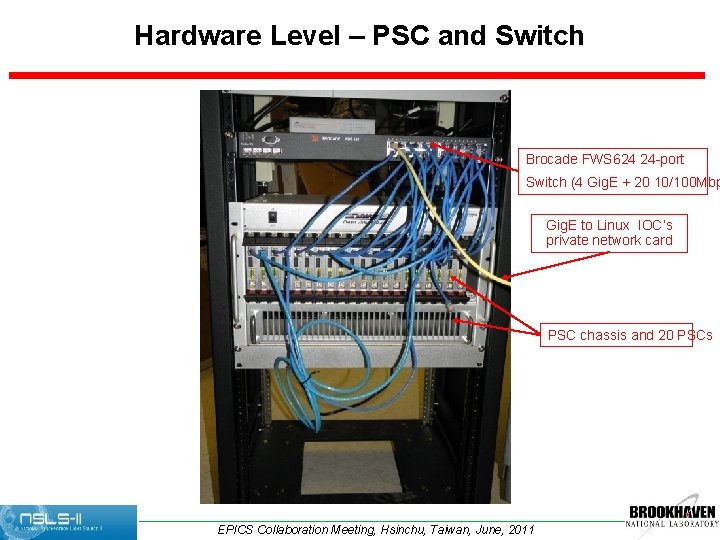

Hardware Level – PSC and Switch Brocade FWS 624 24 -port Switch (4 Gig. E + 20 10/100 Mbp Gig. E to Linux IOC’s private network card PSC chassis and 20 PSCs EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

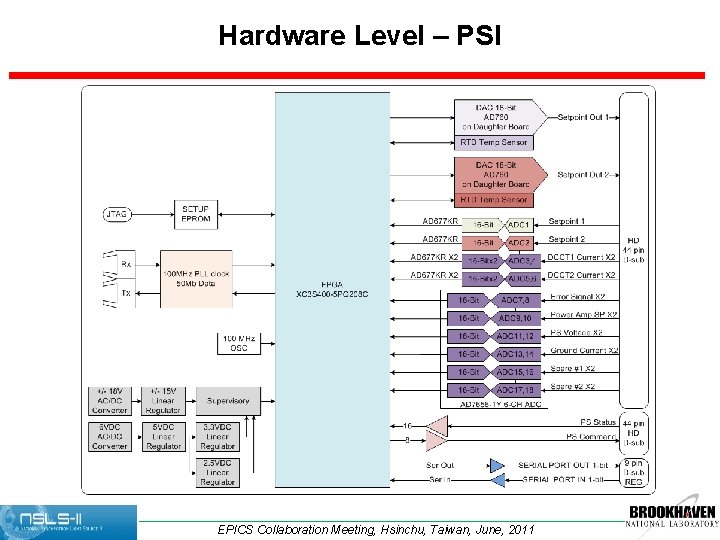

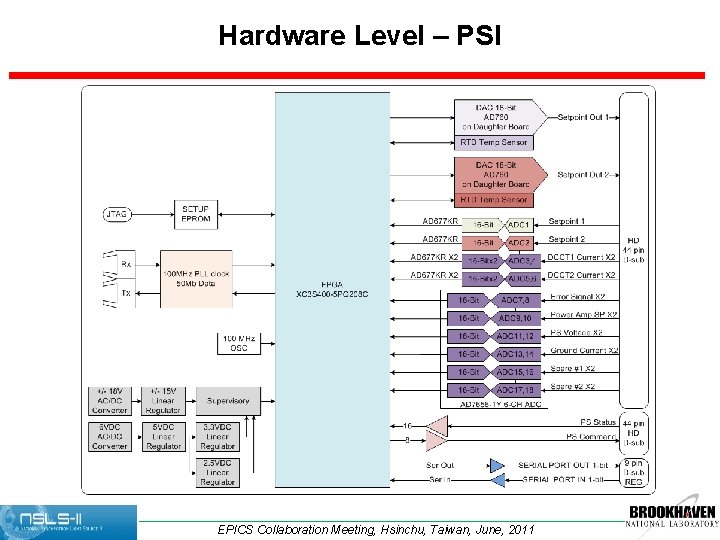

Hardware Level – PSI EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

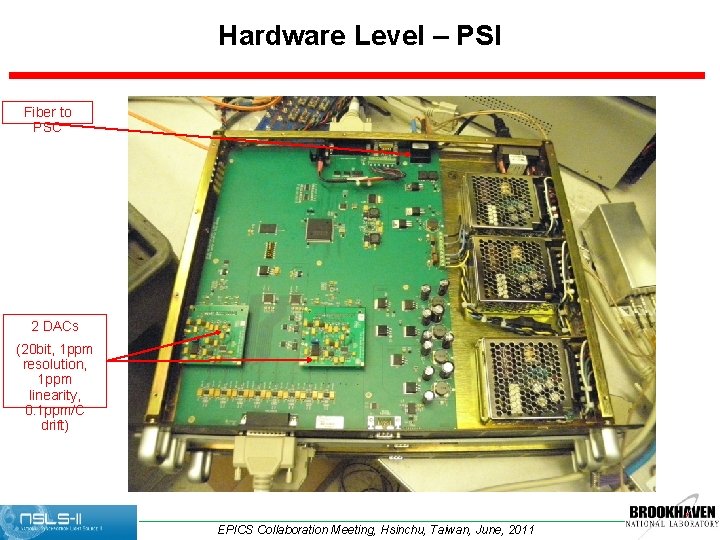

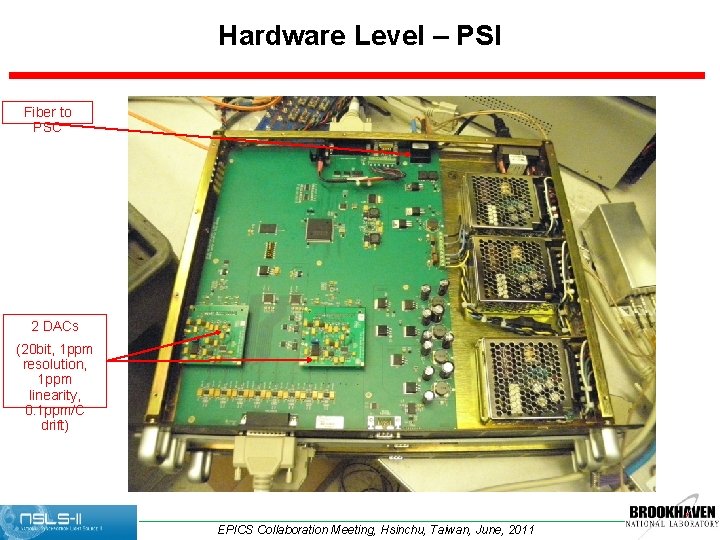

Hardware Level – PSI Fiber to PSC 2 DACs (20 bit, 1 ppm resolution, 1 ppm linearity, 0. 1 ppm/C drift) EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

NSLS-II power supply control system Want it ? You got it. NSLS-II power supply control system is a open source hardware. EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011

Summary 1. Accelerator power supply control is the common task for each laboratory. It has similar requirements, and thus the similar architectures. 2. NSLS-II power supply control system design is based on the experiences from both power supply group and control group. 3. All the NSLS-II power supply control hardwires are in production stage. FPGA firmware and EPICS driver/applications are being tested on Booster and storage ring magnets. 4. NSLS-II power supply control system is a open source hardware. The PCB design, FPGA firmware design, and EPICS Collaboration Meeting, Hsinchu, Taiwan, June, 2011