Moores Law Gordon Moore cofounder of Intel n

- Slides: 32

Moore’s Law Gordon Moore: co-founder of Intel. n Predicted that number of transistors per chip would grow exponentially (double every 18 months). n Exponential improvement in technology is a natural trend: steam engines, dynamos, automobiles. n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

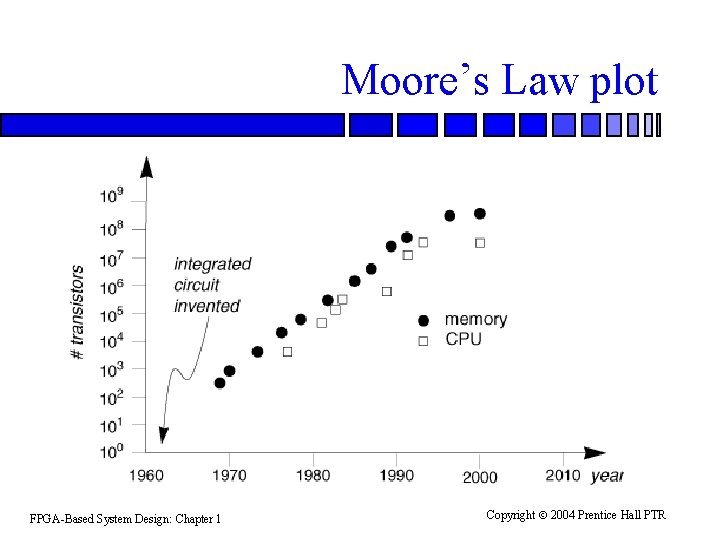

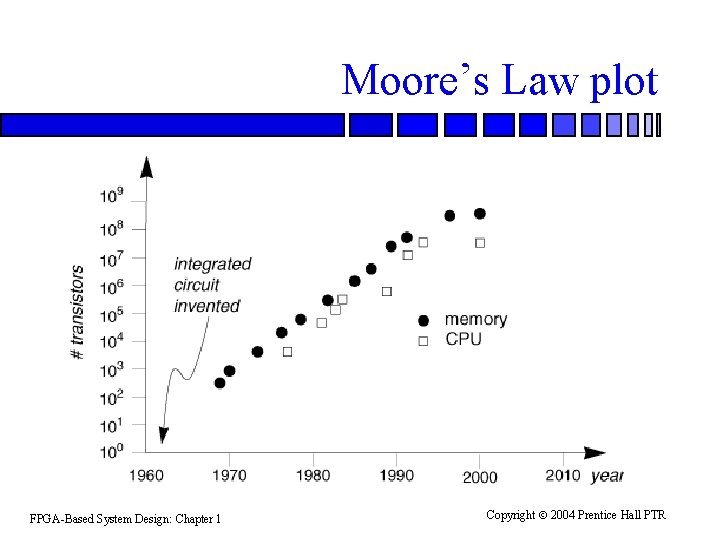

Moore’s Law plot FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

The cost of fabrication Current cost: $2 -3 billion. n Typical fab line occupies about 1 city block, employs a few hundred people. n New fabrication processes require 6 -8 month turnaround. n Most profitable period is first 18 months-2 years. n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Cost factors in ICs n For large-volume ICs: – packaging is largest cost; – testing is second-largest cost. n For low-volume ICs, design costs may swamp all manufacturing costs. – $10 million-$20 million. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

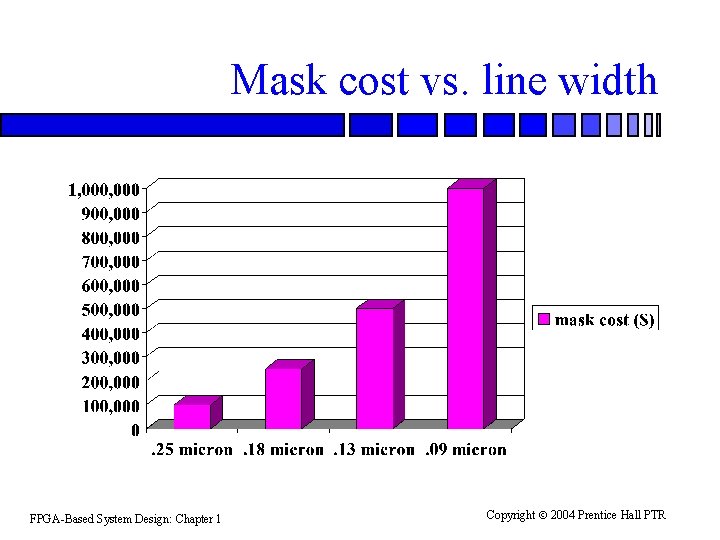

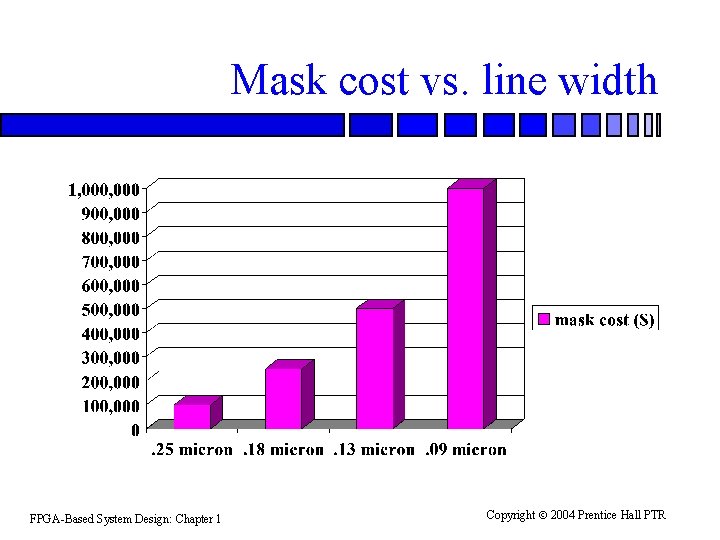

Mask cost vs. line width FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

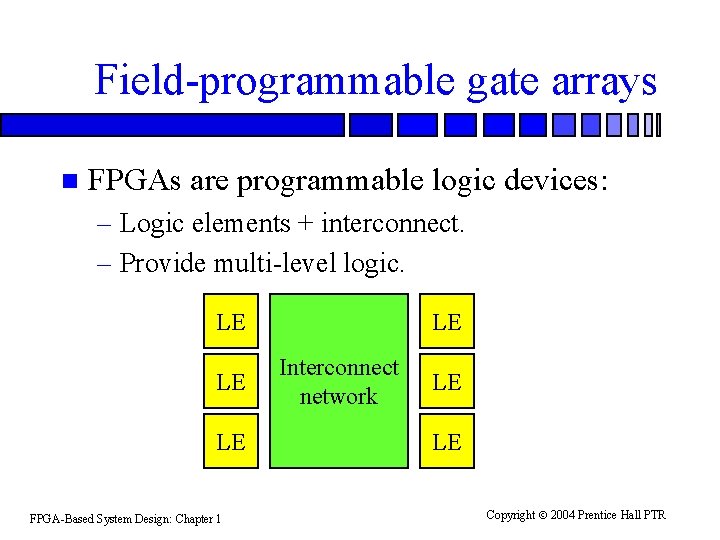

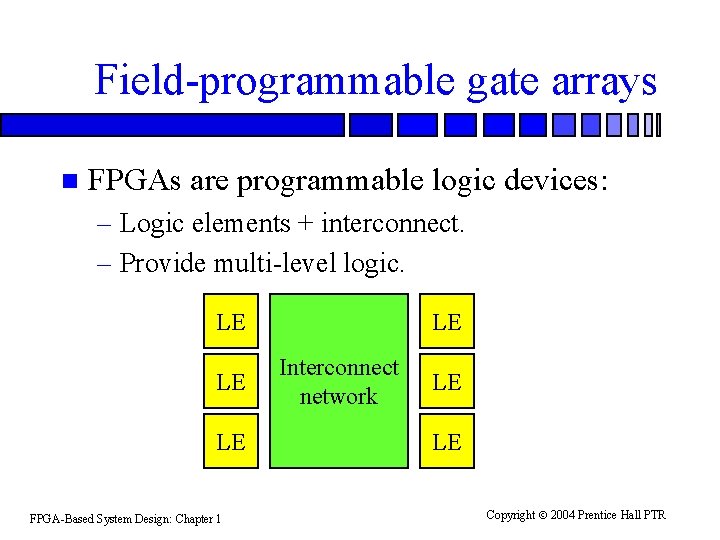

Field-programmable gate arrays n FPGAs are programmable logic devices: – Logic elements + interconnect. – Provide multi-level logic. LE LE LE FPGA-Based System Design: Chapter 1 LE Interconnect network LE LE Copyright 2004 Prentice Hall PTR

FPGAs and VLSI n FPGAs are standard parts: – Pre-manufactured. – Don’t worry (much) about physical design. n Custom silicon: – Tailored to your application. – Generally lower power consumption. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Standard parts vs. custom n Do you build your system with an FPGA or with custom silicon? – FPGAs have shorter design cycle. – FPGAs have no manufacturing delay. – FPGAs reduce inventory. – FPGAs are slower, larger, more power-hungry. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Challenges in system design Multiple levels of abstraction: logic to CPUs. n Multiple and conflicting constraints: low cost and high performance are often at odds. n Short design time: Late products are often irrelevant. n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

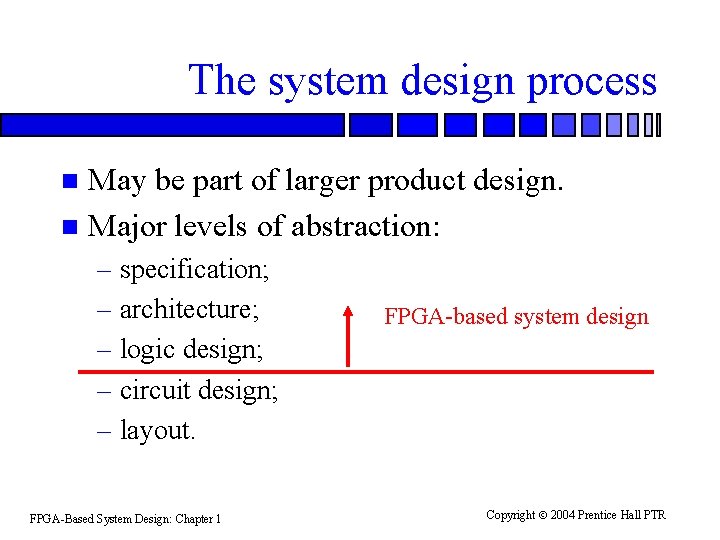

The system design process May be part of larger product design. n Major levels of abstraction: n – specification; – architecture; – logic design; – circuit design; – layout. FPGA-Based System Design: Chapter 1 FPGA-based system design Copyright 2004 Prentice Hall PTR

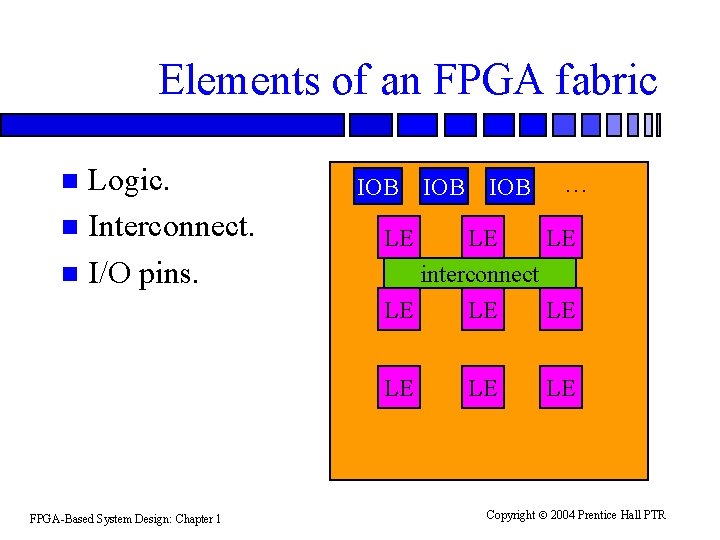

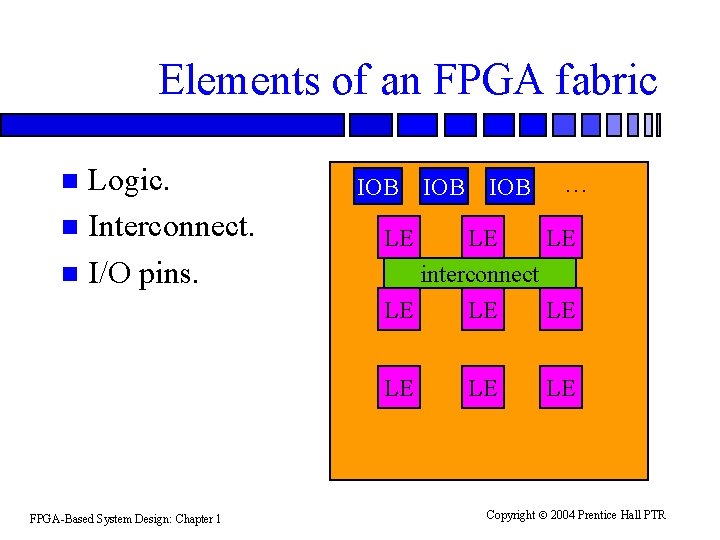

Elements of an FPGA fabric Logic. n Interconnect. n I/O pins. n IOB LE … LE interconnect LE LE LE … LE FPGA-Based System Design: Chapter 1 IOB LE LE Copyright 2004 Prentice Hall PTR

Terminology Configuration: bits that determine logic function + interconnect. n CLB: combinational logic block = logic element (LE). n LUT: Lookup table = SRAM used for truth table. n I/O block (IOB): I/O pin + associated logic and electronics. n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

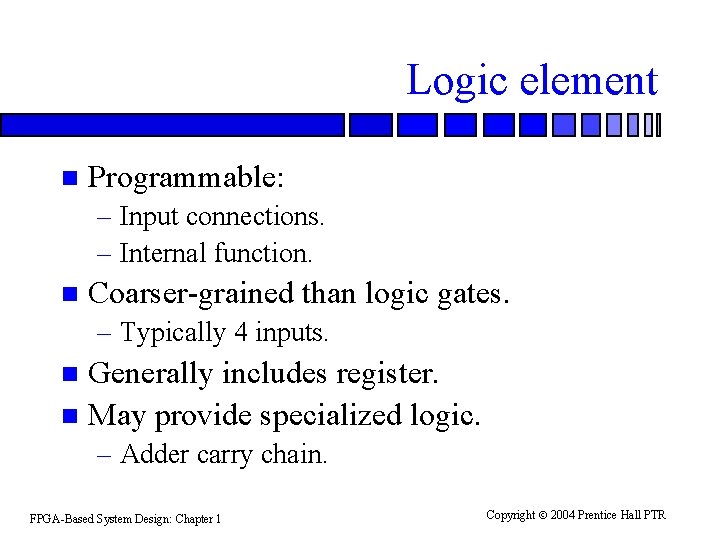

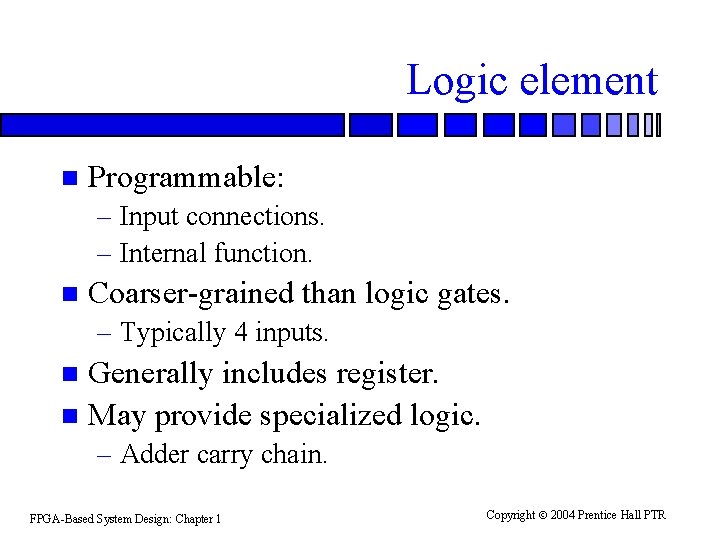

Logic element n Programmable: – Input connections. – Internal function. n Coarser-grained than logic gates. – Typically 4 inputs. Generally includes register. n May provide specialized logic. n – Adder carry chain. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

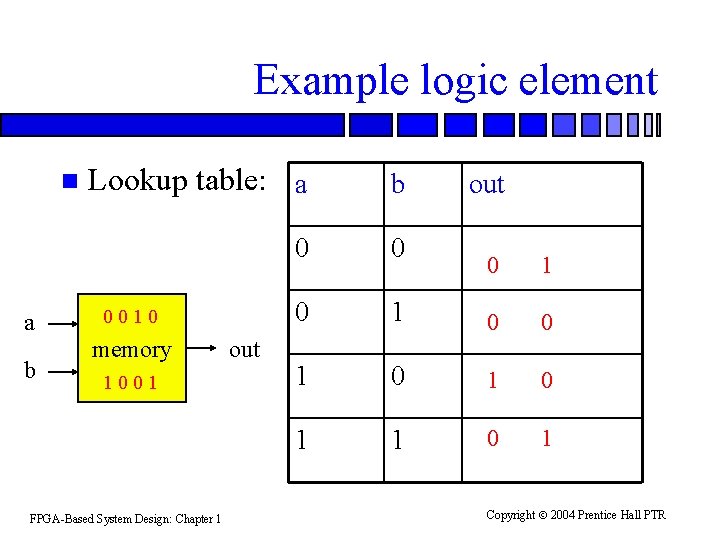

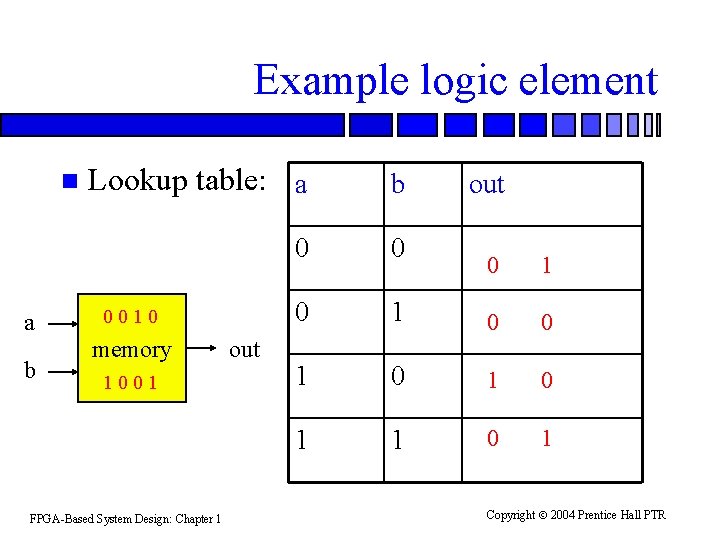

Example logic element n a b Lookup table: a b 0 0010 memory 1001 FPGA-Based System Design: Chapter 1 out 0 1 1 0 0 1 0 1 Copyright 2004 Prentice Hall PTR

Logic synthesis How do we break the function into logic elements? n How do we implement an operation within a logic element? n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

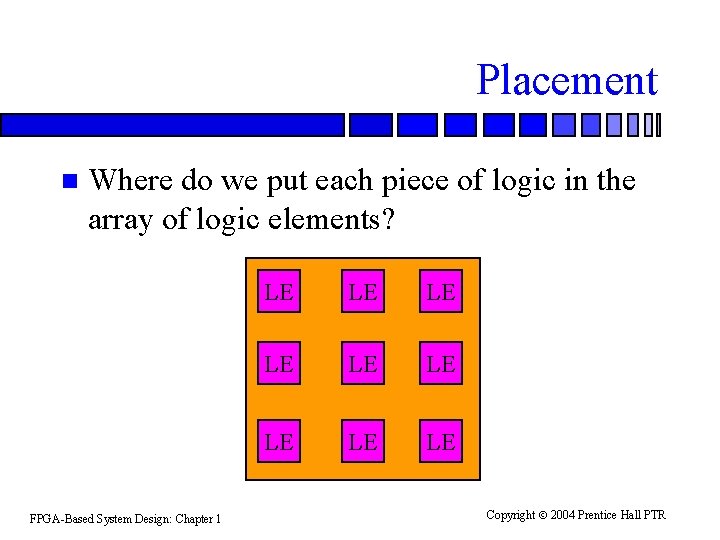

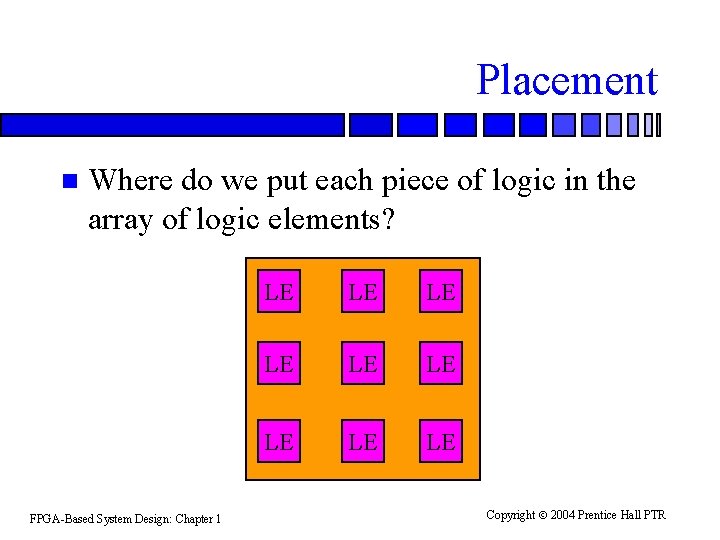

Placement n Where do we put each piece of logic in the array of logic elements? FPGA-Based System Design: Chapter 1 LE LE LE … LE LE Copyright 2004 Prentice Hall PTR

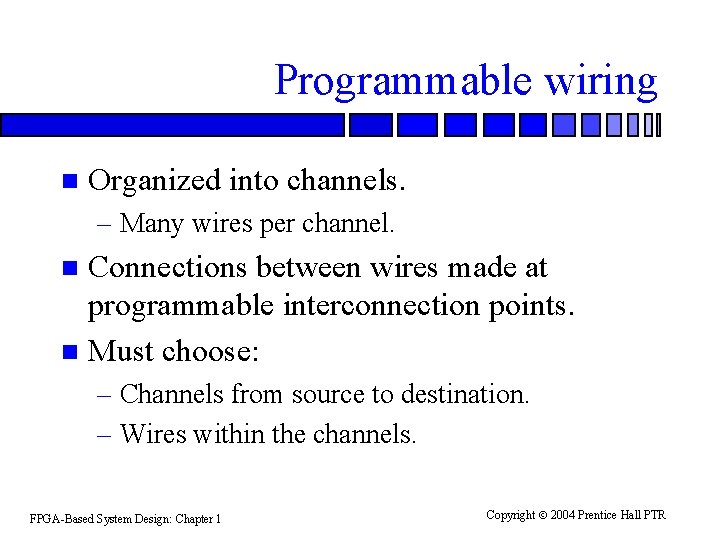

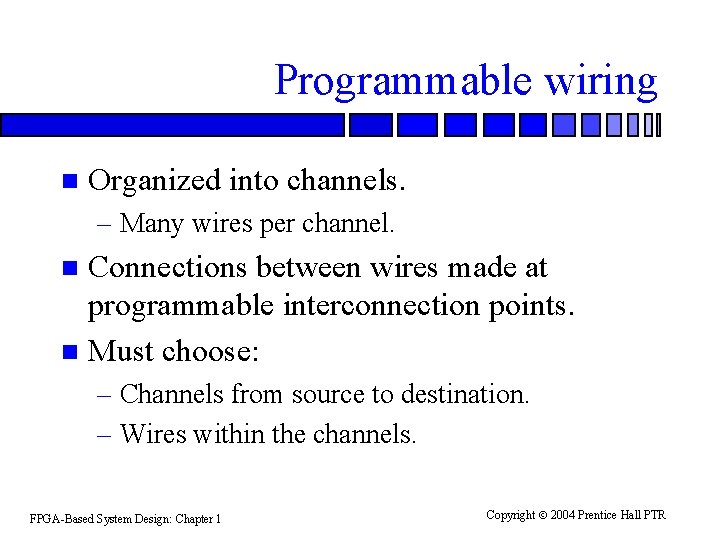

Programmable wiring n Organized into channels. – Many wires per channel. Connections between wires made at programmable interconnection points. n Must choose: n – Channels from source to destination. – Wires within the channels. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

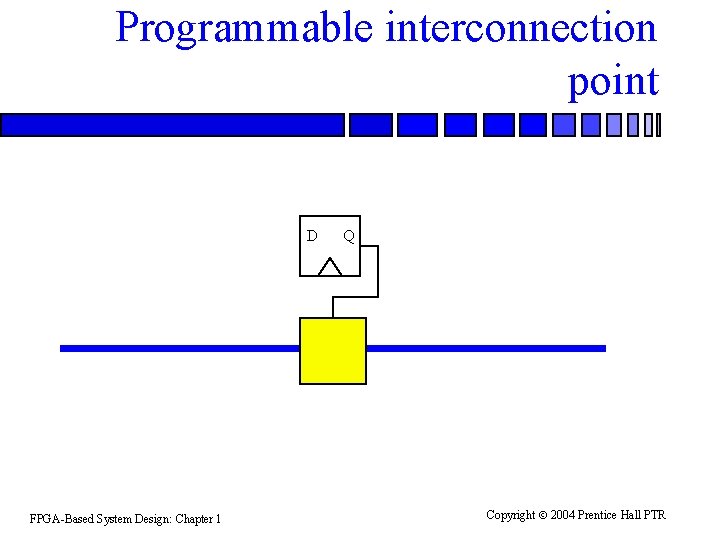

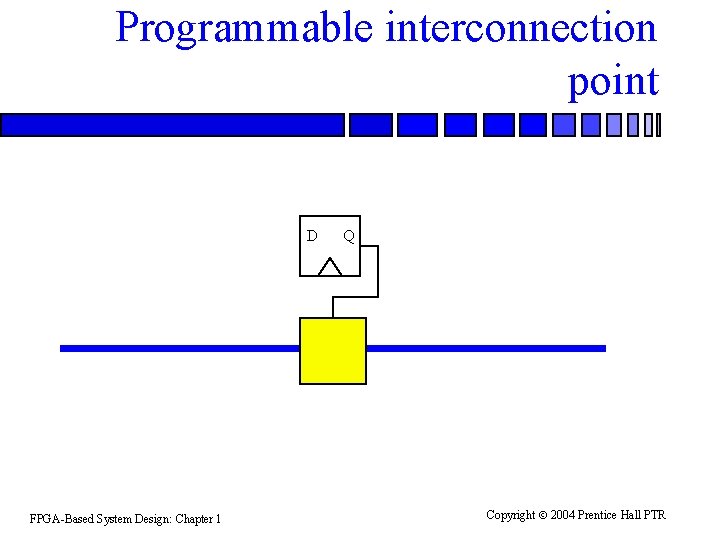

Programmable interconnection point D FPGA-Based System Design: Chapter 1 Q Copyright 2004 Prentice Hall PTR

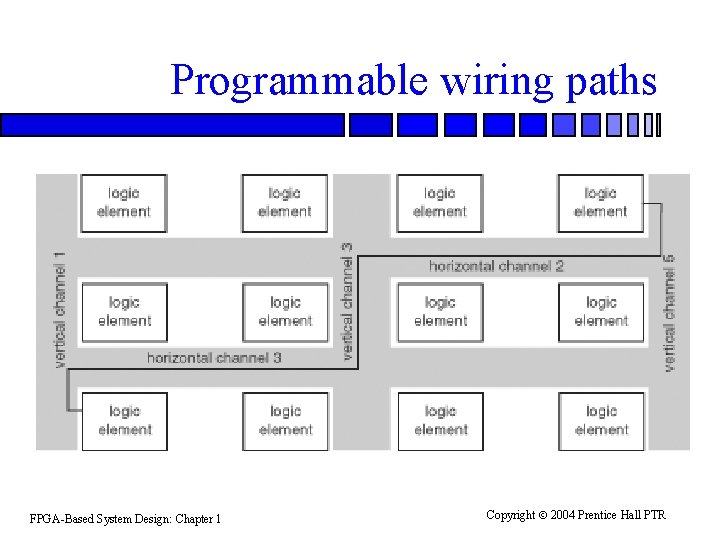

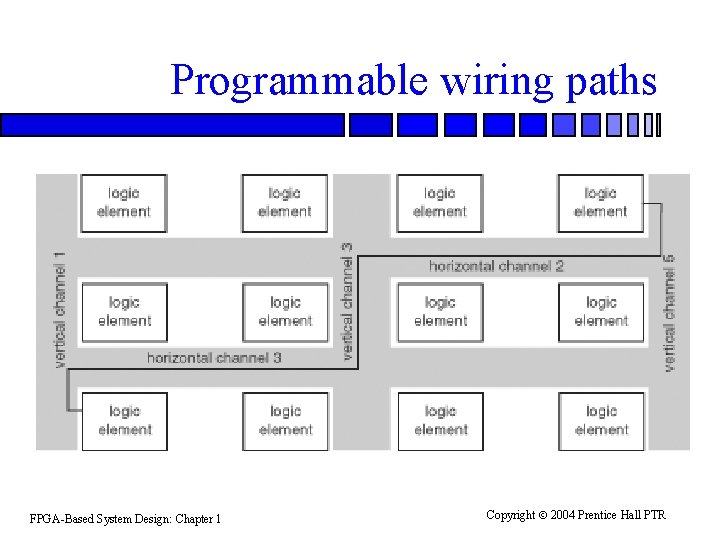

Programmable wiring paths FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

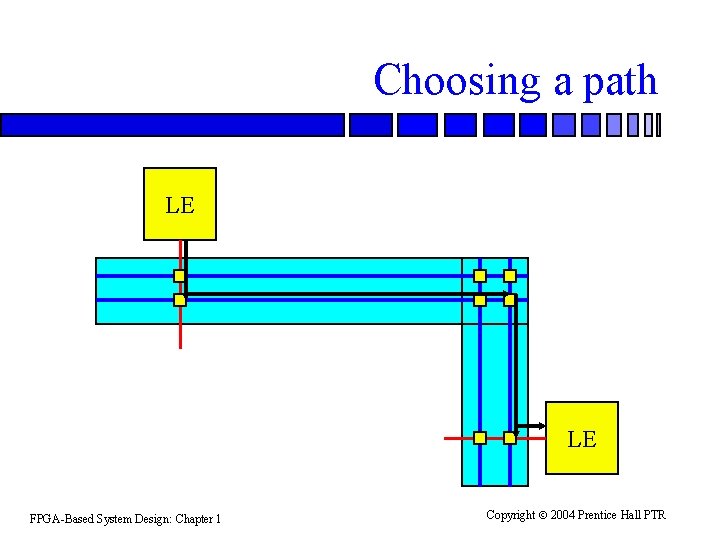

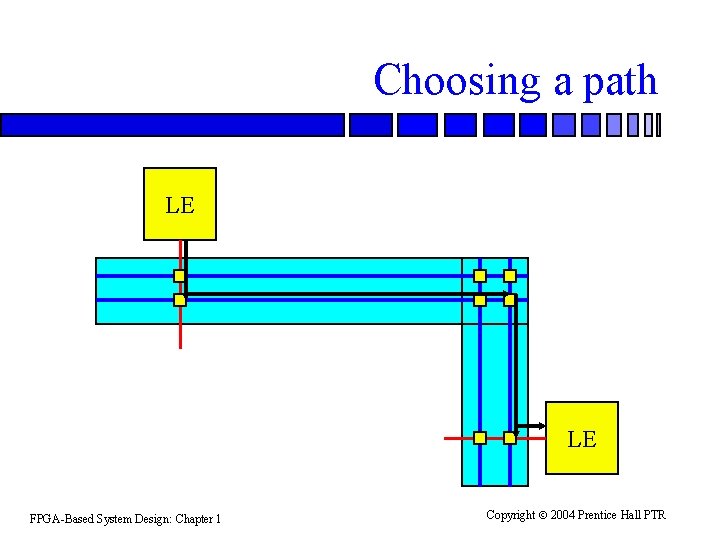

Choosing a path LE LE FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

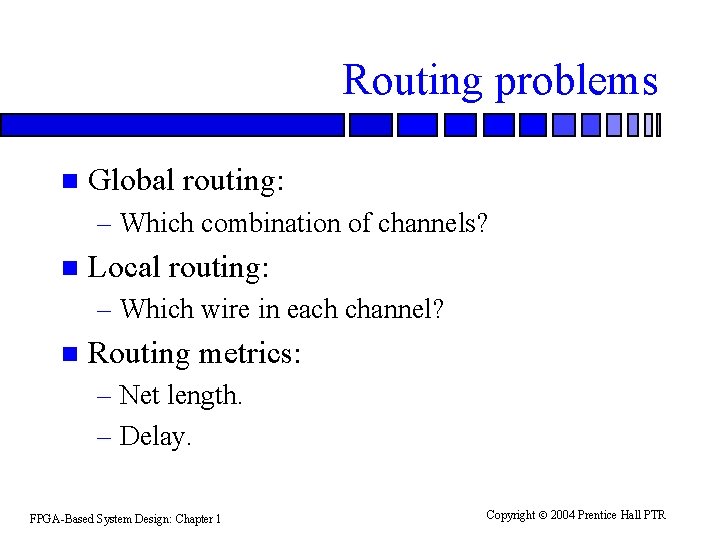

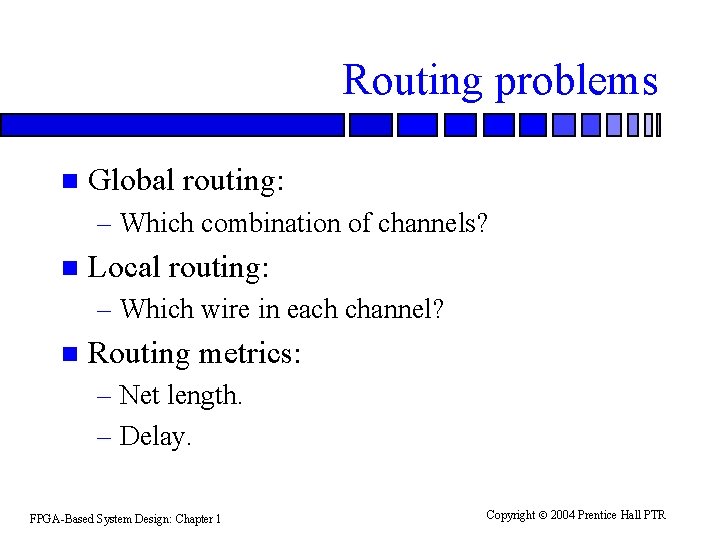

Routing problems n Global routing: – Which combination of channels? n Local routing: – Which wire in each channel? n Routing metrics: – Net length. – Delay. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

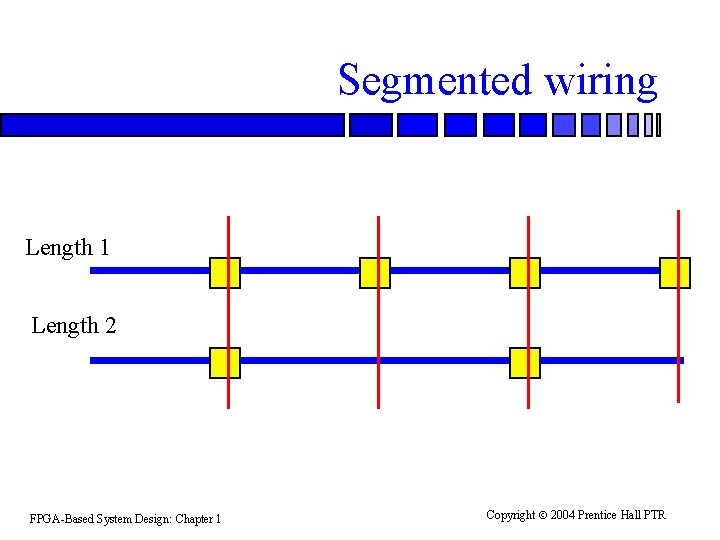

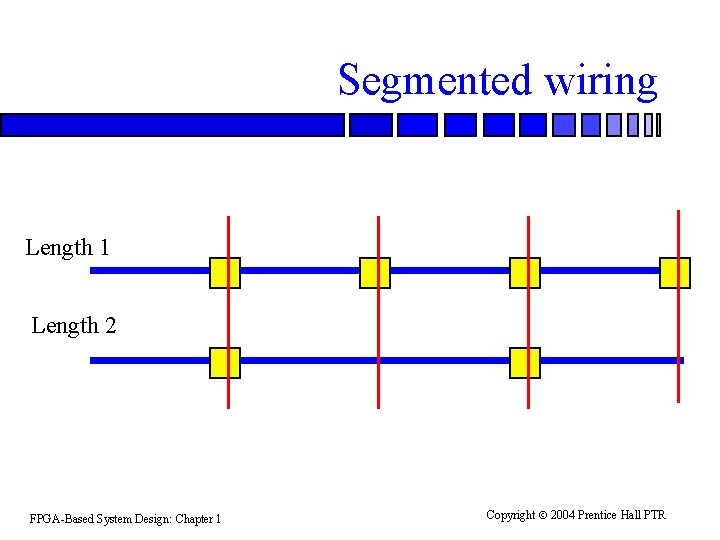

Segmented wiring Length 1 Length 2 FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

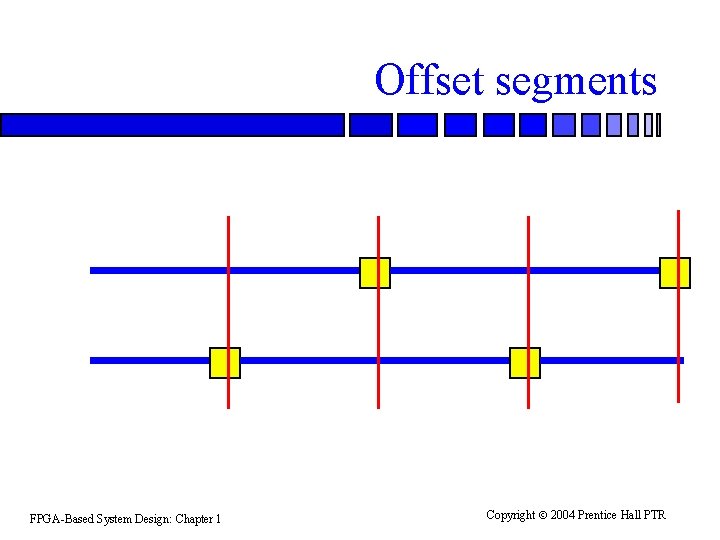

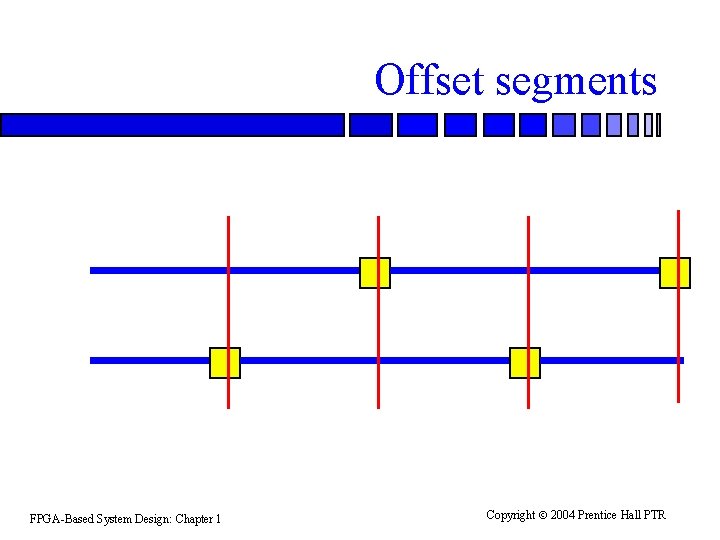

Offset segments FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

I/O Fundamental selection: input, output, threestate? n Additional features: n – Register. – Voltage levels. – Slew rate. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Programming technologies n SRAM. – Can be programmed many times. – Must be programmed at power-up. n Antifuse. – Programmed once. n Flash. – Similar to SRAM but using flash memory. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Configuration n Must set control bits for: – LE. – Interconnect. – I/O blocks. n Usually configured off-line. – Separate burn-in step (antifuse). – At power-up (SRAM). FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

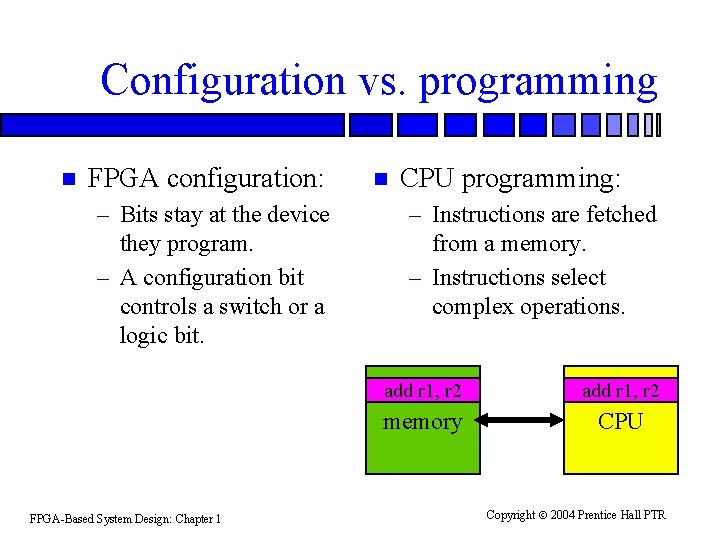

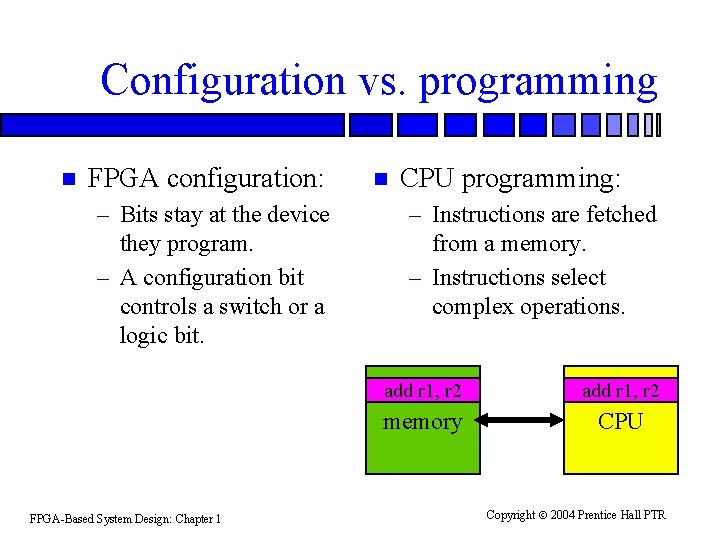

Configuration vs. programming n FPGA configuration: – Bits stay at the device they program. – A configuration bit controls a switch or a logic bit. FPGA-Based System Design: Chapter 1 n CPU programming: – Instructions are fetched from a memory. – Instructions select complex operations. add r 1, r 2 add. IR r 1, r 2 memory CPU Copyright 2004 Prentice Hall PTR

Reconfiguration n Some FPGAs are designed for fast configuration. – A few clock cycles, not thousands of clock cycles. n Allows hardware to be changed on-the-fly. FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

FPGA fabric architecture questions n Given limited area budget: – How many logic elements? – How much interconnect? – How many I/O blocks? FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Logic element questions How many inputs? n How many functions? n – All functions of n inputs or eliminate some combinations? – What inputs go to what pieces of the function? n Any specialized logic? – Adder, etc. n What register features? FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

Interconnect questions How many wires in each channel? n Uniform distribution of wiring? n How should wires be segmented? n How rich is interconnect between channels? n How long is the average wire? n How much buffering do we add to wires? n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR

I/O block questions n How many pins? – Maximum number of pins determined by package type. Are pins programmed individually or in groups? n Can all pins perform all functions? n How many logic families do we support? n FPGA-Based System Design: Chapter 1 Copyright 2004 Prentice Hall PTR