Lecture 11 Memory Design Prith Banerjee ECE C

Lecture 11 Memory Design Prith Banerjee ECE C 03 Advanced Digital Design Spring 1998 ECE C 03 Lecture 11 1

Outline • • • Random Access Memories (RAMS) Static RAMs Dynamic RAMS Memory Organizations Read-Only Memories (ROMS) READING: Katz 7. 6, 4. 2. 5 ECE C 03 Lecture 11 2

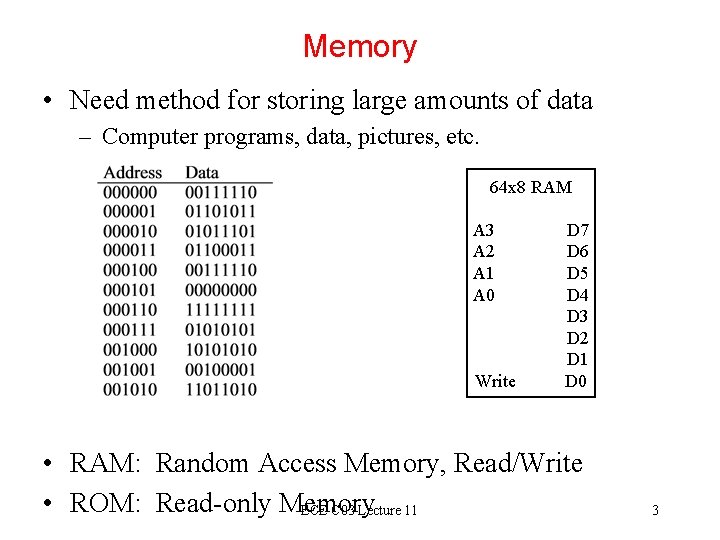

Memory • Need method for storing large amounts of data – Computer programs, data, pictures, etc. 64 x 8 RAM A 3 A 2 A 1 A 0 Write D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 • RAM: Random Access Memory, Read/Write • ROM: Read-only Memory ECE C 03 Lecture 11 3

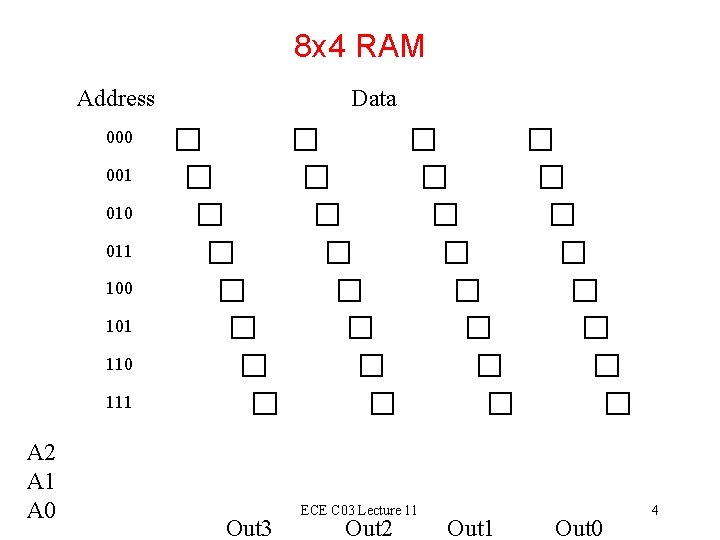

8 x 4 RAM Address Data 000 001 010 011 100 101 110 111 A 2 A 1 A 0 Out 3 ECE C 03 Lecture 11 Out 2 Out 1 Out 0 4

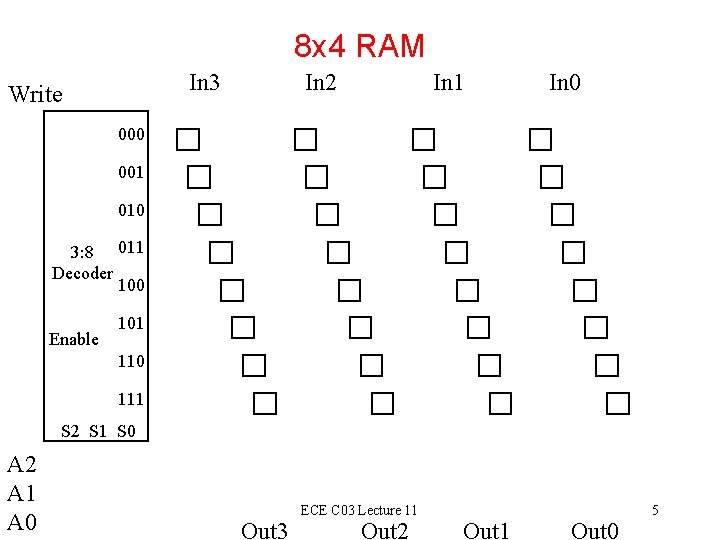

8 x 4 RAM In 3 Write In 2 In 1 In 0 001 010 3: 8 011 Decoder 100 Enable 101 110 111 S 2 S 1 S 0 A 2 A 1 A 0 Out 3 ECE C 03 Lecture 11 Out 2 Out 1 Out 0 5

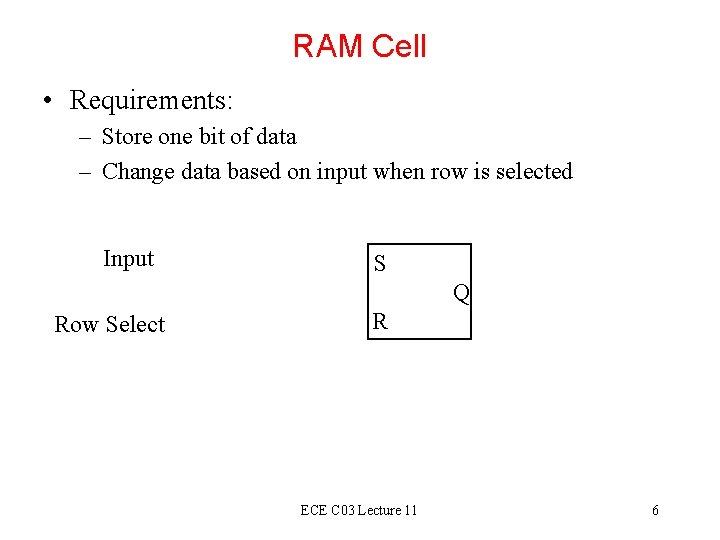

RAM Cell • Requirements: – Store one bit of data – Change data based on input when row is selected Input S Q Row Select R ECE C 03 Lecture 11 6

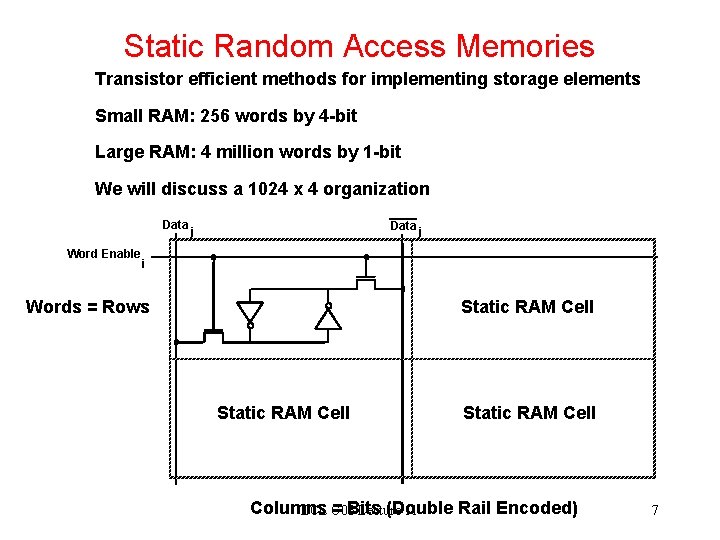

Static Random Access Memories Transistor efficient methods for implementing storage elements Small RAM: 256 words by 4 -bit Large RAM: 4 million words by 1 -bit We will discuss a 1024 x 4 organization Data Word Enable Data j j i Words = Rows Static RAM Cell Columns = Bits (Double Rail Encoded) ECE C 03 Lecture 11 7

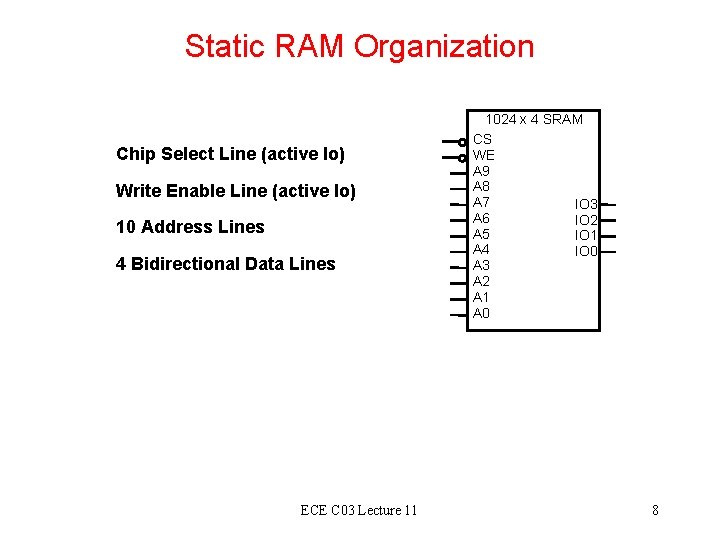

Static RAM Organization Chip Select Line (active lo) Write Enable Line (active lo) 10 Address Lines 4 Bidirectional Data Lines ECE C 03 Lecture 11 1024 x 4 SRAM CS WE A 9 A 8 A 7 IO 3 A 6 IO 2 A 5 IO 1 A 4 IO 0 A 3 A 2 A 1 A 0 8

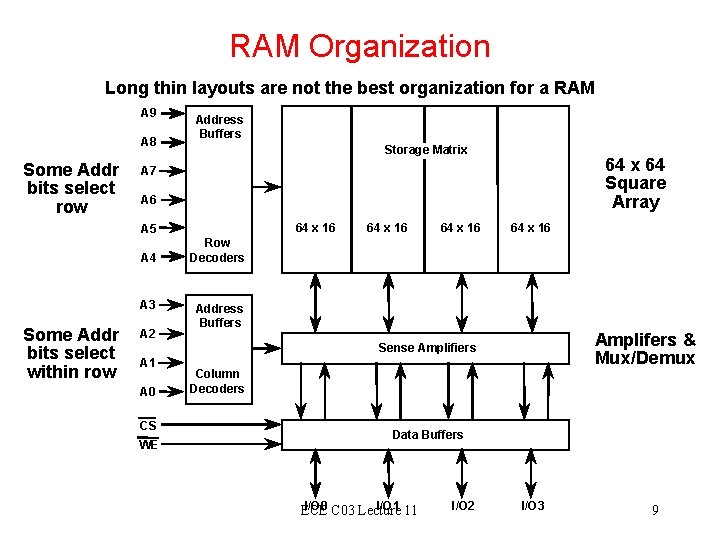

RAM Organization Long thin layouts are not the best organization for a RAM A 9 A 8 Some Addr bits select row Address Buffers Storage Matrix Array A 6 64 x 16 A 5 A 4 A 3 Some Addr bits select within row 64 x 64 Square Array A 7 A 2 64 x 16 Row Decoders Address Buffers Amplifers & Mux/Demux Sense Amplifiers A 1 A 0 CS WE Column Decoders Data Buffers I/O 0 C 03 Lecture I/O 1 11 ECE I/O 2 I/O 3 9

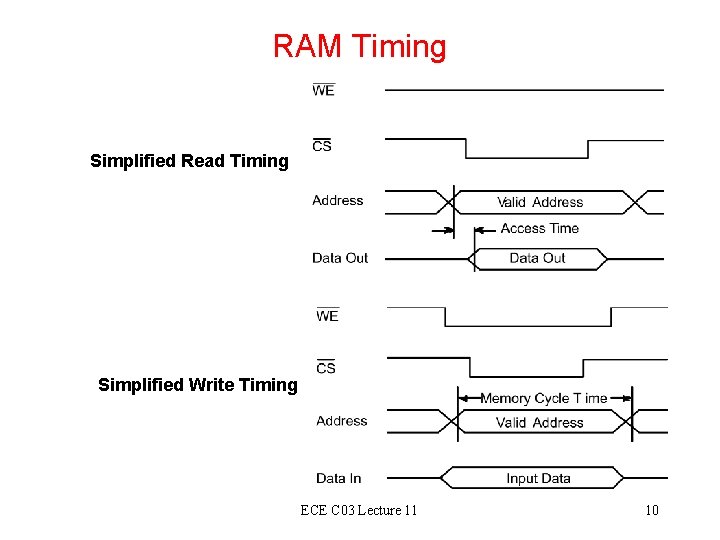

RAM Timing Simplified Read Timing Simplified Write Timing ECE C 03 Lecture 11 10

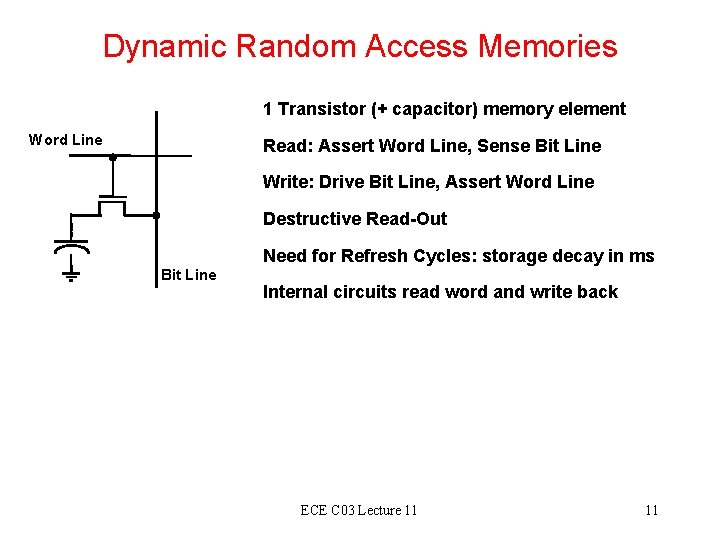

Dynamic Random Access Memories 1 Transistor (+ capacitor) memory element Word Line Read: Assert Word Line, Sense Bit Line Write: Drive Bit Line, Assert Word Line Destructive Read-Out Need for Refresh Cycles: storage decay in ms Bit Line Internal circuits read word and write back ECE C 03 Lecture 11 11

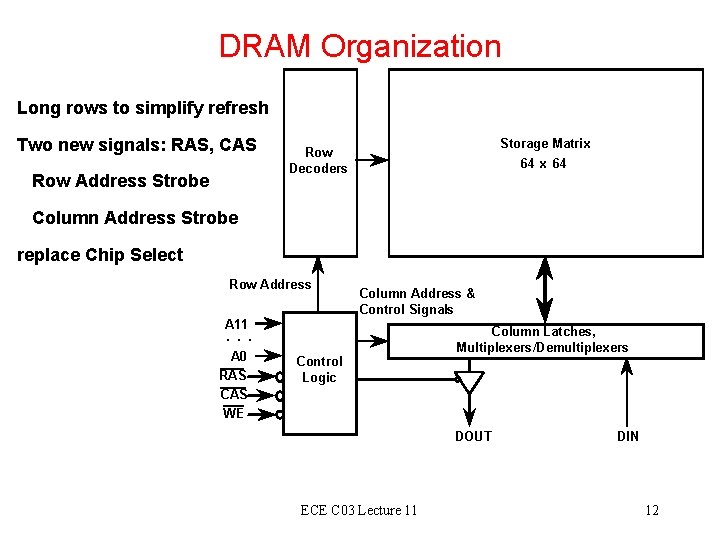

DRAM Organization Long rows to simplify refresh Two new signals: RAS, CAS Row Address Strobe Storage Matrix Row Decoders 64 x 64 Column Address Strobe replace Chip Select Row Address Column Address & Control Signals A 11. . . A 0 RAS CAS WE Control Logic Column Latches, Multiplexers/Demultiplexers DOUT ECE C 03 Lecture 11 DIN 12

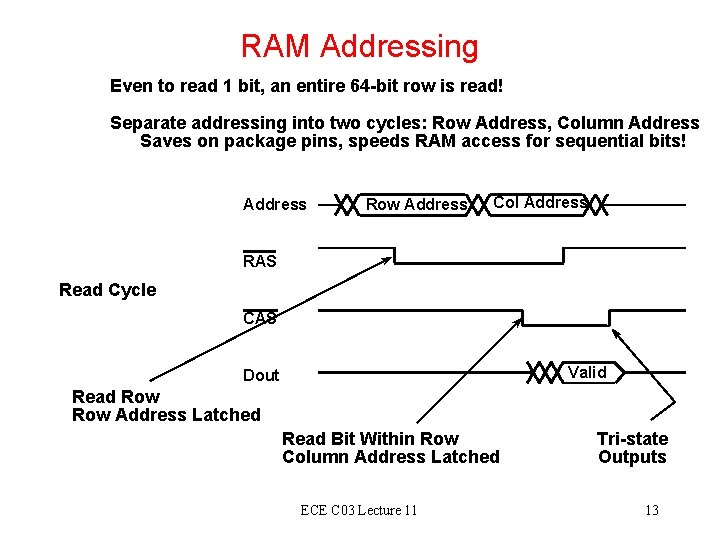

RAM Addressing Even to read 1 bit, an entire 64 -bit row is read! Separate addressing into two cycles: Row Address, Column Address Saves on package pins, speeds RAM access for sequential bits! Address Row Address Col Address RAS Read Cycle CAS Valid Dout Read Row Address Latched Read Bit Within Row Column Address Latched ECE C 03 Lecture 11 Tri-state Outputs 13

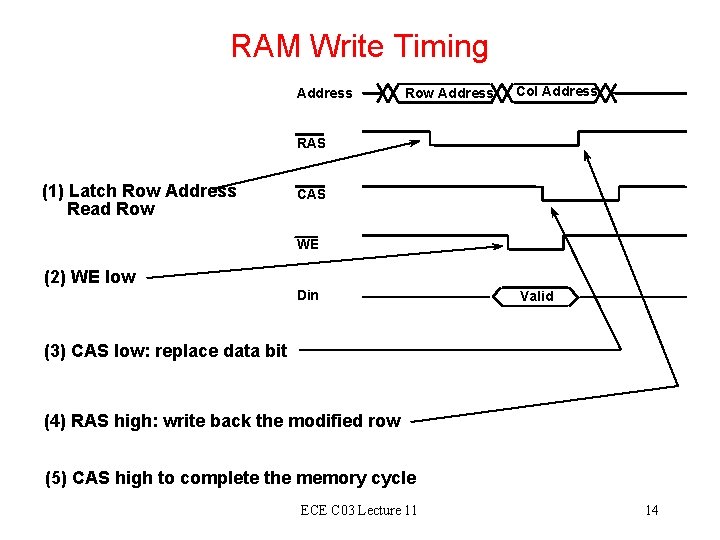

RAM Write Timing Address Row Address Col Address RAS (1) Latch Row Address Read Row CAS WE (2) WE low Din Valid (3) CAS low: replace data bit (4) RAS high: write back the modified row (5) CAS high to complete the memory cycle ECE C 03 Lecture 11 14

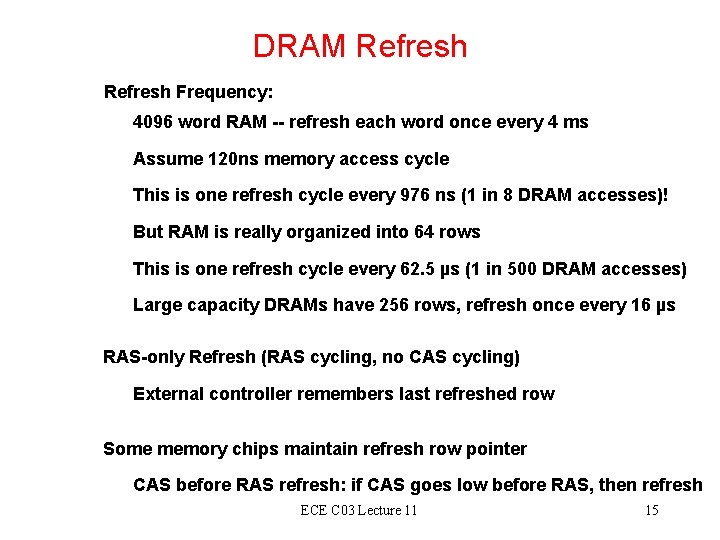

DRAM Refresh Frequency: 4096 word RAM -- refresh each word once every 4 ms Assume 120 ns memory access cycle This is one refresh cycle every 976 ns (1 in 8 DRAM accesses)! But RAM is really organized into 64 rows This is one refresh cycle every 62. 5 µs (1 in 500 DRAM accesses) Large capacity DRAMs have 256 rows, refresh once every 16 µs RAS-only Refresh (RAS cycling, no CAS cycling) External controller remembers last refreshed row Some memory chips maintain refresh row pointer CAS before RAS refresh: if CAS goes low before RAS, then refresh ECE C 03 Lecture 11 15

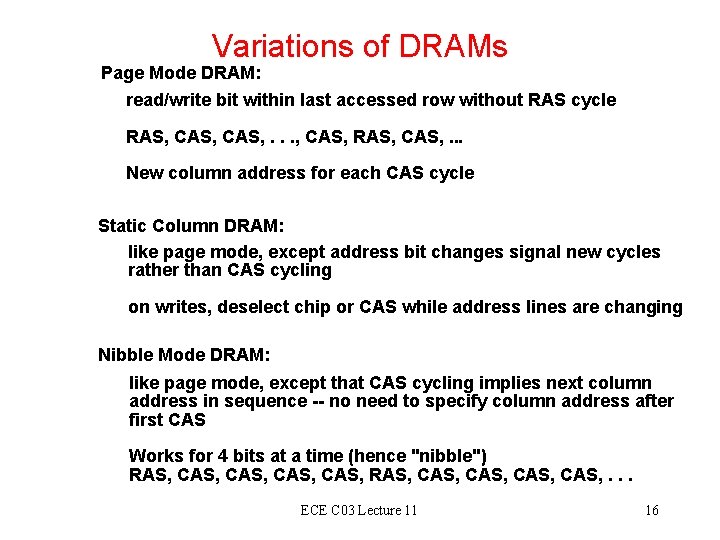

Variations of DRAMs Page Mode DRAM: read/write bit within last accessed row without RAS cycle RAS, CAS, . . . , CAS, RAS, CAS, . . . New column address for each CAS cycle Static Column DRAM: like page mode, except address bit changes signal new cycles rather than CAS cycling on writes, deselect chip or CAS while address lines are changing Nibble Mode DRAM: like page mode, except that CAS cycling implies next column address in sequence -- no need to specify column address after first CAS Works for 4 bits at a time (hence "nibble") RAS, CAS, CAS, . . . ECE C 03 Lecture 11 16

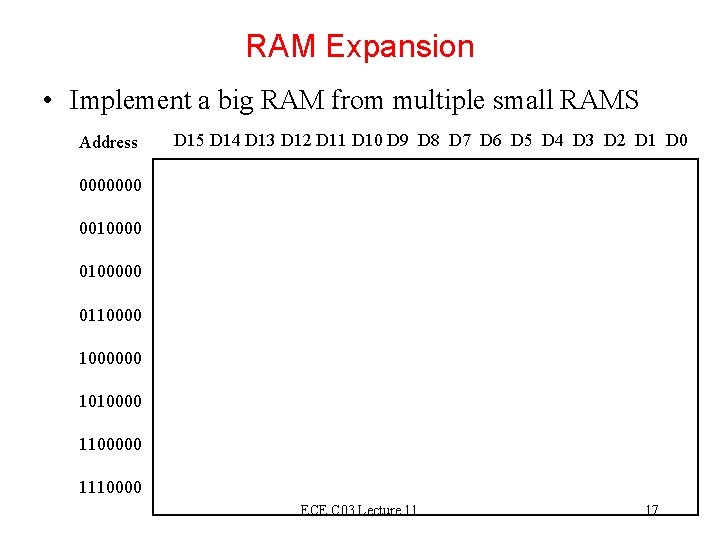

RAM Expansion • Implement a big RAM from multiple small RAMS Address D 15 D 14 D 13 D 12 D 11 D 10 D 9 D 8 D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 0000000 00100000 011000000 1010000 1100000 1110000 ECE C 03 Lecture 11 17

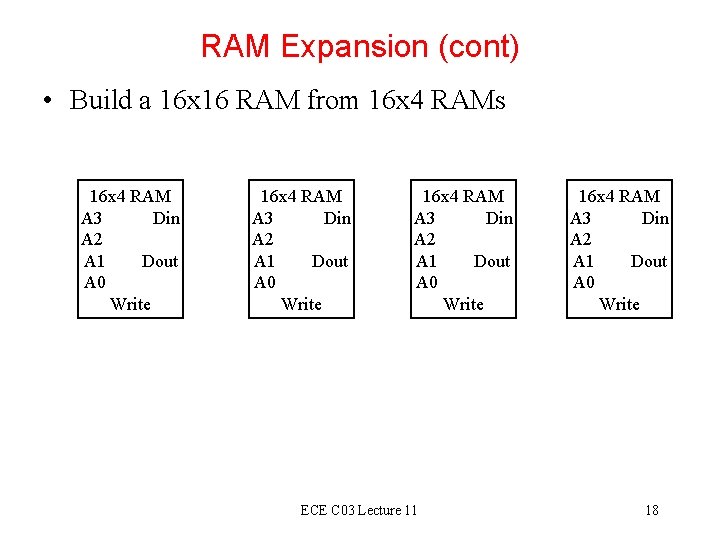

RAM Expansion (cont) • Build a 16 x 16 RAM from 16 x 4 RAMs 16 x 4 RAM A 3 Din A 2 A 1 Dout A 0 Write ECE C 03 Lecture 11 16 x 4 RAM A 3 Din A 2 A 1 Dout A 0 Write 18

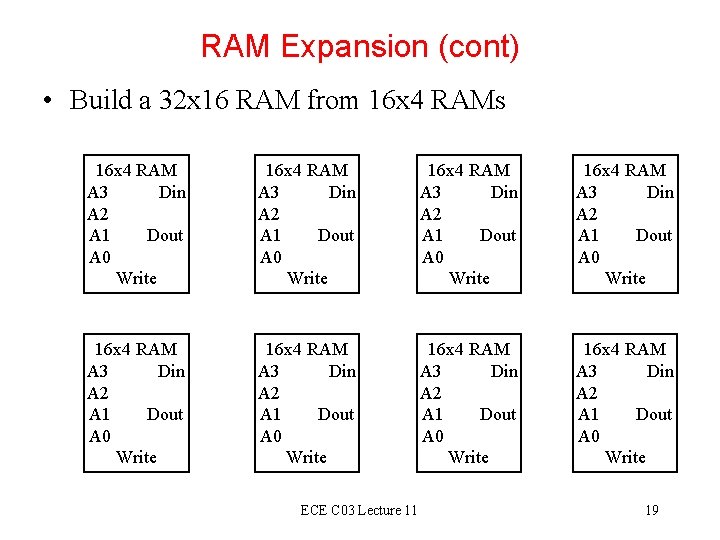

RAM Expansion (cont) • Build a 32 x 16 RAM from 16 x 4 RAMs 16 x 4 RAM A 3 Din A 2 A 1 Dout A 0 Write 16 x 4 RAM A 3 Din A 2 A 1 Dout A 0 Write ECE C 03 Lecture 11 19

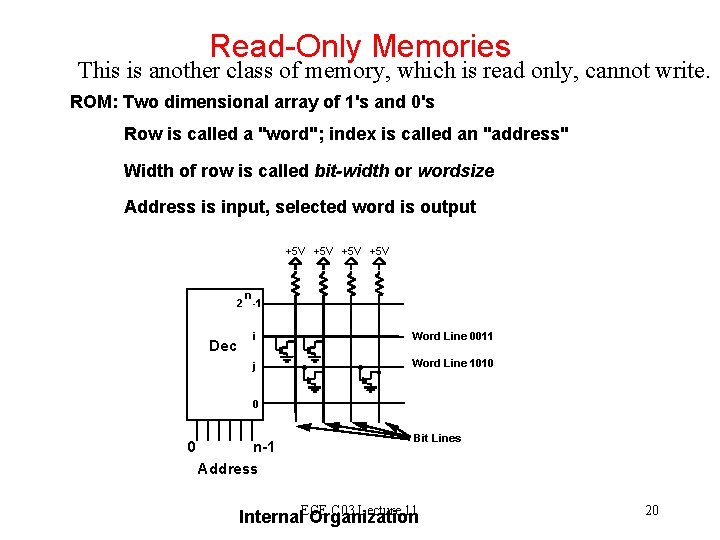

Read-Only Memories This is another class of memory, which is read only, cannot write. ROM: Two dimensional array of 1's and 0's Row is called a "word"; index is called an "address" Width of row is called bit-width or wordsize Address is input, selected word is output +5 V +5 V n 2 -1 Dec i Word Line 0011 j Word Line 1010 0 0 n-1 Address Bit Lines C 03 Lecture 11 Internal. ECE Organization 20

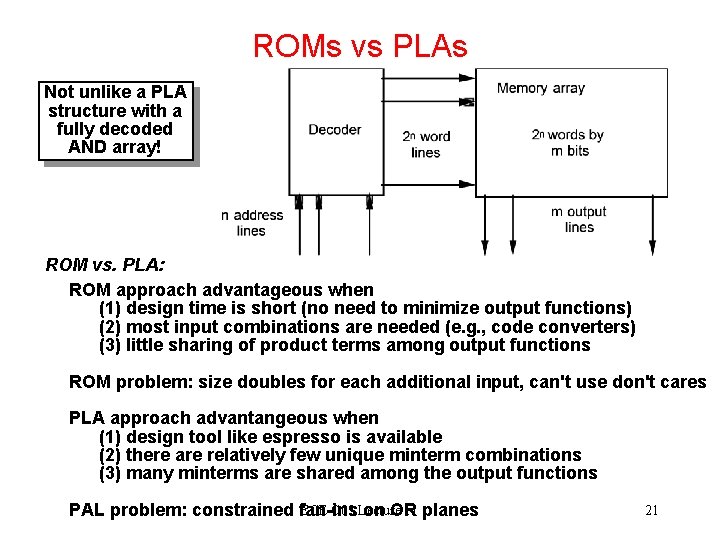

ROMs vs PLAs Not unlike a PLA structure with a fully decoded AND array! ROM vs. PLA: ROM approach advantageous when (1) design time is short (no need to minimize output functions) (2) most input combinations are needed (e. g. , code converters) (3) little sharing of product terms among output functions ROM problem: size doubles for each additional input, can't use don't cares PLA approach advantangeous when (1) design tool like espresso is available (2) there are relatively few unique minterm combinations (3) many minterms are shared among the output functions ECE C 03 Lecture 11 planes PAL problem: constrained fan-ins on OR 21

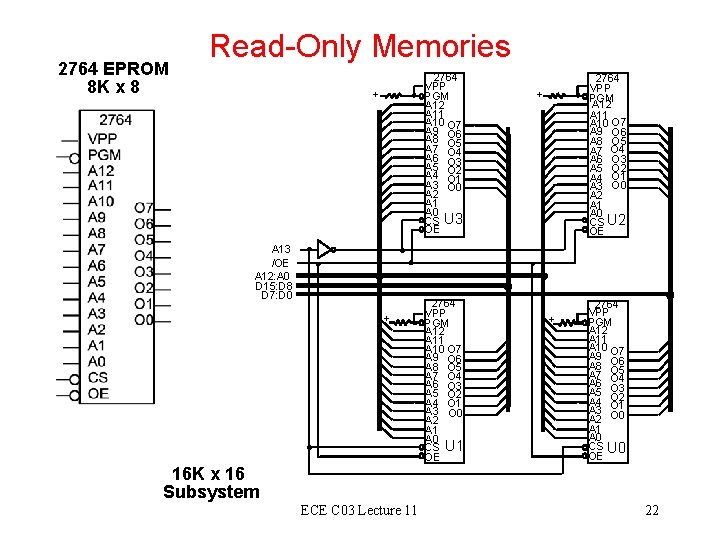

2764 EPROM 8 K x 8 Read-Only Memories 2764 VPP PGM A 12 A 11 A 10 O 7 A 9 O 6 A 8 O 5 A 7 O 4 A 6 O 3 A 5 O 2 A 4 O 1 A 3 O 0 A 2 A 1 A 0 CS U 3 OE + A 13 /OE A 12: A 0 D 15: D 8 D 7: D 0 + 2764 VPP PGM A 12 A 11 A 10 O 7 A 9 O 6 A 8 O 5 A 7 O 4 A 6 O 3 A 5 O 2 A 4 O 1 A 3 O 0 A 2 A 1 A 0 CS U 1 OE 2764 VPP PGM A 12 A 11 A 10 O 7 A 9 O 6 A 8 O 5 A 7 O 4 A 6 O 3 A 5 O 2 A 4 O 1 A 3 O 0 A 2 A 1 A 0 CS U 2 OE + + 2764 VPP PGM A 12 A 11 A 10 O 7 A 9 O 6 A 8 O 5 A 7 O 4 A 6 O 3 A 5 O 2 A 4 O 1 A 3 O 0 A 2 A 1 A 0 CS U 0 OE 16 K x 16 Subsystem ECE C 03 Lecture 11 22

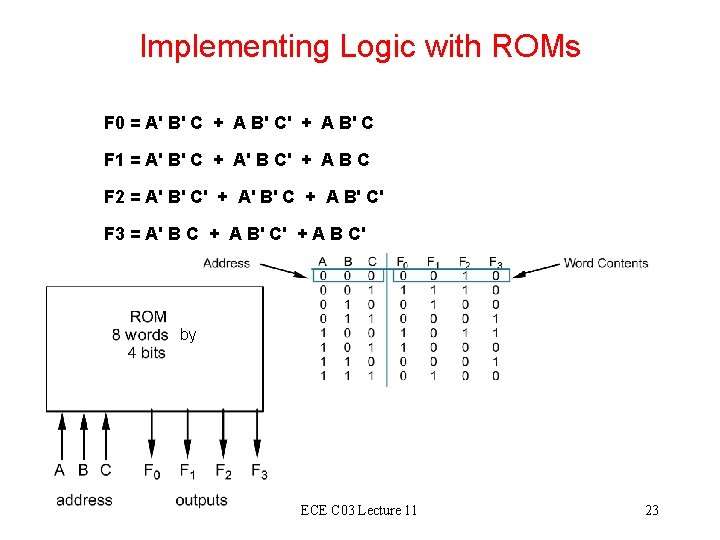

Implementing Logic with ROMs F 0 = A' B' C + A B' C' + A B' C F 1 = A' B' C + A' B C' + A B C F 2 = A' B' C' + A' B' C + A B' C' F 3 = A' B C + A B' C' + A B C' by ECE C 03 Lecture 11 23

Summary • • Random Access Memories (RAMS) Static RAMs Dynamic RAMS Memory Organizations Read-Only Memories (ROMS) NEXT LECTURE: Finite State Machine Design READING: Katz 8. 1, 8. 2, 8. 4, 8. 5, Dewey 9. 1, 9. 2 ECE C 03 Lecture 11 24

- Slides: 24