Lecture 14 Finite State Machine Assignment Prith Banerjee

Lecture 14 Finite State Machine Assignment Prith Banerjee ECE C 03 Advanced Digital Design Spring 1998 ECE C 03 Lecture 14 1

Outline • Motivation for state assignment • Example of state assignment • Paper and pencil method of state assignment for small designs • One hot encodings • CAD Tools for state assignment (NOVA, MUSTANG, JEDI) • READING: Katz 9. 3, Dewey 9. 4 • LAB ASSIGMENT 5: Design of a simple 8 -state FSM (1 week) ECE C 03 Lecture 14 2

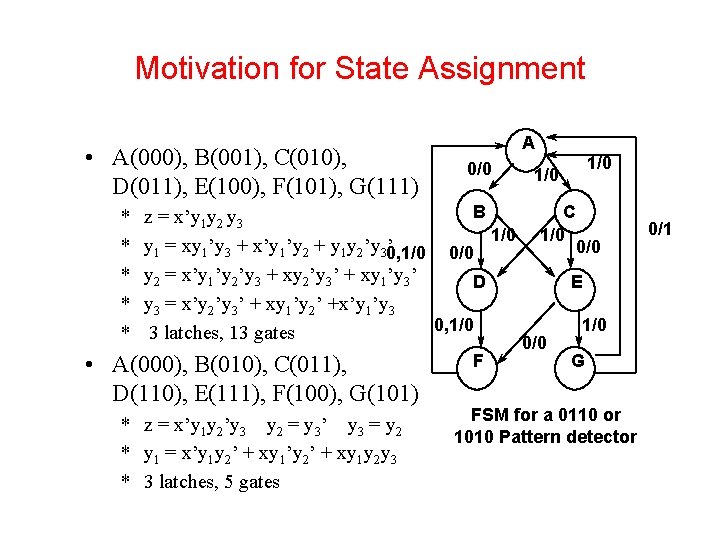

Motivation for State Assignment • A(000), B(001), C(010), D(011), E(100), F(101), G(111) * * * A 0/0 B z = x’y 1 y 2 y 3 1/0 y 1 = xy 1’y 3 + x’y 1’y 2 + y 1 y 2’y 30, 1/0 ’ 0/0 y 2 = x’y 1’y 2’y 3 + xy 2’y 3’ + xy 1’y 3’ D y 3 = x’y 2’y 3’ + xy 1’y 2’ +x’y 1’y 3 0, 1/0 3 latches, 13 gates • A(000), B(010), C(011), D(110), E(111), F(100), G(101) * z = x’y 1 y 2’y 3 y 2 = y 3’ y 3 = y 2 * y 1 = x’y 1 y 2’ + xy 1’y 2’ + xy 1 y 2 y 3 * 3 latches, 5 gates F 1/0 C 1/0 0/0 E 0/0 1/0 G FSM for a 0110 or 1010 Pattern detector 0/1

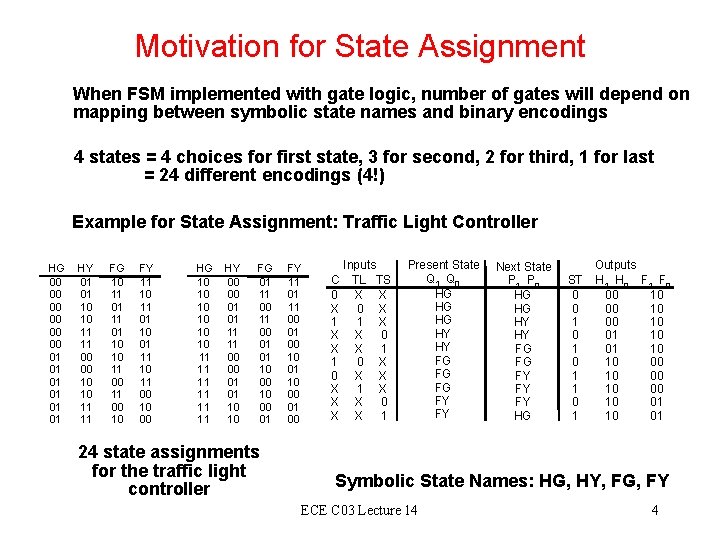

Motivation for State Assignment When FSM implemented with gate logic, number of gates will depend on mapping between symbolic state names and binary encodings 4 states = 4 choices for first state, 3 for second, 2 for third, 1 for last = 24 different encodings (4!) Example for State Assignment: Traffic Light Controller HG 00 00 00 01 01 01 HY 01 01 10 10 11 11 00 00 10 10 11 11 FG 10 11 01 10 10 11 00 10 FY 11 10 11 01 10 01 11 10 11 00 10 00 HG 10 10 10 11 11 11 HY 00 00 01 01 11 11 00 00 01 01 10 10 FG 01 11 00 01 01 10 00 01 24 state assignments for the traffic light controller FY 11 01 11 00 01 00 10 01 10 00 01 00 Inputs C TL TS 0 X X X 0 X 1 1 X X X 0 X X 1 1 0 X X X 1 X X X 0 X X 1 Present State Q 1 Q 0 HG HG HG HY HY FG FG FG FY FY Next State P 1 P 0 HG HG HY HY FG FG FY FY FY HG Outputs ST H 1 H 0 F 1 F 0 0 00 10 1 00 10 0 01 10 1 01 10 00 0 10 01 1 10 01 Symbolic State Names: HG, HY, FG, FY ECE C 03 Lecture 14 4

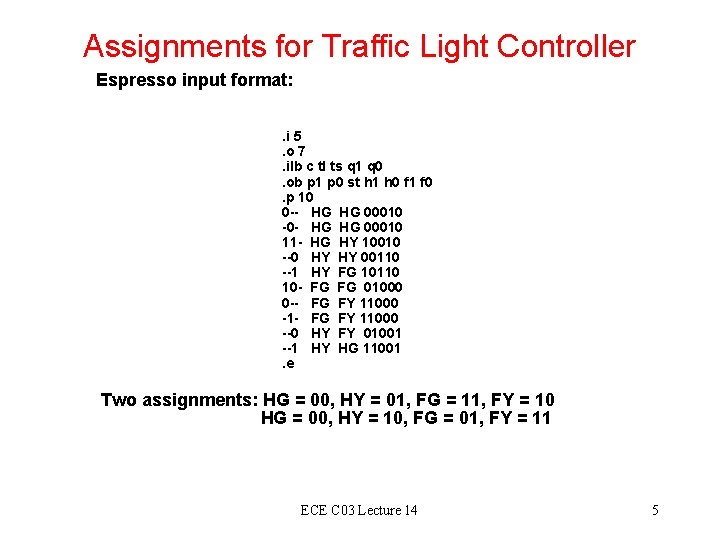

Assignments for Traffic Light Controller Espresso input format: . i 5. o 7. ilb c tl ts q 1 q 0. ob p 1 p 0 st h 1 h 0 f 1 f 0. p 10 0 -- HG HG 00010 -0 - HG HG 00010 11 - HG HY 10010 --0 HY HY 00110 --1 HY FG 10110 10 - FG FG 01000 0 -- FG FY 11000 -1 - FG FY 11000 --0 HY FY 01001 --1 HY HG 11001. e Two assignments: HG = 00, HY = 01, FG = 11, FY = 10 HG = 00, HY = 10, FG = 01, FY = 11 ECE C 03 Lecture 14 5

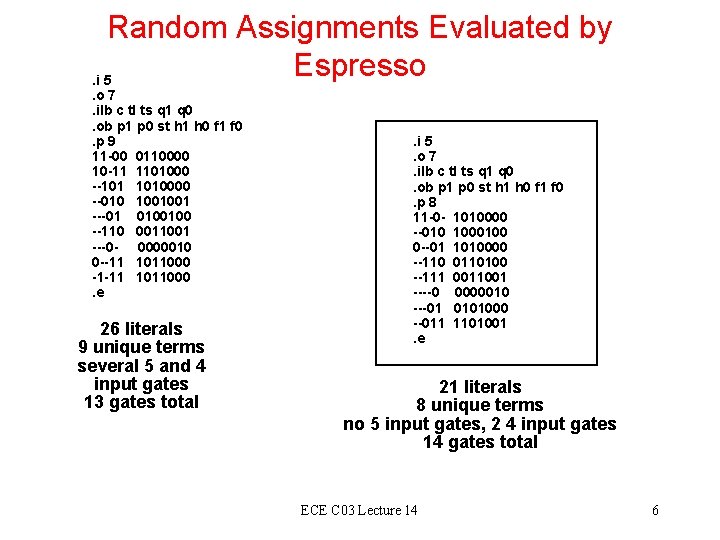

Random Assignments Evaluated by Espresso. i 5. o 7. ilb c tl ts q 1 q 0. ob p 1 p 0 st h 1 h 0 f 1 f 0. p 9 11 -00 0110000 10 -11 1101000 --101 1010000 --010 1001001 ---01 0100100 --110 0011001 ---0 - 0000010 0 --11 1011000 -1 -11 1011000. e 26 literals 9 unique terms several 5 and 4 input gates 13 gates total . i 5. o 7. ilb c tl ts q 1 q 0. ob p 1 p 0 st h 1 h 0 f 1 f 0. p 8 11 -0 - 1010000 --010 1000100 0 --01 1010000 --110 0110100 --111 0011001 ----0 0000010 ---01 0101000 --011 1101001. e 21 literals 8 unique terms no 5 input gates, 2 4 input gates 14 gates total ECE C 03 Lecture 14 6

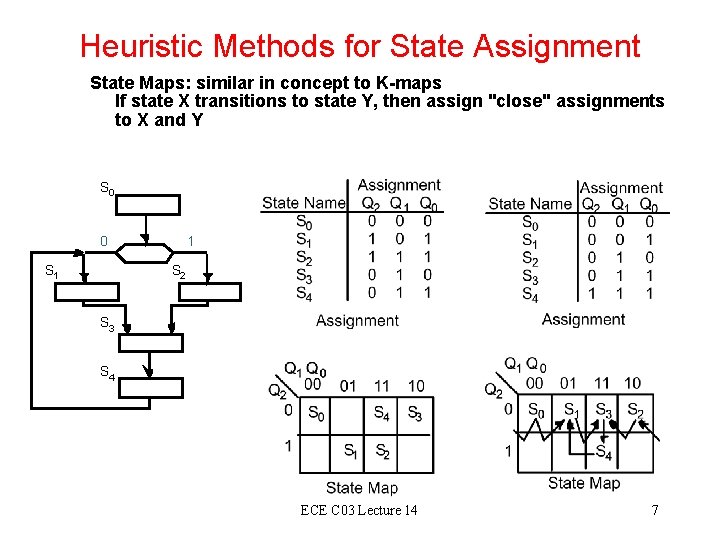

Heuristic Methods for State Assignment State Maps: similar in concept to K-maps If state X transitions to state Y, then assign "close" assignments to X and Y S 0 0 S 1 1 S 2 S 3 S 4 ECE C 03 Lecture 14 7

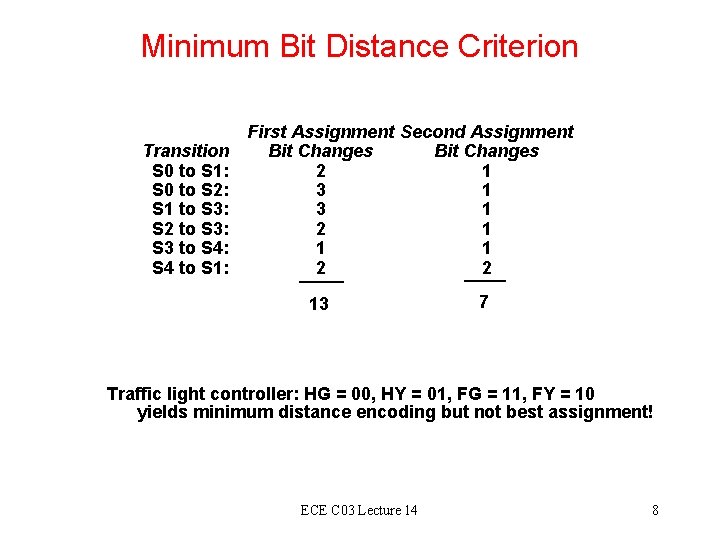

Minimum Bit Distance Criterion Transition S 0 to S 1: S 0 to S 2: S 1 to S 3: S 2 to S 3: S 3 to S 4: S 4 to S 1: First Assignment Second Assignment Bit Changes 2 1 3 1 2 1 1 1 2 2 13 7 Traffic light controller: HG = 00, HY = 01, FG = 11, FY = 10 yields minimum distance encoding but not best assignment! ECE C 03 Lecture 14 8

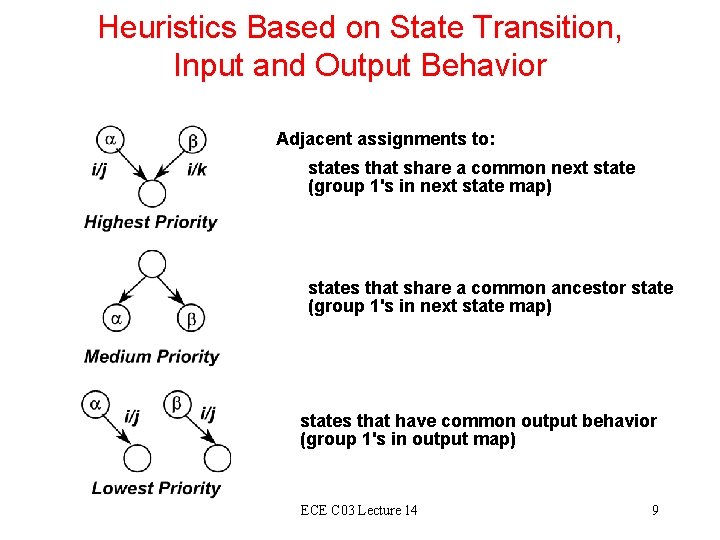

Heuristics Based on State Transition, Input and Output Behavior Adjacent assignments to: states that share a common next state (group 1's in next state map) states that share a common ancestor state (group 1's in next state map) states that have common output behavior (group 1's in output map) ECE C 03 Lecture 14 9

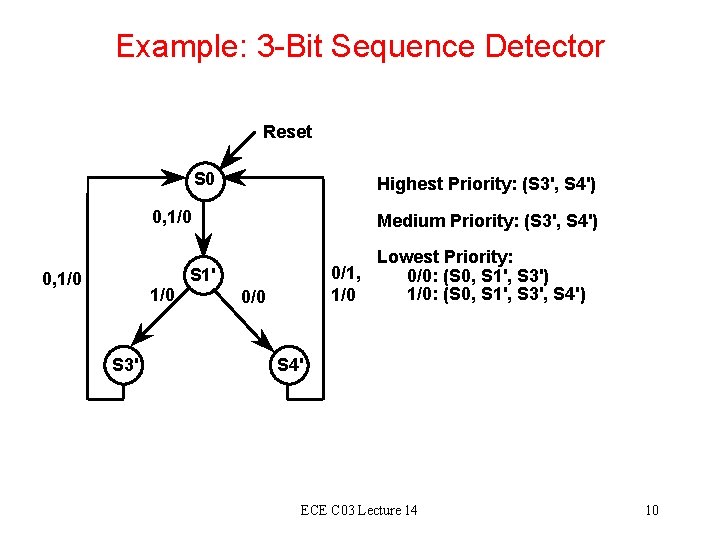

Example: 3 -Bit Sequence Detector Reset S 0 Highest Priority: (S 3', S 4') 0, 1/0 1/0 S 3' Medium Priority: (S 3', S 4') Lowest Priority: 0/1, 0/0: (S 0, S 1', S 3') 1/0: (S 0, S 1', S 3', S 4') 1/0 S 1' 0/0 S 4' ECE C 03 Lecture 14 10

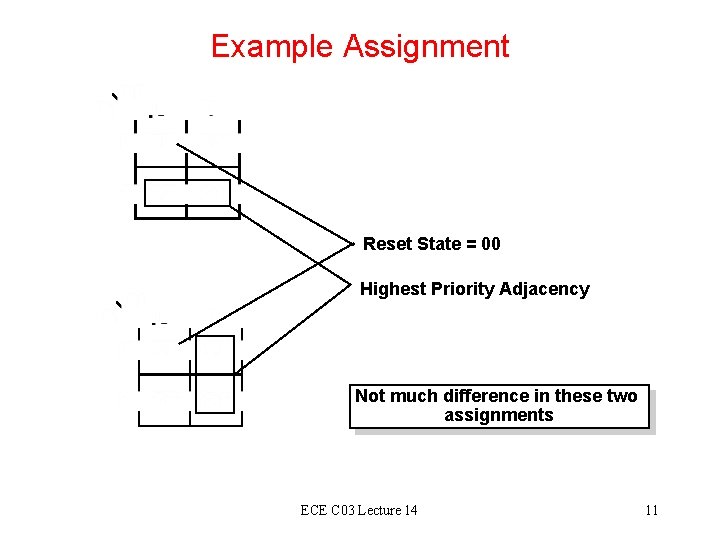

Example Assignment Reset State = 00 Highest Priority Adjacency Not much difference in these two assignments ECE C 03 Lecture 14 11

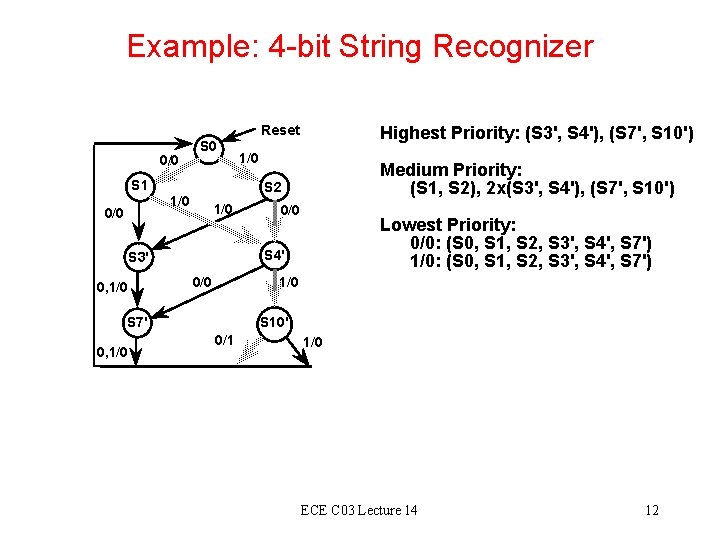

Example: 4 -bit String Recognizer 0/0 S 1 1/0 0/0 S 2 Medium Priority: (S 1, S 2), 2 x(S 3', S 4'), (S 7', S 10') 1/0 0/0 Lowest Priority: 0/0: (S 0, S 1, S 2, S 3', S 4', S 7') 1/0 S 7' 0, 1/0 Highest Priority: (S 3', S 4'), (S 7', S 10') S 4' S 3' 0, 1/0 Reset S 10' 0/1 1/0 ECE C 03 Lecture 14 12

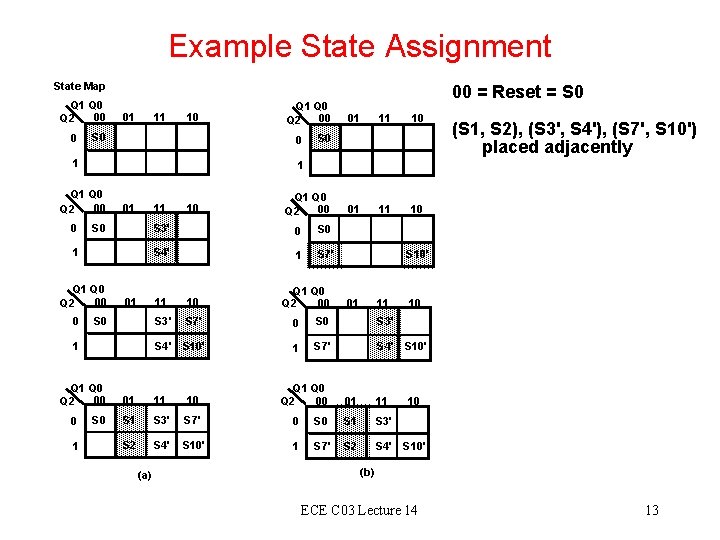

Example State Assignment State Map Q 1 Q 0 00 Q 2 0 01 11 10 S 0 0 1 01 11 S 0 1 Q 0 00 Q 2 0 00 = Reset = S 0 01 11 10 S 0 01 S 0 1 10 Q 1 Q 0 00 Q 2 S 3' 0 S 4' 1 S 7' Q 1 Q 0 Q 2 00 S 10' 11 10 S 3' S 7' 0 S 3' S 4' S 10' 1 S 7' S 4' S 10' 01 11 10 11 01 11 10 S 1 S 3' S 7' 0 S 1 S 3' S 2 S 4' S 10' 1 S 7' S 2 S 4' 1 (a) Q 1 Q 0 Q 2 00 01 Q 0 00 Q 2 0 (S 1, S 2), (S 3', S 4'), (S 7', S 10') placed adjacently 1 Q 0 00 Q 2 0 Q 1 Q 0 00 Q 2 10 S 10' (b) ECE C 03 Lecture 14 13

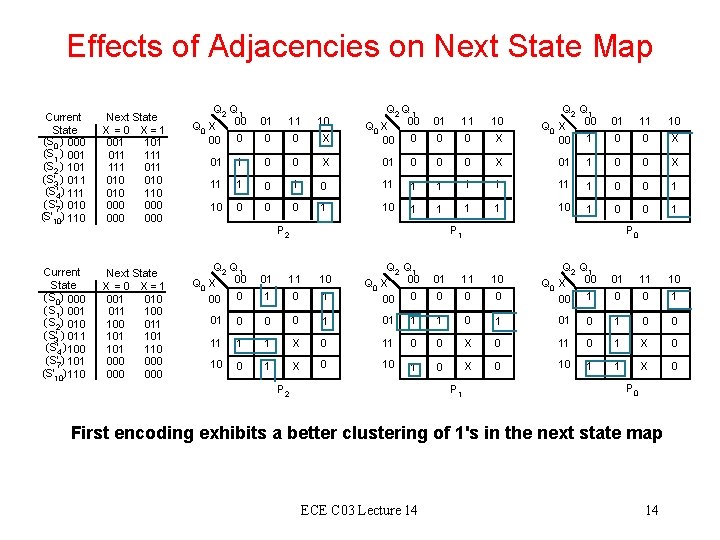

Effects of Adjacencies on Next State Map Current State (S 0 ) 000 (S 1 ) 001 (S 2 ) 101 ( S 3' ) 01 1 (S 4' ) 111 ( S'7) 010 (S'10) 110 Next State X =0 X=1 001 101 011 111 010 010 110 000 000 Current State ( S 0) 000 ( S 1) 001 ( S 2) 010 ( S 3' ) 01 1 ( S 4' ) 100 ( S 7' ) 101 (S'10) 110 Next State X =0 X=1 001 010 011 100 011 101 101 110 000 000 Q 2 Q 1 00 Q 0 X 00 0 01 11 10 Q 2 Q 1 00 Q 0 X 00 0 X 01 11 1 0 10 0 1 Q 2 Q 1 00 Q 0 X 00 1 01 11 10 0 0 X 01 11 1 1 10 1 1 P 2 01 11 10 0 0 X 11 1 0 0 1 10 1 01 11 10 0 0 1 P 1 Q 2 Q 1 00 Q 0 X 00 0 01 11 10 Q 2 Q 1 00 Q 0 X 00 0 1 01 0 0 0 1 01 11 1 1 X 0 10 0 1 X 0 P 0 Q 2 Q 1 00 Q 0 X 00 1 01 11 10 0 1 1 01 0 0 11 0 0 X 0 11 0 1 X 0 10 1 0 X 0 10 1 1 X 0 P 2 P 1 P 0 First encoding exhibits a better clustering of 1's in the next state map ECE C 03 Lecture 14 14

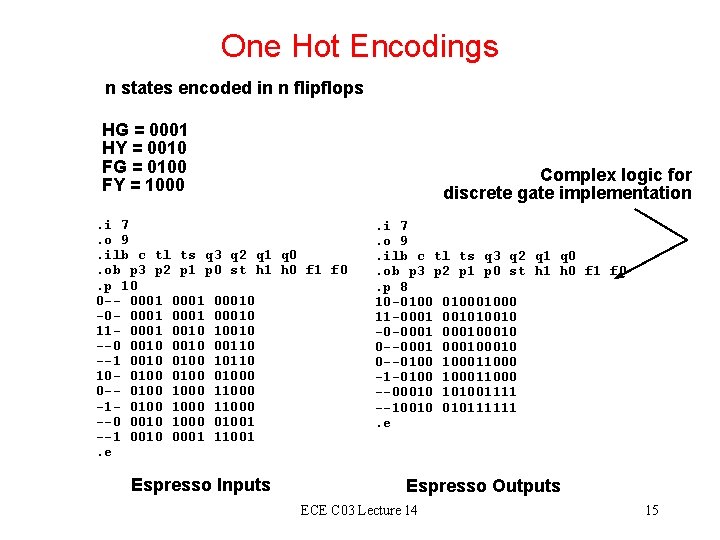

One Hot Encodings n states encoded in n flipflops HG = 0001 HY = 0010 FG = 0100 FY = 1000 Complex logic for discrete gate implementation . i 7. o 9. ilb c tl ts q 3 q 2 q 1 q 0. ob p 3 p 2 p 1 p 0 st h 1 h 0 f 1 f 0. p 10 0 -- 00010 -0 - 00010 11 - 0001 0010 10010 --0 0010 00110 --1 0010 0100 10110 10 - 01000 0 -- 0100 1000 11000 -1 - 0100 1000 11000 --0 0010 1000 01001 --1 0010 0001 11001. e Espresso Inputs . i 7. o 9. ilb c tl ts q 3 q 2 q 1 q 0. ob p 3 p 2 p 1 p 0 st h 1 h 0 f 1 f 0. p 8 10 -01000 11 -0001 001010010 -0 -000100010 0 --0100 100011000 -1 -0100 100011000 --00010 101001111 --10010 010111111. e Espresso Outputs ECE C 03 Lecture 14 15

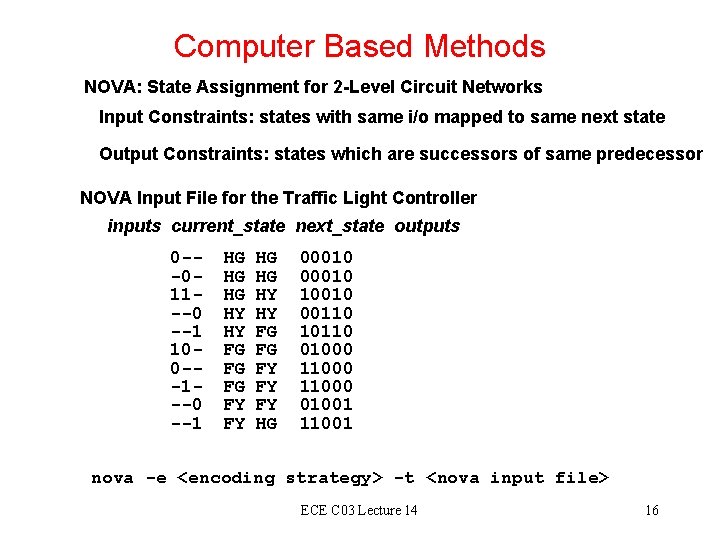

Computer Based Methods NOVA: State Assignment for 2 -Level Circuit Networks Input Constraints: states with same i/o mapped to same next state Output Constraints: states which are successors of same predecessor NOVA Input File for the Traffic Light Controller inputs current_state next_state outputs 0 --011 --0 --1 100 --1 --0 --1 HG HG HG HY HY FG FG FG FY FY HG HG HY HY FG FG FY FY FY HG 00010 10010 00110 10110 01000 11000 01001 11001 nova -e <encoding strategy> -t <nova input file> ECE C 03 Lecture 14 16

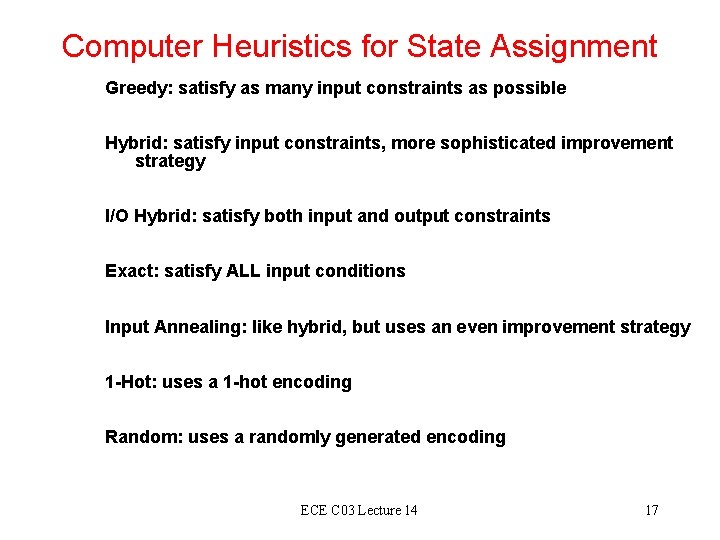

Computer Heuristics for State Assignment Greedy: satisfy as many input constraints as possible Hybrid: satisfy input constraints, more sophisticated improvement strategy I/O Hybrid: satisfy both input and output constraints Exact: satisfy ALL input conditions Input Annealing: like hybrid, but uses an even improvement strategy 1 -Hot: uses a 1 -hot encoding Random: uses a randomly generated encoding ECE C 03 Lecture 14 17

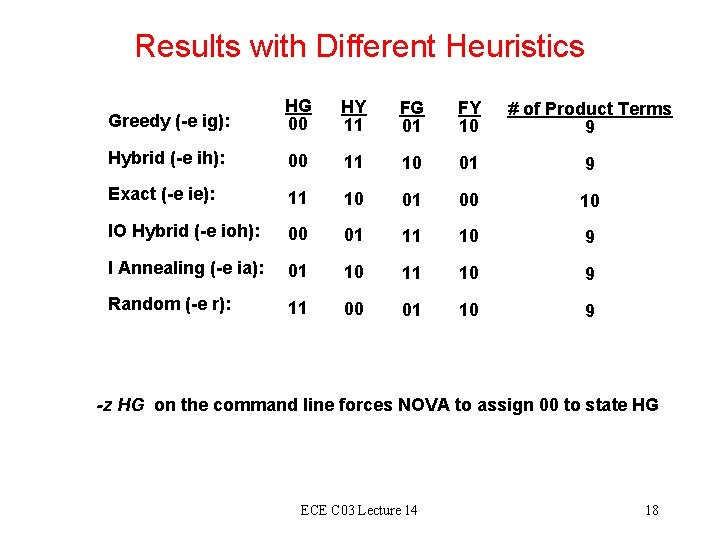

Results with Different Heuristics Greedy (-e ig): HG 00 HY 11 FG 01 FY 10 # of Product Terms 9 Hybrid (-e ih): 00 11 10 01 9 Exact (-e ie): 11 10 01 00 10 IO Hybrid (-e ioh): 00 01 11 10 9 I Annealing (-e ia): 01 10 11 10 9 Random (-e r): 11 00 01 10 9 -z HG on the command line forces NOVA to assign 00 to state HG ECE C 03 Lecture 14 18

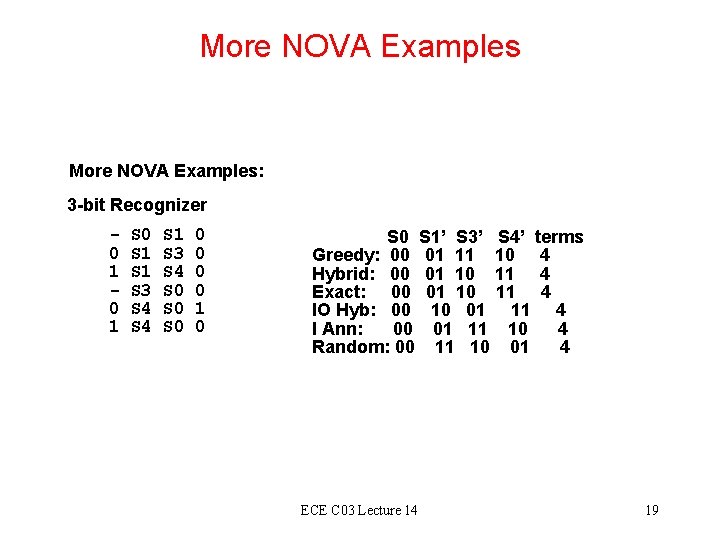

More NOVA Examples: 3 -bit Recognizer 0 1 S 0 S 1 S 3 S 4 S 0 S 0 0 0 1 0 S 1’ S 3’ S 4’ terms Greedy: 00 01 11 10 4 Hybrid: 00 01 10 11 4 Exact: 00 01 10 11 4 IO Hyb: 00 10 01 11 4 I Ann: 00 01 11 10 4 Random: 00 11 10 01 4 ECE C 03 Lecture 14 19

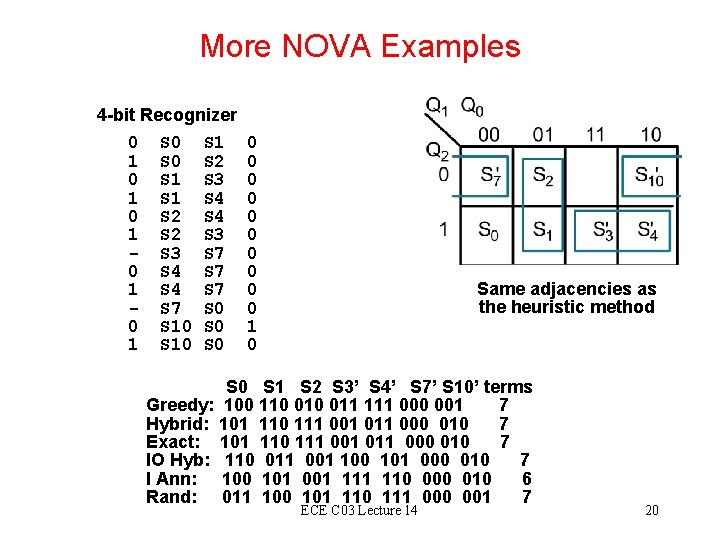

More NOVA Examples 4 -bit Recognizer 0 1 0 1 0 1 S 0 S 1 S 2 S 3 S 4 S 7 S 10 S 1 S 2 S 3 S 4 S 3 S 7 S 7 S 0 S 0 0 0 1 0 Same adjacencies as the heuristic method S 0 S 1 S 2 S 3’ S 4’ S 7’ S 10’ terms Greedy: 100 110 011 111 000 001 7 Hybrid: 101 110 111 001 011 000 010 7 Exact: 101 110 111 001 011 000 010 7 IO Hyb: 110 011 001 100 101 000 010 7 I Ann: 100 101 001 110 000 010 6 Rand: 011 100 101 110 111 000 001 7 ECE C 03 Lecture 14 20

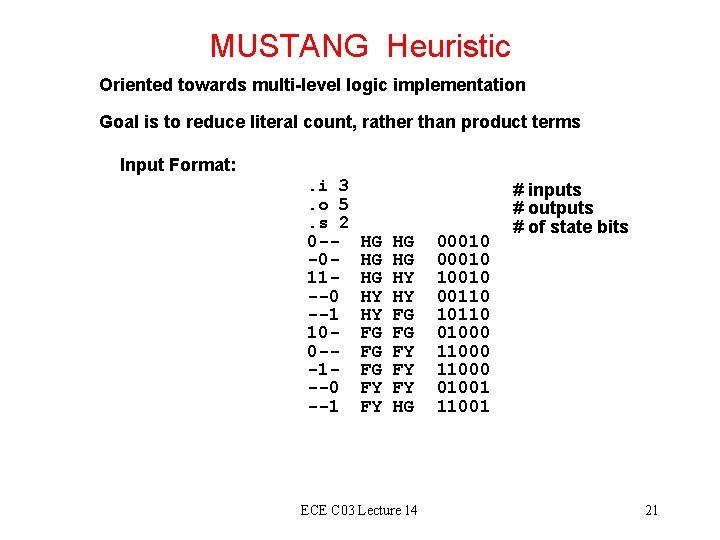

MUSTANG Heuristic Oriented towards multi-level logic implementation Goal is to reduce literal count, rather than product terms Input Format: . i 3. o 5. s 2 0 --011 --0 --1 100 --1 --0 --1 HG HG HG HY HY FG FG FG FY FY HG HG HY HY FG FG FY FY FY HG ECE C 03 Lecture 14 00010 10010 00110 10110 01000 11000 01001 11001 # inputs # outputs # of state bits 21

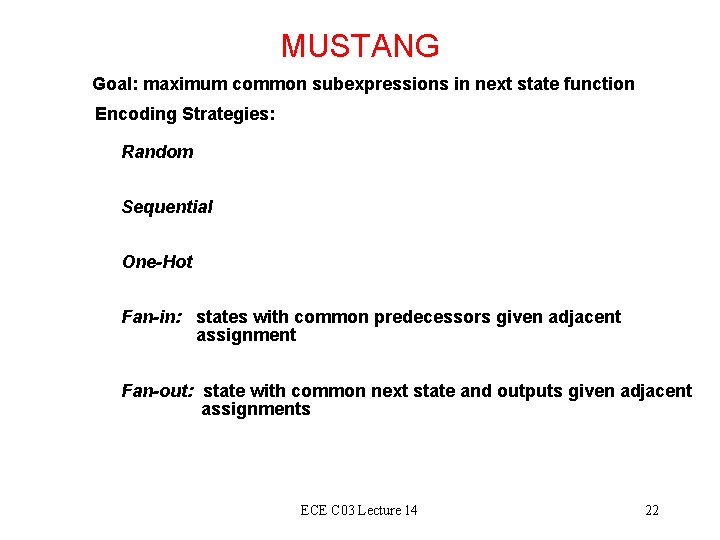

MUSTANG Goal: maximum common subexpressions in next state function Encoding Strategies: Random Sequential One-Hot Fan-in: states with common predecessors given adjacent assignment Fan-out: state with common next state and outputs given adjacent assignments ECE C 03 Lecture 14 22

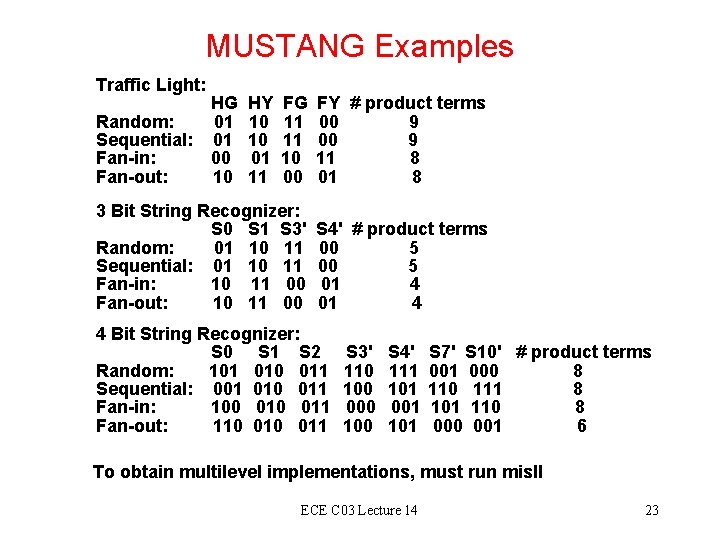

MUSTANG Examples Traffic Light: HG Random: 01 Sequential: 01 Fan-in: 00 Fan-out: 10 HY 10 10 01 11 FG 11 11 10 00 FY # product terms 00 9 11 8 01 8 3 Bit String Recognizer: S 0 S 1 S 3' Random: 01 10 11 Sequential: 01 10 11 Fan-in: 10 11 00 Fan-out: 10 11 00 S 4' # product terms 00 5 01 4 4 Bit String Recognizer: S 0 S 1 S 2 Random: 101 010 011 Sequential: 001 010 011 Fan-in: 100 011 Fan-out: 110 011 S 3' 110 100 000 100 S 4' 111 101 001 101 S 7' S 10' # product terms 001 000 8 110 111 8 101 110 8 000 001 6 To obtain multilevel implementations, must run mis. II ECE C 03 Lecture 14 23

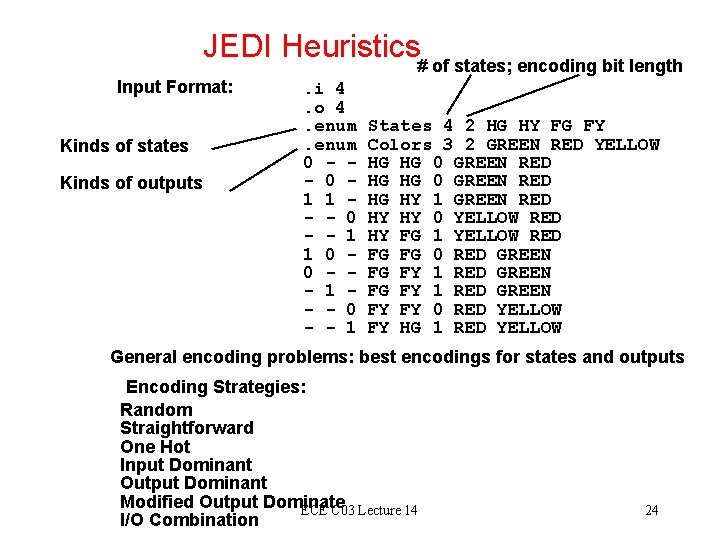

JEDI Heuristics# of states; encoding bit length Input Format: Kinds of states Kinds of outputs . i 4. o 4. enum 0 - - 0 1 1 - - 0 - - 1 1 0 0 - - 1 - - 0 - - 1 States 4 2 HG HY FG FY Colors 3 2 GREEN RED YELLOW HG HG 0 GREEN RED HG HY 1 GREEN RED HY HY 0 YELLOW RED HY FG 1 YELLOW RED FG FG 0 RED GREEN FG FY 1 RED GREEN FY FY 0 RED YELLOW FY HG 1 RED YELLOW General encoding problems: best encodings for states and outputs Encoding Strategies: Random Straightforward One Hot Input Dominant Output Dominant Modified Output Dominate ECE C 03 Lecture 14 I/O Combination 24

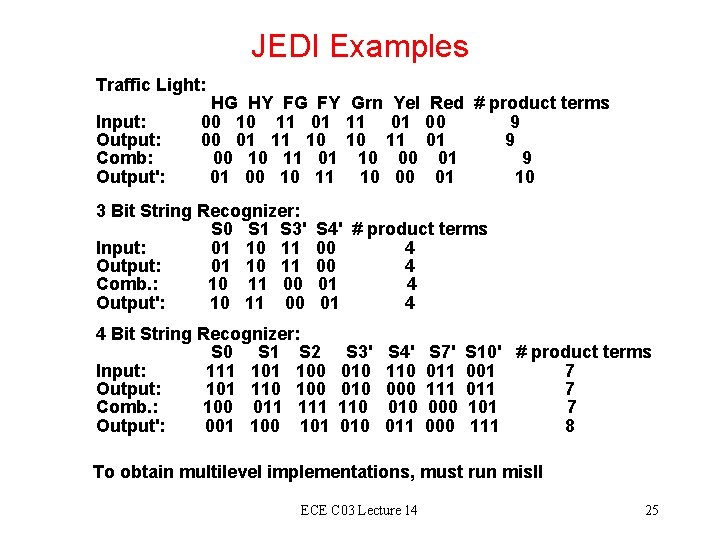

JEDI Examples Traffic Light: Input: Output: Comb: Output': HG HY FG FY Grn Yel 00 10 11 01 00 01 11 10 10 11 01 10 00 01 00 10 11 10 00 3 Bit String Recognizer: S 0 S 1 S 3' Input: 01 10 11 Output: 01 10 11 Comb. : 10 11 00 Output': 10 11 00 Red # product terms 00 9 01 10 S 4' # product terms 00 4 01 4 4 Bit String Recognizer: S 0 S 1 S 2 Input: 111 100 Output: 101 110 100 Comb. : 100 011 111 Output': 001 100 101 S 3' 010 110 010 S 4' 110 000 011 S 7' 011 111 000 S 10' # product terms 001 7 011 7 101 7 111 8 To obtain multilevel implementations, must run mis. II ECE C 03 Lecture 14 25

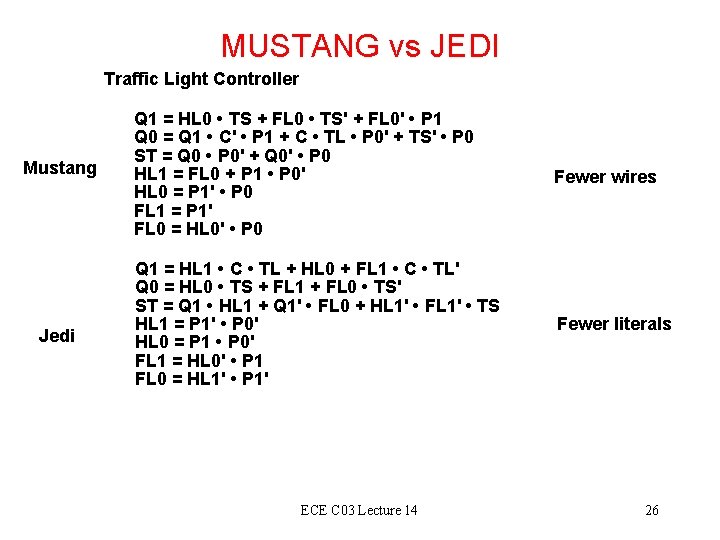

MUSTANG vs JEDI Traffic Light Controller Mustang Jedi Q 1 = HL 0 • TS + FL 0 • TS' + FL 0' • P 1 Q 0 = Q 1 • C' • P 1 + C • TL • P 0' + TS' • P 0 ST = Q 0 • P 0' + Q 0' • P 0 HL 1 = FL 0 + P 1 • P 0' HL 0 = P 1' • P 0 FL 1 = P 1' FL 0 = HL 0' • P 0 Fewer wires Q 1 = HL 1 • C • TL + HL 0 + FL 1 • C • TL' Q 0 = HL 0 • TS + FL 1 + FL 0 • TS' ST = Q 1 • HL 1 + Q 1' • FL 0 + HL 1' • FL 1' • TS HL 1 = P 1' • P 0' HL 0 = P 1 • P 0' FL 1 = HL 0' • P 1 FL 0 = HL 1' • P 1' Fewer literals ECE C 03 Lecture 14 26

JEDI Algorithm • Gain Estimate Computation Phase – Calculates an Ns. XNs gain estimate matrix M[: , : ] – M[i, j] is an estimate of the gain obtained by encoding States i and j at a small Hamming Distance from each other • State Encoding Phase – Assigns binary codes to the states of the FSM guided by the gain estimates – Based on simulated annealing, use random exchanges of states among encoding space – Use a cost function

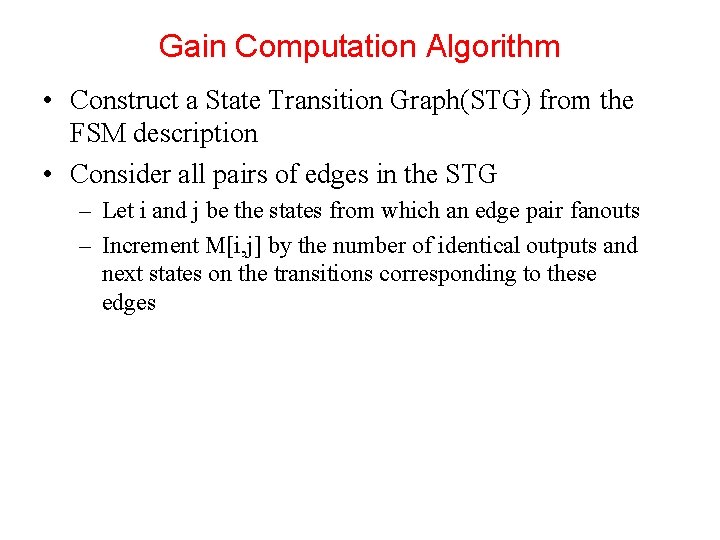

Gain Computation Algorithm • Construct a State Transition Graph(STG) from the FSM description • Consider all pairs of edges in the STG – Let i and j be the states from which an edge pair fanouts – Increment M[i, j] by the number of identical outputs and next states on the transitions corresponding to these edges

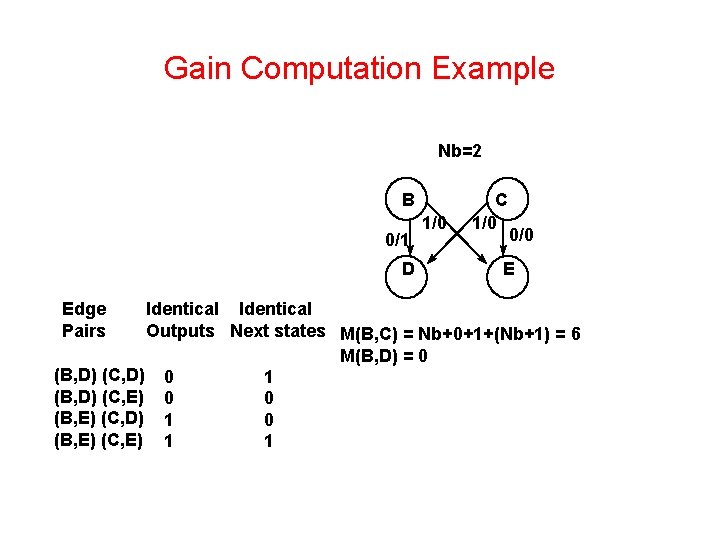

Gain Computation Example Nb=2 B 0/1 D Edge Pairs 1/0 C 1/0 0/0 E Identical Outputs Next states M(B, C) = Nb+0+1+(Nb+1) = 6 M(B, D) = 0 (B, D) (C, D) 0 1 (B, D) (C, E) 0 0 (B, E) (C, D) 1 0 (B, E) (C, E) 1 1

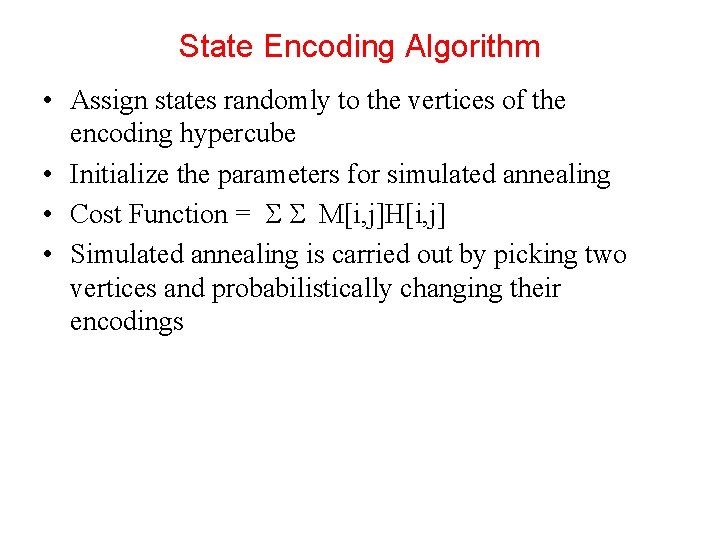

State Encoding Algorithm • Assign states randomly to the vertices of the encoding hypercube • Initialize the parameters for simulated annealing • Cost Function = S S M[i, j]H[i, j] • Simulated annealing is carried out by picking two vertices and probabilistically changing their encodings

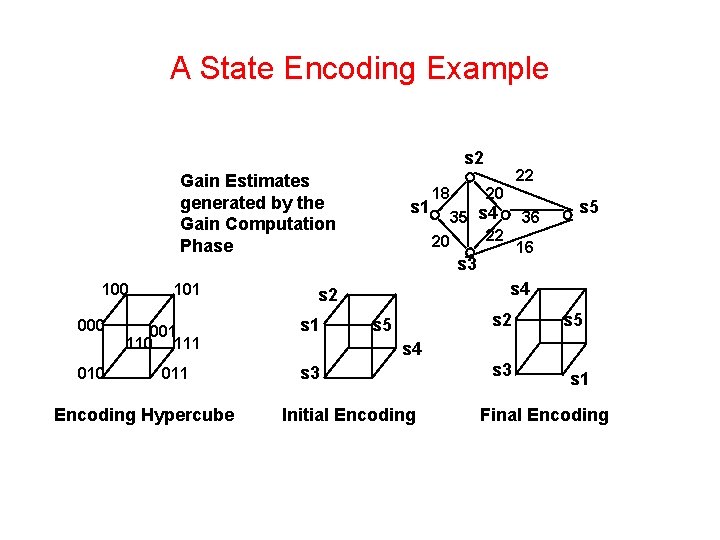

A State Encoding Example s 2 Gain Estimates generated by the Gain Computation Phase 100 010 101 001 110 111 011 Encoding Hypercube s 1 20 35 s 4 22 20 36 s 5 16 s 3 s 4 s 2 s 1 18 22 s 5 s 4 s 3 Initial Encoding s 3 s 1 Final Encoding

Choice of Flipflops J-K FFs: reduce gate count, increase # of connections D FFs: simplify implementation process, decrease # of connections Procedure: 1. Given state assignments, derive the next state maps from the state transition table 2. Remap the next state maps given excitation tables for a given FF 3. Minimize the remapped next state function ECE C 03 Lecture 14 32

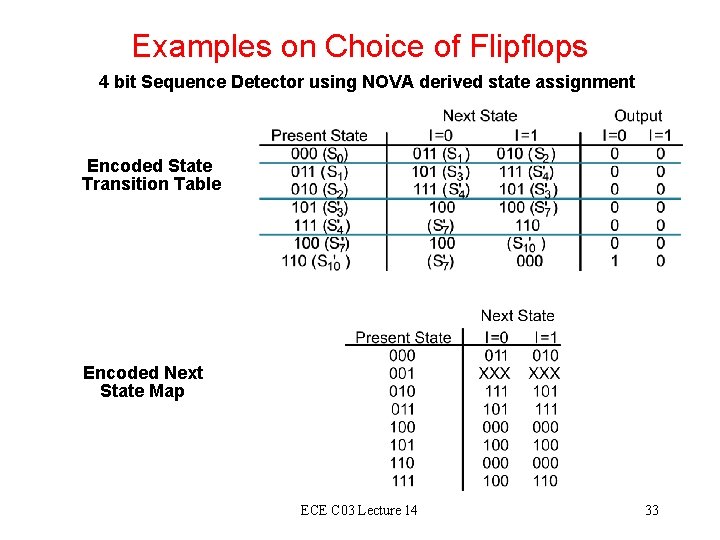

Examples on Choice of Flipflops 4 bit Sequence Detector using NOVA derived state assignment Encoded State Transition Table Encoded Next State Map ECE C 03 Lecture 14 33

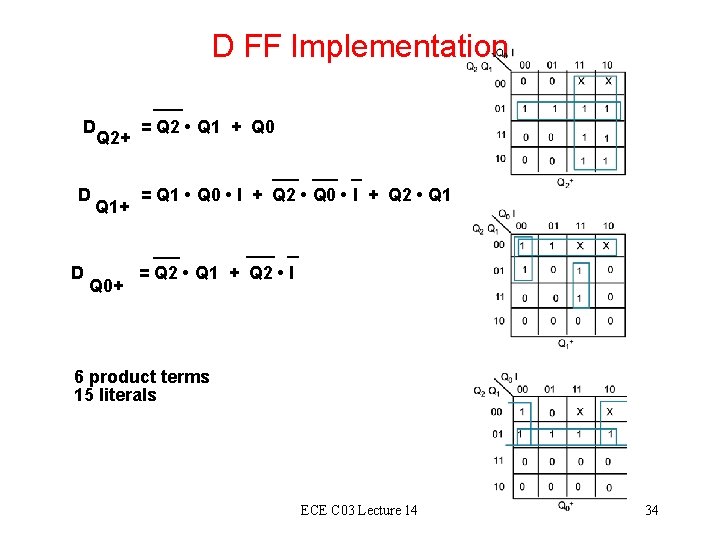

D FF Implementation D D D Q 2+ Q 1+ Q 0+ = Q 2 • Q 1 + Q 0 = Q 1 • Q 0 • I + Q 2 • Q 1 = Q 2 • Q 1 + Q 2 • I 6 product terms 15 literals ECE C 03 Lecture 14 34

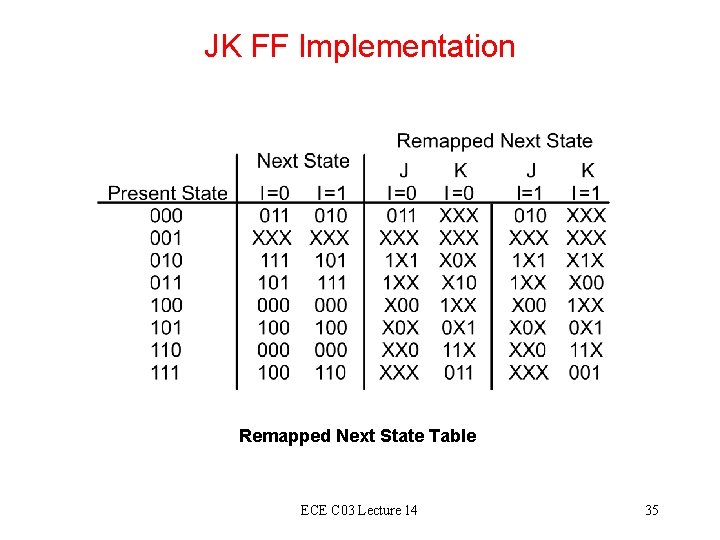

JK FF Implementation Remapped Next State Table ECE C 03 Lecture 14 35

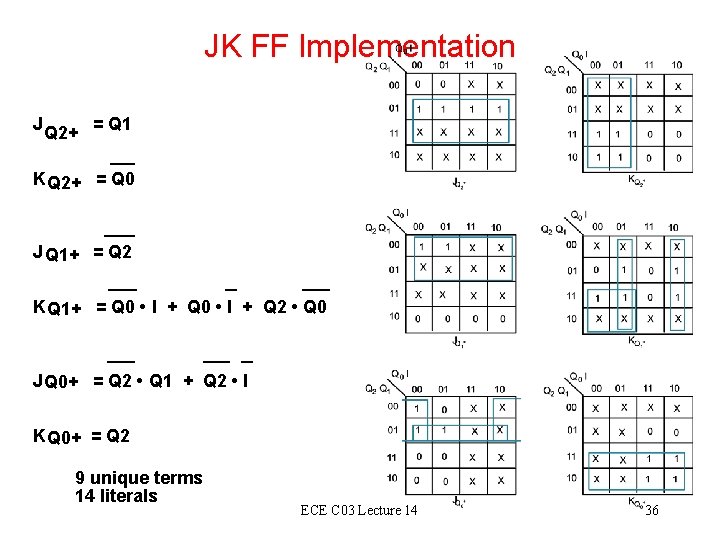

JK FF Implementation J Q 2+ = Q 1 K Q 2+ = Q 0 J Q 1+ = Q 2 K Q 1+ = Q 0 • I + Q 2 • Q 0 J Q 0+ = Q 2 • Q 1 + Q 2 • I K Q 0+ = Q 2 9 unique terms 14 literals ECE C 03 Lecture 14 36

Summary • Motivation for state assignment • Example of state assignment • Paper and pencil method of state assignment for small designs • One hot encodings • CAD Tools for state assignment (NOVA, MUSTANG, JEDI) • NEXT LECTURE: Finite State Machine Implementation • READING: Katz 10. 1. 1, 10. 1. 2, Dewey 9. 5 ECE C 03 Lecture 14 37

- Slides: 37