Lecture 10 MPC 555 Interrupt 1 Interrupt System

![UIMB: U-bus to IMB Interface IMB 3 Bus 32 addr/data UIPEND 2 UMCR[IRQUX] 8 UIMB: U-bus to IMB Interface IMB 3 Bus 32 addr/data UIPEND 2 UMCR[IRQUX] 8](https://slidetodoc.com/presentation_image/243e1c80fc9d0f6e2c8593001e7cc80f/image-6.jpg)

![External Interrupts U-BUS 2 IRQ[0: 7] external 8 8 3 1 4 USIU 1 External Interrupts U-BUS 2 IRQ[0: 7] external 8 8 3 1 4 USIU 1](https://slidetodoc.com/presentation_image/243e1c80fc9d0f6e2c8593001e7cc80f/image-8.jpg)

![Interrupt Controller SIPEND[0: 31]: Interrupt pending register l Handler accesses SIPEND for source of Interrupt Controller SIPEND[0: 31]: Interrupt pending register l Handler accesses SIPEND for source of](https://slidetodoc.com/presentation_image/243e1c80fc9d0f6e2c8593001e7cc80f/image-11.jpg)

![Connecting To Power. PC Core Finally! 5 MSR[EE] IREQ 1 & NMI 2 Decrementer Connecting To Power. PC Core Finally! 5 MSR[EE] IREQ 1 & NMI 2 Decrementer](https://slidetodoc.com/presentation_image/243e1c80fc9d0f6e2c8593001e7cc80f/image-13.jpg)

![PIT Block Diagram PTE PISCR[15] pitrtclk clock Clock Disable PITF PITC 16 -bit Modulus PIT Block Diagram PTE PISCR[15] pitrtclk clock Clock Disable PITF PITC 16 -bit Modulus](https://slidetodoc.com/presentation_image/243e1c80fc9d0f6e2c8593001e7cc80f/image-29.jpg)

- Slides: 31

Lecture 10 MPC 555 Interrupt 1

Interrupt System Design: Hardware issues l l l Connect interrupt sources to processor core. Determine ISR addresses using exception vector table. Help software determine interrupt source. Disable/enable interrupts. Mask interrupts. 2

Interrupt System Design: Software Issues Interrupt setup l Set up interrupt level l Set up exception vector table l Set up interrupt mask l Enable interrupt l Device-specific setup Interrupt Processing l Create/destroy stack frame l Save/restore machine states and EPC l Mask interrupt (optional) l Enable interrupt (optional) l Save/restore registers contents l Determine interrupt source l Determine ISR address l Device-specific processing 3

MPC 555 Interrupt Overview Internal I/O 2 1 External I/O 3 USIU Processor Core handler MPC 555 Interrupt Sources: 1. External I/O devices 2. Internal I/O device 3. From USIU inside (Unified System Interface unit) USIU includes interrupt control memory 4

Power. PC Internal I/O Modules TPU 3 MIOS 1 QADC 64 Tou. CAN QSMCM IMB 3 Bus l l l 1 TPU 3: Time Processor Units, 3 rd version; versatile functions, e. g. counting pulses MIOS 1: Modular I/O System; QADC 64: Queued Analog-to-digital converter Tou. CAN: Control Area Network, two-wire, up to 1 Mbps and 40 m; e. g. network inside vehicle QSMCM: Queued Serial Multi-channel Module IMB 3 bus: Inter-Module Bus 5

![UIMB Ubus to IMB Interface IMB 3 Bus 32 addrdata UIPEND 2 UMCRIRQUX 8 UIMB: U-bus to IMB Interface IMB 3 Bus 32 addr/data UIPEND 2 UMCR[IRQUX] 8](https://slidetodoc.com/presentation_image/243e1c80fc9d0f6e2c8593001e7cc80f/image-6.jpg)

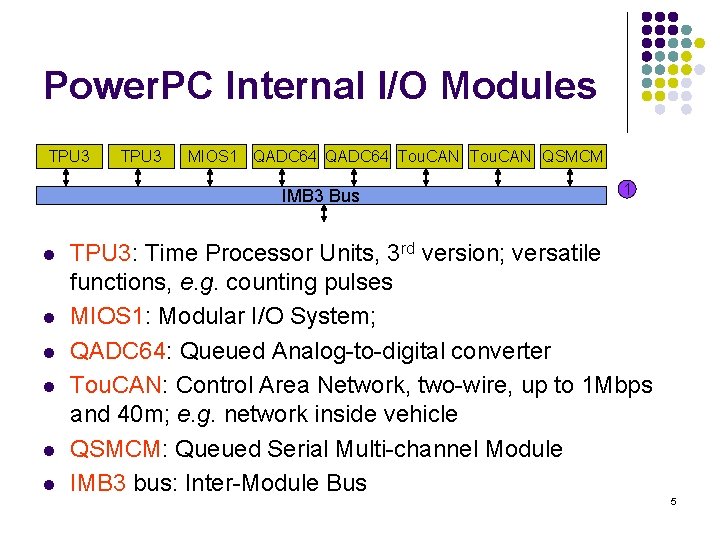

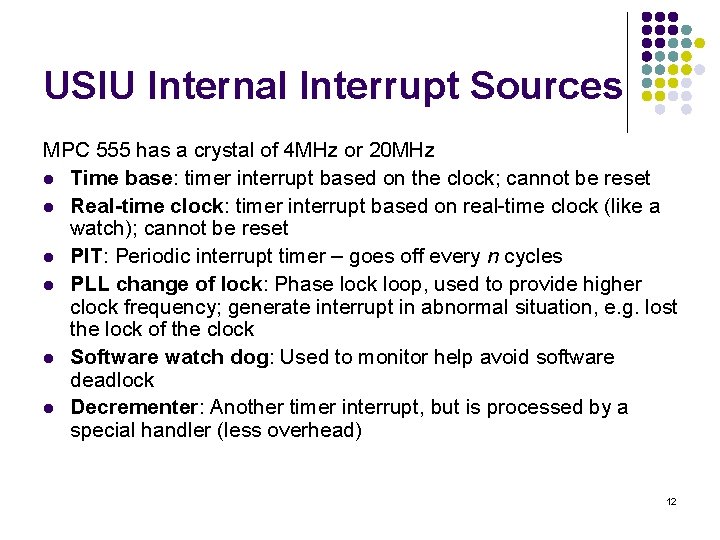

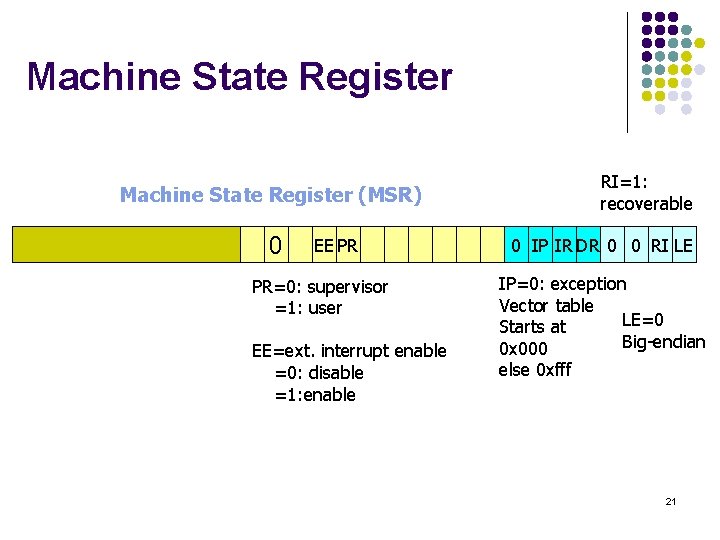

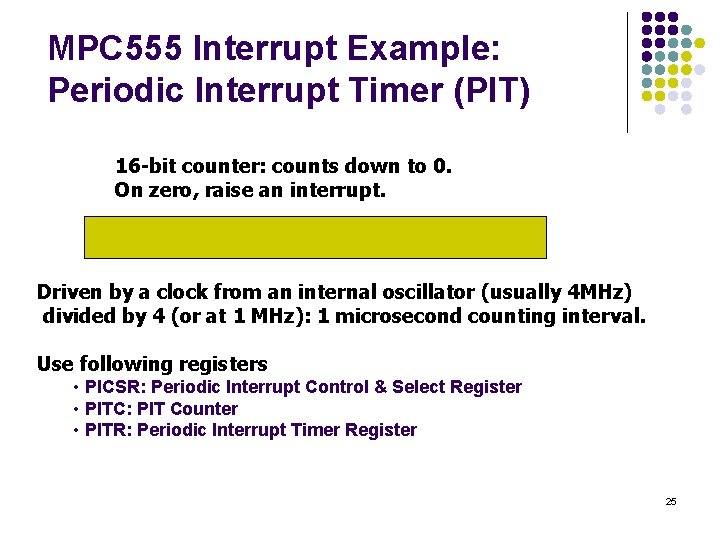

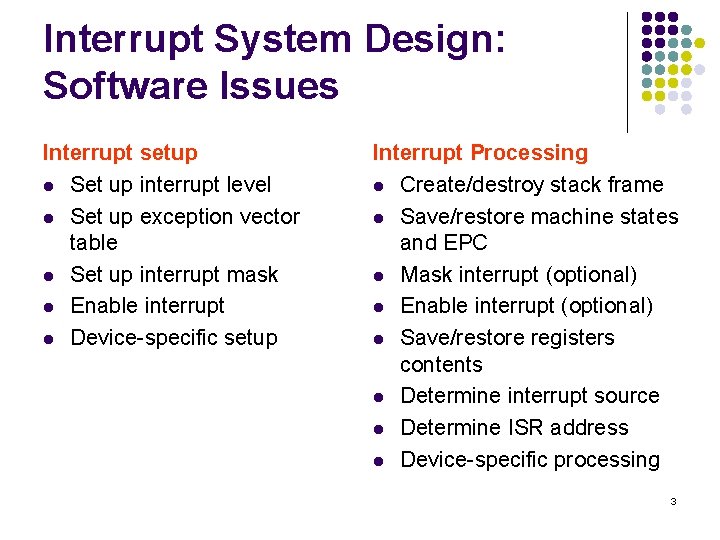

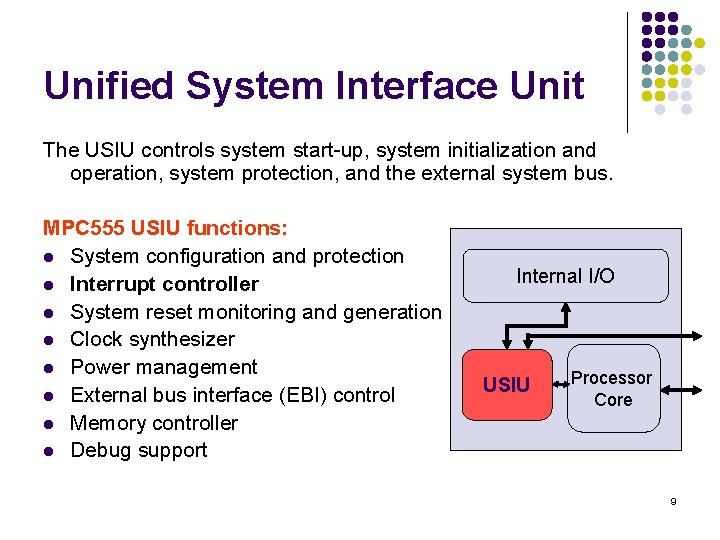

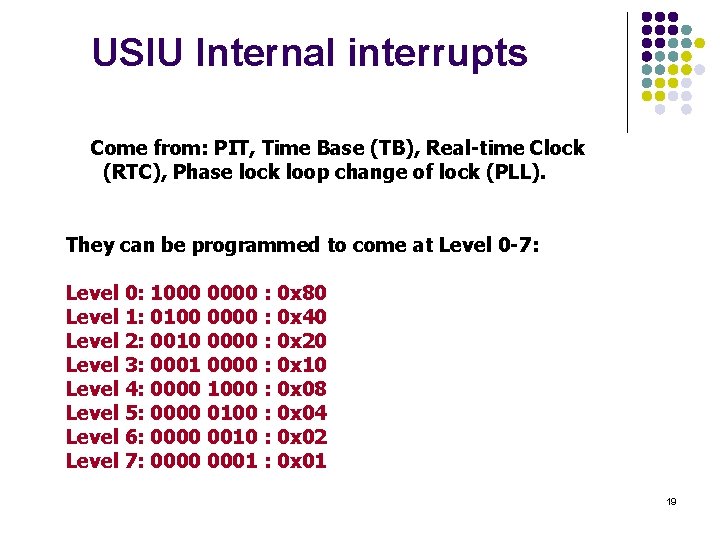

UIMB: U-bus to IMB Interface IMB 3 Bus 32 addr/data UIPEND 2 UMCR[IRQUX] 8 U-Bus Other bus Interrupt controller • UIMB: U-bus to IMB interface • UIPEND: Interrupt pending reg. • U-bus: Unified bus, connecting multiple internal buses • UMCR[IRQUX]: Enable level 7 -31 6

UIMB: U-bus to IMB Interface The interface converts 32 interrupt levels on IMB 3 Bus to 8 interrupt levels on U-Bus l l l Level 0 -6 to U-Bus level 0 -6 Level 7 -31 to U-Bus level 7 Interrupt handler reads full UIPEND through memory-mapped I/O 7

![External Interrupts UBUS 2 IRQ0 7 external 8 8 3 1 4 USIU 1 External Interrupts U-BUS 2 IRQ[0: 7] external 8 8 3 1 4 USIU 1](https://slidetodoc.com/presentation_image/243e1c80fc9d0f6e2c8593001e7cc80f/image-8.jpg)

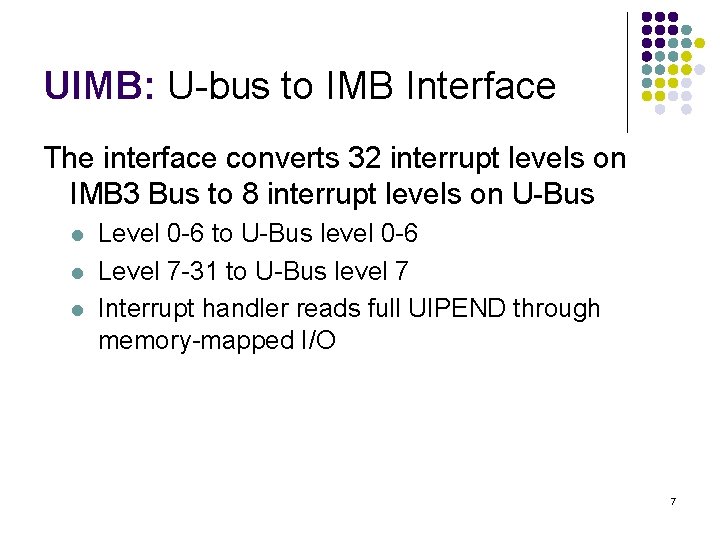

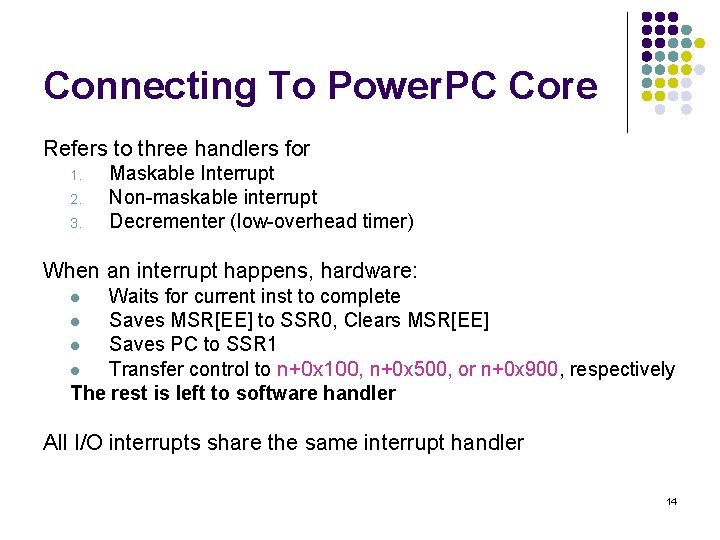

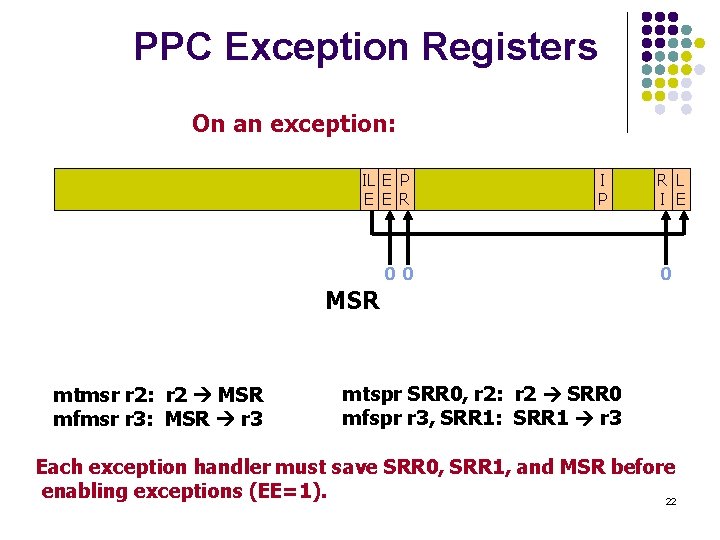

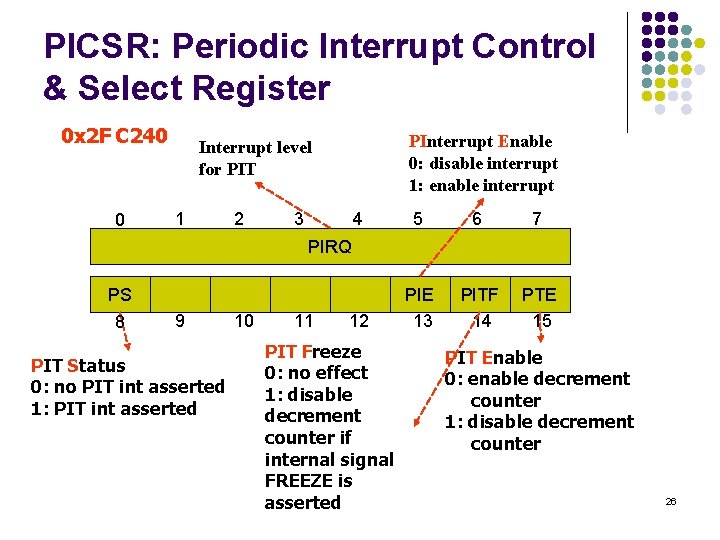

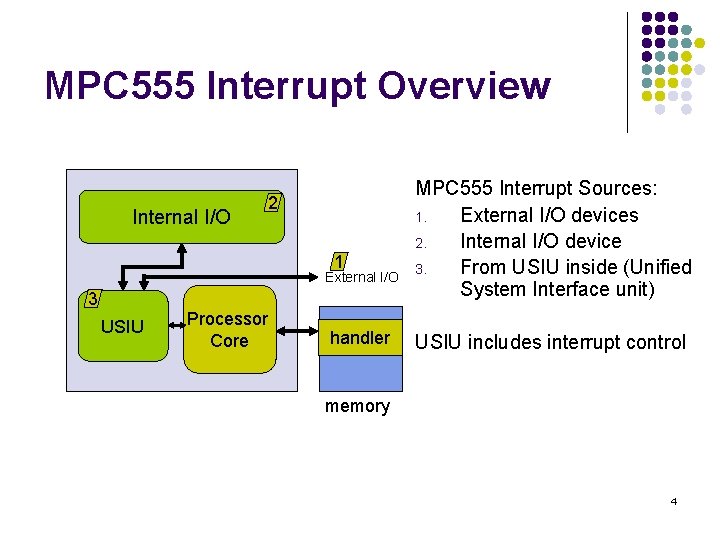

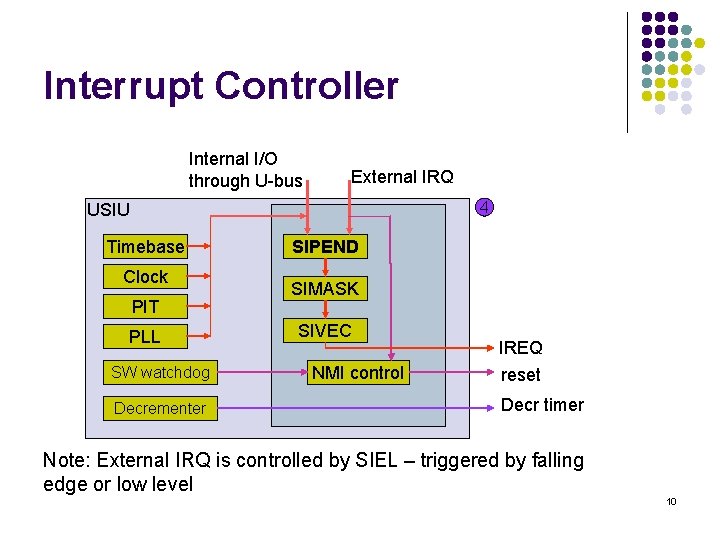

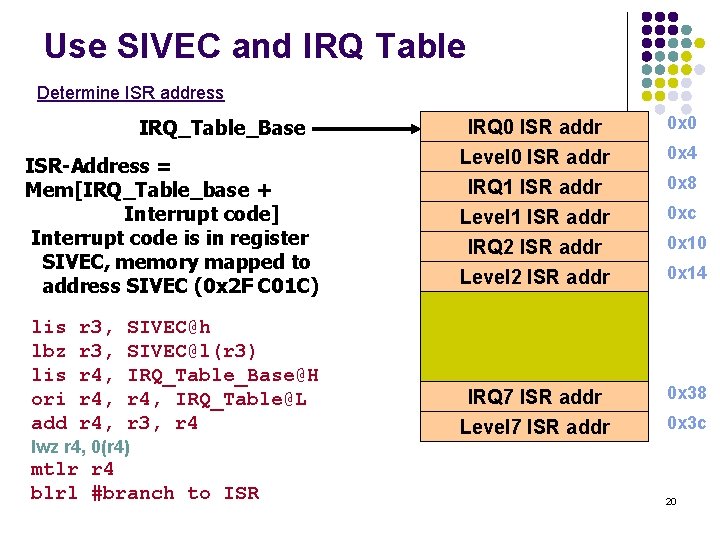

External Interrupts U-BUS 2 IRQ[0: 7] external 8 8 3 1 4 USIU 1 1 IRQ Reset Timer Other I/O device: l l Hard drive, video card, … IRQ[0]: connect to reset 8

Unified System Interface Unit The USIU controls system start-up, system initialization and operation, system protection, and the external system bus. MPC 555 USIU functions: l System configuration and protection l Interrupt controller l System reset monitoring and generation l Clock synthesizer l Power management l External bus interface (EBI) control l Memory controller l Debug support Internal I/O USIU Processor Core 9

Interrupt Controller Internal I/O through U-bus External IRQ 4 USIU Timebase Clock PIT PLL SW watchdog Decrementer SIPEND SIMASK SIVEC NMI control IREQ reset Decr timer Note: External IRQ is controlled by SIEL – triggered by falling edge or low level 10

![Interrupt Controller SIPEND0 31 Interrupt pending register l Handler accesses SIPEND for source of Interrupt Controller SIPEND[0: 31]: Interrupt pending register l Handler accesses SIPEND for source of](https://slidetodoc.com/presentation_image/243e1c80fc9d0f6e2c8593001e7cc80f/image-11.jpg)

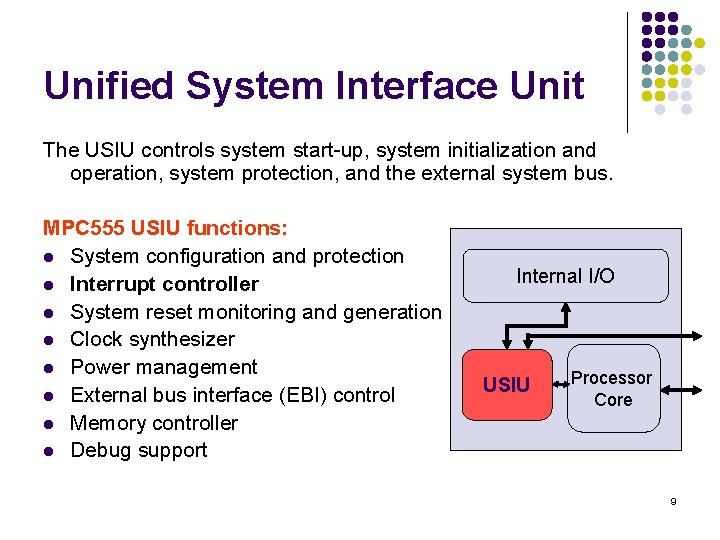

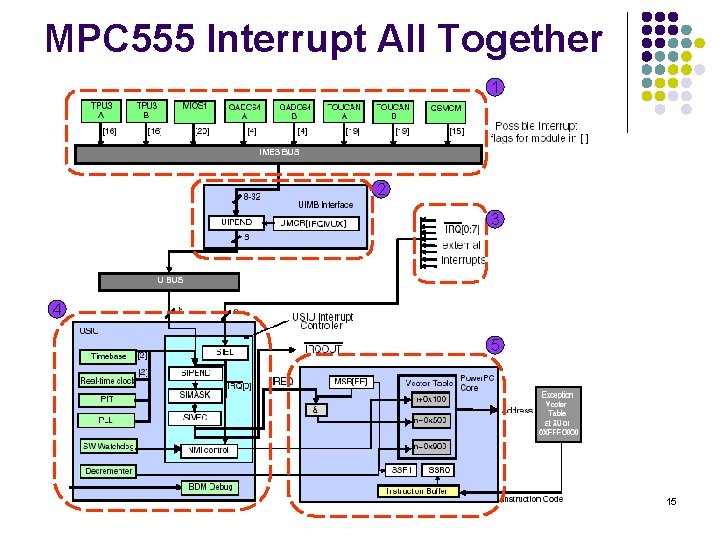

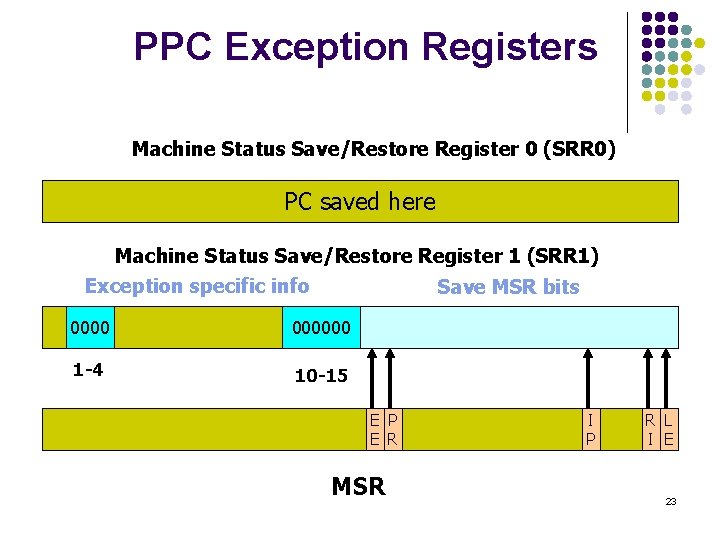

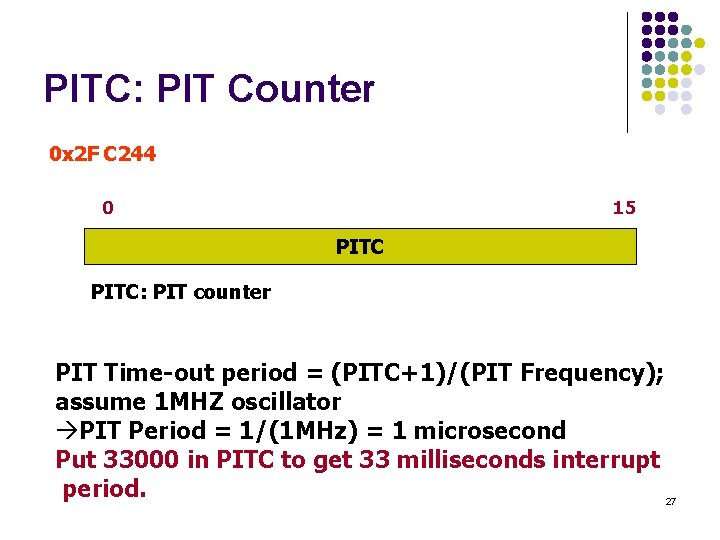

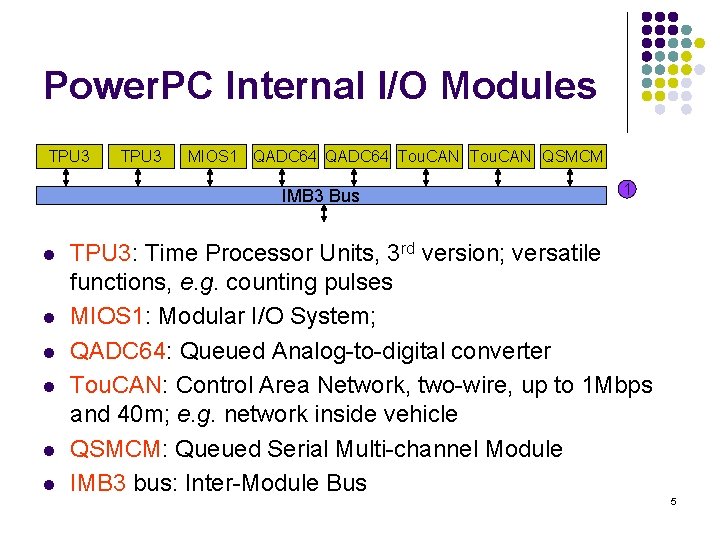

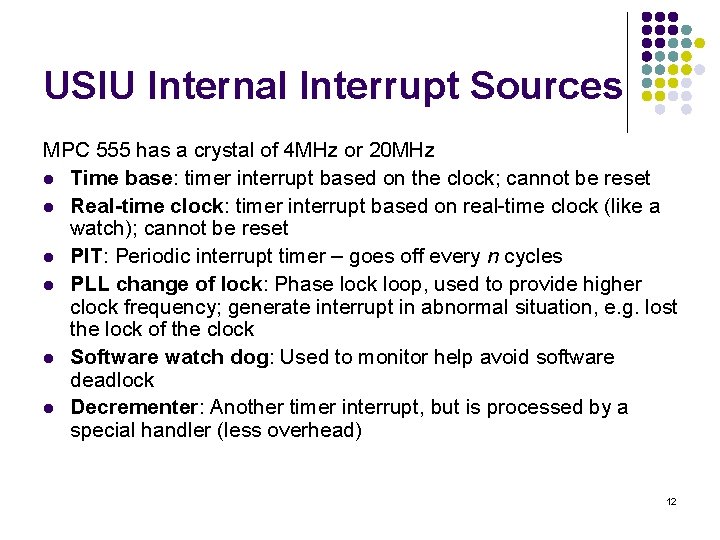

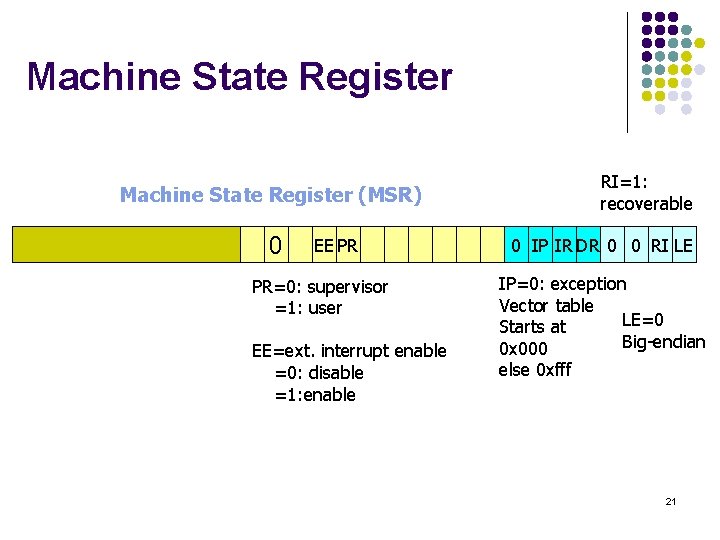

Interrupt Controller SIPEND[0: 31]: Interrupt pending register l Handler accesses SIPEND for source of interrupt l l l Bits 0 -15 record interrupt source; 16 -31 reserved External IRQ[0: 7]: accessing SIPEND is enough Internal IMB 3 device: further accessing UIPEND SIMASK: mask register l If SIMASK[i]= 0, then SIPEND[i] is blocked l SIMASK[0] = 0 has no effect SIVEC: interrupt vector register l Index to exception vector table l Accessed by interrupt service routine (ISR) NMI control: non-maskable interrupt control l External IRQ[0] is non-maskable l SW watchdog is non-maskable 11

USIU Internal Interrupt Sources MPC 555 has a crystal of 4 MHz or 20 MHz l Time base: timer interrupt based on the clock; cannot be reset l Real-time clock: timer interrupt based on real-time clock (like a watch); cannot be reset l PIT: Periodic interrupt timer – goes off every n cycles l PLL change of lock: Phase lock loop, used to provide higher clock frequency; generate interrupt in abnormal situation, e. g. lost the lock of the clock l Software watch dog: Used to monitor help avoid software deadlock l Decrementer: Another timer interrupt, but is processed by a special handler (less overhead) 12

![Connecting To Power PC Core Finally 5 MSREE IREQ 1 NMI 2 Decrementer Connecting To Power. PC Core Finally! 5 MSR[EE] IREQ 1 & NMI 2 Decrementer](https://slidetodoc.com/presentation_image/243e1c80fc9d0f6e2c8593001e7cc80f/image-13.jpg)

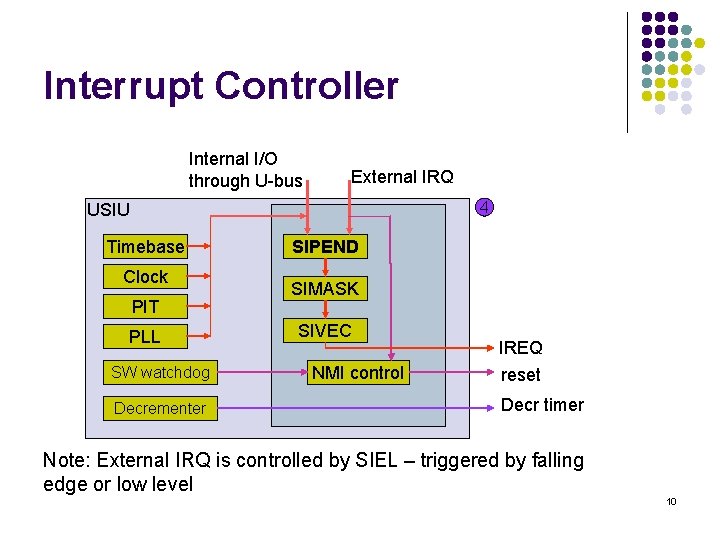

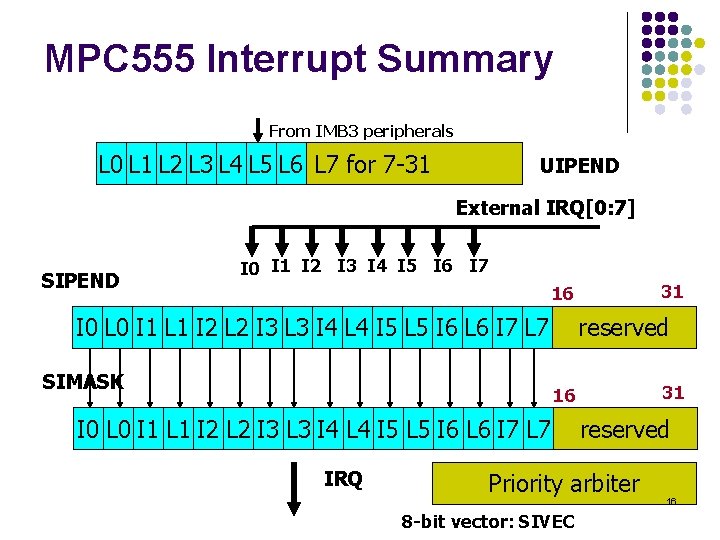

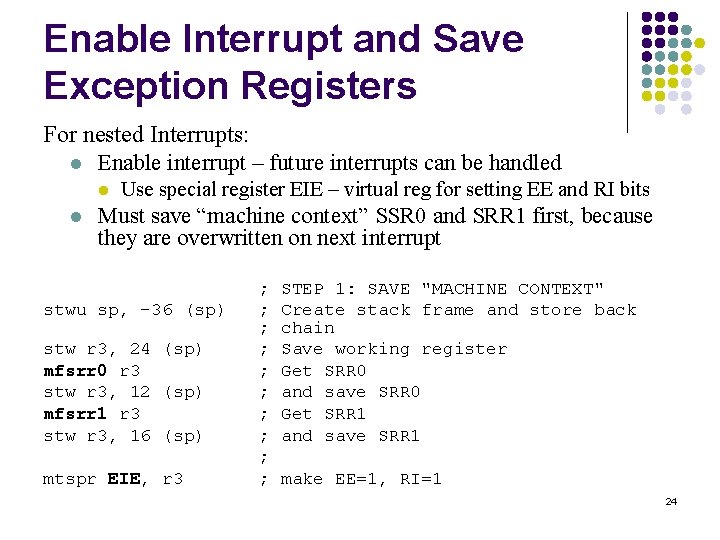

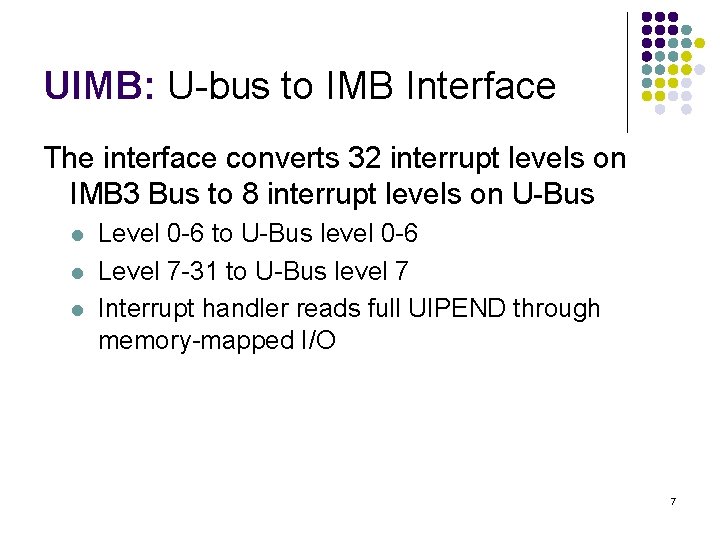

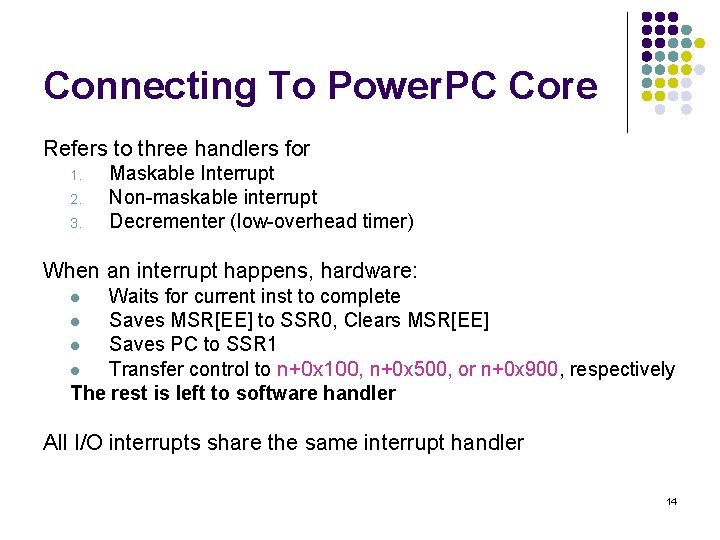

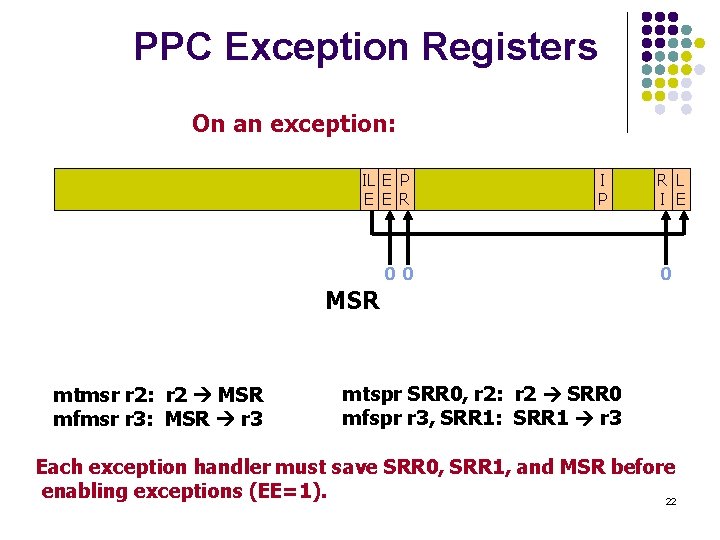

Connecting To Power. PC Core Finally! 5 MSR[EE] IREQ 1 & NMI 2 Decrementer 3 Vector table n+0 x 100 n+0 x 500 inst addr to mem n+0 x 900 SSR 1 Inst buffer inst Three interrupt lines to processor core: IREQ, NMI, and Decrementer l MSR[EE]: Enable external interrupt l IREQ: External interrupt l NMI: Non-maskable interrupt (e. g. reset button is pushed) l Decrementer: fast timer interrupt Other processor components not shown 13

Connecting To Power. PC Core Refers to three handlers for 1. 2. 3. Maskable Interrupt Non-maskable interrupt Decrementer (low-overhead timer) When an interrupt happens, hardware: Waits for current inst to complete l Saves MSR[EE] to SSR 0, Clears MSR[EE] l Saves PC to SSR 1 l Transfer control to n+0 x 100, n+0 x 500, or n+0 x 900, respectively The rest is left to software handler l All I/O interrupts share the same interrupt handler 14

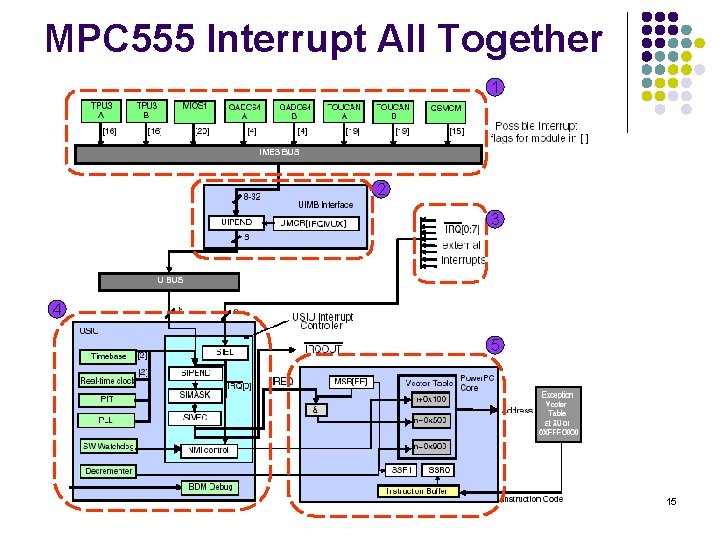

MPC 555 Interrupt All Together 1 2 3 4 5 15

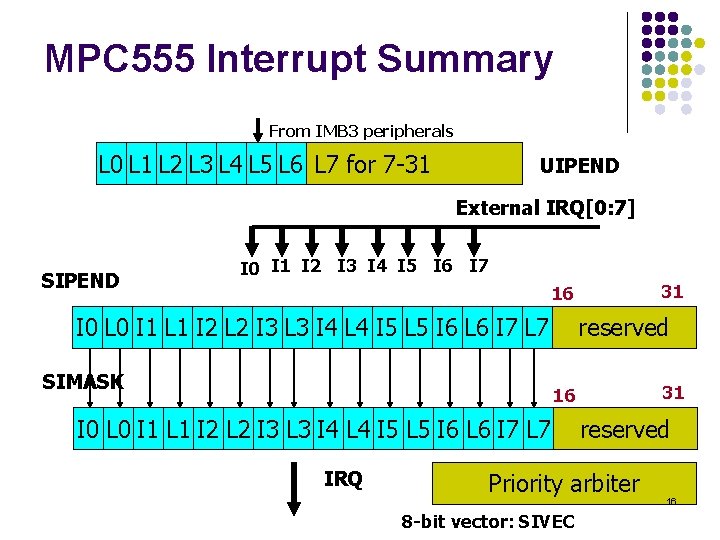

MPC 555 Interrupt Summary From IMB 3 peripherals L 0 L 1 L 2 L 3 L 4 L 5 L 6 L 7 for 7 -31 UIPEND External IRQ[0: 7] SIPEND I 0 I 1 I 2 I 3 I 4 I 5 I 6 I 7 31 16 I 0 L 0 I 1 L 1 I 2 L 2 I 3 L 3 I 4 L 4 I 5 L 5 I 6 L 6 I 7 L 7 SIMASK reserved 31 16 I 0 L 0 I 1 L 1 I 2 L 2 I 3 L 3 I 4 L 4 I 5 L 5 I 6 L 6 I 7 L 7 IRQ reserved Priority arbiter 8 -bit vector: SIVEC 16

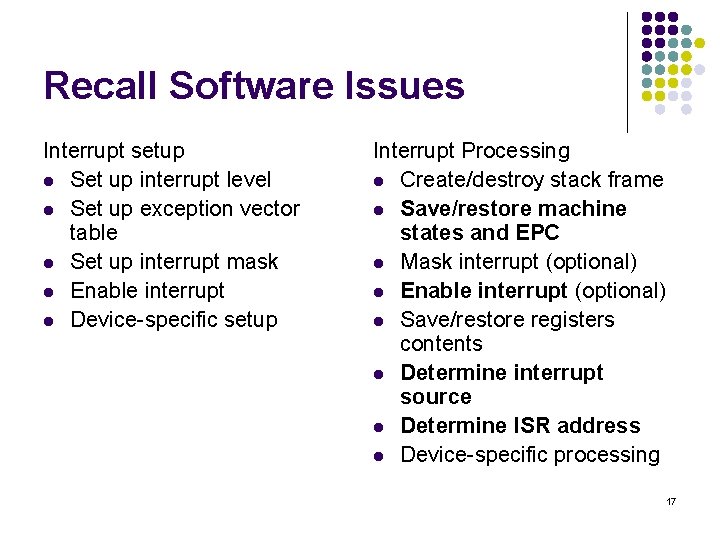

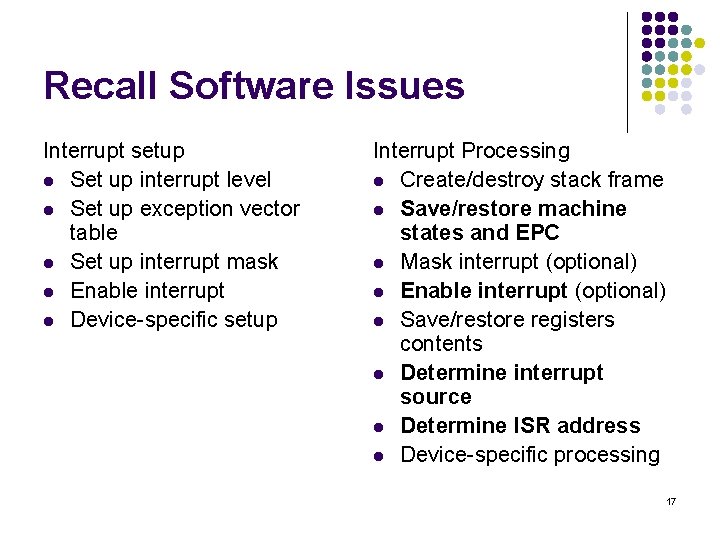

Recall Software Issues Interrupt setup l Set up interrupt level l Set up exception vector table l Set up interrupt mask l Enable interrupt l Device-specific setup Interrupt Processing l Create/destroy stack frame l Save/restore machine states and EPC l Mask interrupt (optional) l Enable interrupt (optional) l Save/restore registers contents l Determine interrupt source l Determine ISR address l Device-specific processing 17

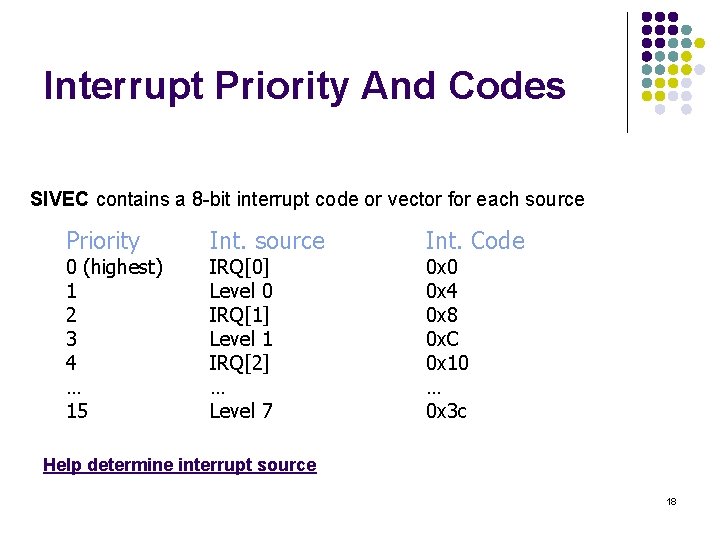

Interrupt Priority And Codes SIVEC contains a 8 -bit interrupt code or vector for each source Priority 0 (highest) 1 2 3 4 … 15 Int. source IRQ[0] Level 0 IRQ[1] Level 1 IRQ[2] … Level 7 Int. Code 0 x 0 0 x 4 0 x 8 0 x. C 0 x 10 … 0 x 3 c Help determine interrupt source 18

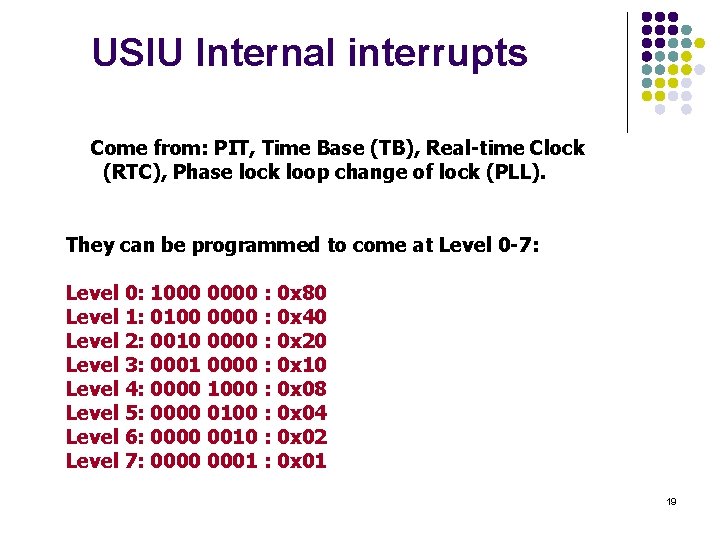

USIU Internal interrupts Come from: PIT, Time Base (TB), Real-time Clock (RTC), Phase lock loop change of lock (PLL). They can be programmed to come at Level 0 -7: Level 0: 1000 0000 : 0 x 80 Level 1: 0100 0000 : 0 x 40 Level 2: 0010 0000 : 0 x 20 Level 3: 0001 0000 : 0 x 10 Level 4: 0000 1000 : 0 x 08 Level 5: 0000 0100 : 0 x 04 Level 6: 0000 0010 : 0 x 02 Level 7: 0000 0001 : 0 x 01 19

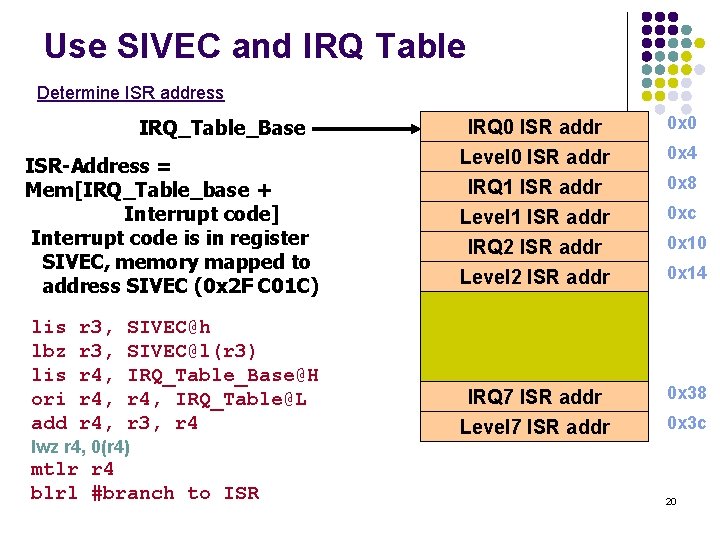

Use SIVEC and IRQ Table Determine ISR address IRQ_Table_Base ISR-Address = Mem[IRQ_Table_base + Interrupt code] Interrupt code is in register SIVEC, memory mapped to address SIVEC (0 x 2 F C 01 C) lis lbz lis ori add r 3, r 4, SIVEC@h SIVEC@l(r 3) IRQ_Table_Base@H r 4, IRQ_Table@L r 3, r 4 lwz r 4, 0(r 4) mtlr r 4 blrl #branch to ISR IRQ 0 ISR addr 0 x 0 Level 0 ISR addr IRQ 1 ISR addr Level 1 ISR addr IRQ 2 ISR addr 0 x 4 Level 2 ISR addr 0 x 14 IRQ 7 ISR addr Level 7 ISR addr 0 x 38 0 xc 0 x 10 0 x 3 c 20

Machine State Register (MSR) 0 EE PR PR=0: supervisor =1: user EE=ext. interrupt enable =0: disable =1: enable RI=1: recoverable 0 IP IR DR 0 0 RI LE IP=0: exception Vector table LE=0 Starts at Big-endian 0 x 000 else 0 xfff 21

PPC Exception Registers On an exception: IL E P E E R I P 00 R L I E 0 MSR mtmsr r 2: r 2 MSR mfmsr r 3: MSR r 3 mtspr SRR 0, r 2: r 2 SRR 0 mfspr r 3, SRR 1: SRR 1 r 3 Each exception handler must save SRR 0, SRR 1, and MSR before enabling exceptions (EE=1). 22

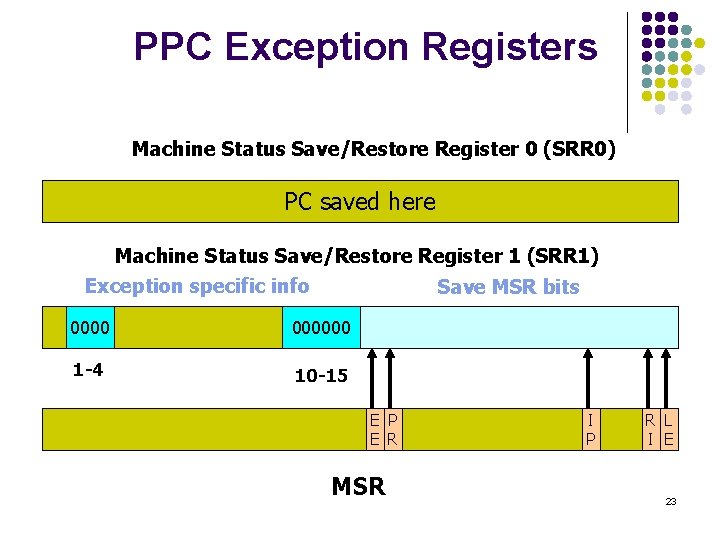

PPC Exception Registers Machine Status Save/Restore Register 0 (SRR 0) PC saved here Machine Status Save/Restore Register 1 (SRR 1) Exception specific info Save MSR bits 000000 1 -4 10 -15 E P E R MSR I P R L I E 23

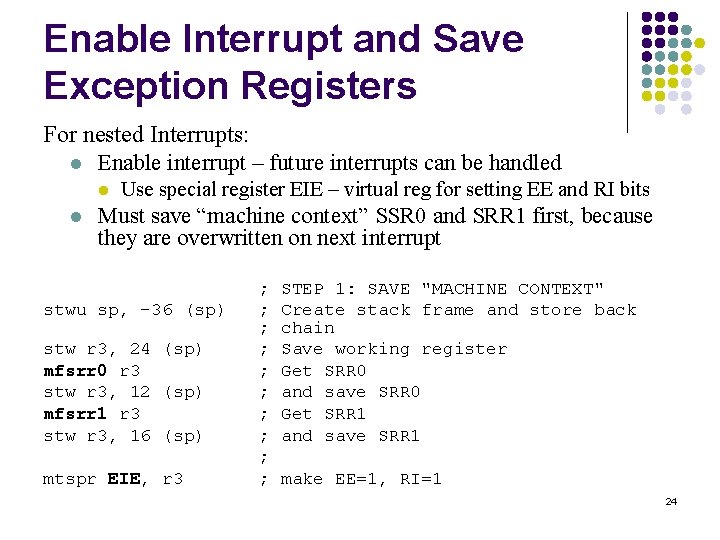

Enable Interrupt and Save Exception Registers For nested Interrupts: l Enable interrupt – future interrupts can be handled l l Use special register EIE – virtual reg for setting EE and RI bits Must save “machine context” SSR 0 and SRR 1 first, because they are overwritten on next interrupt stwu sp, -36 (sp) stw r 3, 24 (sp) mfsrr 0 r 3 stw r 3, 12 (sp) mfsrr 1 r 3 stw r 3, 16 (sp) mtspr EIE, r 3 ; ; ; ; ; STEP 1: SAVE "MACHINE CONTEXT" Create stack frame and store back chain Save working register Get SRR 0 and save SRR 0 Get SRR 1 and save SRR 1 make EE=1, RI=1 24

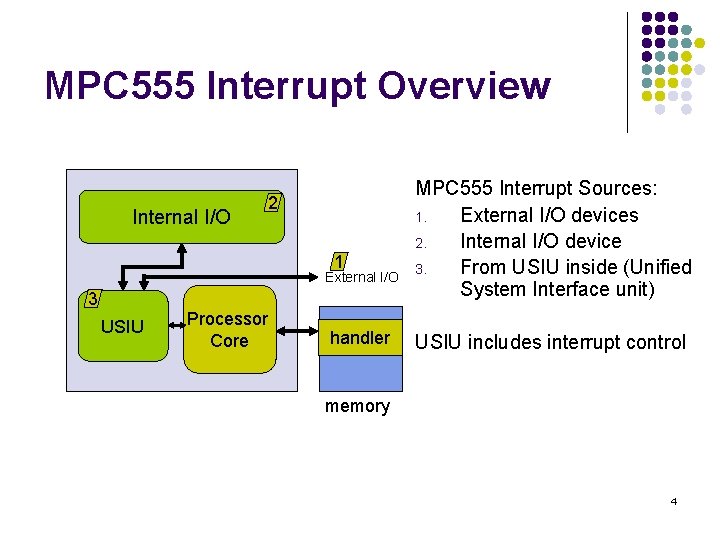

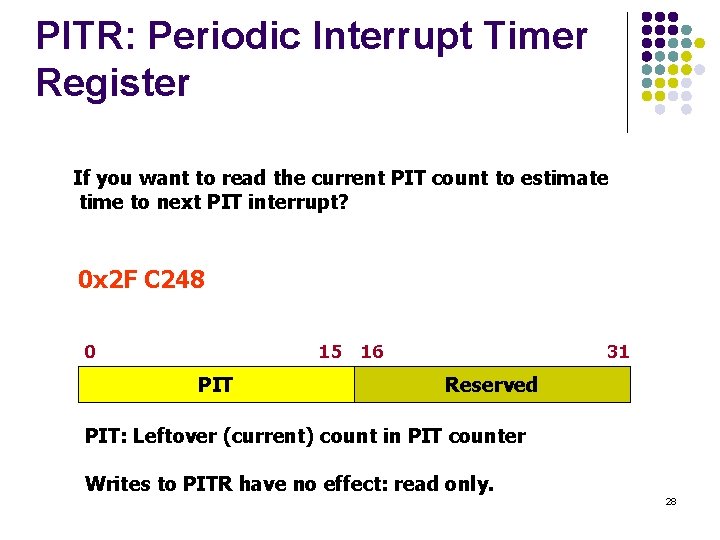

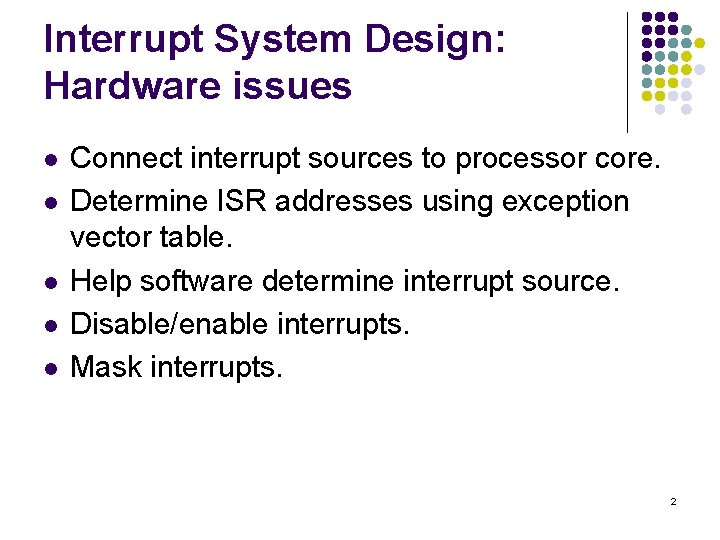

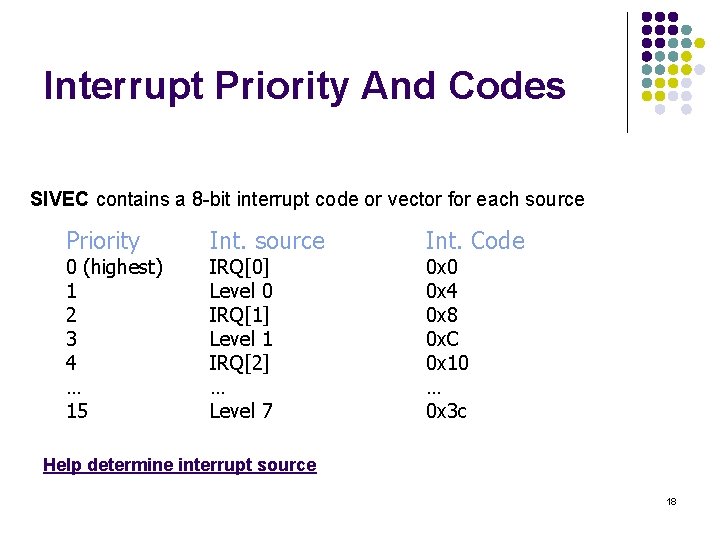

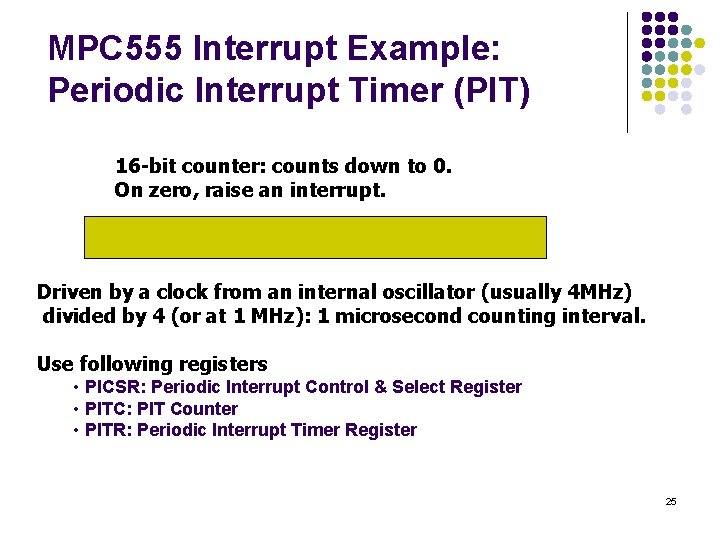

MPC 555 Interrupt Example: Periodic Interrupt Timer (PIT) 16 -bit counter: counts down to 0. On zero, raise an interrupt. Driven by a clock from an internal oscillator (usually 4 MHz) divided by 4 (or at 1 MHz): 1 microsecond counting interval. Use following registers • PICSR: Periodic Interrupt Control & Select Register • PITC: PIT Counter • PITR: Periodic Interrupt Timer Register 25

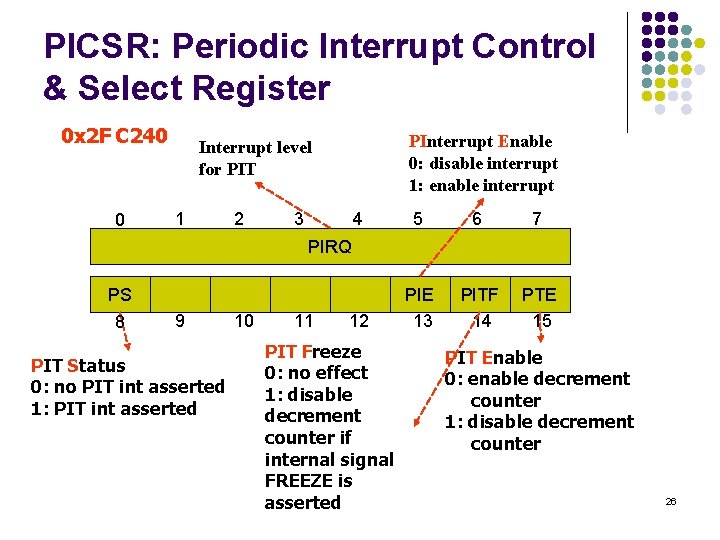

PICSR: Periodic Interrupt Control & Select Register 0 x 2 F C 240 0 PInterrupt Enable 0: disable interrupt 1: enable interrupt Interrupt level for PIT 1 2 3 4 5 6 7 12 PIE 13 PITF 14 PTE 15 PIRQ PS 8 9 PIT Status 0: no PIT int asserted 1: PIT int asserted 10 11 PIT Freeze 0: no effect 1: disable decrement counter if internal signal FREEZE is asserted PIT Enable 0: enable decrement counter 1: disable decrement counter 26

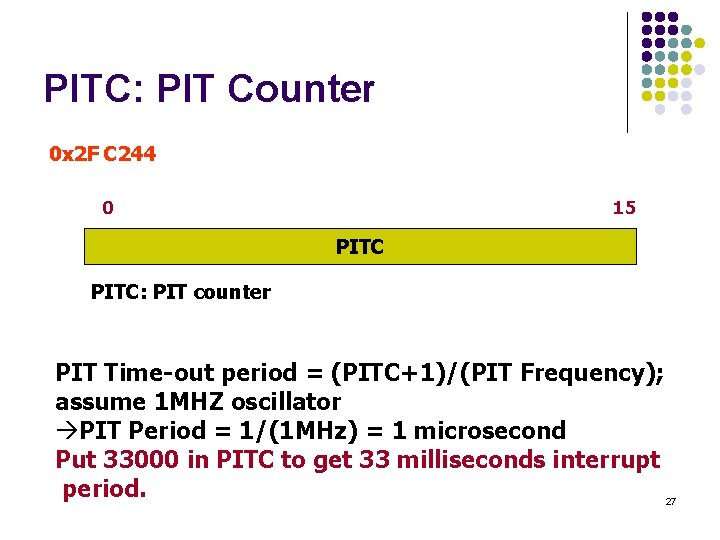

PITC: PIT Counter 0 x 2 F C 244 0 15 PITC: PIT counter PIT Time-out period = (PITC+1)/(PIT Frequency); assume 1 MHZ oscillator àPIT Period = 1/(1 MHz) = 1 microsecond Put 33000 in PITC to get 33 milliseconds interrupt period. 27

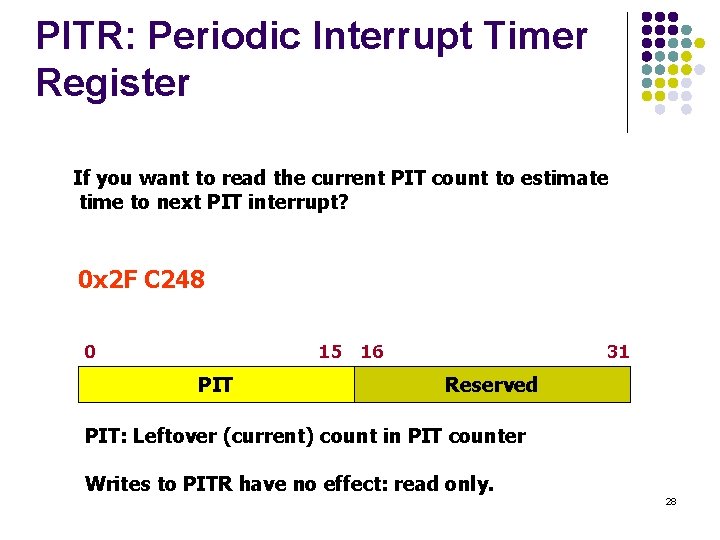

PITR: Periodic Interrupt Timer Register If you want to read the current PIT count to estimate time to next PIT interrupt? 0 x 2 F C 248 0 15 PIT 16 31 Reserved PIT: Leftover (current) count in PIT counter Writes to PITR have no effect: read only. 28

![PIT Block Diagram PTE PISCR15 pitrtclk clock Clock Disable PITF PITC 16 bit Modulus PIT Block Diagram PTE PISCR[15] pitrtclk clock Clock Disable PITF PITC 16 -bit Modulus](https://slidetodoc.com/presentation_image/243e1c80fc9d0f6e2c8593001e7cc80f/image-29.jpg)

PIT Block Diagram PTE PISCR[15] pitrtclk clock Clock Disable PITF PITC 16 -bit Modulus Counter PS PISCR[8] PIE PISCR[13] PIT interrupt PISCR[14] 29

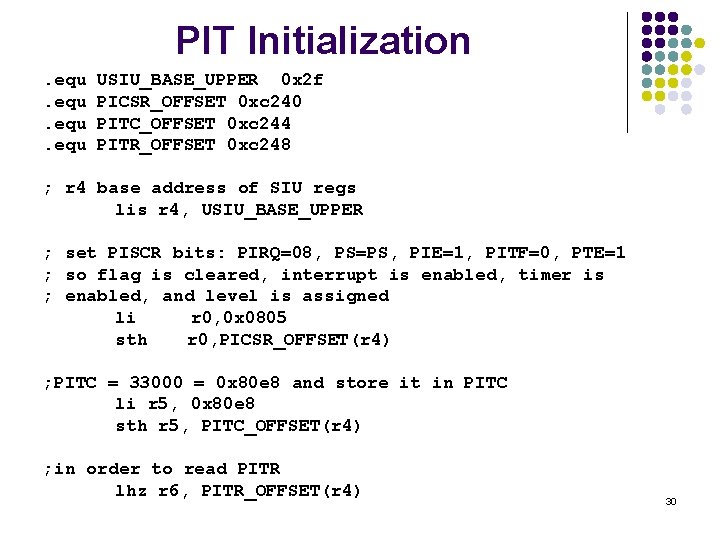

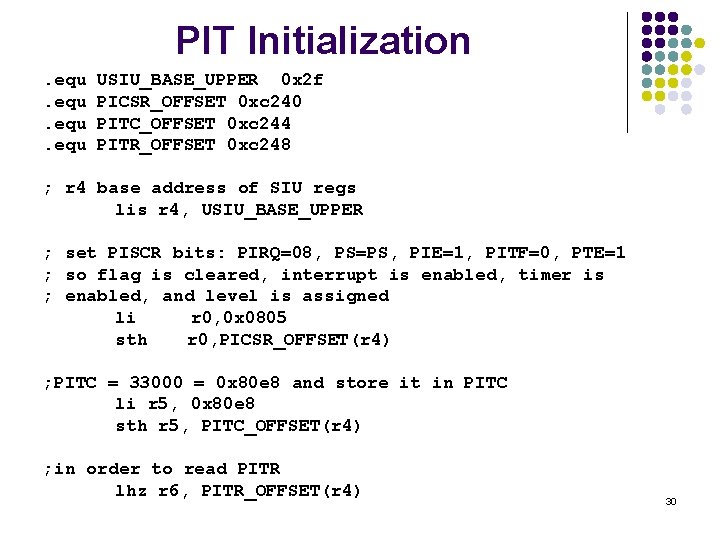

PIT Initialization. equ USIU_BASE_UPPER 0 x 2 f PICSR_OFFSET 0 xc 240 PITC_OFFSET 0 xc 244 PITR_OFFSET 0 xc 248 ; r 4 base address of SIU regs lis r 4, USIU_BASE_UPPER ; set PISCR bits: PIRQ=08, PS=PS, PIE=1, PITF=0, PTE=1 ; so flag is cleared, interrupt is enabled, timer is ; enabled, and level is assigned li r 0, 0 x 0805 sth r 0, PICSR_OFFSET(r 4) ; PITC = 33000 = 0 x 80 e 8 and store it in PITC li r 5, 0 x 80 e 8 sth r 5, PITC_OFFSET(r 4) ; in order to read PITR lhz r 6, PITR_OFFSET(r 4) 30

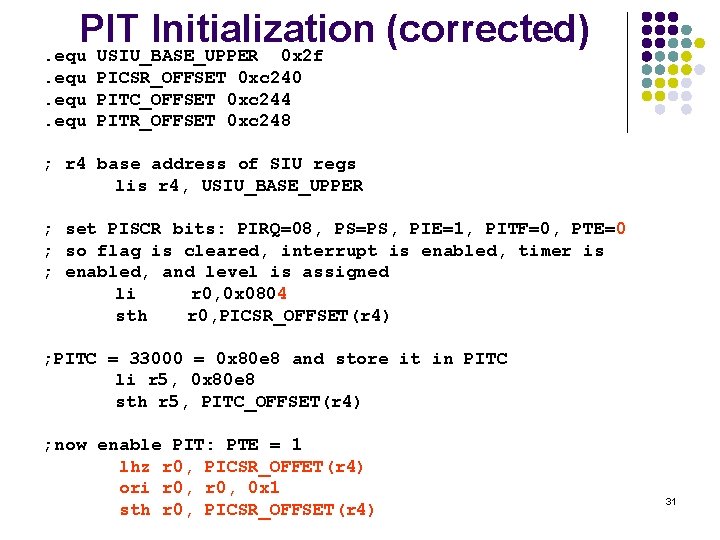

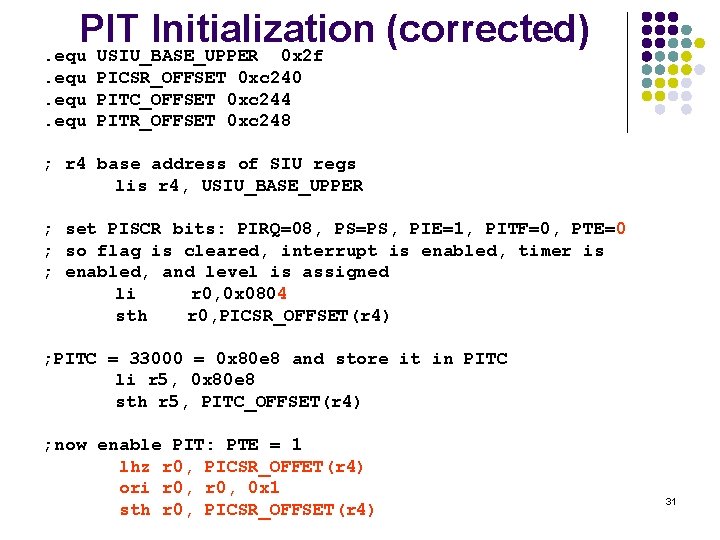

PIT Initialization (corrected). equ USIU_BASE_UPPER 0 x 2 f. equ PICSR_OFFSET 0 xc 240. equ PITC_OFFSET 0 xc 244. equ PITR_OFFSET 0 xc 248 ; r 4 base address of SIU regs lis r 4, USIU_BASE_UPPER ; set PISCR bits: PIRQ=08, PS=PS, PIE=1, PITF=0, PTE=0 ; so flag is cleared, interrupt is enabled, timer is ; enabled, and level is assigned li r 0, 0 x 0804 sth r 0, PICSR_OFFSET(r 4) ; PITC = 33000 = 0 x 80 e 8 and store it in PITC li r 5, 0 x 80 e 8 sth r 5, PITC_OFFSET(r 4) ; now enable PIT: PTE = 1 lhz r 0, PICSR_OFFET(r 4) ori r 0, 0 x 1 sth r 0, PICSR_OFFSET(r 4) 31