MPC 555 Queued Serial Module 1 MPC 555

- Slides: 19

MPC 555: Queued Serial Module 1

MPC 555 QSM QSPI: Queued Serial Peripheral Interface: full duplex serial, synchronous interface. 160 B of queue RAM. SCI 1 & 2: serial communication interfaces 2

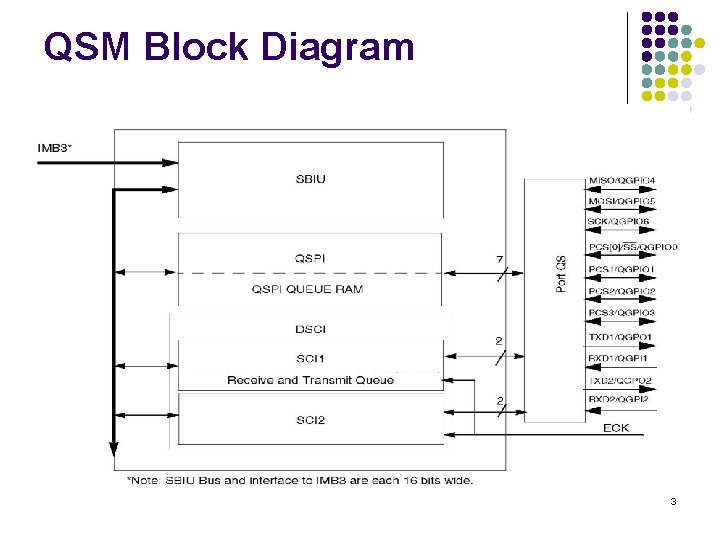

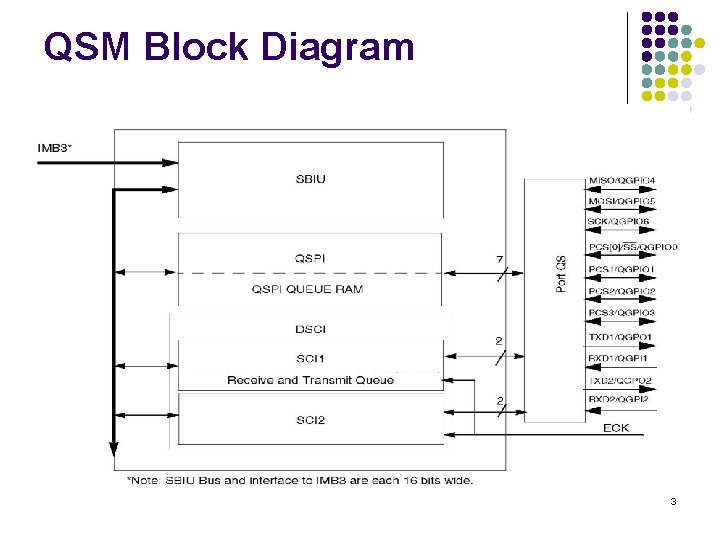

QSM Block Diagram 3

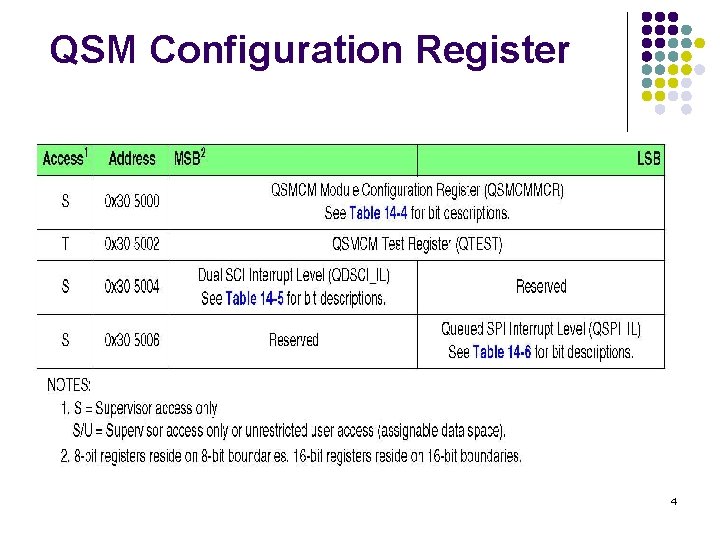

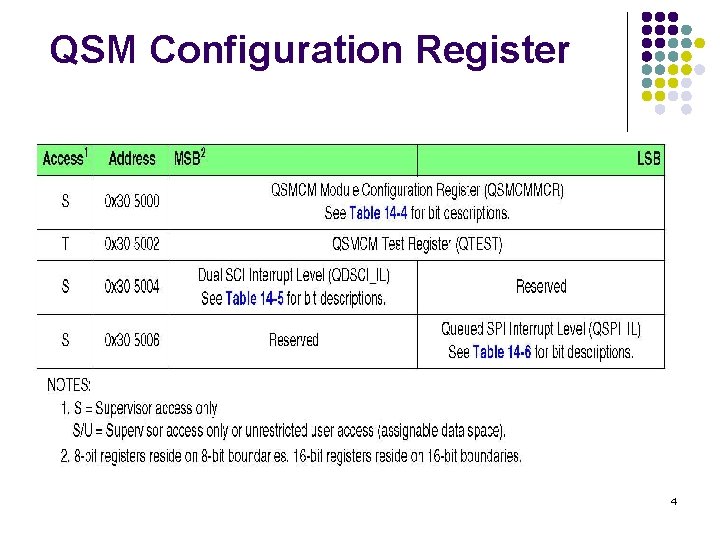

QSM Configuration Register 4

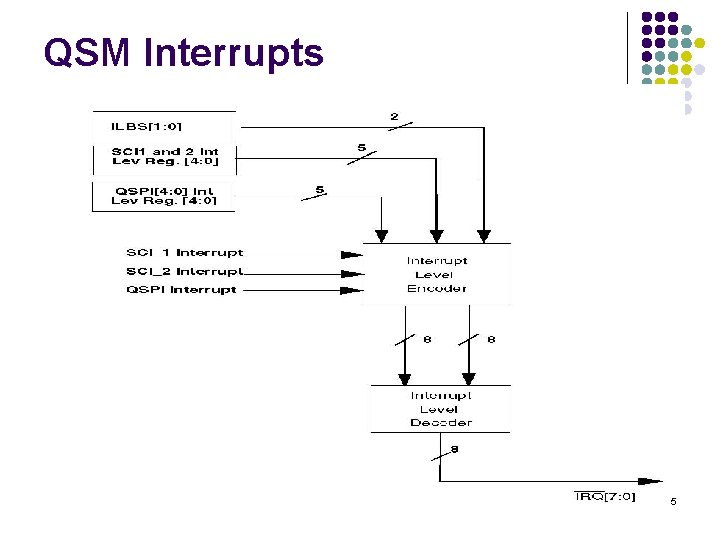

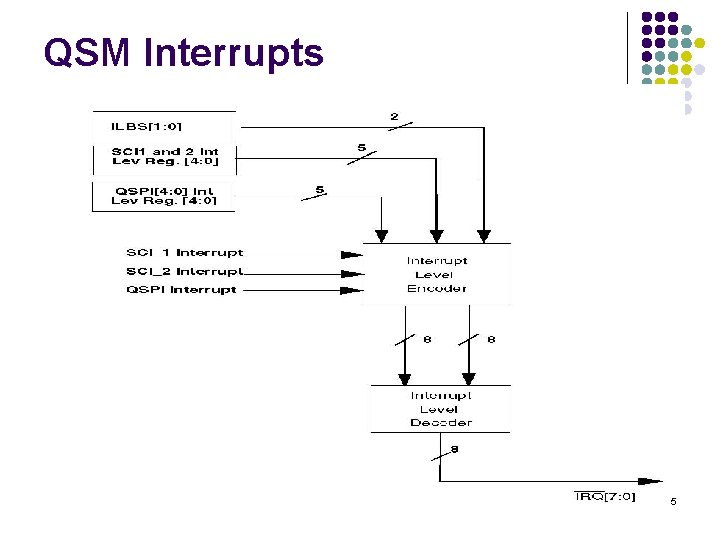

QSM Interrupts 5

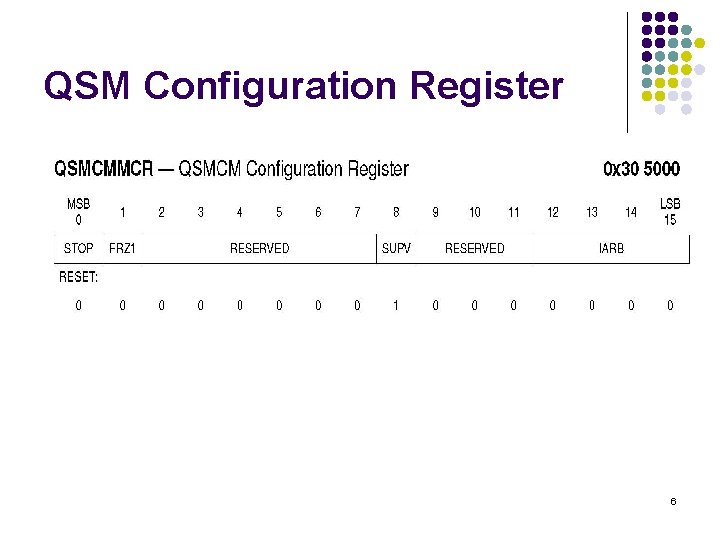

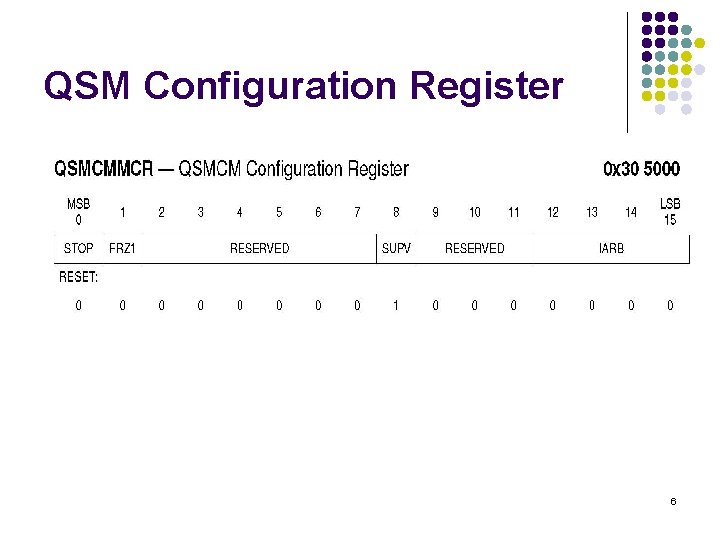

QSM Configuration Register 6

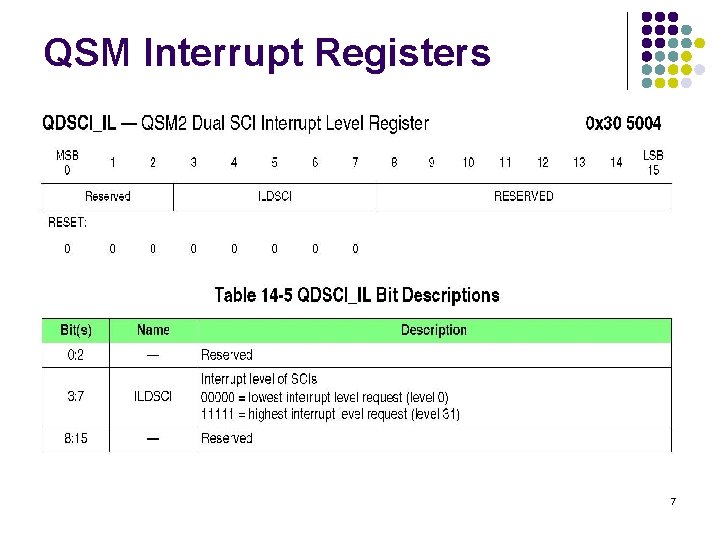

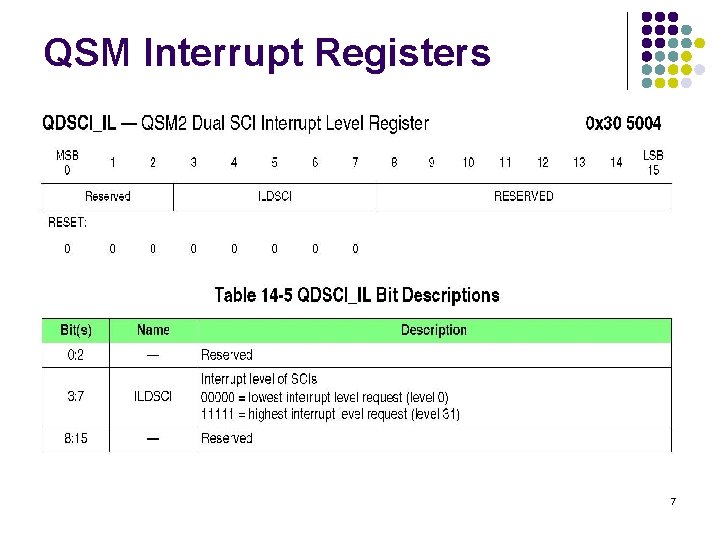

QSM Interrupt Registers 7

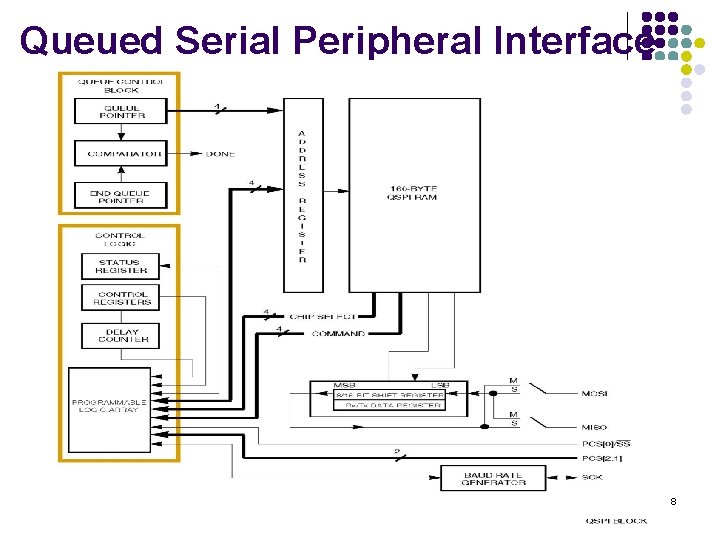

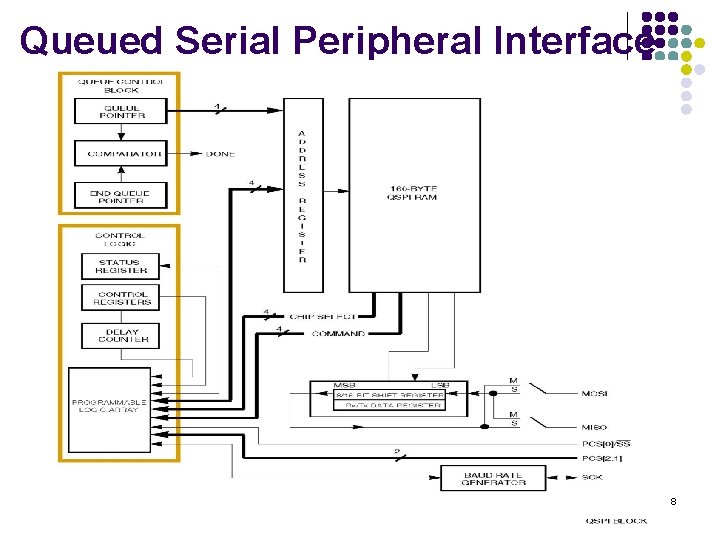

Queued Serial Peripheral Interface 8

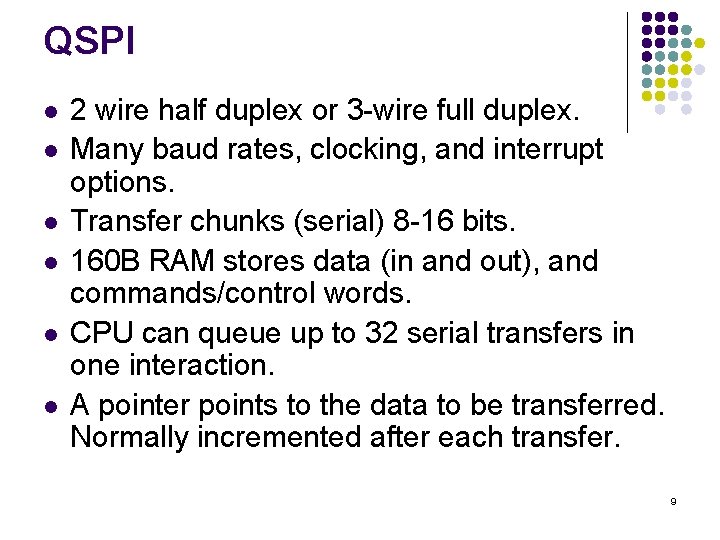

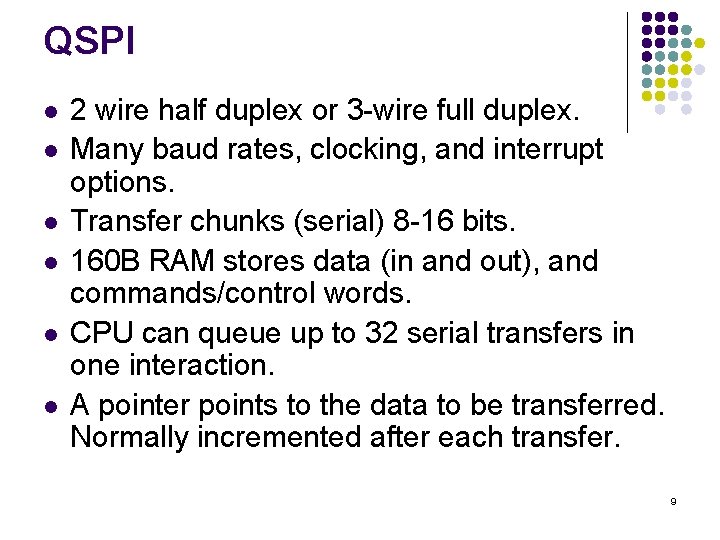

QSPI l l l 2 wire half duplex or 3 -wire full duplex. Many baud rates, clocking, and interrupt options. Transfer chunks (serial) 8 -16 bits. 160 B RAM stores data (in and out), and commands/control words. CPU can queue up to 32 serial transfers in one interaction. A pointer points to the data to be transferred. Normally incremented after each transfer. 9

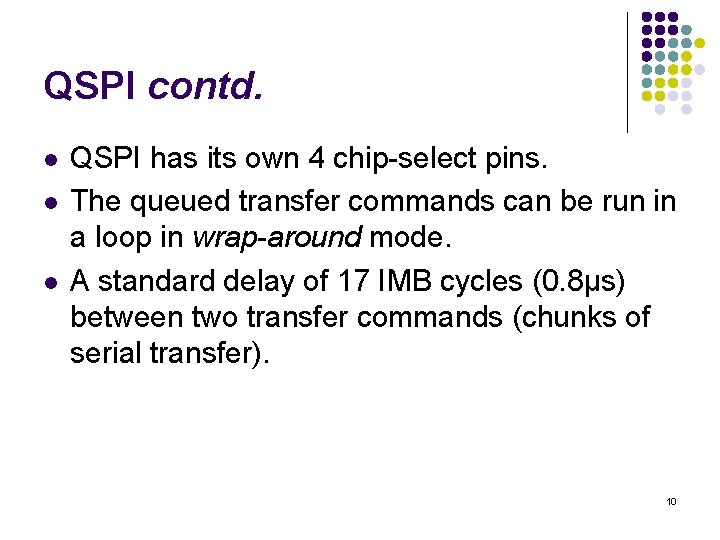

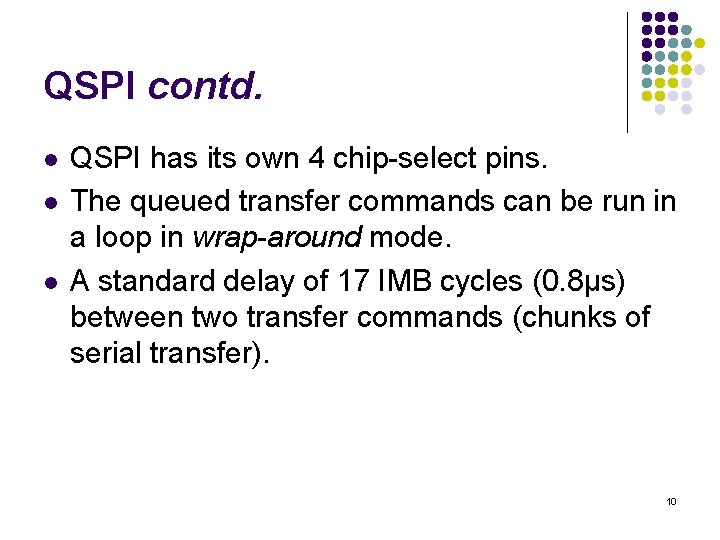

QSPI contd. l l l QSPI has its own 4 chip-select pins. The queued transfer commands can be run in a loop in wrap-around mode. A standard delay of 17 IMB cycles (0. 8µs) between two transfer commands (chunks of serial transfer). 10

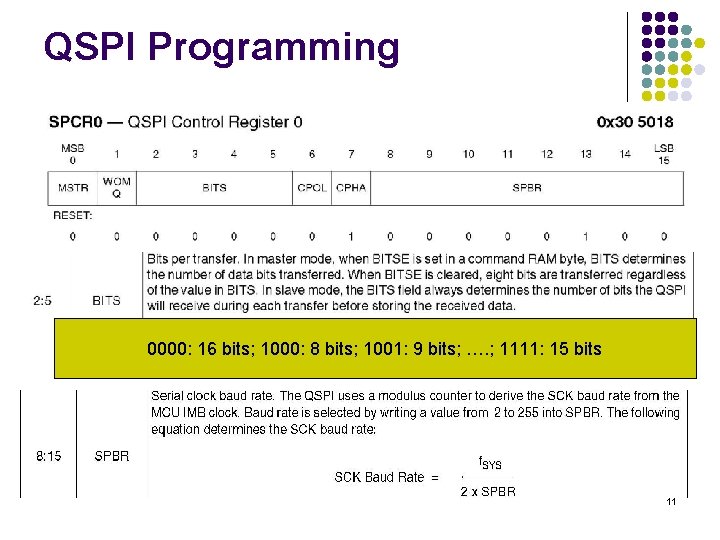

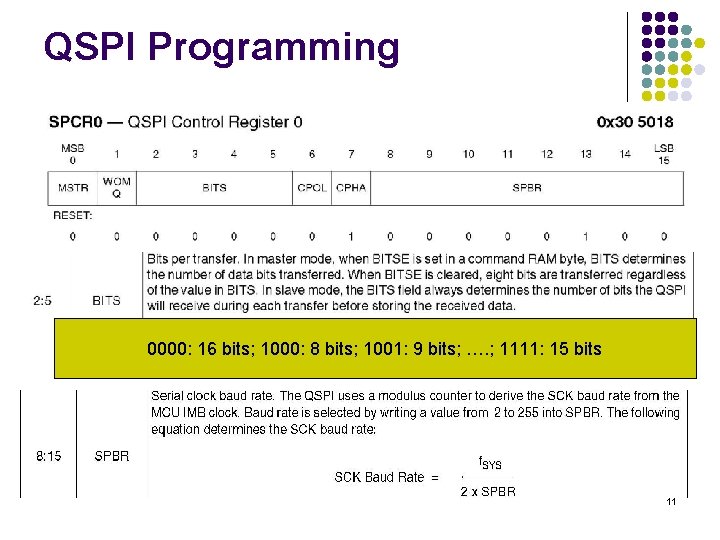

QSPI Programming 0000: 16 bits; 1000: 8 bits; 1001: 9 bits; …. ; 1111: 15 bits 11

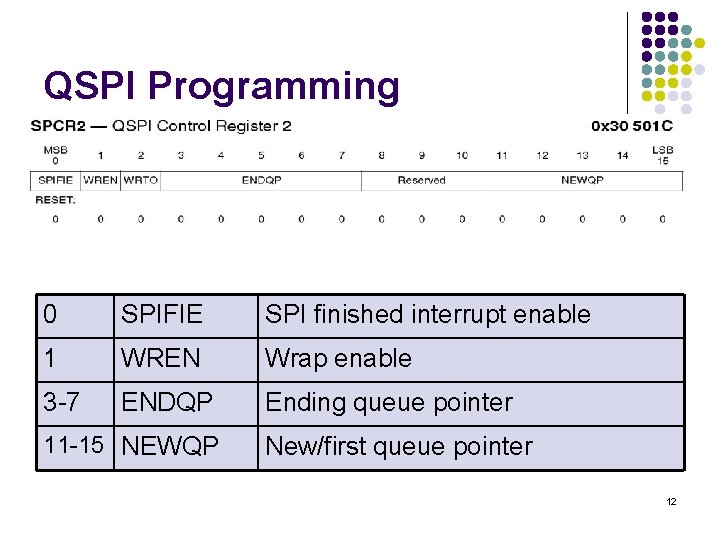

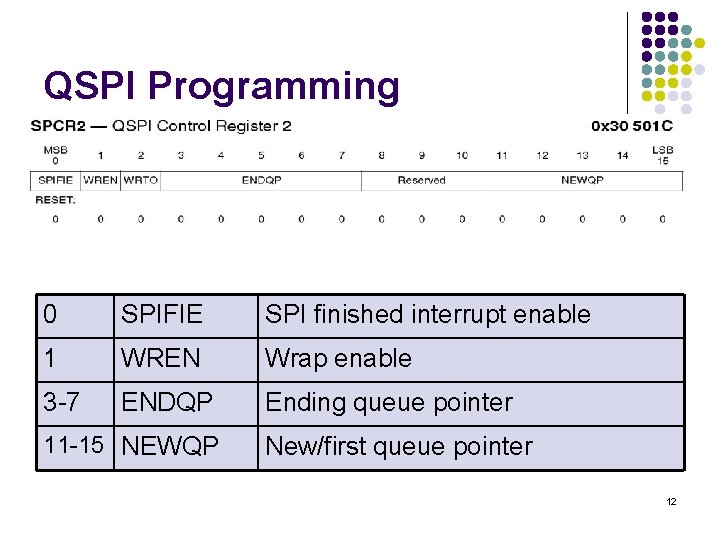

QSPI Programming 0 SPIFIE SPI finished interrupt enable 1 WREN Wrap enable 3 -7 ENDQP Ending queue pointer 11 -15 NEWQP New/first queue pointer 12

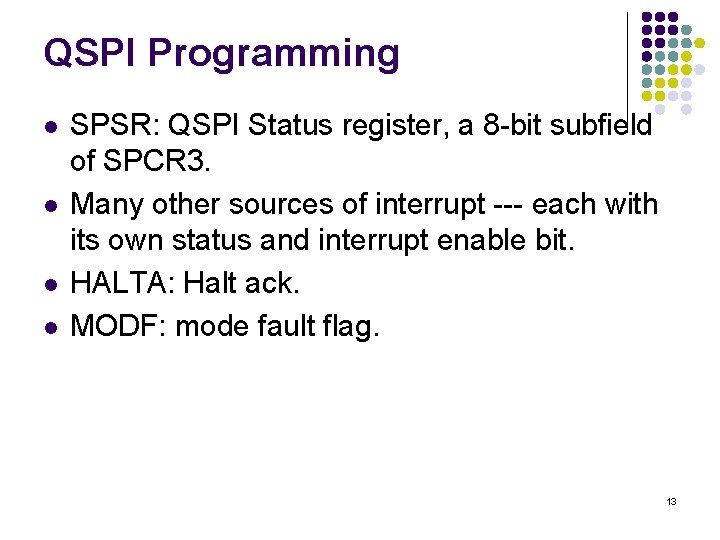

QSPI Programming l l SPSR: QSPI Status register, a 8 -bit subfield of SPCR 3. Many other sources of interrupt --- each with its own status and interrupt enable bit. HALTA: Halt ack. MODF: mode fault flag. 13

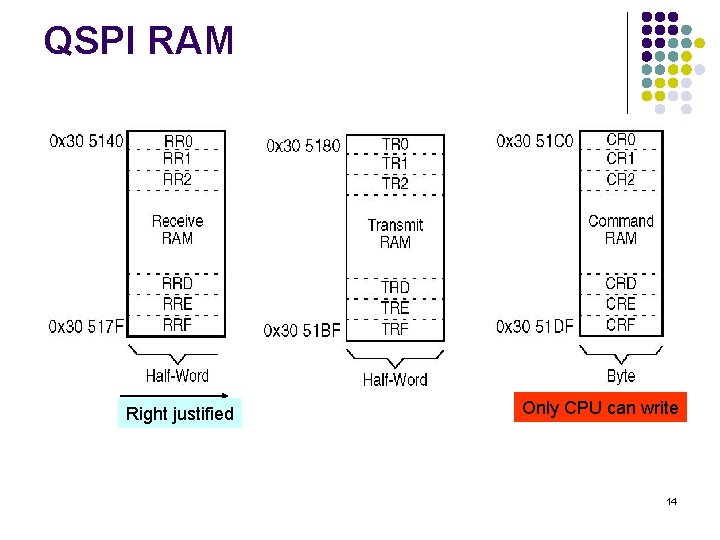

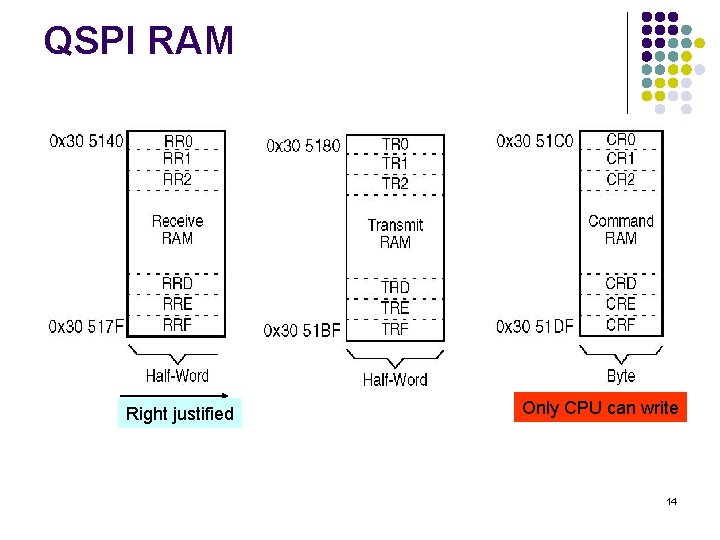

QSPI RAM Right justified Only CPU can write 14

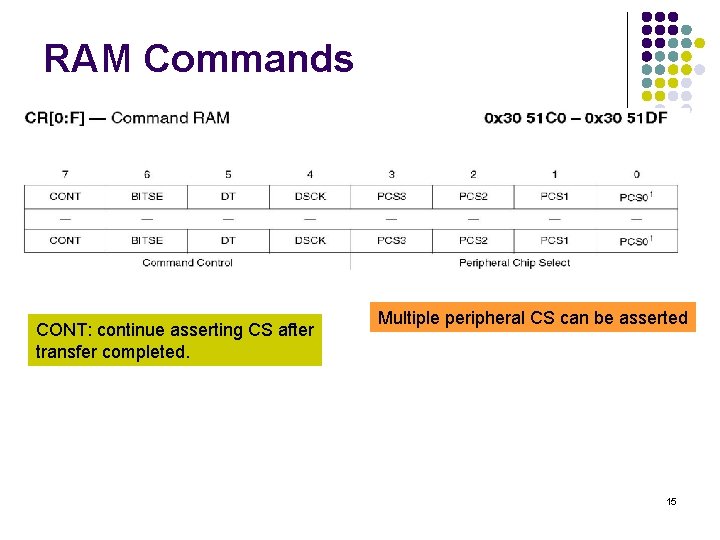

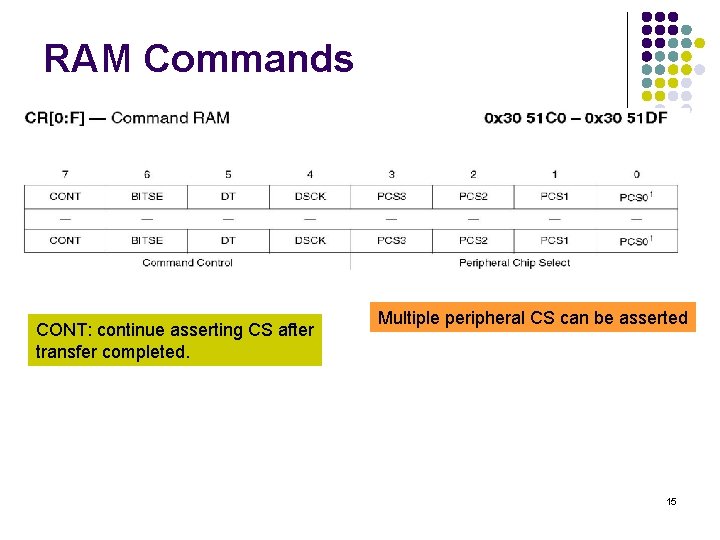

RAM Commands CONT: continue asserting CS after transfer completed. Multiple peripheral CS can be asserted 15

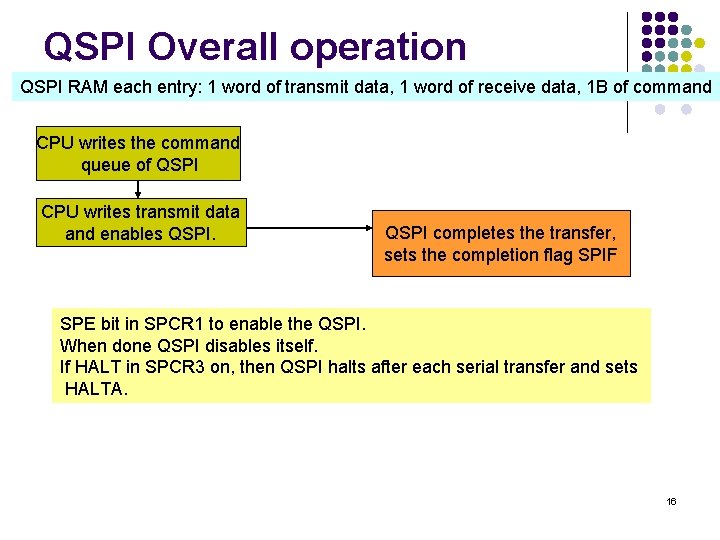

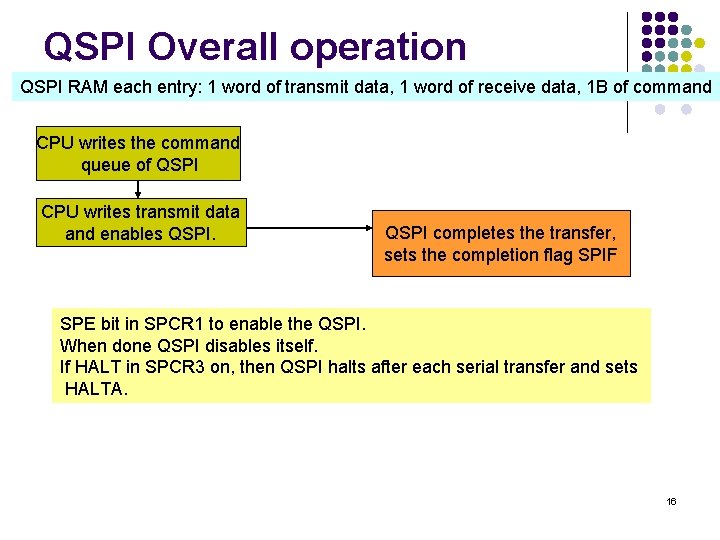

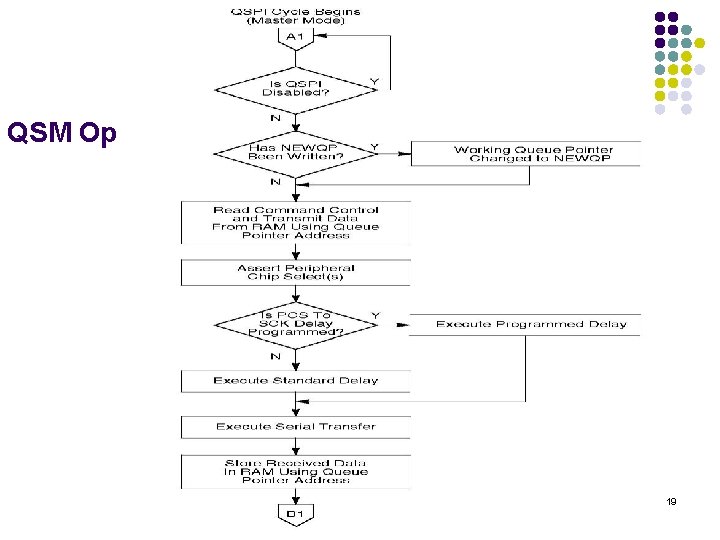

QSPI Overall operation QSPI RAM each entry: 1 word of transmit data, 1 word of receive data, 1 B of command CPU writes the command queue of QSPI CPU writes transmit data and enables QSPI completes the transfer, sets the completion flag SPIF SPE bit in SPCR 1 to enable the QSPI. When done QSPI disables itself. If HALT in SPCR 3 on, then QSPI halts after each serial transfer and sets HALTA. 16

QSPI Interrupt sources l l Three sources of interrupt (all on the same vector). SPIF (finished). MODF: Mode fault (inconsistent configuration). HALTA: acknowledge HALT. 17

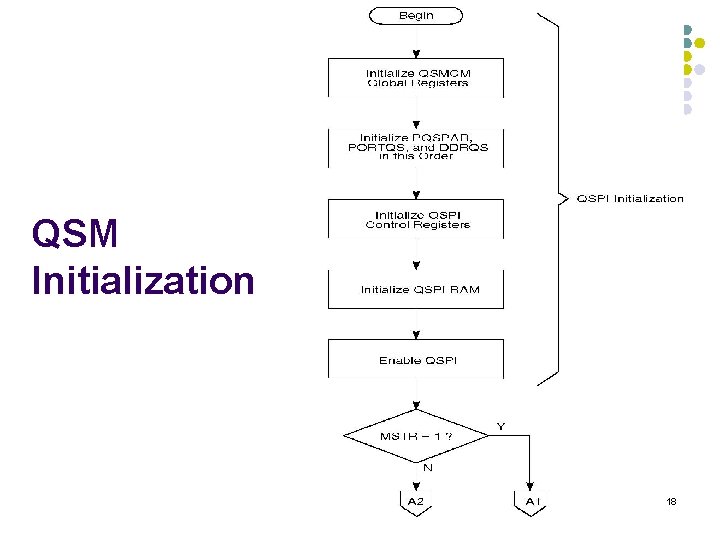

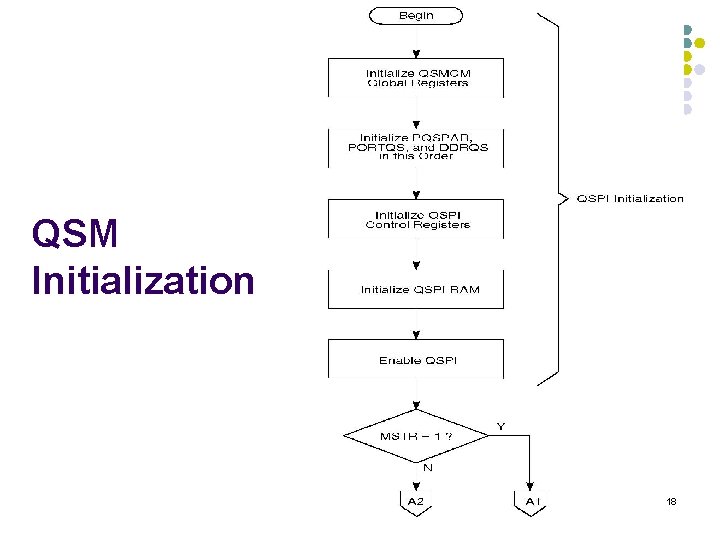

QSM Initialization 18

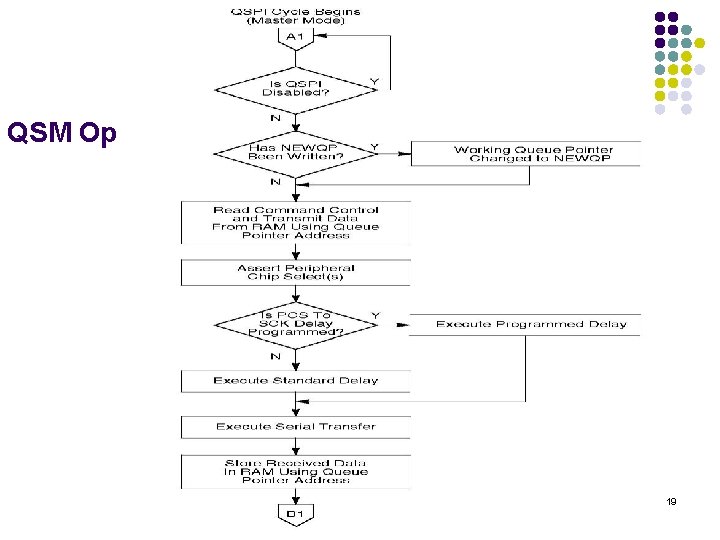

QSM Op 19