Introduction to Computer Architecture 2471 CE Computer Architecture

- Slides: 28

Introduction to Computer Architecture 2471 CE– Computer Architecture Instructor: Mustafa Alqudah Department of Computer and Information Science

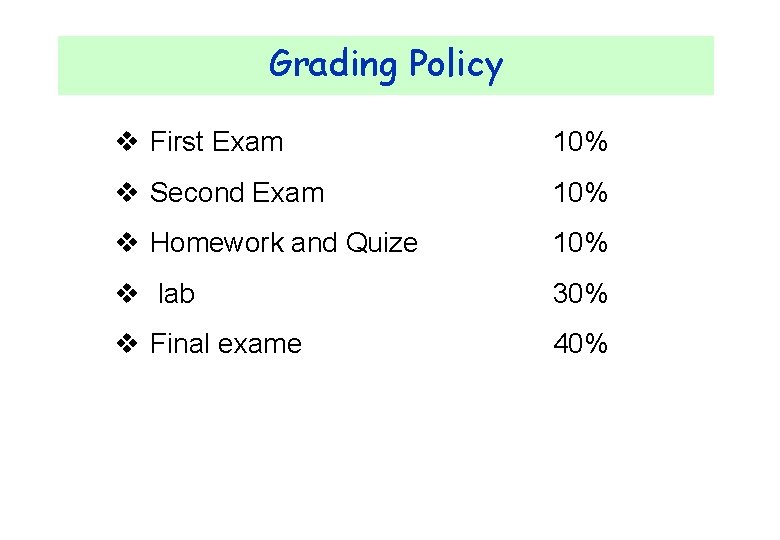

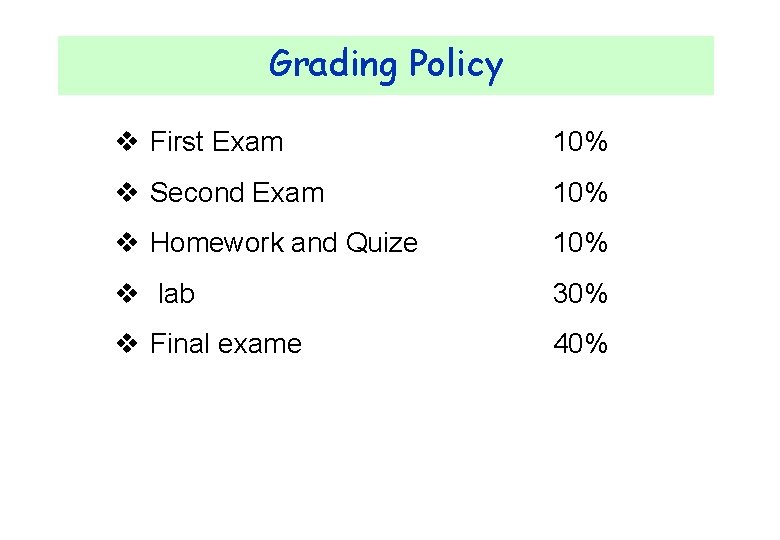

Grading Policy v First Exam 10% v Second Exam 10% v Homework and Quize 10% v lab 30% v Final exame 40%

Software v MIPS Simulators MARS: MIPS Assembly and Runtime Simulator ² Runs MIPS-32 assembly language programs

Why Study Computer Architecture? v You want to be called “Computer Engineer or Scientist” v You want to become an “expert” on computer hardware v You want to become a “computer system designer” v You want to become a “software designer” and need to understand how to improve code performance v Technology is improving rapidly new opportunities v Has never been more exciting! v Impacts Electrical Engineering and Computer Science

Which Books will be Used? v Computer Organization & Design The Hardware/Software Interface David Patterson and John Hennessy Morgan Kaufmann Publishers Fifth Edition (2014) v References: MIPS 32 Architecture

Course Objectives v Understand modern computers, their evolution, and trade -offs at the HW/SW interface Instruction Set Architecture Computer Arithmetic Performance and Metrics Pipelining v Understand the design of a modern computer system Datapath design Control design Memory System Design I/O System Design

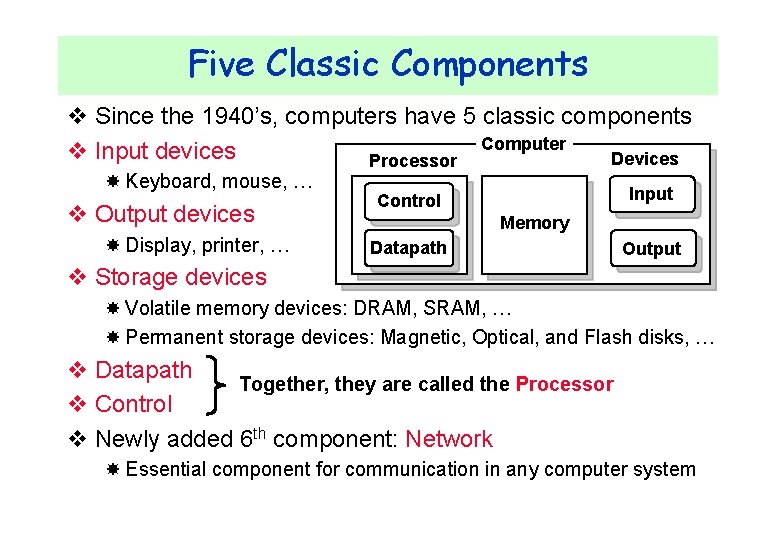

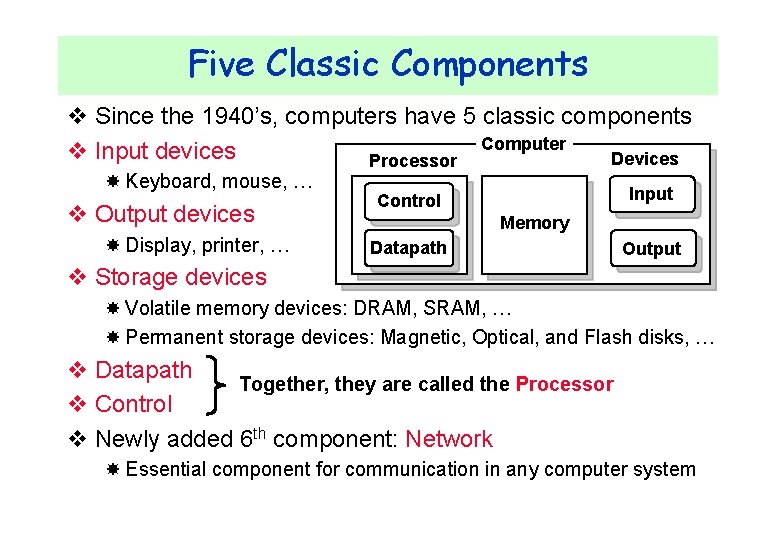

Five Classic Components v Since the 1940’s, computers have 5 classic components Computer v Input devices Devices Processor Keyboard, mouse, … v Output devices Display, printer, … Input Control Memory Datapath Output v Storage devices Volatile memory devices: DRAM, SRAM, … Permanent storage devices: Magnetic, Optical, and Flash disks, … v Datapath Together, they are called the Processor v Control v Newly added 6 th component: Network Essential component for communication in any computer system

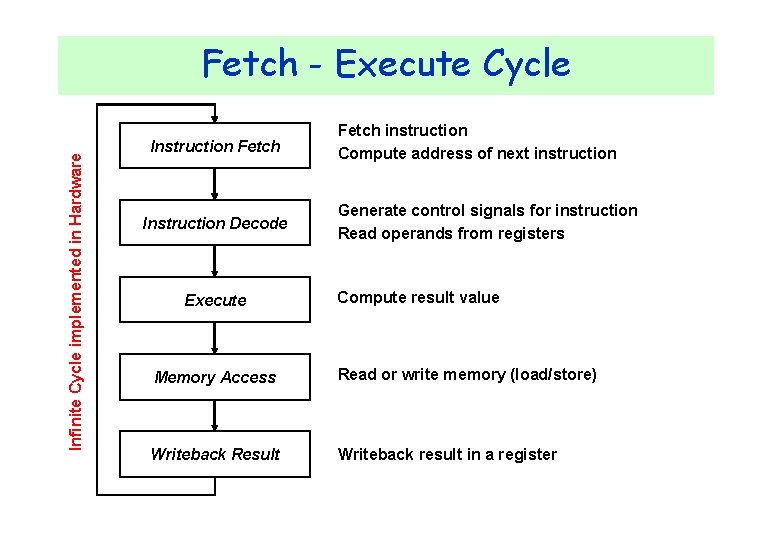

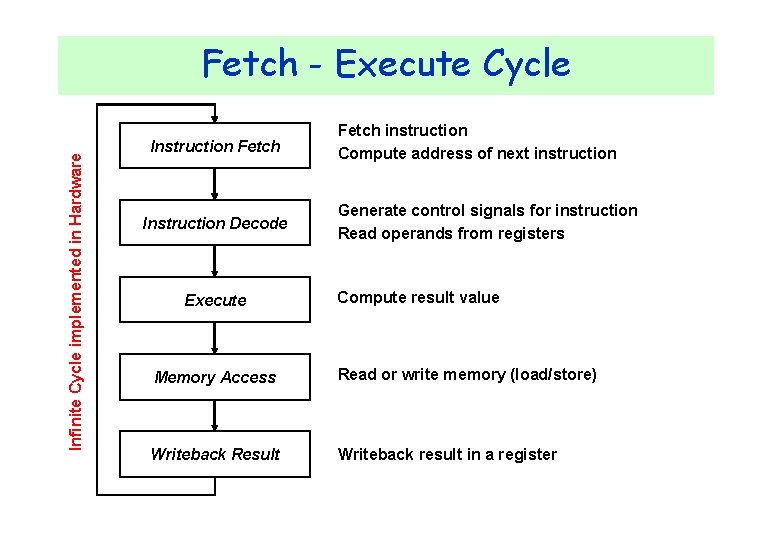

Infinite Cycle implemented in Hardware Fetch - Execute Cycle Instruction Fetch Instruction Decode Execute Fetch instruction Compute address of next instruction Generate control signals for instruction Read operands from registers Compute result value Memory Access Read or write memory (load/store) Writeback Result Writeback result in a register

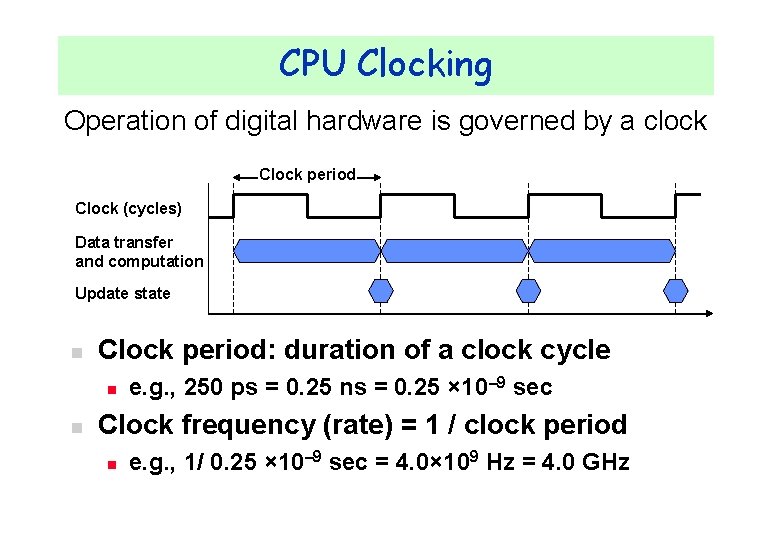

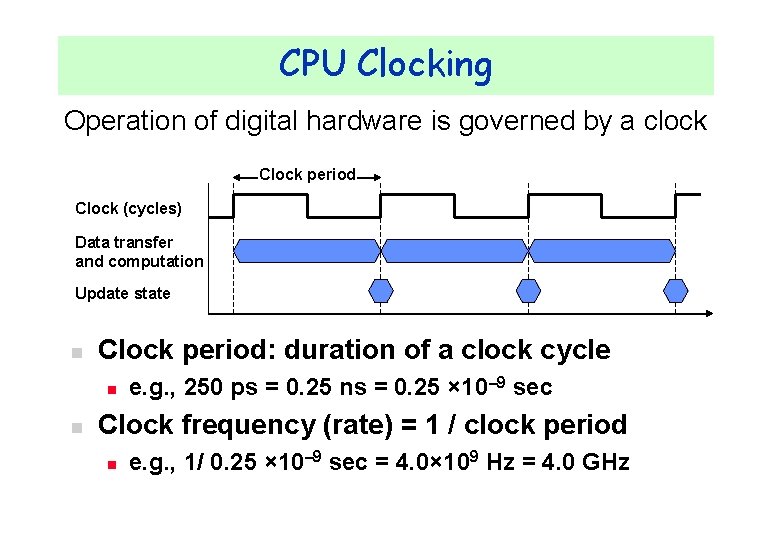

CPU Clocking Operation of digital hardware is governed by a clock Clock period Clock (cycles) Data transfer and computation Update state n Clock period: duration of a clock cycle n n e. g. , 250 ps = 0. 25 ns = 0. 25 × 10– 9 sec Clock frequency (rate) = 1 / clock period n e. g. , 1/ 0. 25 × 10– 9 sec = 4. 0× 109 Hz = 4. 0 GHz

What is “Computer Architecture” ? v Computer Architecture = Instruction Set Architecture + Computer Organization v Instruction Set Architecture (ISA) WHAT the computer does (logical view) v Computer Organization HOW the ISA is implemented (physical view) v We will study both in this course

Instruction Set Architecture (ISA) v Is a subset of Computer Architecture v Definition by Amdahl, Blaaw, and Brooks – 1964 “… the attributes of a [computing] system as seen by the programmer, i. e. the conceptual structure and functional behavior, as distinct from the organization of the data flows and controls the logic design, and the physical implementation. ” v An ISA encompasses … Instructions and Instruction Formats Data Types, Encodings, and Representations Programmable Storage: Registers and Memory Addressing Modes: Accessing Instructions and Data Handling Exceptional Conditions

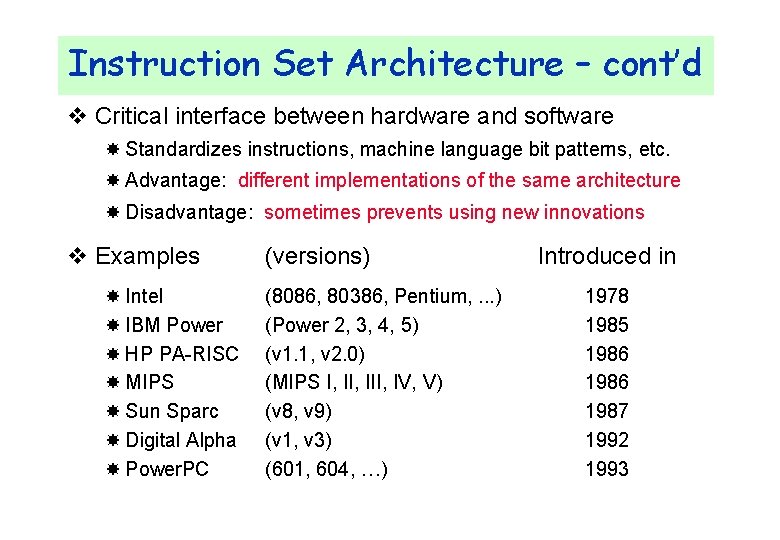

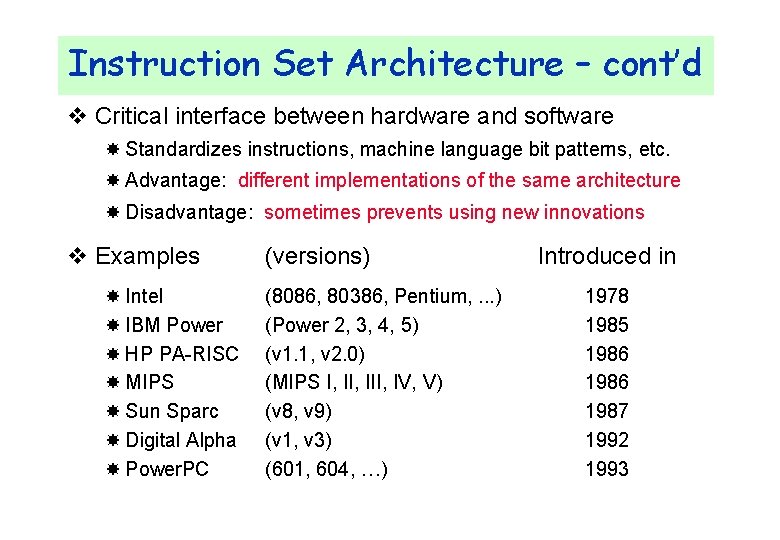

Instruction Set Architecture – cont’d v Critical interface between hardware and software Standardizes instructions, machine language bit patterns, etc. Advantage: different implementations of the same architecture Disadvantage: sometimes prevents using new innovations v Examples Intel IBM Power HP PA-RISC MIPS Sun Sparc Digital Alpha Power. PC (versions) (8086, 80386, Pentium, . . . ) (Power 2, 3, 4, 5) (v 1. 1, v 2. 0) (MIPS I, III, IV, V) (v 8, v 9) (v 1, v 3) (601, 604, …) Introduced in 1978 1985 1986 1987 1992 1993

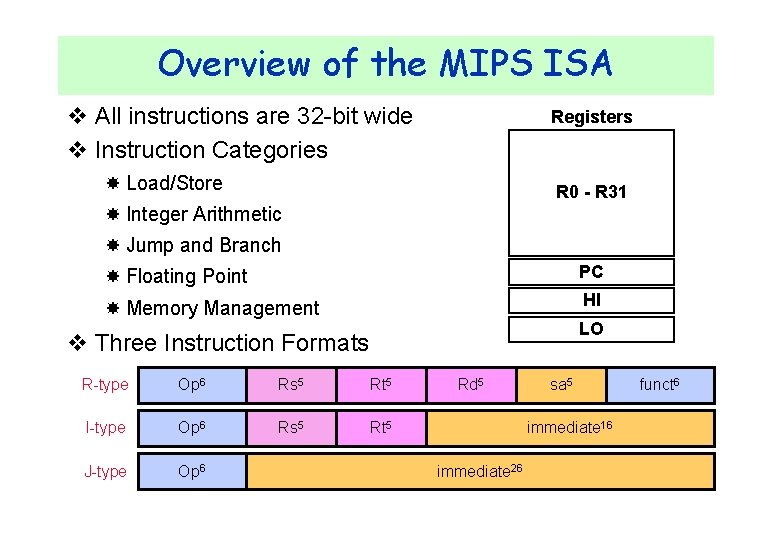

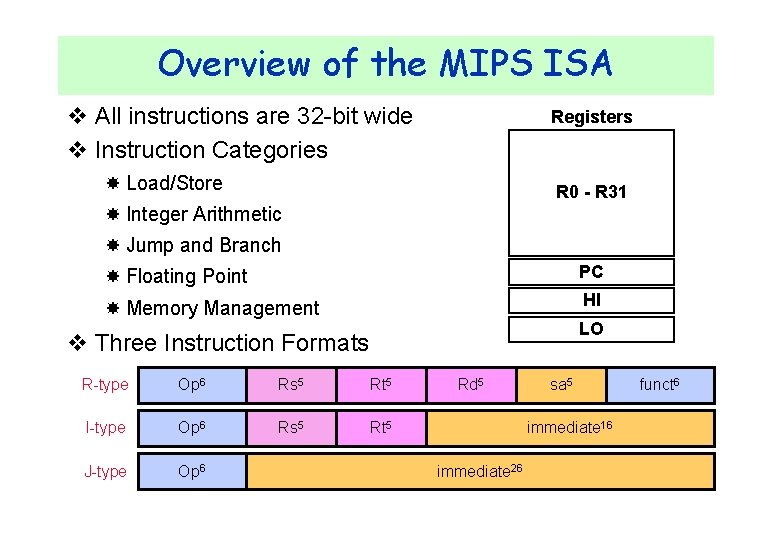

Overview of the MIPS ISA v All instructions are 32 -bit wide v Instruction Categories Registers Load/Store R 0 - R 31 Integer Arithmetic Jump and Branch Floating Point PC Memory Management HI LO v Three Instruction Formats R-type Op 6 Rs 5 Rt 5 I-type Op 6 Rs 5 Rt 5 J-type Op 6 Rd 5 sa 5 immediate 16 immediate 26 funct 6

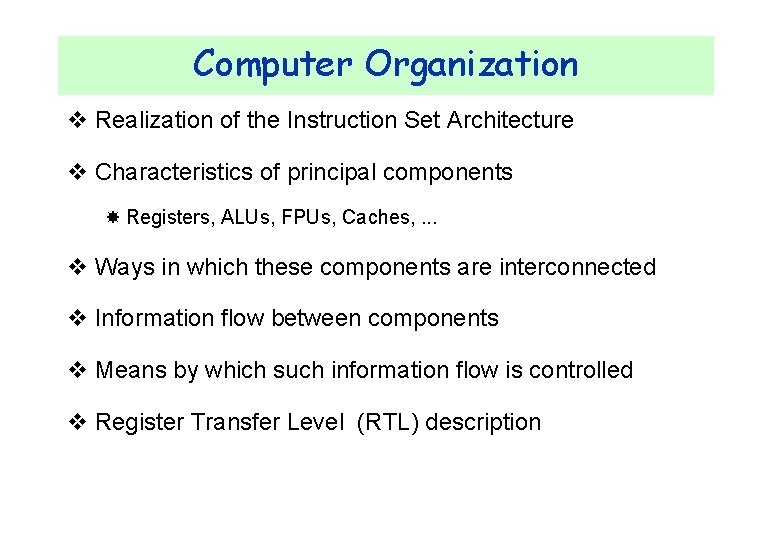

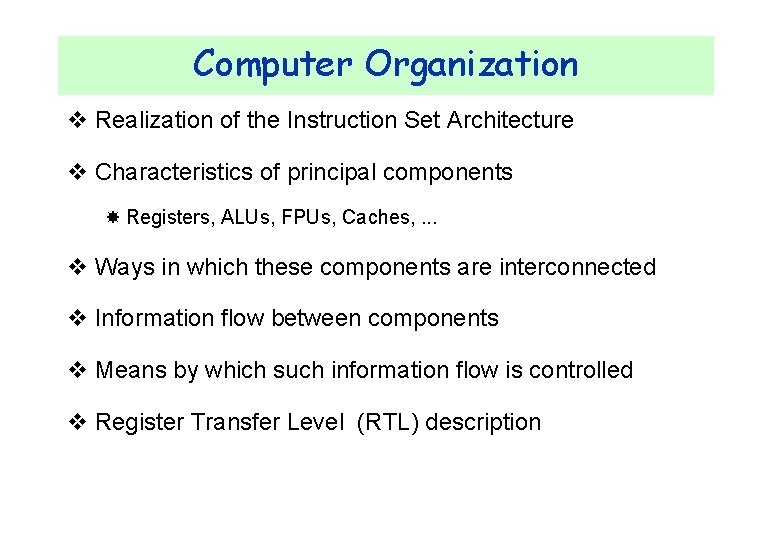

Computer Organization v Realization of the Instruction Set Architecture v Characteristics of principal components Registers, ALUs, FPUs, Caches, . . . v Ways in which these components are interconnected v Information flow between components v Means by which such information flow is controlled v Register Transfer Level (RTL) description

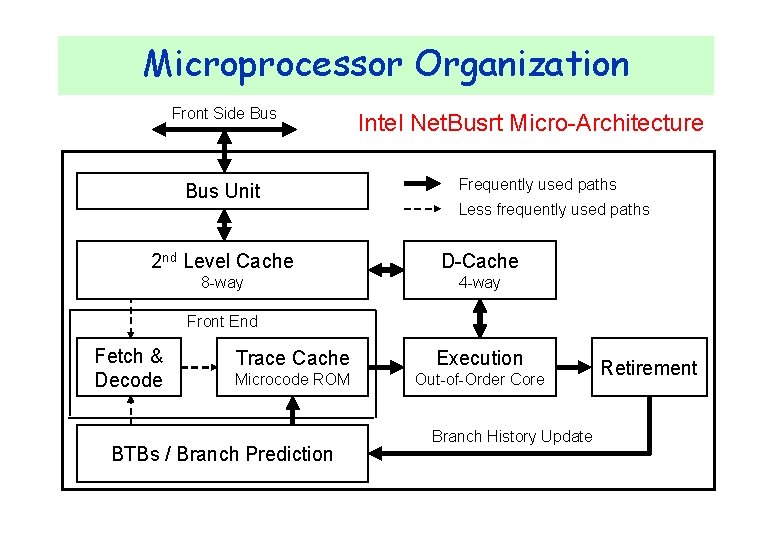

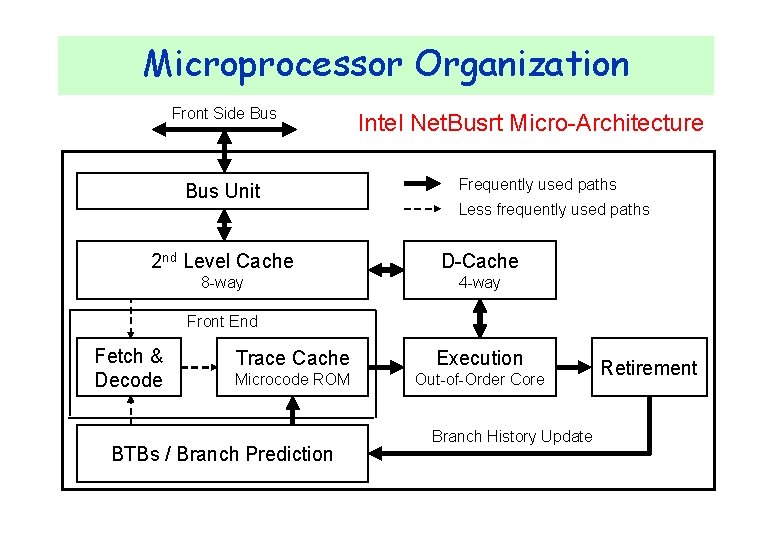

Microprocessor Organization Front Side Bus Unit Intel Net. Busrt Micro-Architecture Frequently used paths Less frequently used paths 2 nd Level Cache D-Cache 8 -way 4 -way Front End Fetch & Decode Trace Cache Execution Microcode ROM Out-of-Order Core BTBs / Branch Prediction Branch History Update Retirement

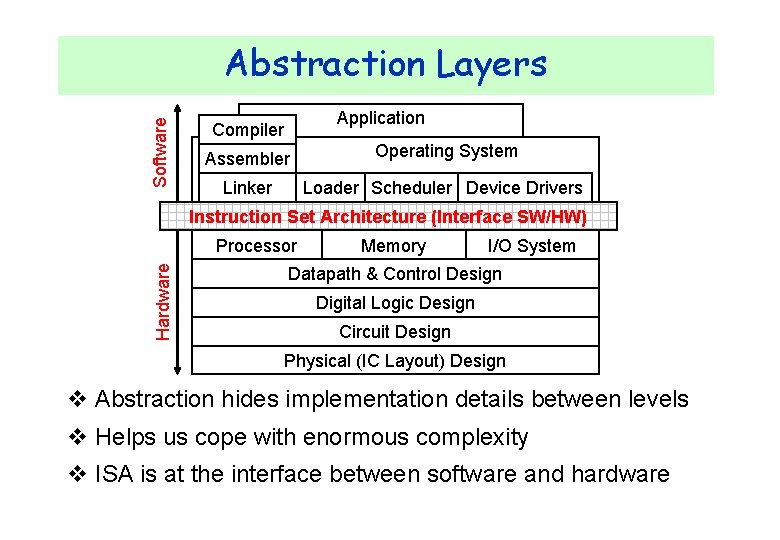

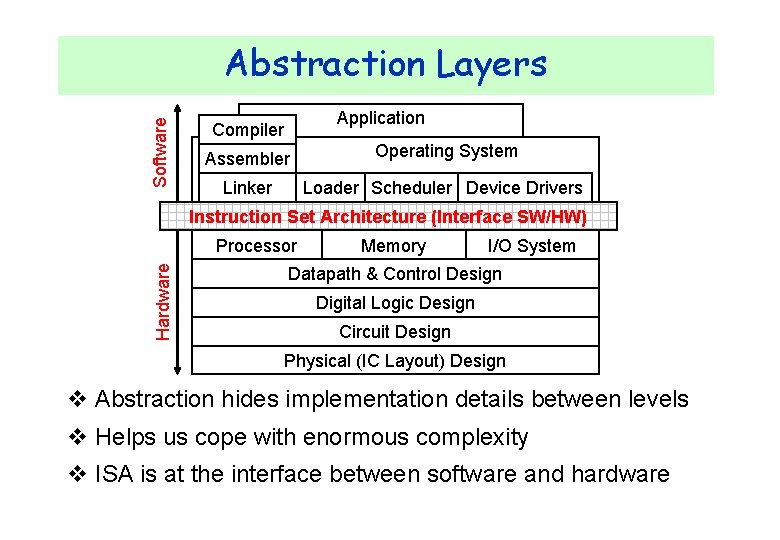

Software Abstraction Layers Application Compiler Assembler Operating System Linker Loader Scheduler Device Drivers Instruction Set Architecture (Interface SW/HW) Hardware Processor Memory I/O System Datapath & Control Design Digital Logic Design Circuit Design Physical (IC Layout) Design v Abstraction hides implementation details between levels v Helps us cope with enormous complexity v ISA is at the interface between software and hardware

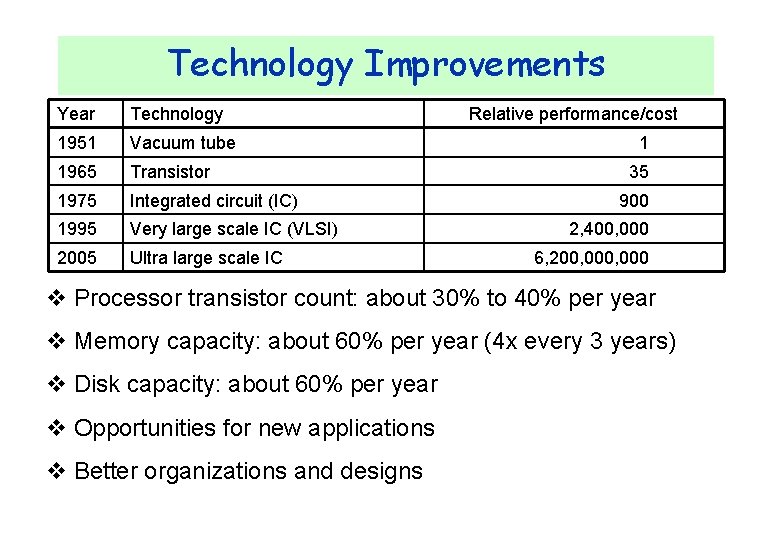

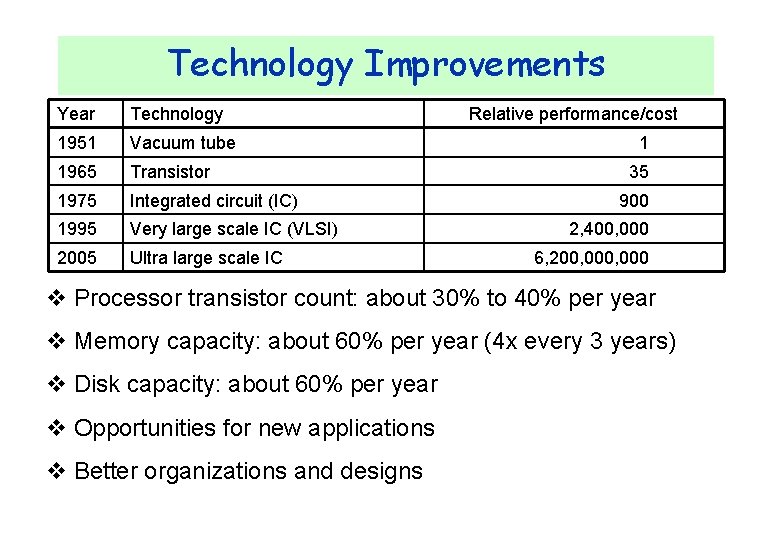

Technology Improvements Year Technology 1951 Vacuum tube 1965 Transistor 1975 Integrated circuit (IC) 1995 Very large scale IC (VLSI) 2005 Ultra large scale IC Relative performance/cost 1 35 900 2, 400, 000 6, 200, 000 v Processor transistor count: about 30% to 40% per year v Memory capacity: about 60% per year (4 x every 3 years) v Disk capacity: about 60% per year v Opportunities for new applications v Better organizations and designs

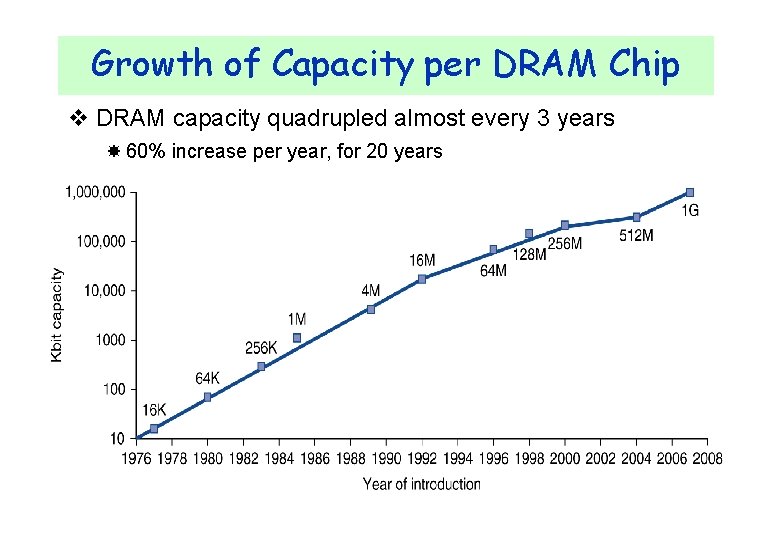

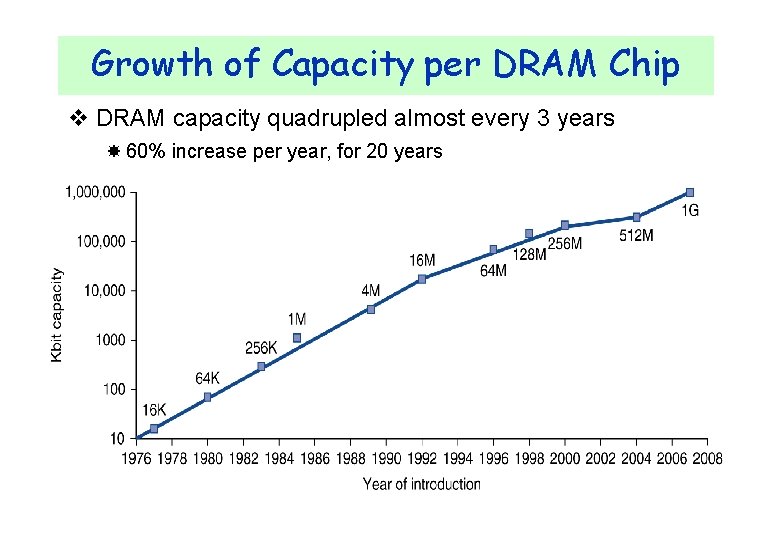

Growth of Capacity per DRAM Chip v DRAM capacity quadrupled almost every 3 years 60% increase per year, for 20 years

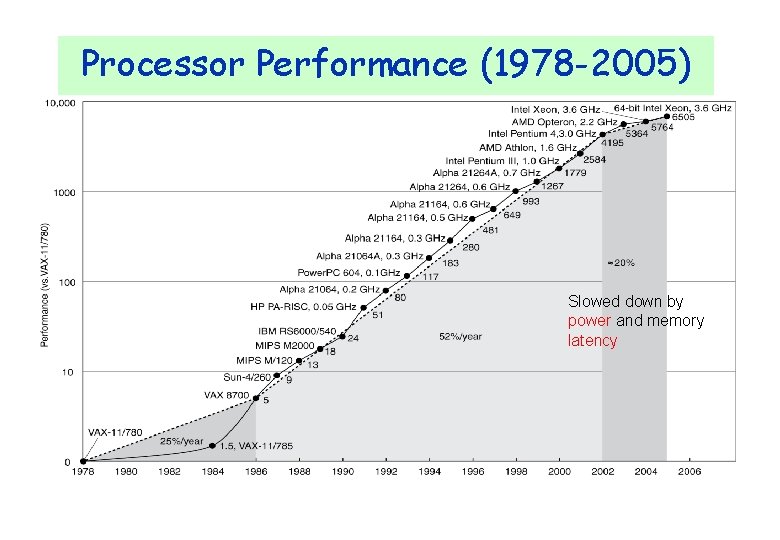

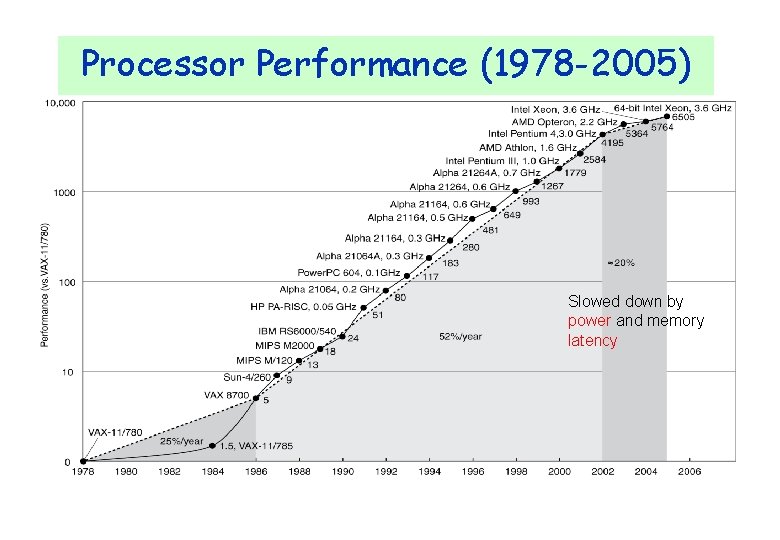

Processor Performance (1978 -2005) Slowed down by power and memory latency Almost 10000 x improvement between 1978 and 2005

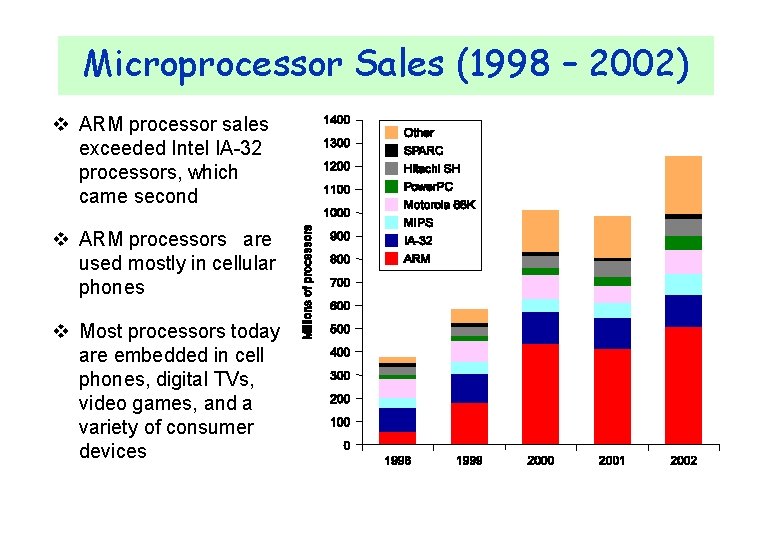

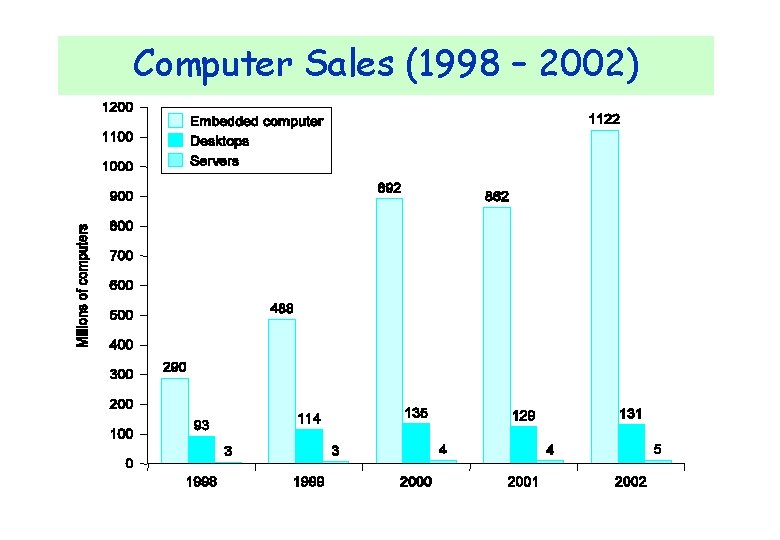

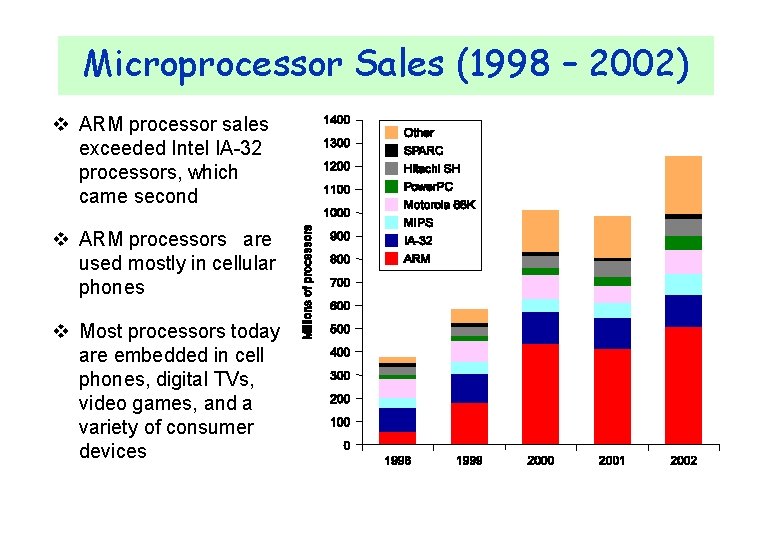

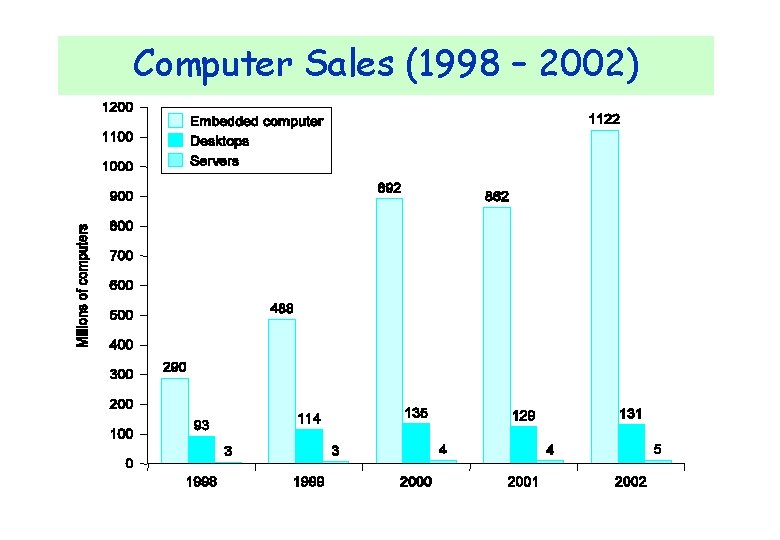

Microprocessor Sales (1998 – 2002) v ARM processor sales exceeded Intel IA-32 processors, which came second v ARM processors are used mostly in cellular phones v Most processors today are embedded in cell phones, digital TVs, video games, and a variety of consumer devices

Classes of Computers v Desktop / Notebook Computers General purpose, variety of software Subject to cost/performance tradeoff v Server Computers Network based High capacity, performance, reliability Range from small servers to building sized v Embedded Computers Hidden as components of systems Stringent power/performance/cost constraints

Computer Sales (1998 – 2002)

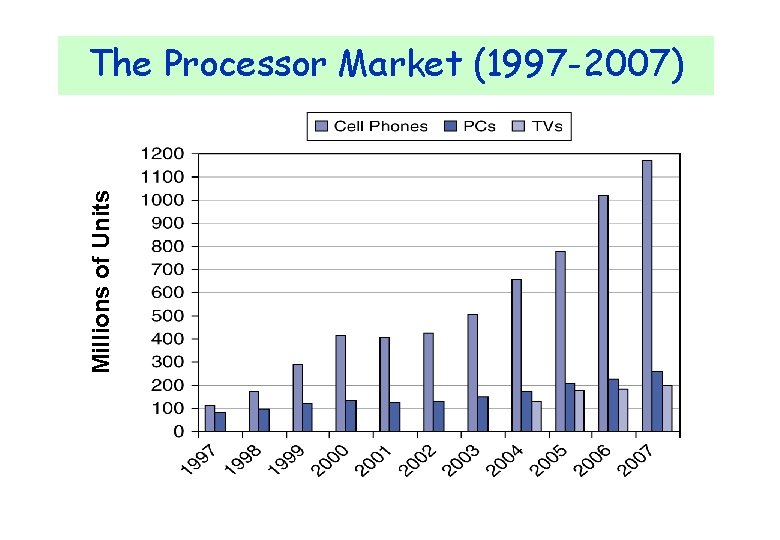

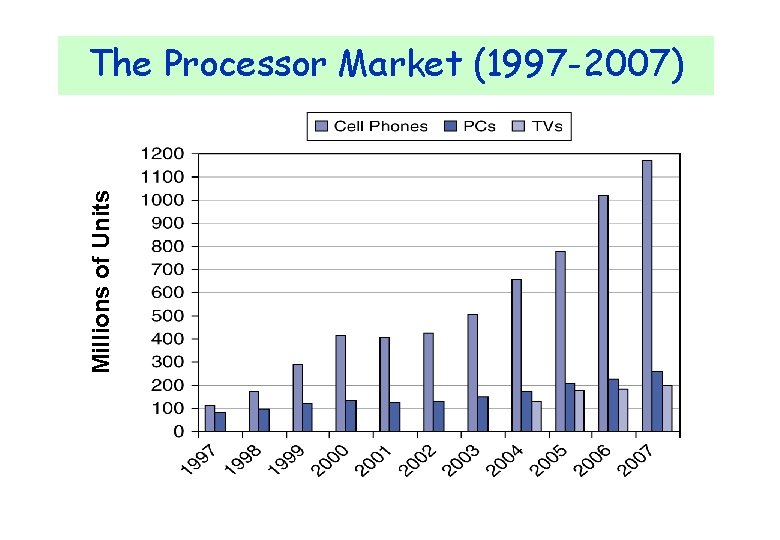

Millions of Units The Processor Market (1997 -2007)

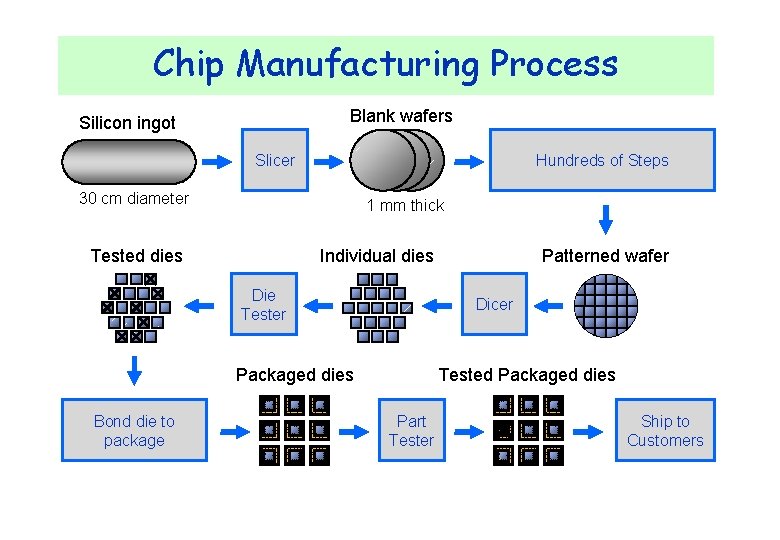

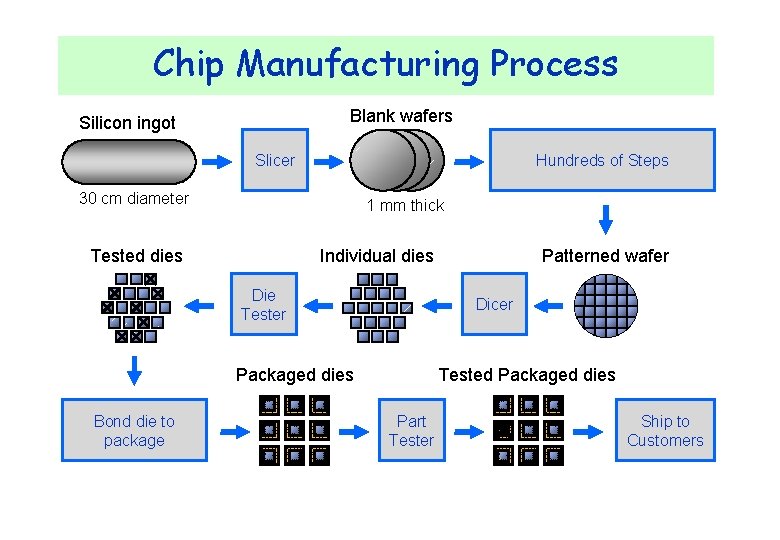

Chip Manufacturing Process Blank wafers Silicon ingot Slicer Hundreds of Steps 30 cm diameter 1 mm thick Tested dies Die Tester Dicer Packaged dies Bond die to package Patterned wafer Individual dies Tested Packaged dies Part Tester Ship to Customers

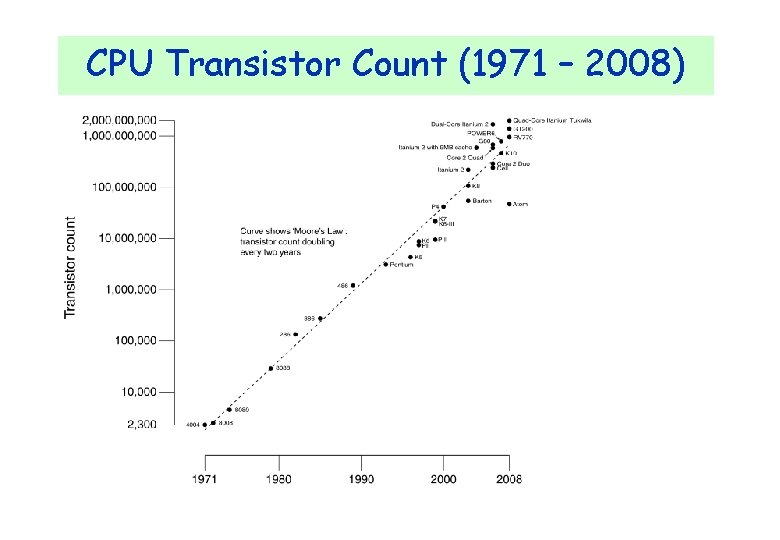

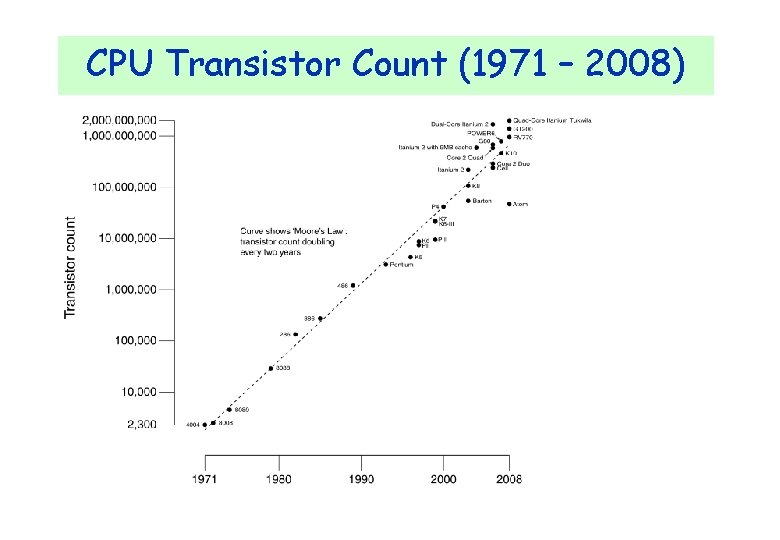

CPU Transistor Count (1971 – 2008)

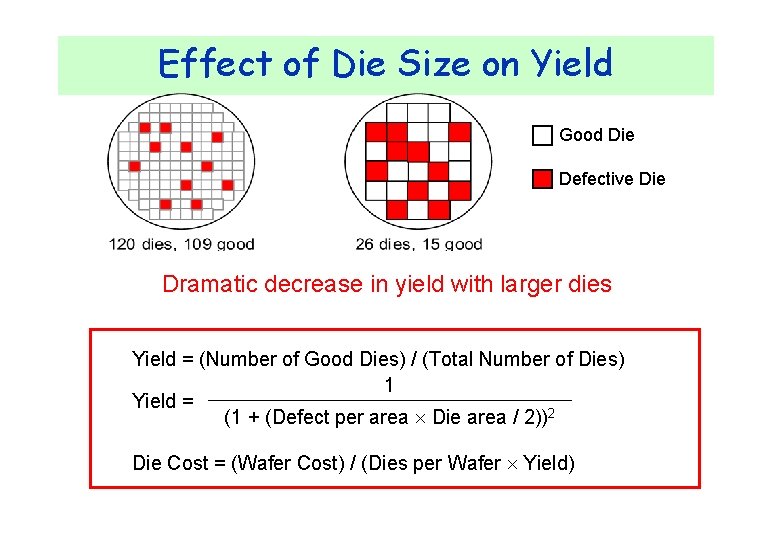

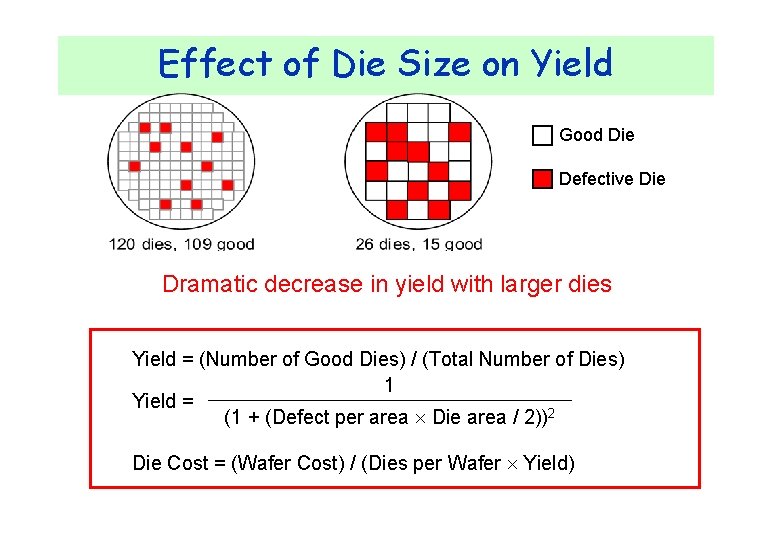

Effect of Die Size on Yield Good Die Defective Die Dramatic decrease in yield with larger dies Yield = (Number of Good Dies) / (Total Number of Dies) 1 Yield = (1 + (Defect per area Die area / 2))2 Die Cost = (Wafer Cost) / (Dies per Wafer Yield)

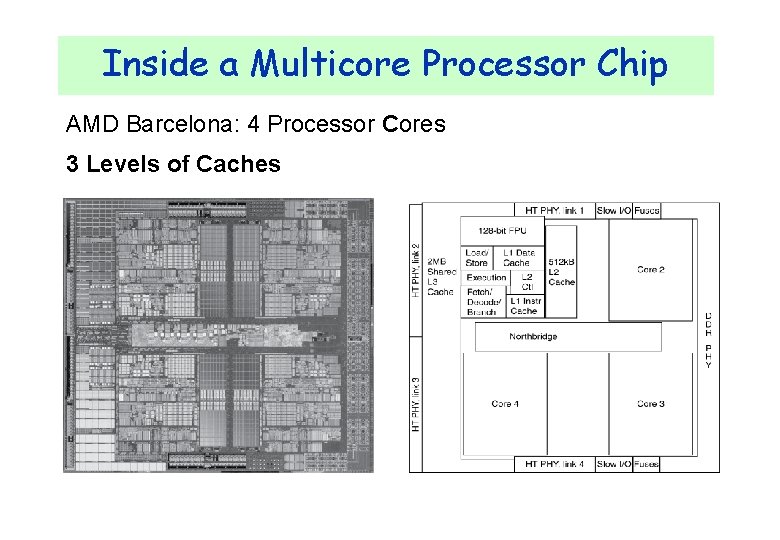

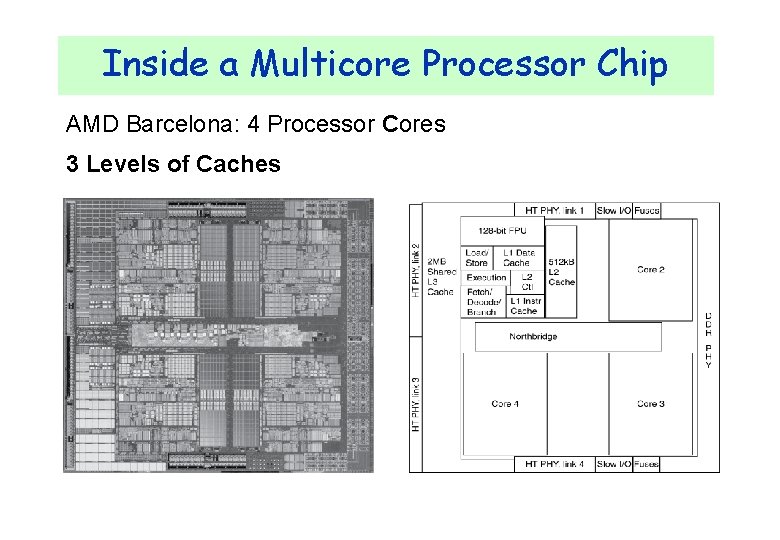

Inside a Multicore Processor Chip AMD Barcelona: 4 Processor Cores 3 Levels of Caches

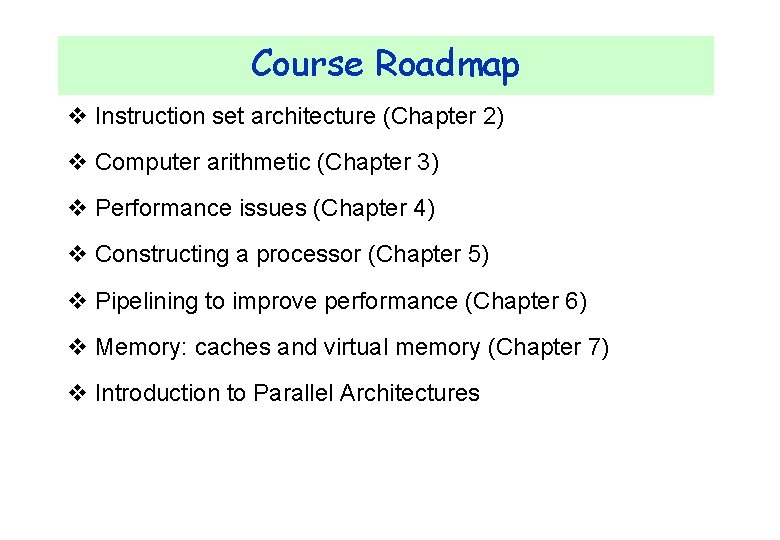

Course Roadmap v Instruction set architecture (Chapter 2) v Computer arithmetic (Chapter 3) v Performance issues (Chapter 4) v Constructing a processor (Chapter 5) v Pipelining to improve performance (Chapter 6) v Memory: caches and virtual memory (Chapter 7) v Introduction to Parallel Architectures