GHz Differential Signaling High Speed Design 1242002 2

- Slides: 41

GHz Differential Signaling High Speed Design 12/4/2002

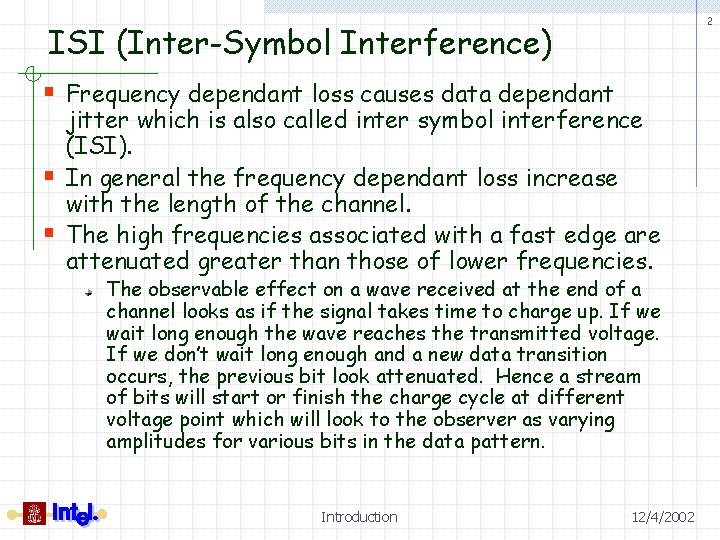

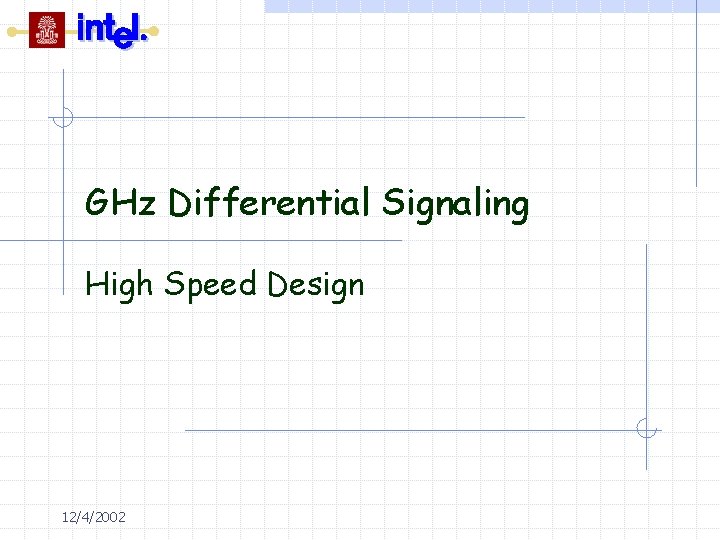

2 ISI (Inter-Symbol Interference) § Frequency dependant loss causes data dependant § § jitter which is also called inter symbol interference (ISI). In general the frequency dependant loss increase with the length of the channel. The high frequencies associated with a fast edge are attenuated greater than those of lower frequencies. The observable effect on a wave received at the end of a channel looks as if the signal takes time to charge up. If we wait long enough the wave reaches the transmitted voltage. If we don’t wait long enough and a new data transition occurs, the previous bit look attenuated. Hence a stream of bits will start or finish the charge cycle at different voltage point which will look to the observer as varying amplitudes for various bits in the data pattern. Introduction 12/4/2002

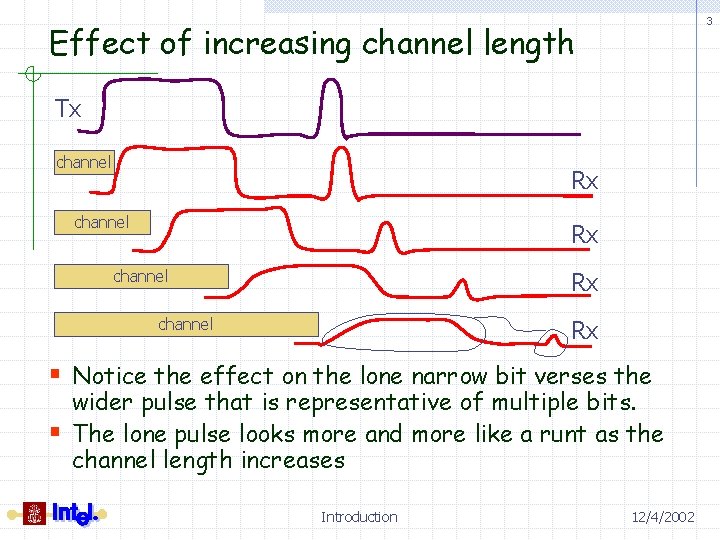

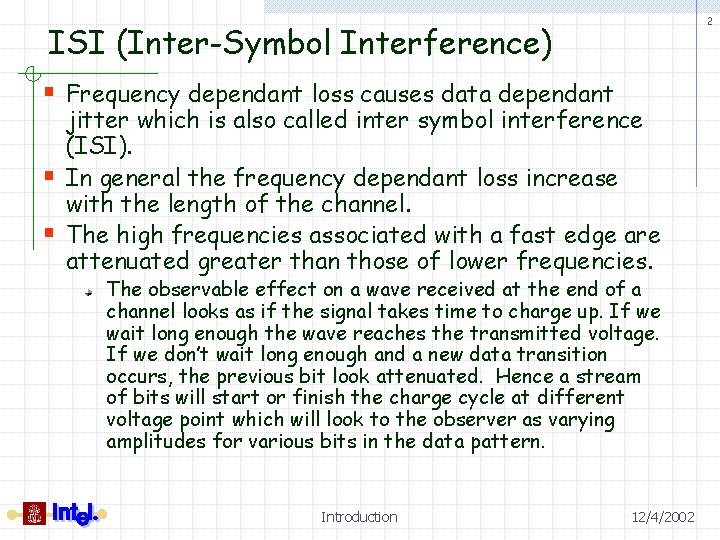

3 Effect of increasing channel length Tx channel Rx § Notice the effect on the lone narrow bit verses the § wider pulse that is representative of multiple bits. The lone pulse looks more and more like a runt as the channel length increases Introduction 12/4/2002

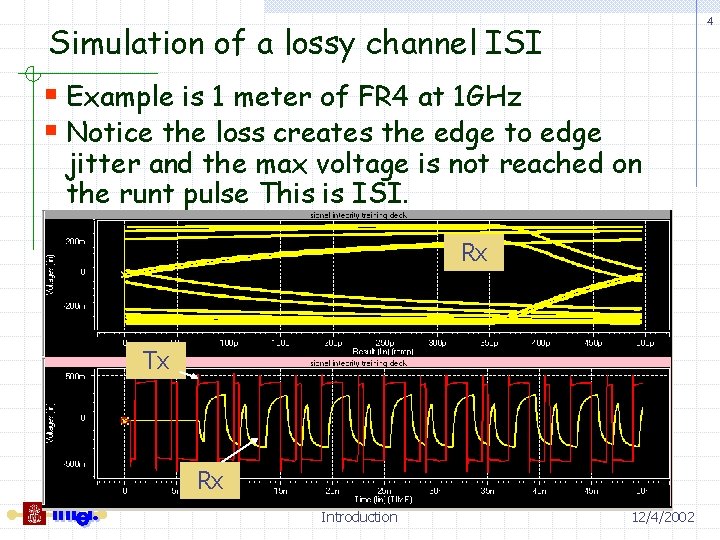

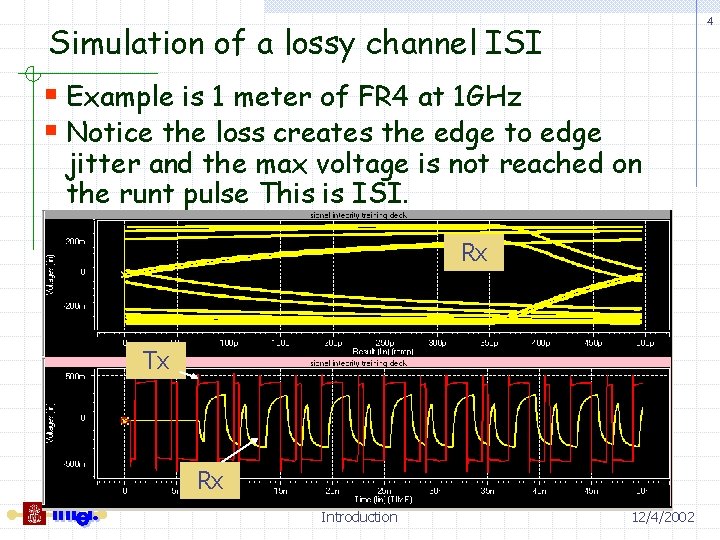

4 Simulation of a lossy channel ISI § Example is 1 meter of FR 4 at 1 GHz § Notice the loss creates the edge to edge jitter and the max voltage is not reached on the runt pulse This is ISI. Rx Tx Rx Introduction 12/4/2002

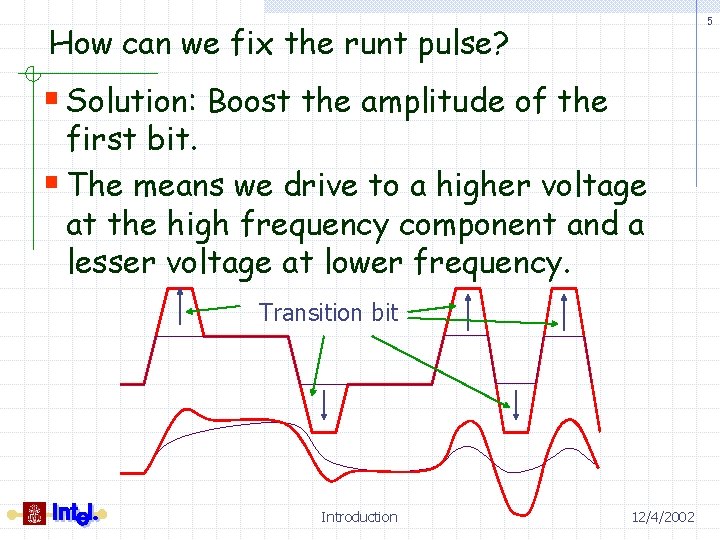

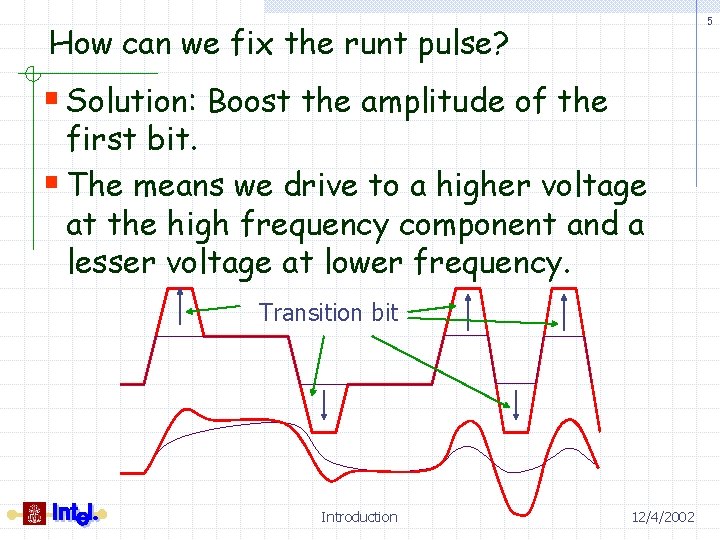

5 How can we fix the runt pulse? § Solution: Boost the amplitude of the first bit. § The means we drive to a higher voltage at the high frequency component and a lesser voltage at lower frequency. Transition bit Introduction 12/4/2002

6 Equalization § The previous slide illustrates the concept of equalization. § Normally the max current is supplied on the transition bit and reduces on subsequent bits. Thus if we reference to the transition bit to a transmitter this equalization is commonly called “de”-emphasis. If we talk about the a the non-transition bit in reference to a receiver or passive network we might call this “pre”-emphasis. Although the two may be considered the same, the former is used more commonly. Introduction 12/4/2002

7 Equalization Philosophy – First step § Given the channel has a complex loss verses frequency transfer function, Hch(w) § The FFT of an input signal multiplied by the transfer function in the frequency domain is the response of the channel to that input in the frequency domain. tx(t) Tx(w) § If we take the IFFT of the previous cascade response we get the time domain signal of the output of the channel. We talked about this last semester. rx(t)=IFFT(Tx(w)*Hch(w)) Introduction 12/4/2002

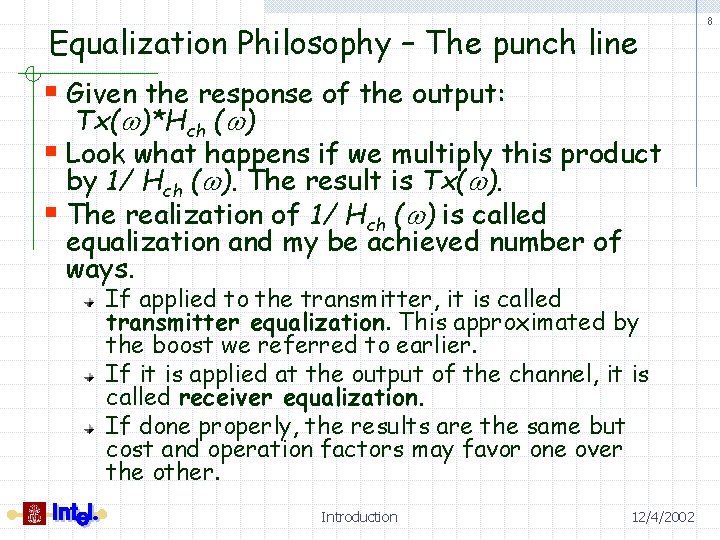

Equalization Philosophy – The punch line § Given the response of the output: Tx(w)*Hch (w) § Look what happens if we multiply this product by 1/ Hch (w). The result is Tx(w). § The realization of 1/ Hch (w) is called equalization and my be achieved number of ways. If applied to the transmitter, it is called transmitter equalization. This approximated by the boost we referred to earlier. If it is applied at the output of the channel, it is called receiver equalization. If done properly, the results are the same but cost and operation factors may favor one over the other. Introduction 12/4/2002 8

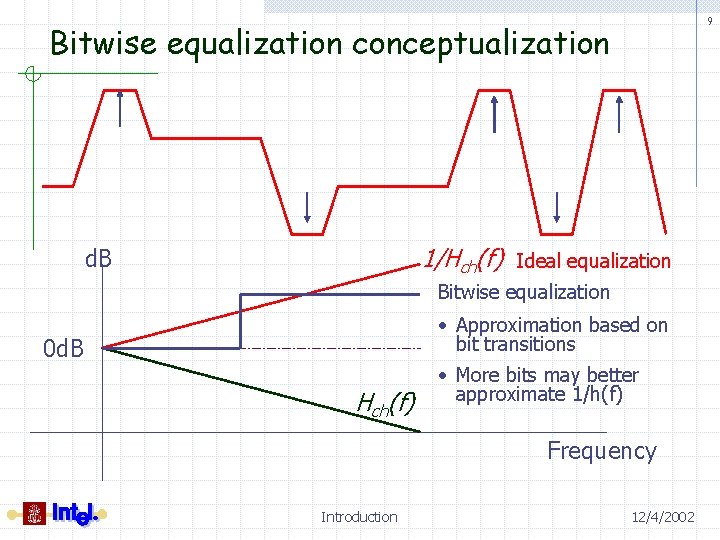

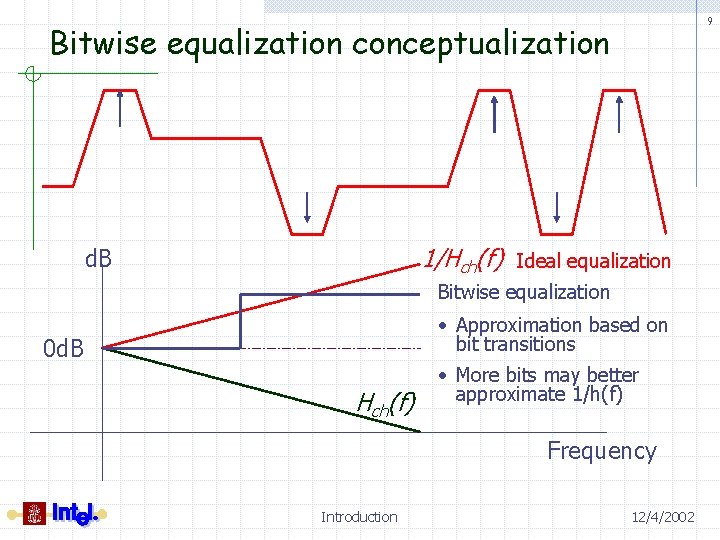

9 Bitwise equalization conceptualization 1/Hch(f) d. B Ideal equalization Bitwise equalization • Approximation based on bit transitions 0 d. B Hch(f) • More bits may better approximate 1/h(f) Frequency Introduction 12/4/2002

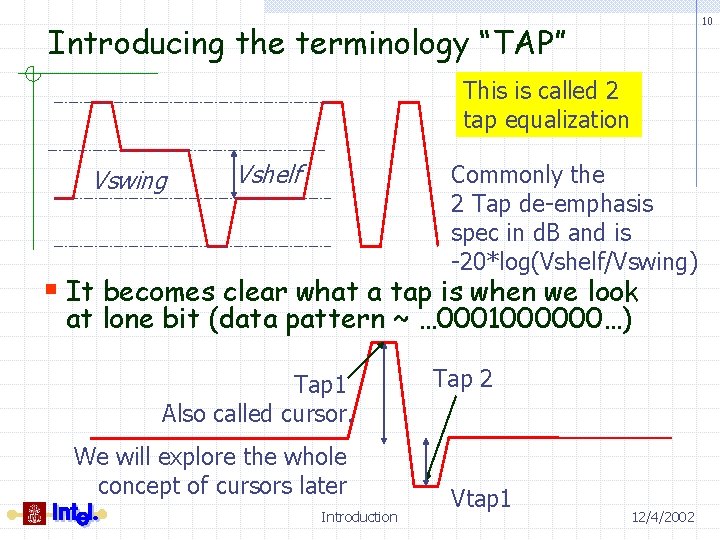

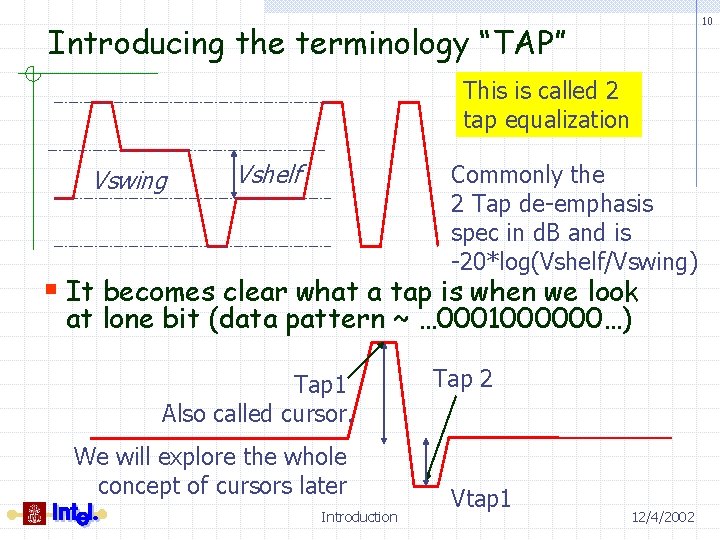

10 Introducing the terminology “TAP” This is called 2 tap equalization Vswing Vshelf Commonly the 2 Tap de-emphasis spec in d. B and is -20*log(Vshelf/Vswing) § It becomes clear what a tap is when we look at lone bit (data pattern ~ … 0001000000…) Tap 1 Also called cursor. We will explore the whole concept of cursors later Introduction Tap 2 Vtap 1 12/4/2002

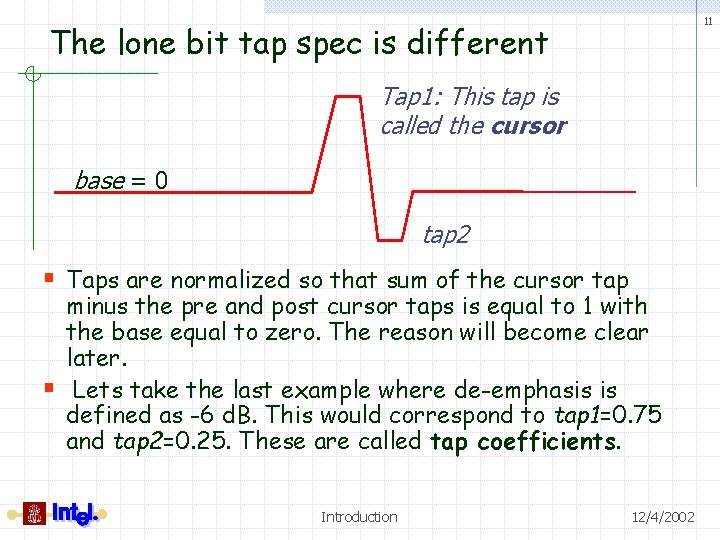

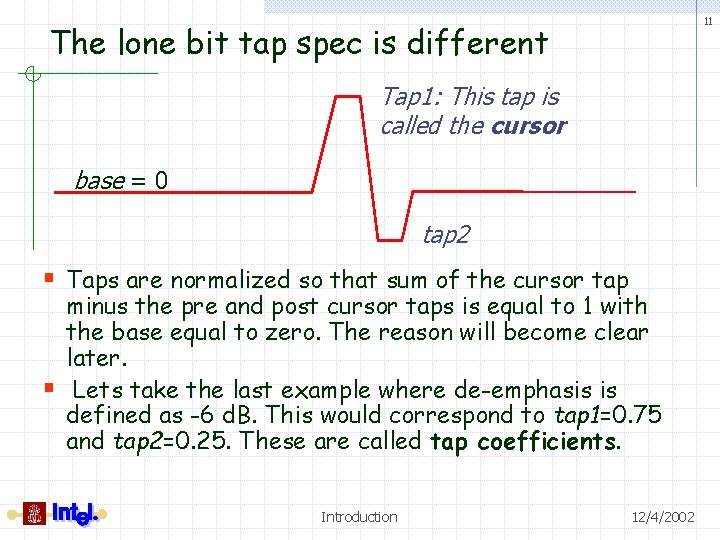

11 The lone bit tap spec is different Tap 1: This tap is called the cursor base = 0 tap 2 § Taps are normalized so that sum of the cursor tap § minus the pre and post cursor taps is equal to 1 with the base equal to zero. The reason will become clear later. Lets take the last example where de-emphasis is defined as -6 d. B. This would correspond to tap 1=0. 75 and tap 2=0. 25. These are called tap coefficients. Introduction 12/4/2002

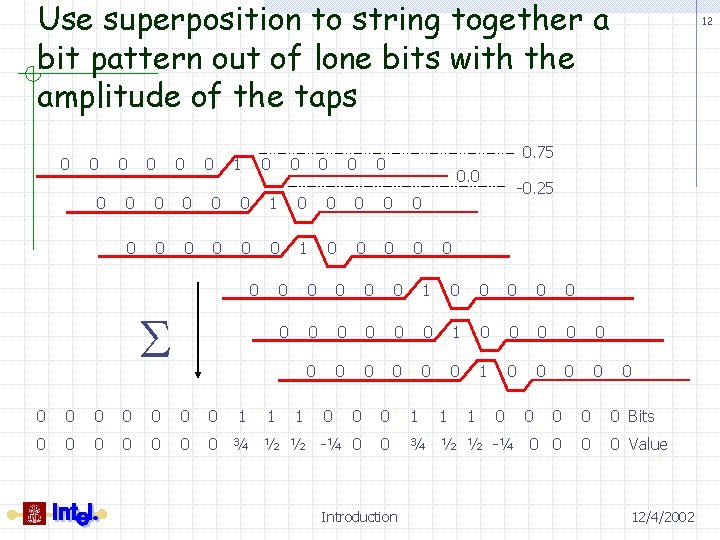

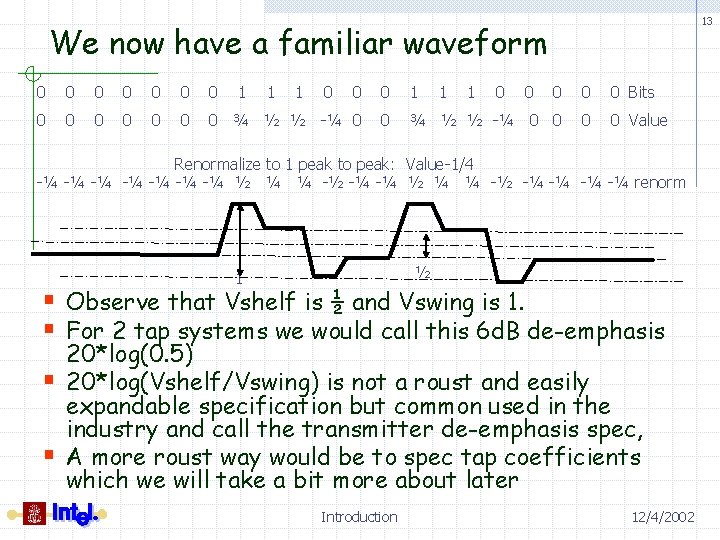

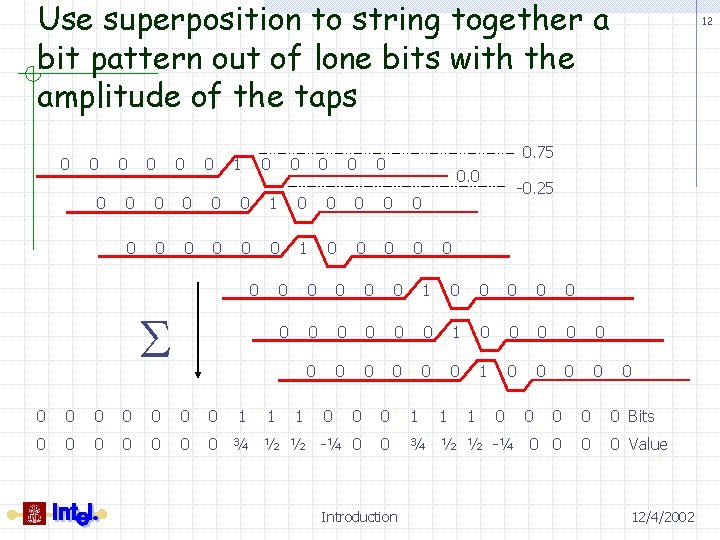

Use superposition to string together a bit pattern out of lone bits with the amplitude of the taps 0 0 0 0 1 0 0 0. 75 0 0 0 1 0 0 0 0 0 S 1 1 -0. 25 0 0 0 0 0 0 1 0 0 1 0 12 0 0 0 0 0 1 0 0 0 Bits 0 0 0 0 ¾ ½ ½ -¼ 0 0 0 0 Value Introduction 1 1 0 0 0 12/4/2002

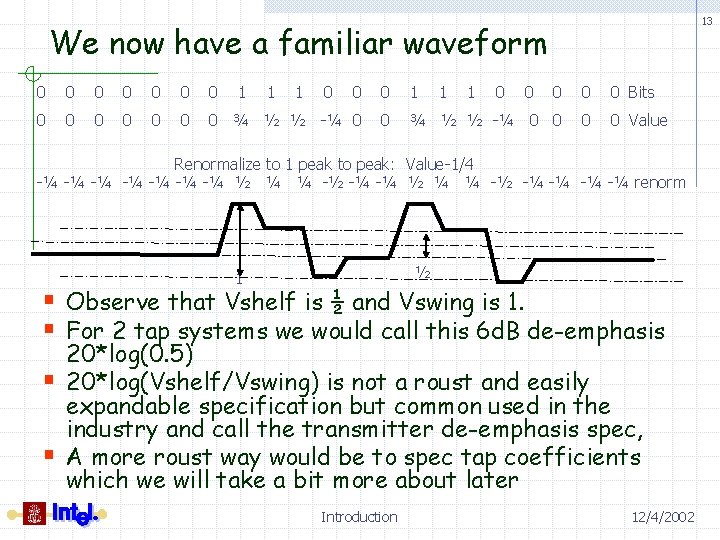

13 We now have a familiar waveform 0 0 0 0 1 1 1 0 0 0 0 0 Bits 0 0 0 0 ¾ ½ ½ -¼ 0 0 0 0 Value Renormalize to 1 peak to peak: Value-1/4 -¼ -¼ ½ ¼ ¼ -½ -¼ -¼ renorm ½ 1 § Observe that Vshelf is ½ and Vswing is 1. § For 2 tap systems we would call this 6 d. B de-emphasis § § 20*log(0. 5) 20*log(Vshelf/Vswing) is not a roust and easily expandable specification but common used in the industry and call the transmitter de-emphasis spec, A more roust way would be to spec tap coefficients which we will take a bit more about later Introduction 12/4/2002

14 Assignment 8: § What are the tap coefficients for 2 tap equalization with de-emphasis specified at 3. 5 d. B § Draw and label the lone pulse tap waveform. § If Vswing is 500 millivolts what is Vshelf Introduction 12/4/2002

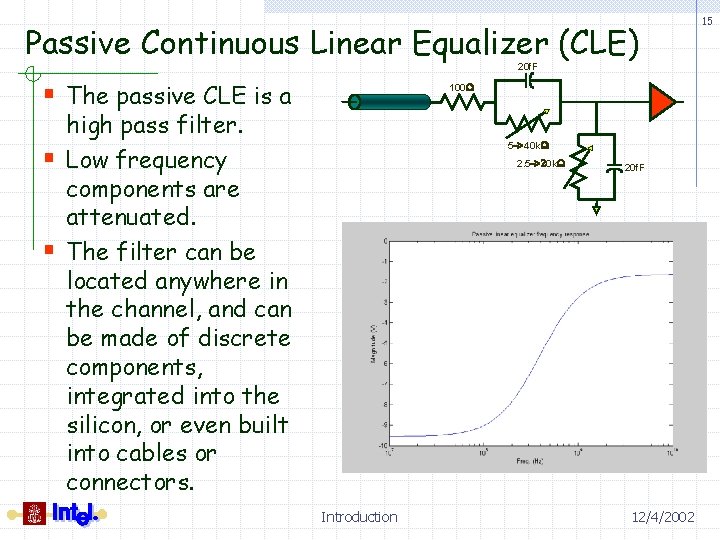

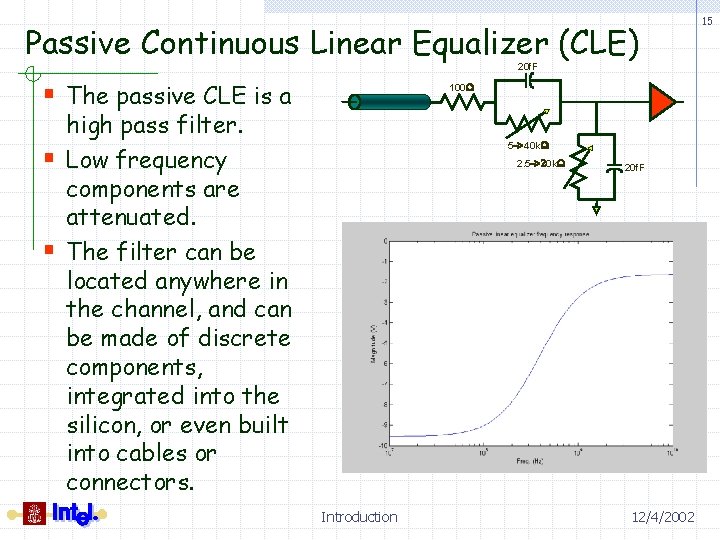

Passive Continuous Linear Equalizer (CLE) 20 f. F § The passive CLE is a § § 100 W high pass filter. Low frequency components are attenuated. The filter can be located anywhere in the channel, and can be made of discrete components, integrated into the silicon, or even built into cables or connectors. 5 ->40 k. W 2. 5 ->20 k. W Introduction 20 f. F 12/4/2002 15

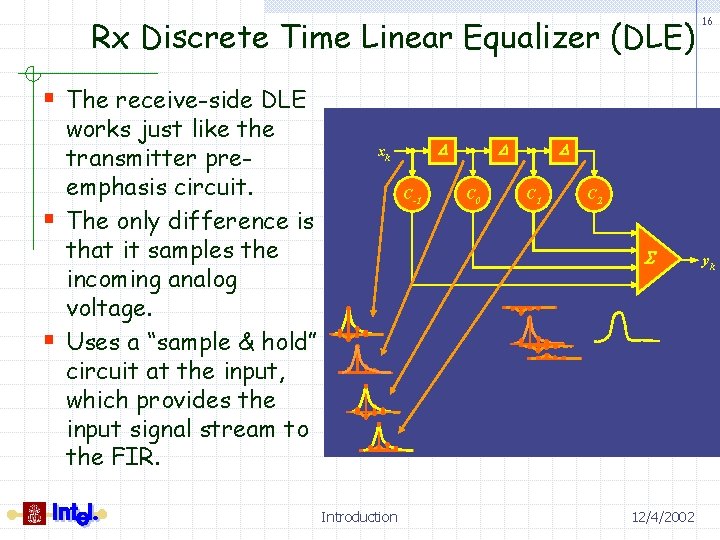

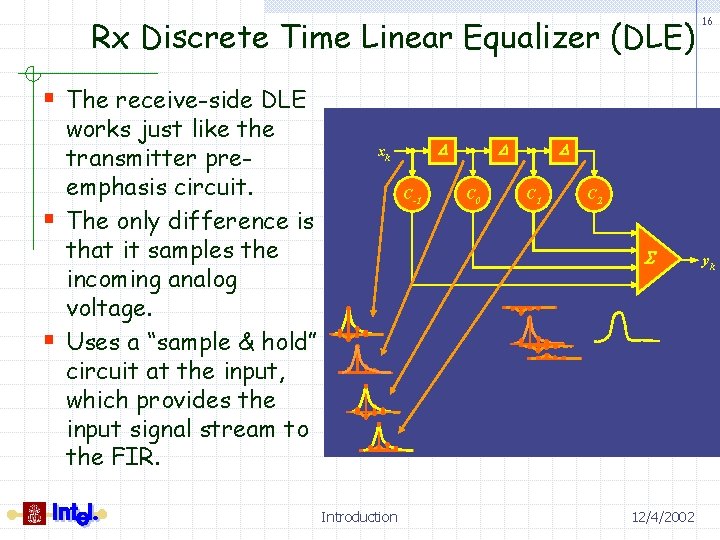

Rx Discrete Time Linear Equalizer (DLE) 16 § The receive-side DLE § § works just like the transmitter preemphasis circuit. The only difference is that it samples the incoming analog voltage. Uses a “sample & hold” circuit at the input, which provides the input signal stream to the FIR. D xk C -1 D C 0 D C 1 C 2 S Introduction 12/4/2002 yk

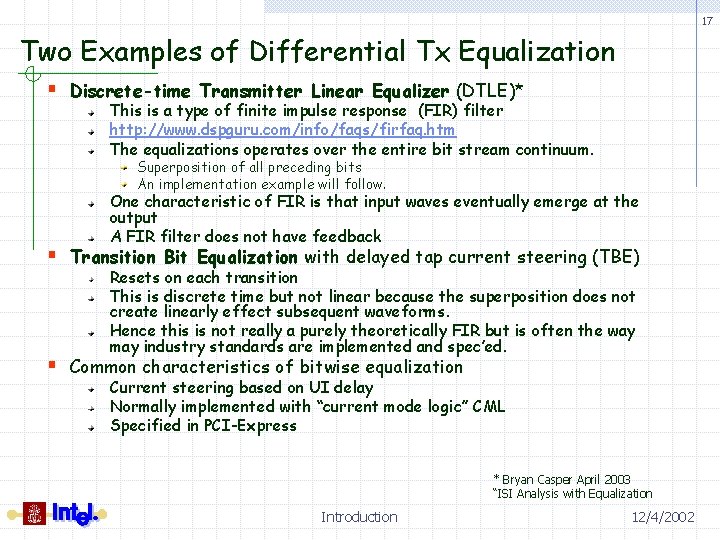

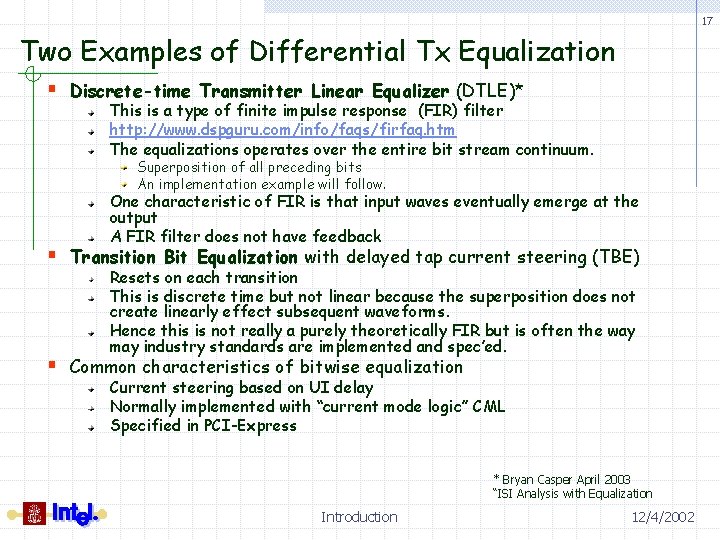

17 Two Examples of Differential Tx Equalization § Discrete-time Transmitter Linear Equalizer (DTLE)* This is a type of finite impulse response (FIR) filter http: //www. dspguru. com/info/faqs/firfaq. htm The equalizations operates over the entire bit stream continuum. Superposition of all preceding bits An implementation example will follow. One characteristic of FIR is that input waves eventually emerge at the output A FIR filter does not have feedback § Transition Bit Equalization with delayed tap current steering (TBE) Resets on each transition This is discrete time but not linear because the superposition does not create linearly effect subsequent waveforms. Hence this is not really a purely theoretically FIR but is often the way may industry standards are implemented and spec’ed. § Common characteristics of bitwise equalization Current steering based on UI delay Normally implemented with “current mode logic” CML Specified in PCI-Express * Bryan Casper April 2003 “ISI Analysis with Equalization Introduction 12/4/2002

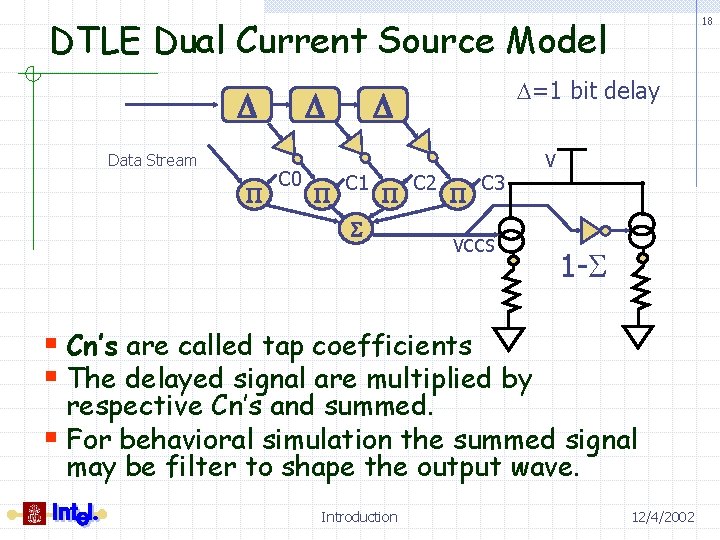

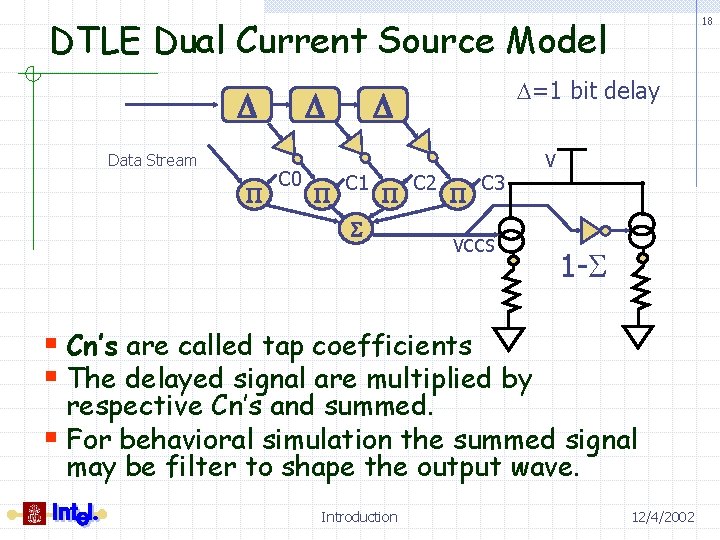

DTLE Dual Current Source Model D Data Stream P D C 0 P D=1 bit delay D C 1 P S 18 C 2 P C 3 VCCS V 1 -S § Cn’s are called tap coefficients § The delayed signal are multiplied by respective Cn’s and summed. § For behavioral simulation the summed signal may be filter to shape the output wave. Introduction 12/4/2002

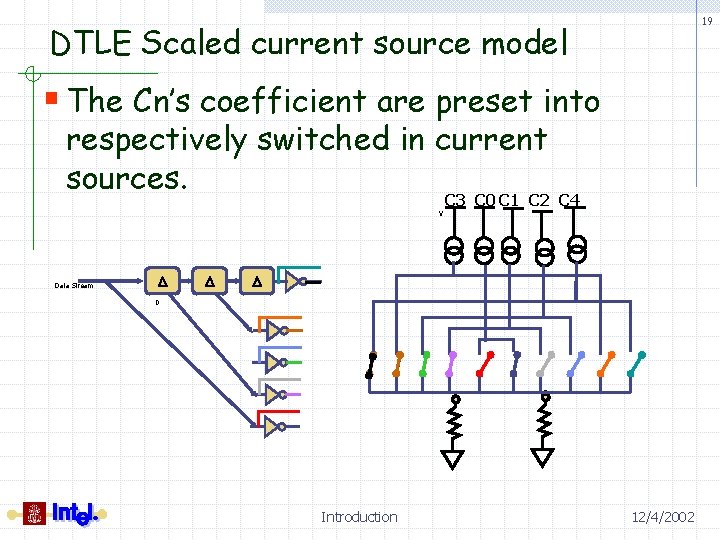

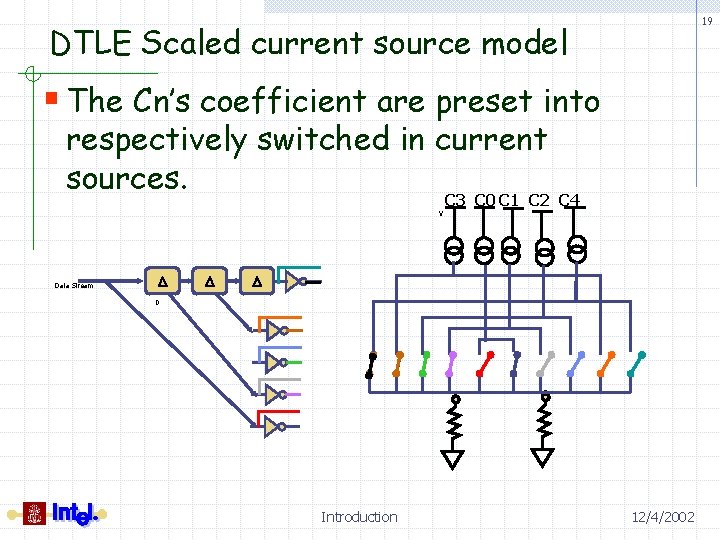

19 DTLE Scaled current source model § The Cn’s coefficient are preset into respectively switched in current sources. V Data Stream D D C 3 C 0 C 1 C 2 C 4 D 0 Introduction 12/4/2002

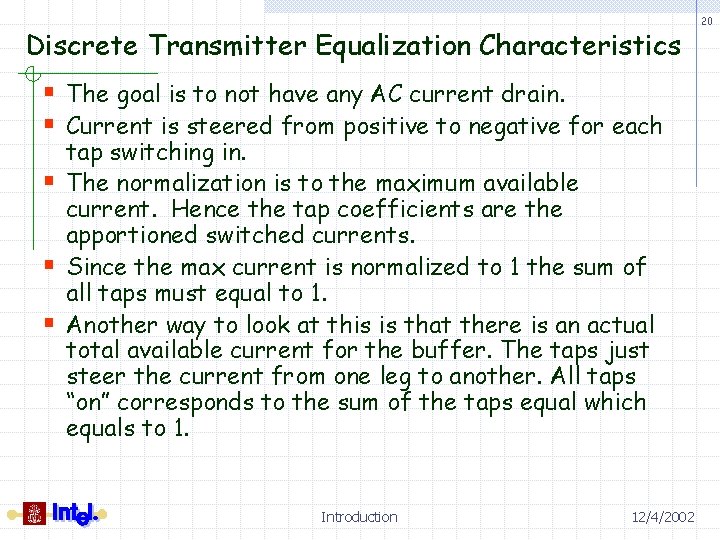

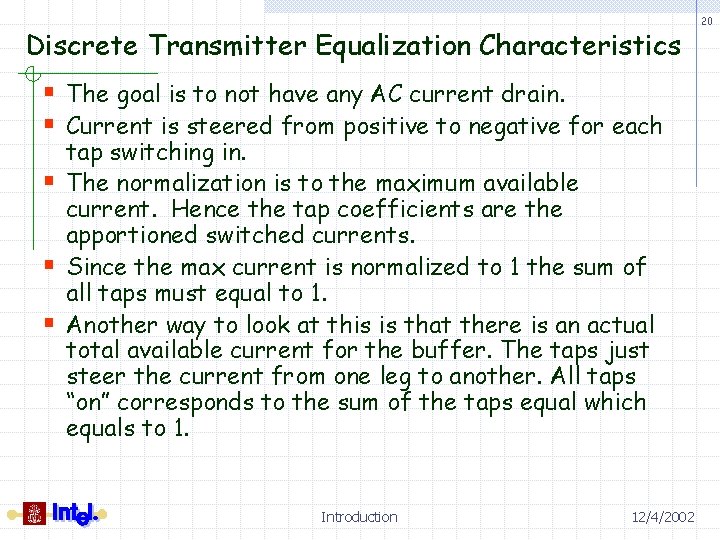

Discrete Transmitter Equalization Characteristics § The goal is to not have any AC current drain. § Current is steered from positive to negative for each § § § tap switching in. The normalization is to the maximum available current. Hence the tap coefficients are the apportioned switched currents. Since the max current is normalized to 1 the sum of all taps must equal to 1. Another way to look at this is that there is an actual total available current for the buffer. The taps just steer the current from one leg to another. All taps “on” corresponds to the sum of the taps equal which equals to 1. Introduction 12/4/2002 20

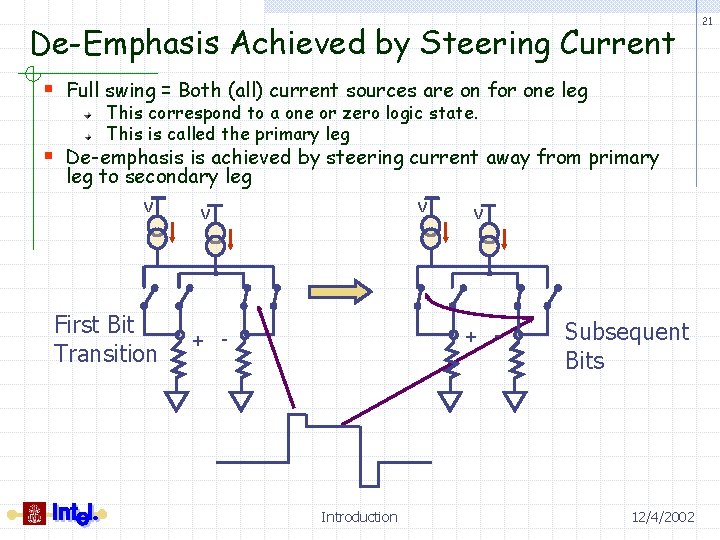

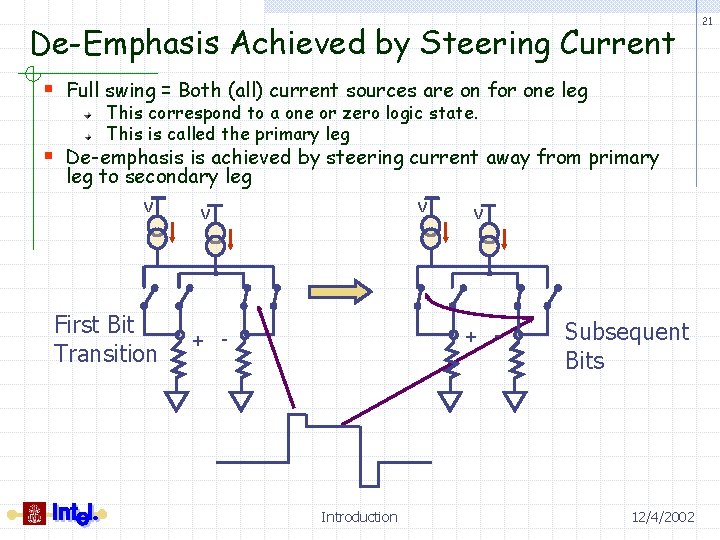

De-Emphasis Achieved by Steering Current § Full swing = Both (all) current sources are on for one leg This correspond to a one or zero logic state. This is called the primary leg § De-emphasis is achieved by steering current away from primary leg to secondary leg V First Bit Transition V V V + - Introduction Subsequent Bits 12/4/2002 21

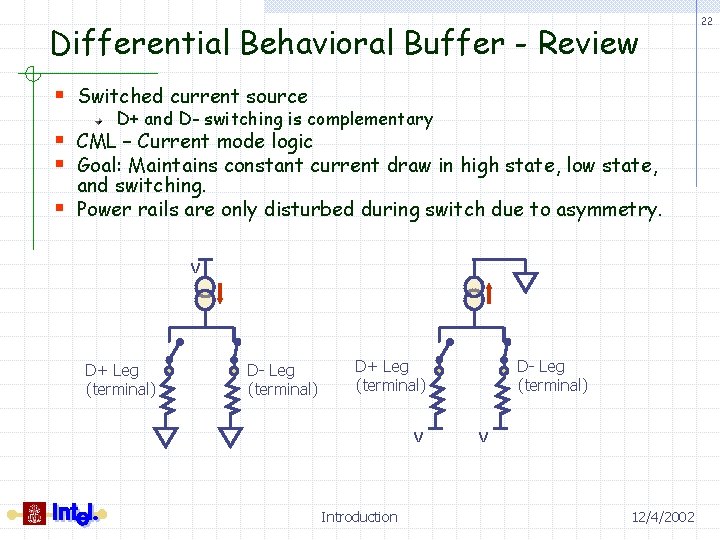

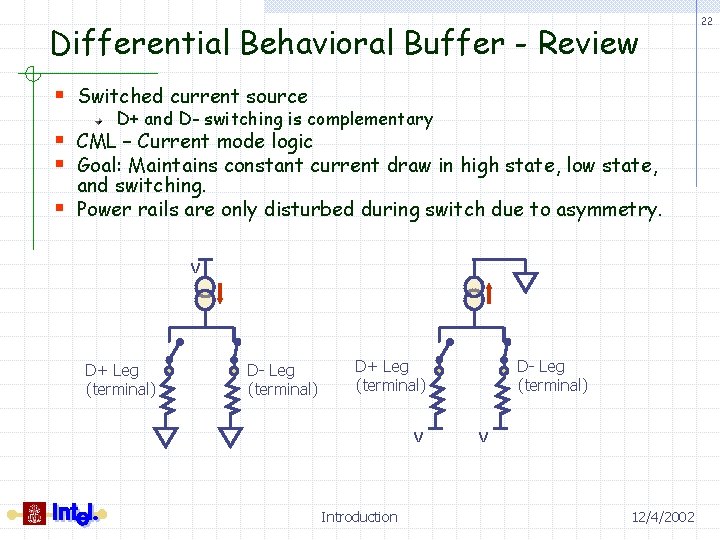

Differential Behavioral Buffer - Review § Switched current source D+ and D- switching is complementary § CML – Current mode logic § Goal: Maintains constant current draw in high state, low state, § and switching. Power rails are only disturbed during switch due to asymmetry. V D+ Leg (terminal) D- Leg (terminal) D+ Leg (terminal) V Introduction D- Leg (terminal) V 12/4/2002 22

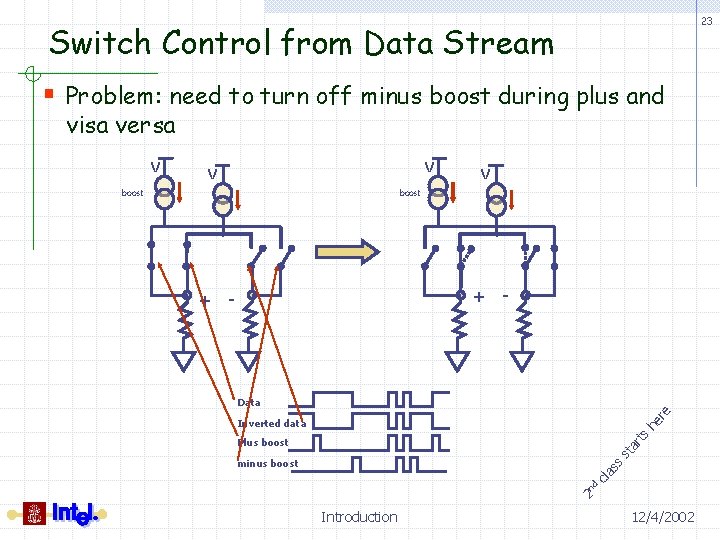

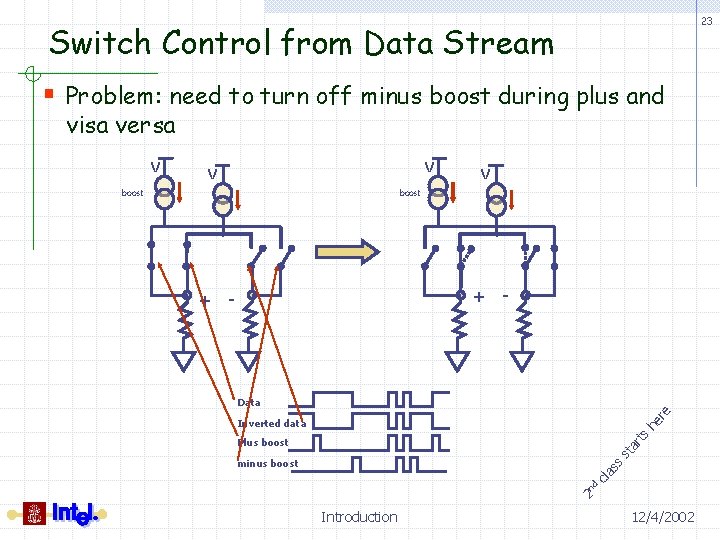

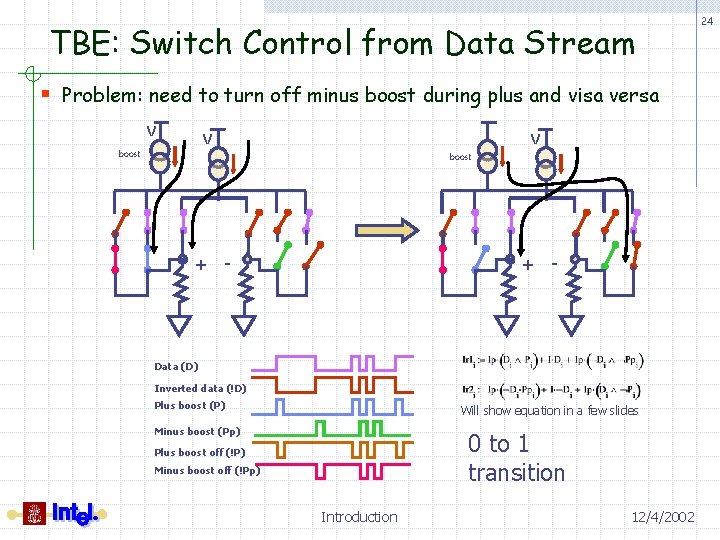

23 Switch Control from Data Stream § Problem: need to turn off minus boost during plus and visa versa V V V boost + - re Data ts he Inverted data st ar Plus boost 2 nd cla ss minus boost Introduction 12/4/2002

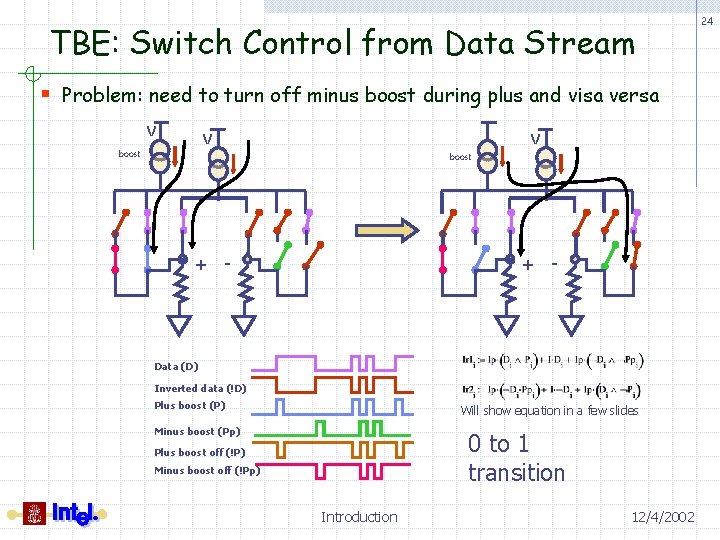

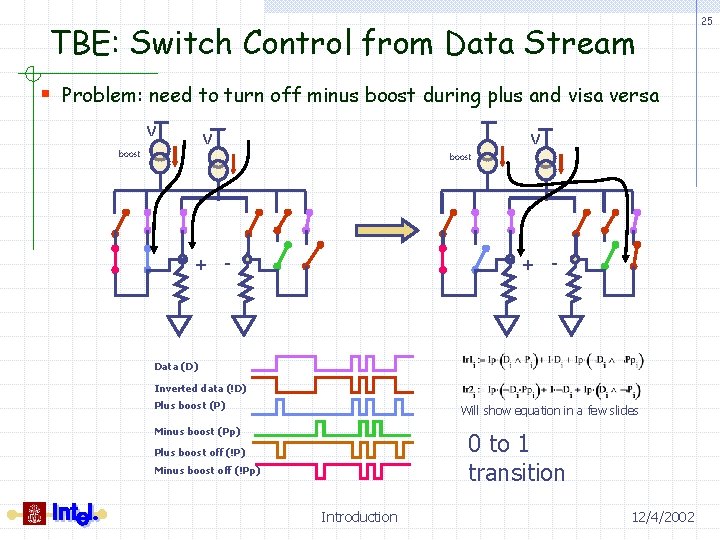

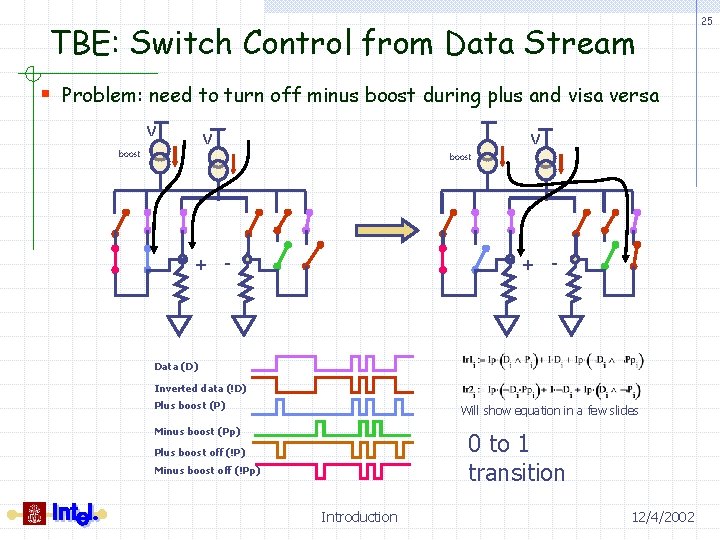

TBE: Switch Control from Data Stream § Problem: need to turn off minus boost during plus and visa versa V V V boost + - Data (D) Inverted data (!D) Plus boost (P) Will show equation in a few slides Minus boost (Pp) 0 to 1 transition Plus boost off (!P) Minus boost off (!Pp) Introduction 12/4/2002 24

TBE: Switch Control from Data Stream § Problem: need to turn off minus boost during plus and visa versa V V V boost + - Data (D) Inverted data (!D) Plus boost (P) Will show equation in a few slides Minus boost (Pp) 0 to 1 transition Plus boost off (!P) Minus boost off (!Pp) Introduction 12/4/2002 25

26 TBE currents § The previous slide illustrate the logic that controls the switches. § The remaining tasks is to determine is the two currents. Introduction 12/4/2002

Use Vmax and d. B shelf spec to define currents Introduction 12/4/2002 27

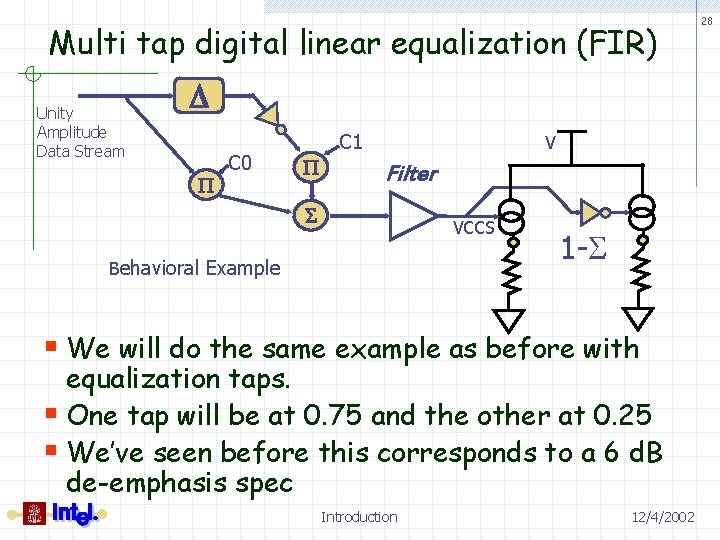

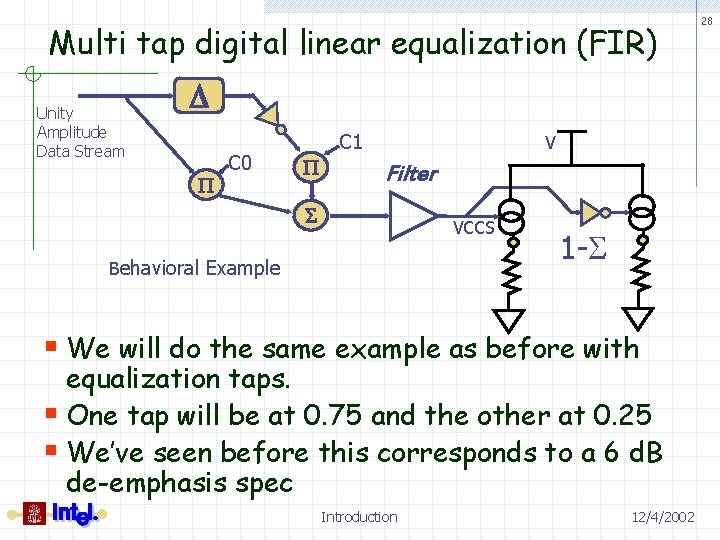

Multi tap digital linear equalization (FIR) Unity Amplitude Data Stream D P C 0 C 1 P V Filter S VCCS Behavioral Example 1 -S § We will do the same example as before with equalization taps. § One tap will be at 0. 75 and the other at 0. 25 § We’ve seen before this corresponds to a 6 d. B de-emphasis spec Introduction 12/4/2002 28

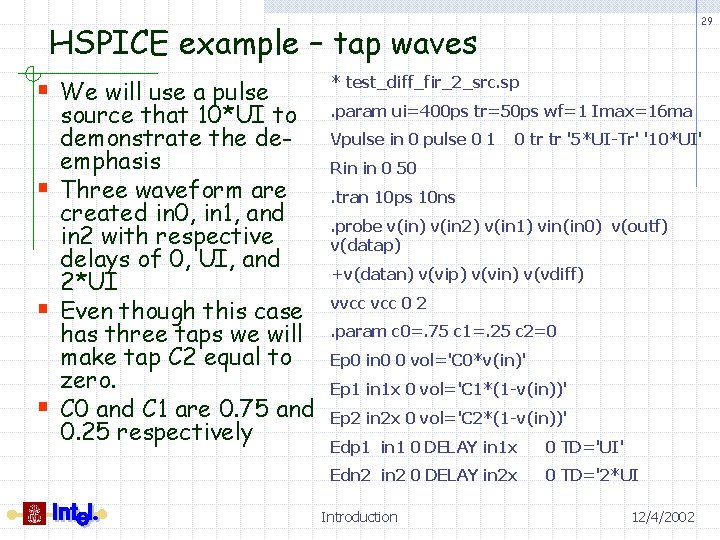

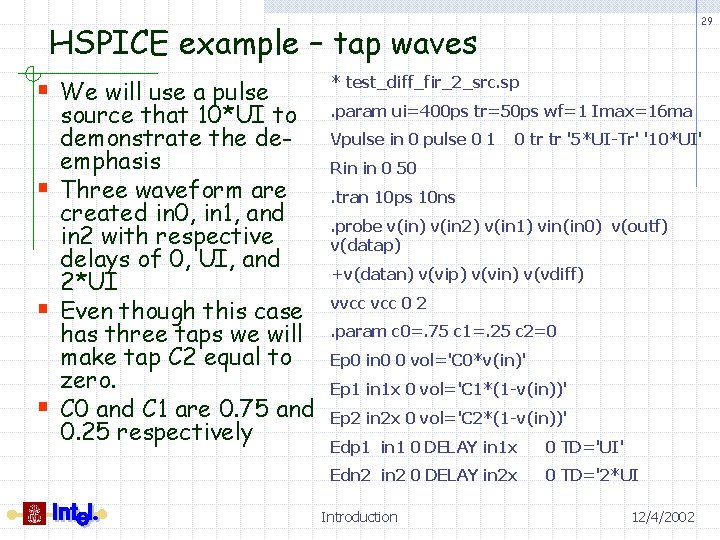

29 HSPICE example – tap waves § We will use a pulse § § § source that 10*UI to demonstrate the deemphasis Three waveform are created in 0, in 1, and in 2 with respective delays of 0, UI, and 2*UI Even though this case has three taps we will make tap C 2 equal to zero. C 0 and C 1 are 0. 75 and 0. 25 respectively * test_diff_fir_2_src. sp. param ui=400 ps tr=50 ps wf=1 Imax=16 ma Vpulse in 0 pulse 0 1 0 tr tr '5*UI-Tr' '10*UI' Rin in 0 50. tran 10 ps 10 ns. probe v(in) v(in 2) v(in 1) vin(in 0) v(outf) v(datap) +v(datan) v(vip) v(vin) v(vdiff) vvcc 0 2. param c 0=. 75 c 1=. 25 c 2=0 Ep 0 in 0 0 vol='C 0*v(in)' Ep 1 in 1 x 0 vol='C 1*(1 -v(in))' Ep 2 in 2 x 0 vol='C 2*(1 -v(in))' Edp 1 in 1 0 DELAY in 1 x 0 TD='UI' Edn 2 in 2 0 DELAY in 2 x 0 TD='2*UI Introduction 12/4/2002

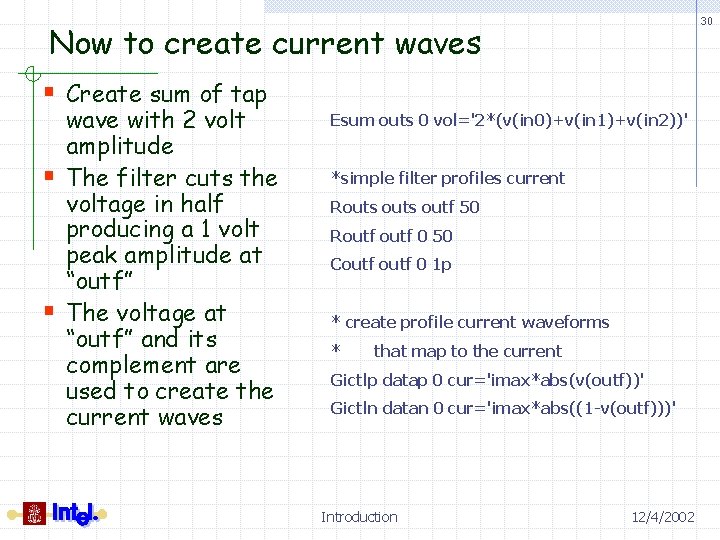

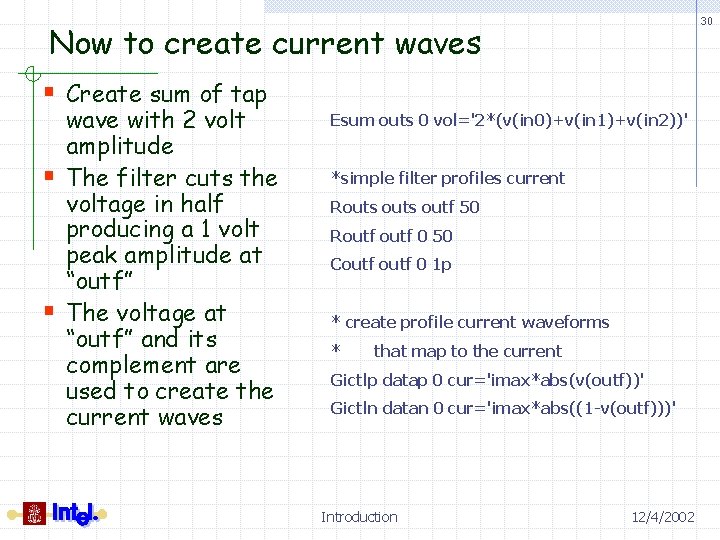

30 Now to create current waves § Create sum of tap § § wave with 2 volt amplitude The filter cuts the voltage in half producing a 1 volt peak amplitude at “outf” The voltage at “outf” and its complement are used to create the current waves Esum outs 0 vol='2*(v(in 0)+v(in 1)+v(in 2))' *simple filter profiles current Routs outf 50 Routf 0 50 Coutf 0 1 p * create profile current waveforms * that map to the current Gictlp datap 0 cur='imax*abs(v(outf))' Gictln datan 0 cur='imax*abs((1 -v(outf)))' Introduction 12/4/2002

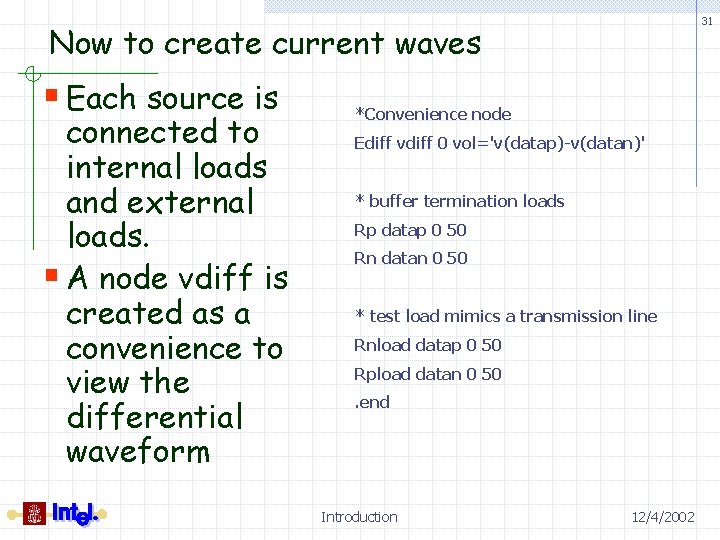

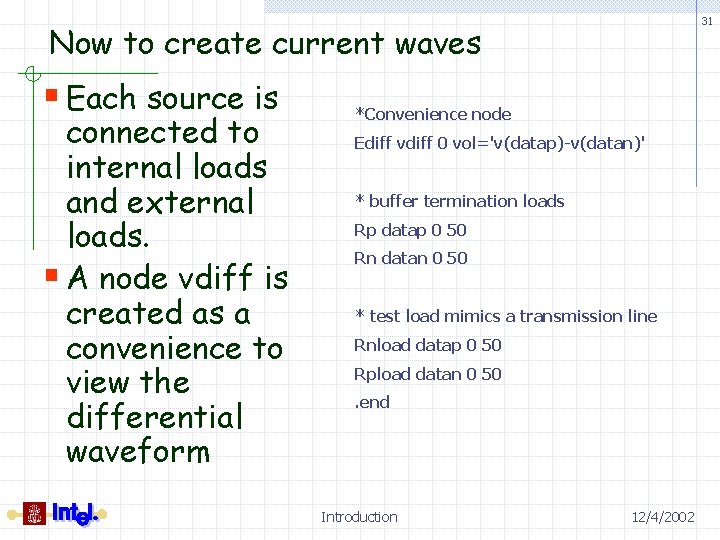

31 Now to create current waves § Each source is connected to internal loads and external loads. § A node vdiff is created as a convenience to view the differential waveform *Convenience node Ediff vdiff 0 vol='v(datap)-v(datan)' * buffer termination loads Rp datap 0 50 Rn datan 0 50 * test load mimics a transmission line Rnload datap 0 50 Rpload datan 0 50. end Introduction 12/4/2002

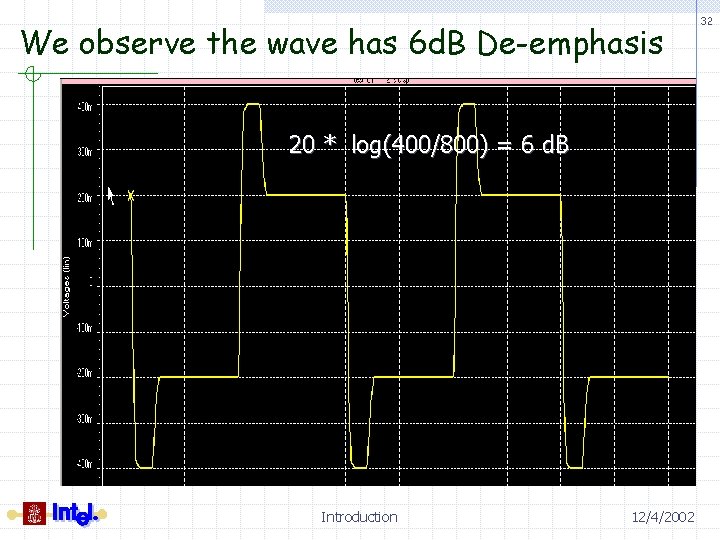

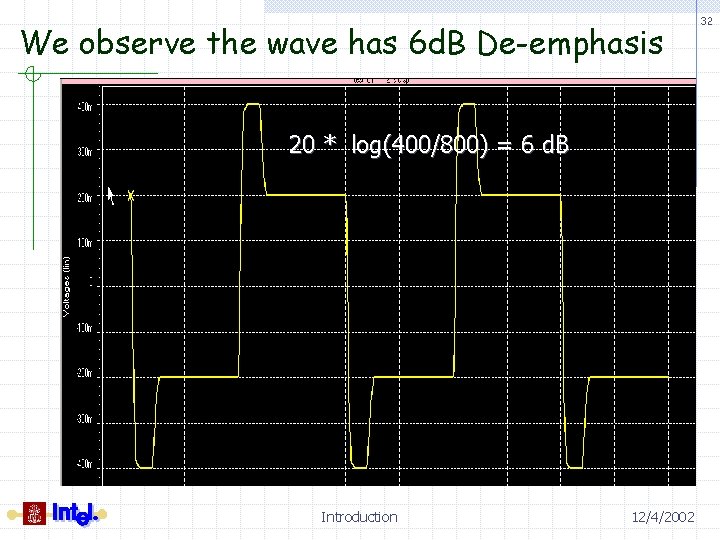

We observe the wave has 6 d. B De-emphasis 20 * log(400/800) = 6 d. B Introduction 12/4/2002 32

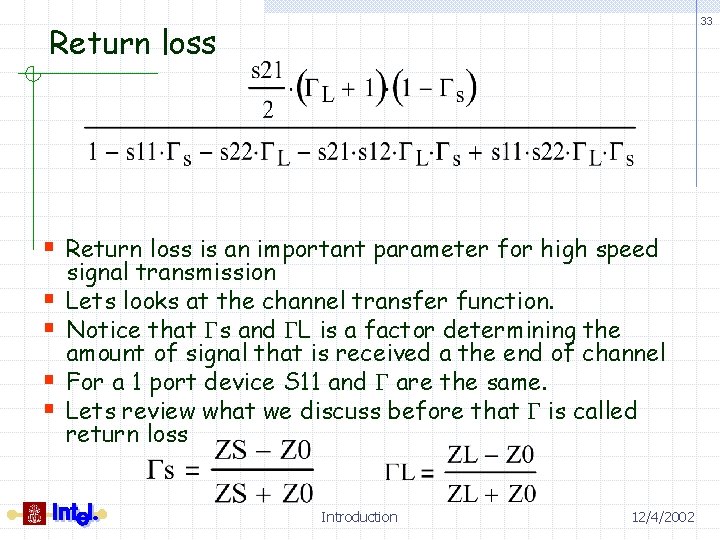

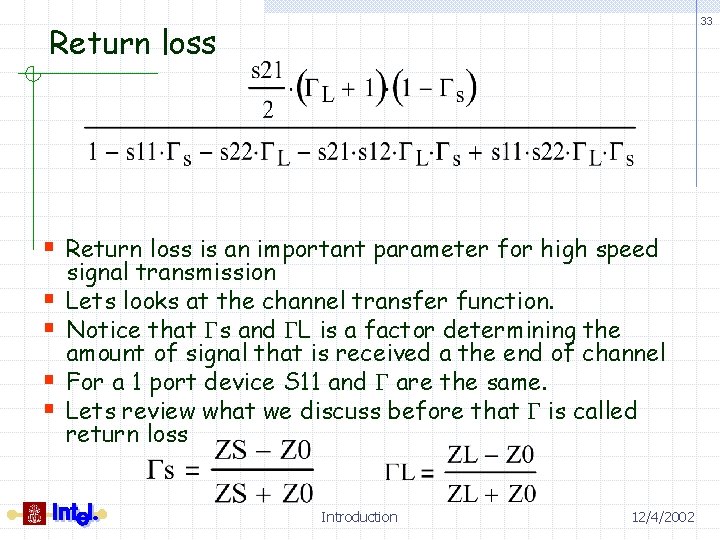

33 Return loss § Return loss is an important parameter for high speed § § signal transmission Lets looks at the channel transfer function. Notice that Gs and GL is a factor determining the amount of signal that is received a the end of channel For a 1 port device S 11 and G are the same. Lets review what we discuss before that G is called return loss Introduction 12/4/2002

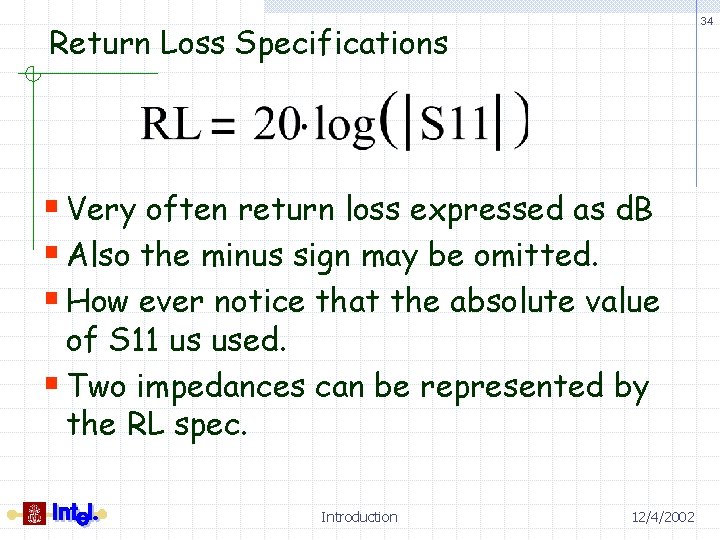

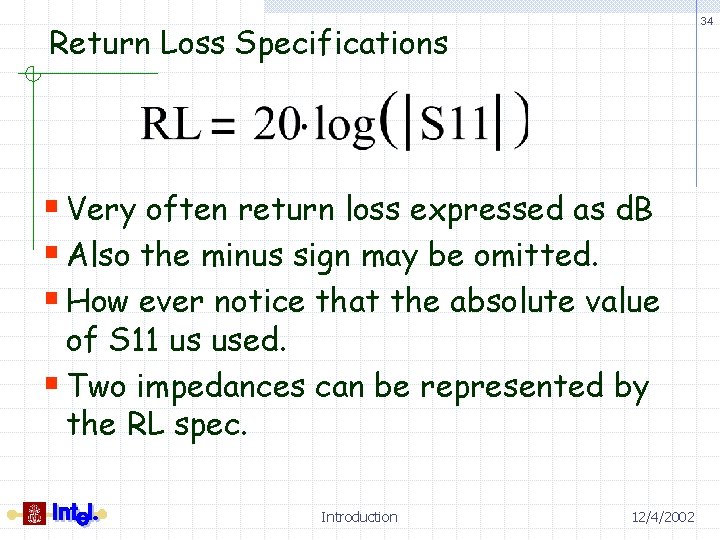

34 Return Loss Specifications § Very often return loss expressed as d. B § Also the minus sign may be omitted. § How ever notice that the absolute value of S 11 us used. § Two impedances can be represented by the RL spec. Introduction 12/4/2002

35 Example 0 f Impedance Spec From RL Introduction 12/4/2002

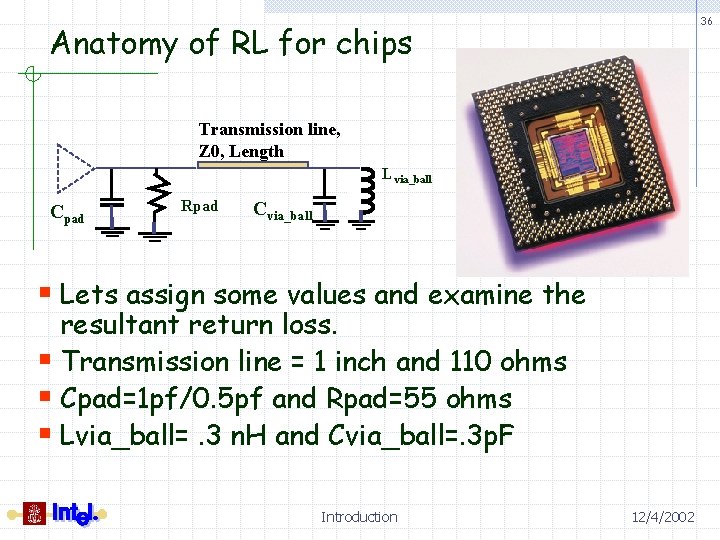

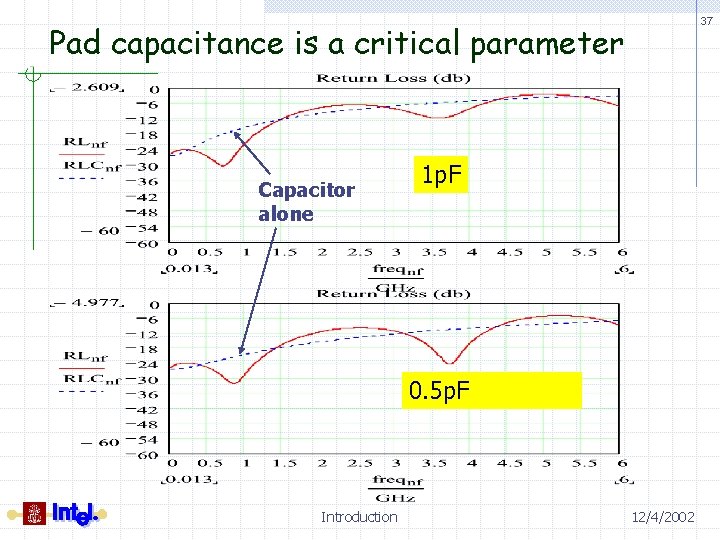

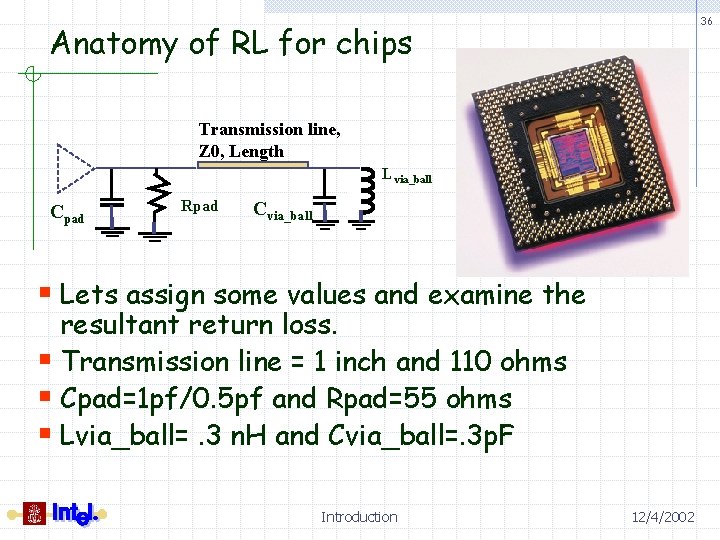

36 Anatomy of RL for chips Transmission line, Z 0, Length L via_ball Cpad Rpad Cvia_ball § Lets assign some values and examine the resultant return loss. § Transmission line = 1 inch and 110 ohms § Cpad=1 pf/0. 5 pf and Rpad=55 ohms § Lvia_ball=. 3 n. H and Cvia_ball=. 3 p. F Introduction 12/4/2002

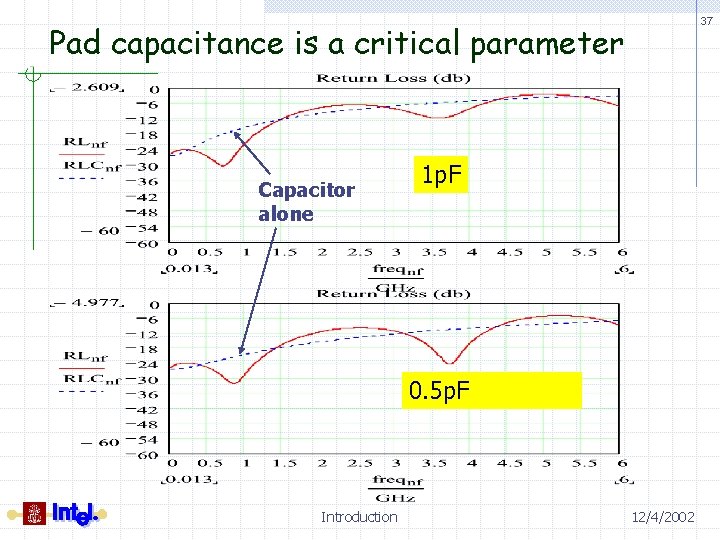

37 Pad capacitance is a critical parameter Capacitor alone 1 p. F 0. 5 p. F Introduction 12/4/2002

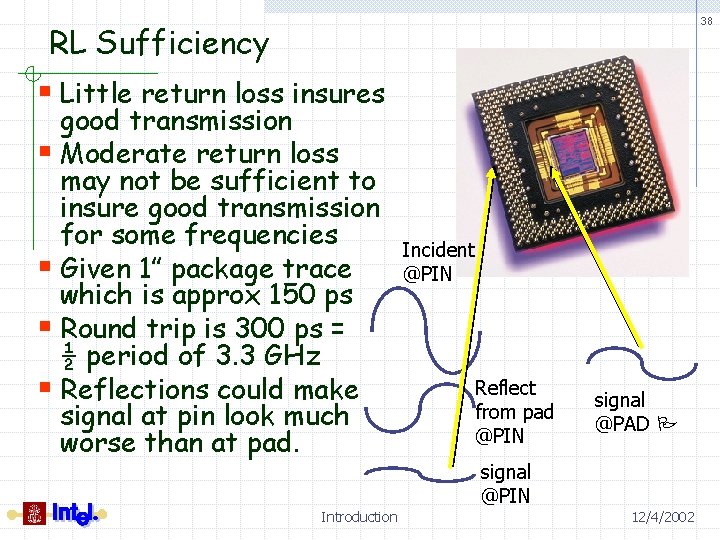

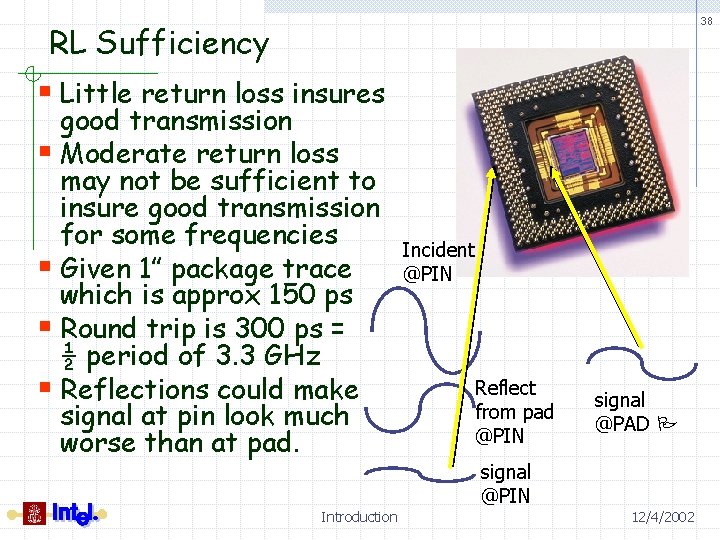

38 RL Sufficiency § Little return loss insures good transmission § Moderate return loss may not be sufficient to insure good transmission for some frequencies § Given 1” package trace which is approx 150 ps § Round trip is 300 ps = ½ period of 3. 3 GHz § Reflections could make signal at pin look much worse than at pad. Introduction Incident @PIN Reflect from pad @PIN signal @PAD 12/4/2002

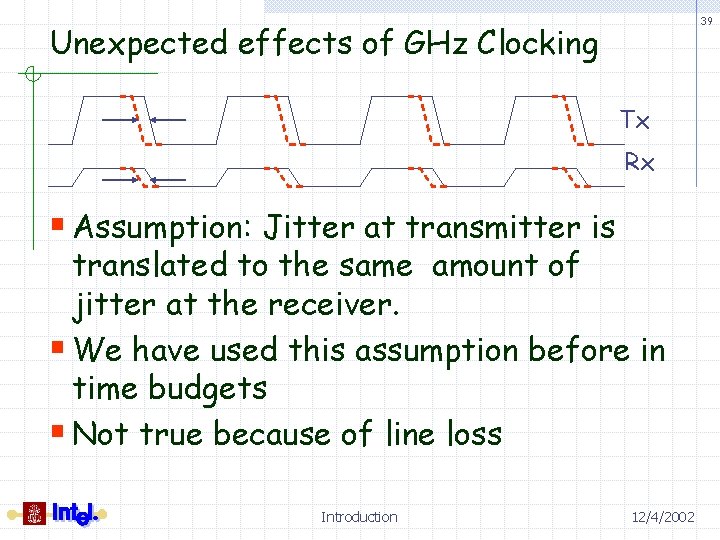

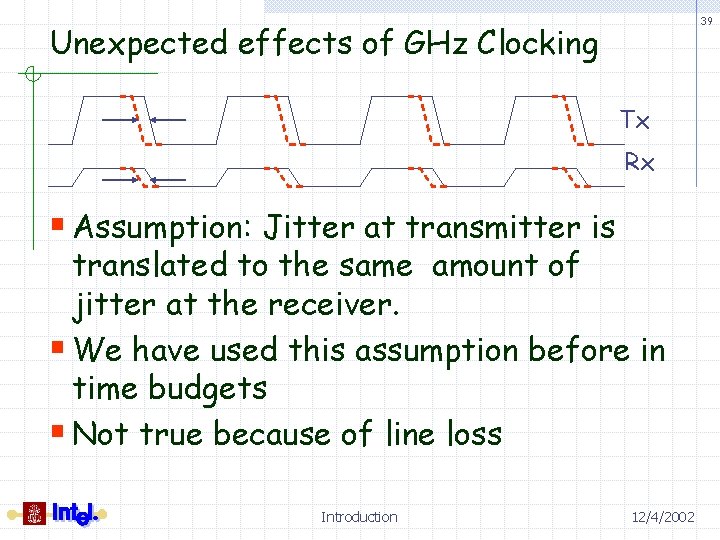

39 Unexpected effects of GHz Clocking Tx Rx § Assumption: Jitter at transmitter is translated to the same amount of jitter at the receiver. § We have used this assumption before in time budgets § Not true because of line loss Introduction 12/4/2002

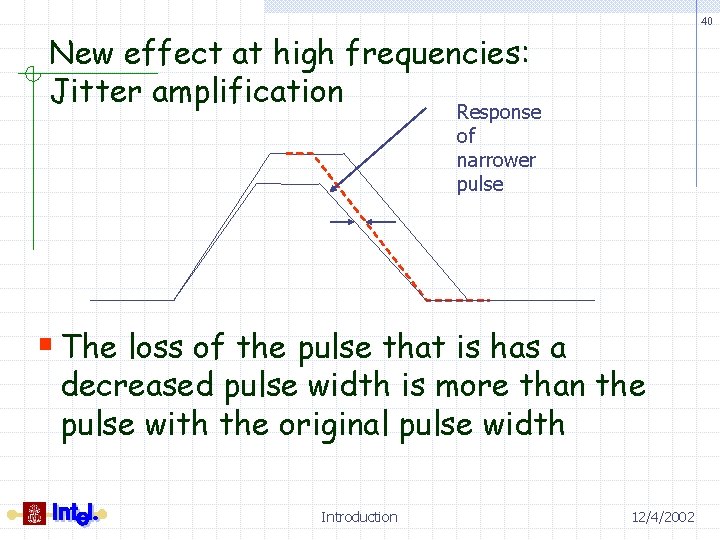

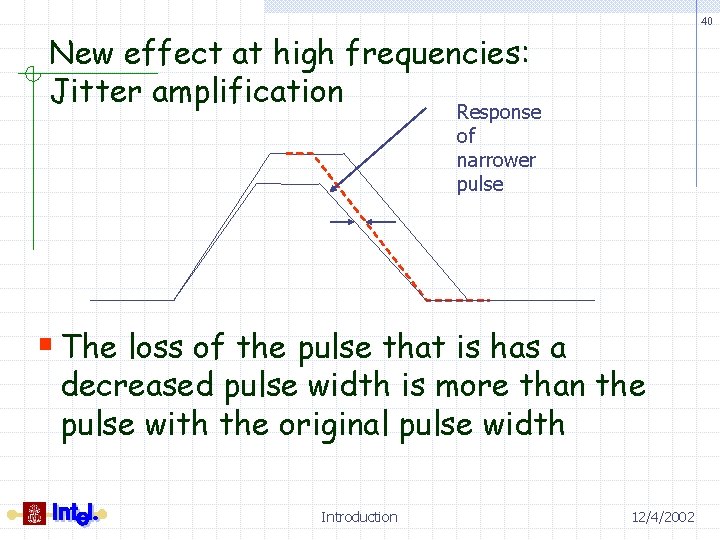

40 New effect at high frequencies: Jitter amplification Response of narrower pulse § The loss of the pulse that is has a decreased pulse width is more than the pulse with the original pulse width Introduction 12/4/2002

41 In summary here a few high frequency and differential topics we touched upon § § § § Clock recovery Return loss Common and differential mode signal Equalization Inter-symbol interference (ISI) Current mode logic The next task is to evaluate a channel’s quality when all these effects are included. In other words what does the worst signal look like and how do we find it? This will be the subject the next class Introduction 12/4/2002