ELE 22 MIC Lecture 10 MULTIPLEXOR DATA SELECTOR

- Slides: 36

ELE 22 MIC Lecture 10 • • MULTIPLEXOR - DATA SELECTOR DEMULTIPLEXOR - DATA DISTRIBUTOR Parallel to Serial Data Conversion External Address Bus Latching Address Strobe timing Diagram Address Decoding using a 74 ls 138 Serial Peripheral Interface - SPI

Microprocessors: Web Resources

Multiplexor - Data Selector • Multiplex (MUX) many inputs to one output • Switch selects the one signal source from many input signals. • Like Stereo source selection

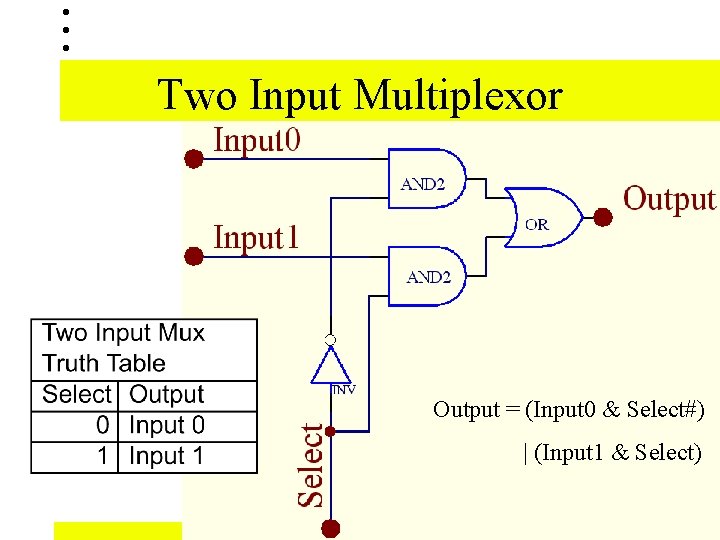

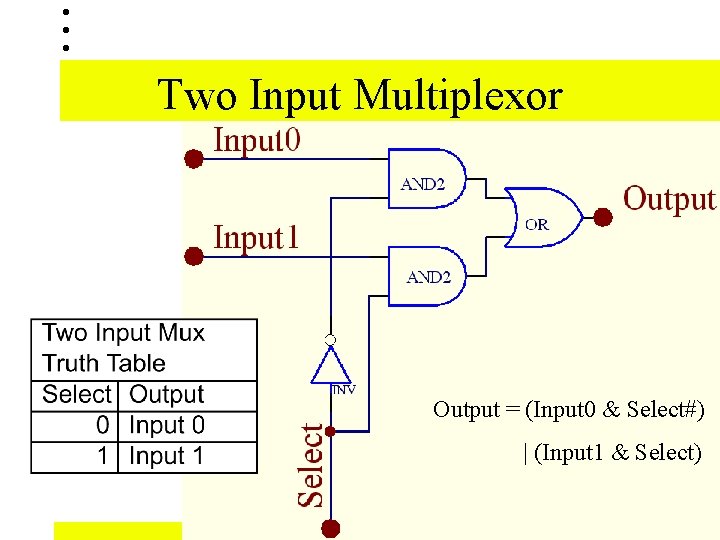

Two Input Multiplexor Output = (Input 0 & Select#) | (Input 1 & Select)

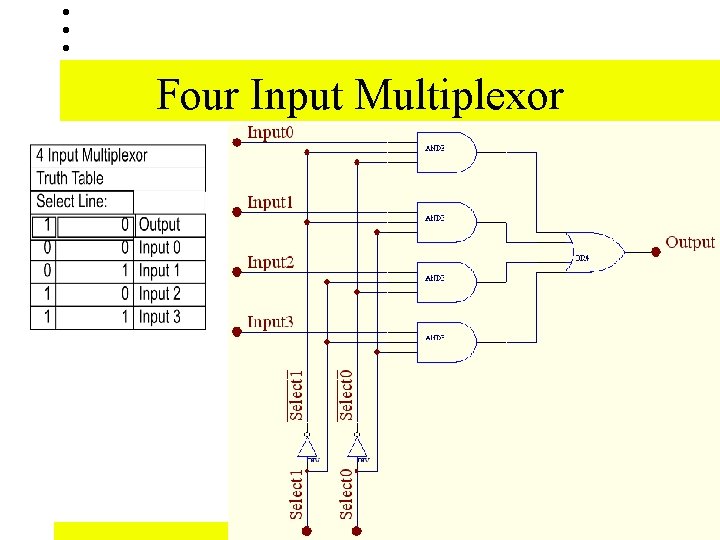

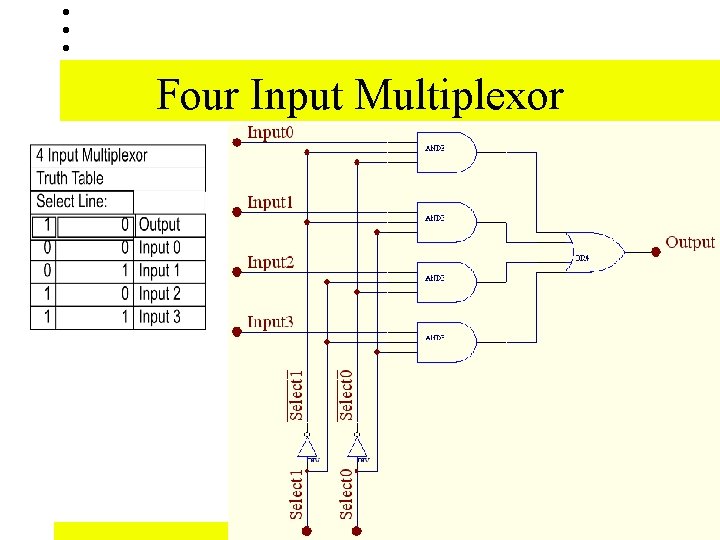

Four Input Multiplexor

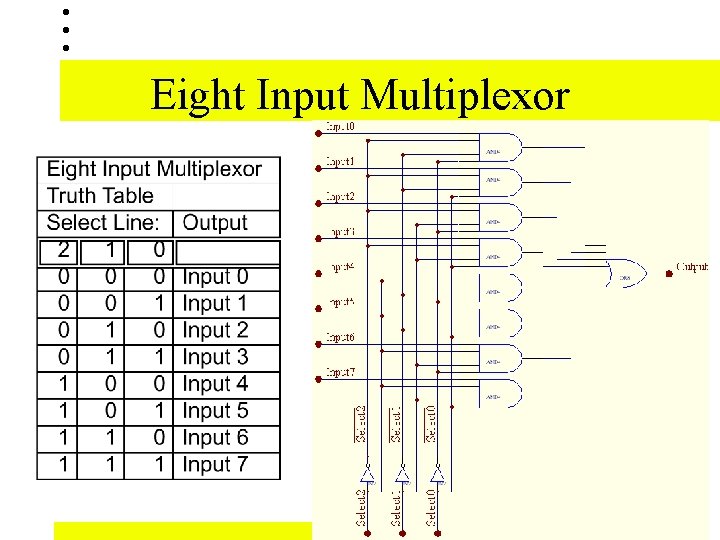

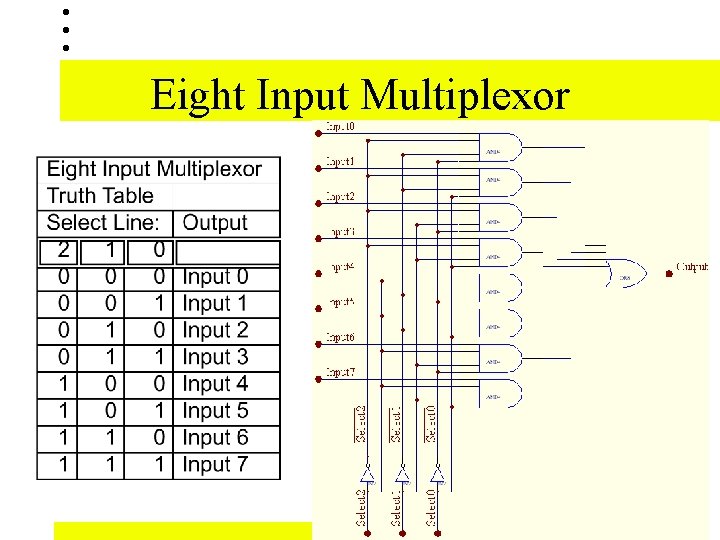

Eight Input Multiplexor

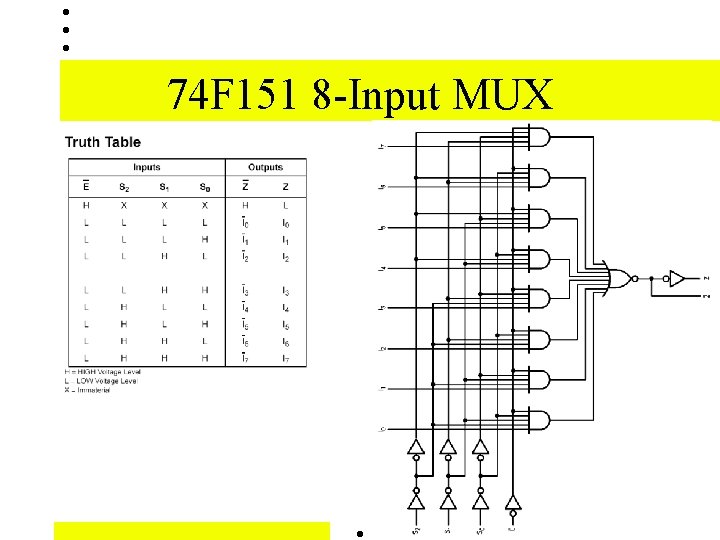

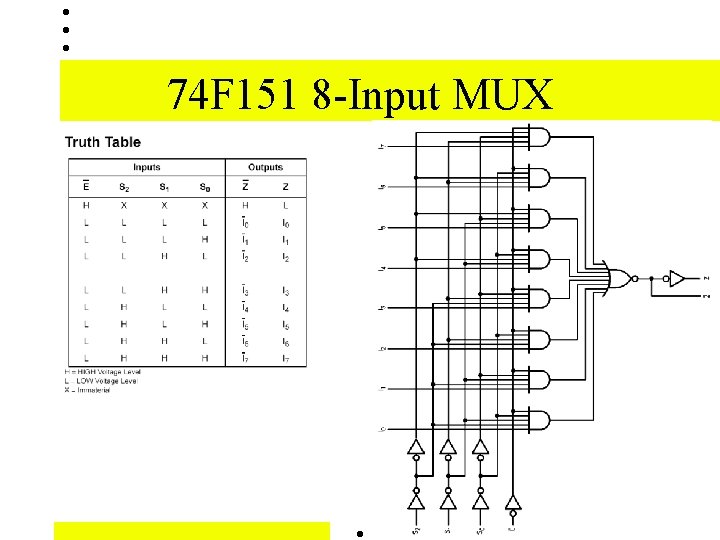

74 F 151 8 -Input MUX

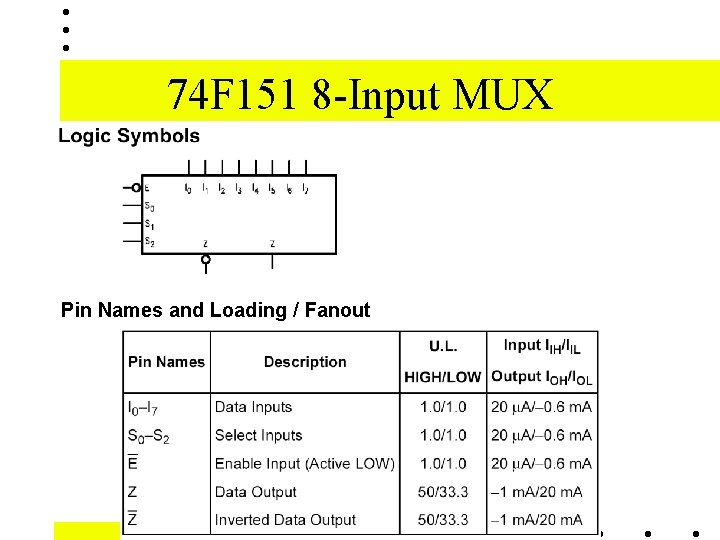

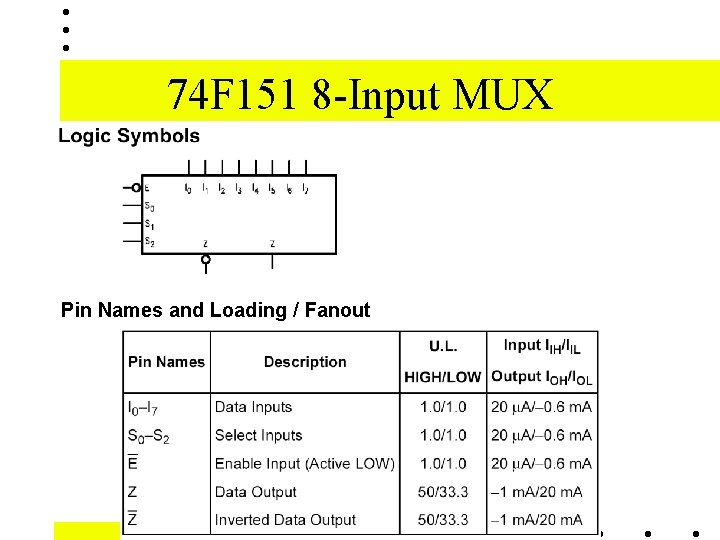

74 F 151 8 -Input MUX Pin Names and Loading / Fanout

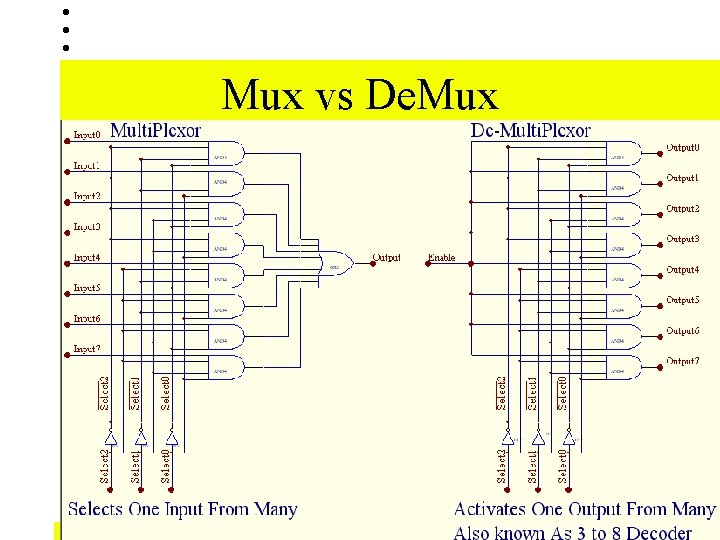

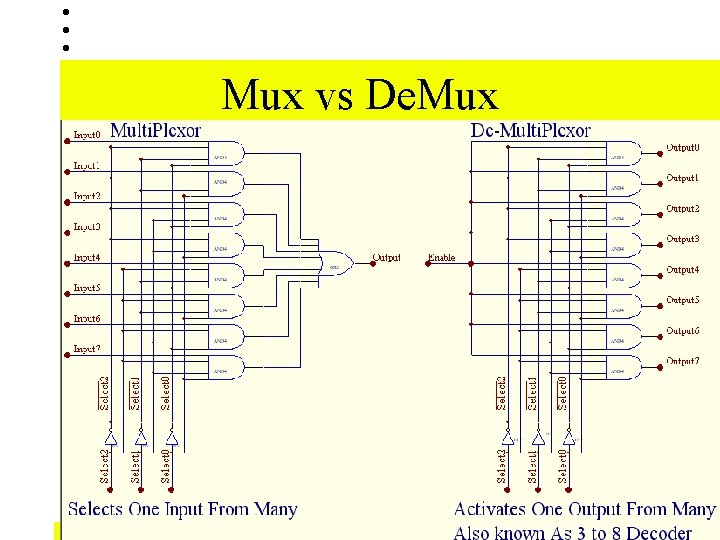

Mux vs De. Mux

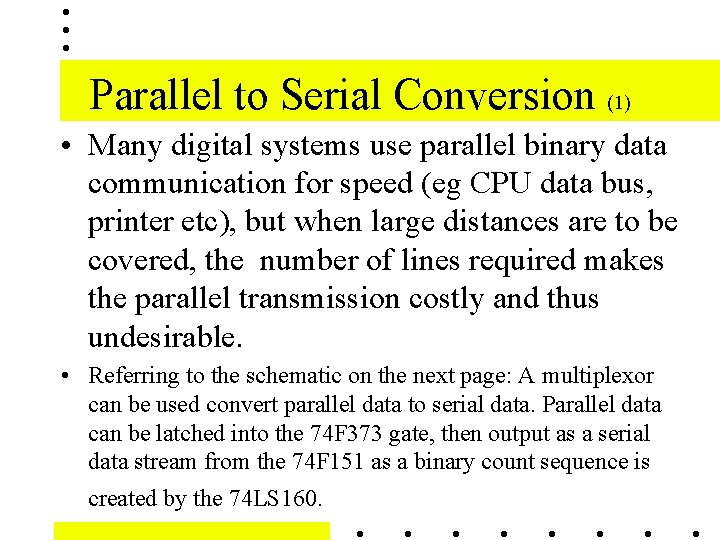

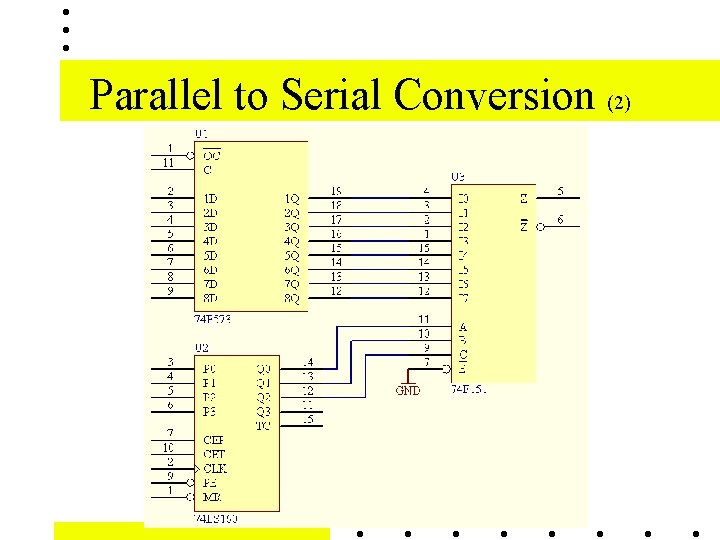

Parallel to Serial Conversion (1) • Many digital systems use parallel binary data communication for speed (eg CPU data bus, printer etc), but when large distances are to be covered, the number of lines required makes the parallel transmission costly and thus undesirable. • Referring to the schematic on the next page: A multiplexor can be used convert parallel data to serial data. Parallel data can be latched into the 74 F 373 gate, then output as a serial data stream from the 74 F 151 as a binary count sequence is created by the 74 LS 160.

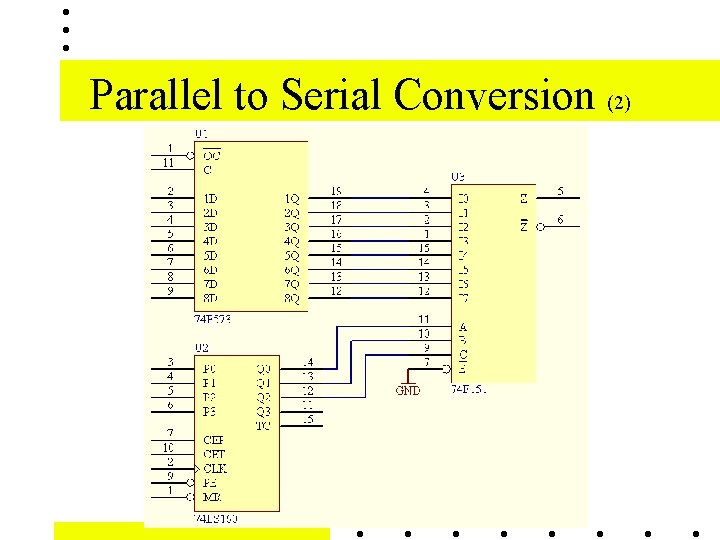

Parallel to Serial Conversion (2)

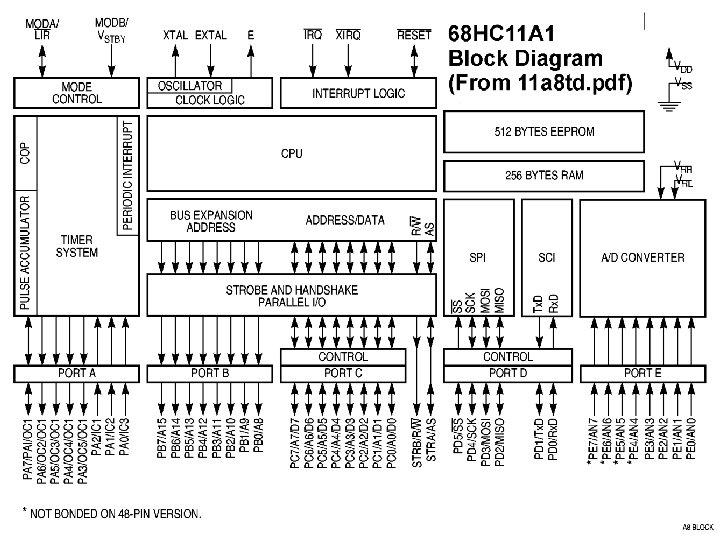

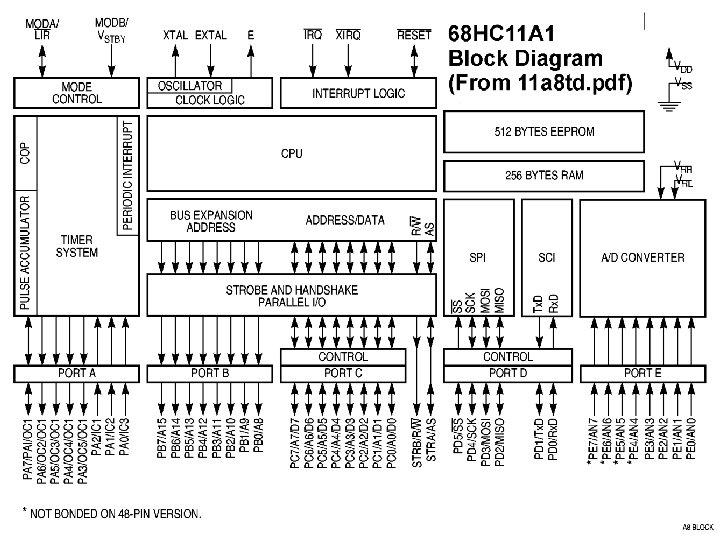

Parallel I/O

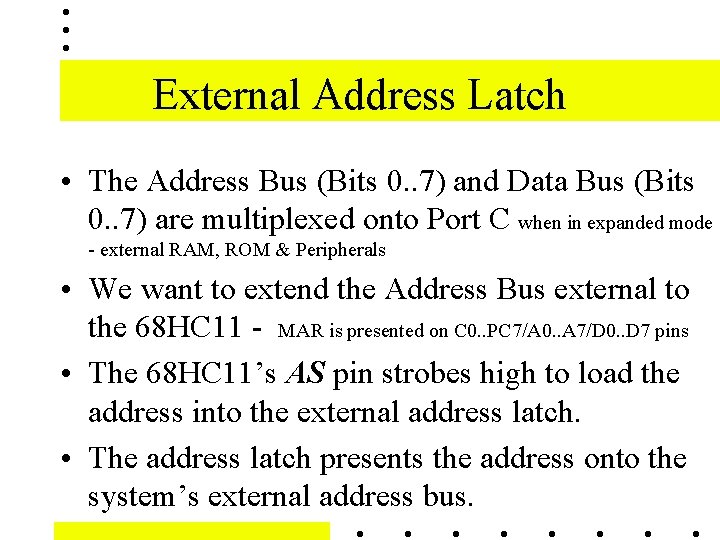

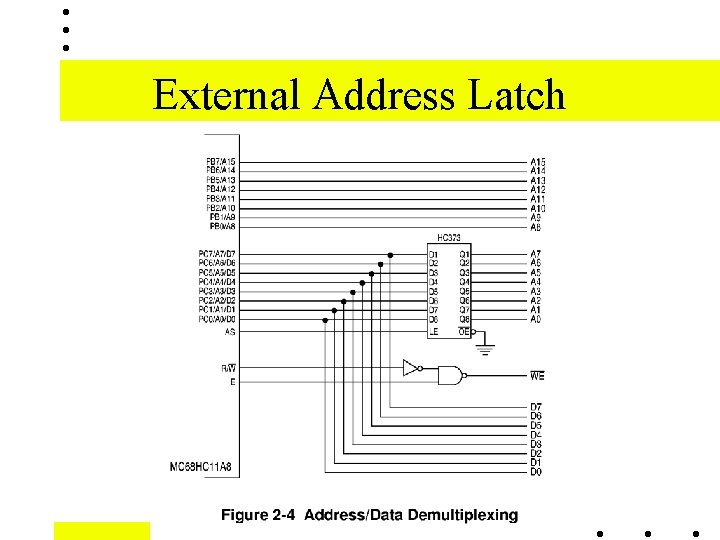

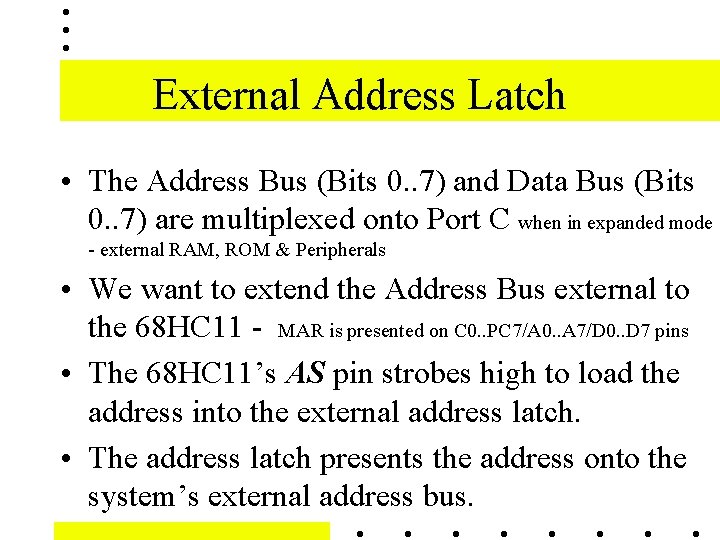

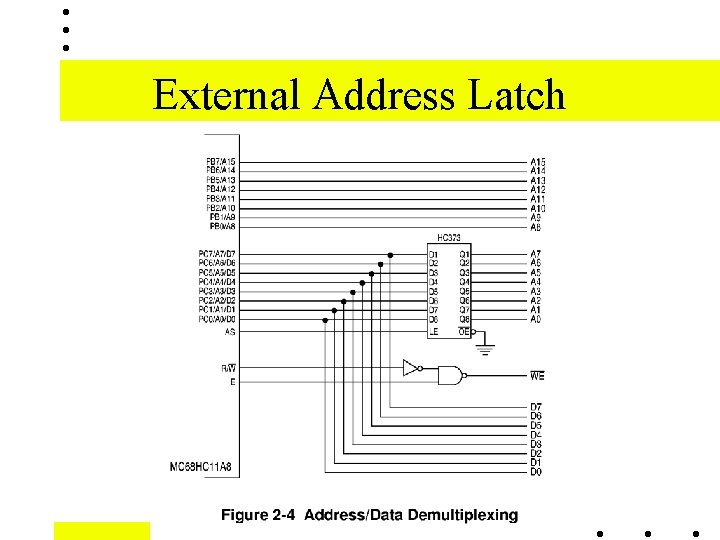

External Address Latch • The Address Bus (Bits 0. . 7) and Data Bus (Bits 0. . 7) are multiplexed onto Port C when in expanded mode - external RAM, ROM & Peripherals • We want to extend the Address Bus external to the 68 HC 11 - MAR is presented on C 0. . PC 7/A 0. . A 7/D 0. . D 7 pins • The 68 HC 11’s AS pin strobes high to load the address into the external address latch. • The address latch presents the address onto the system’s external address bus.

External Address Latch

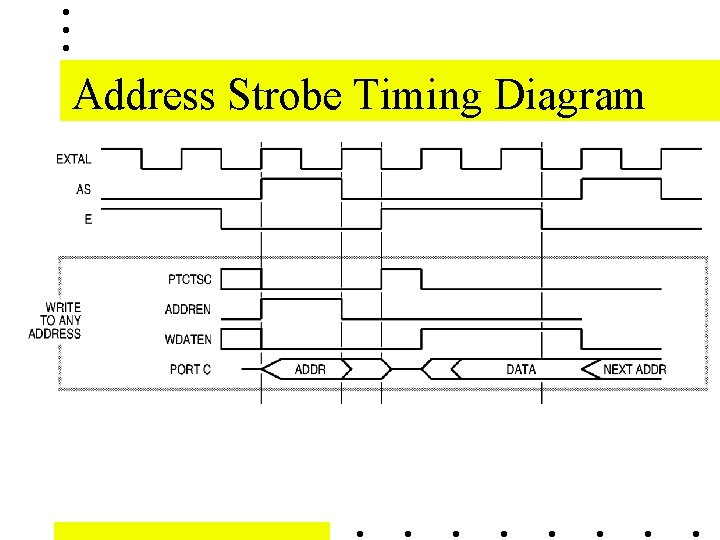

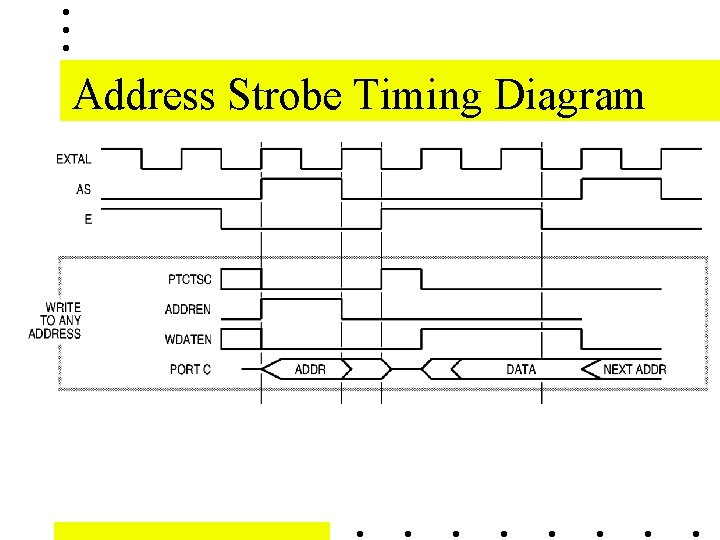

Address Strobe Timing Diagram

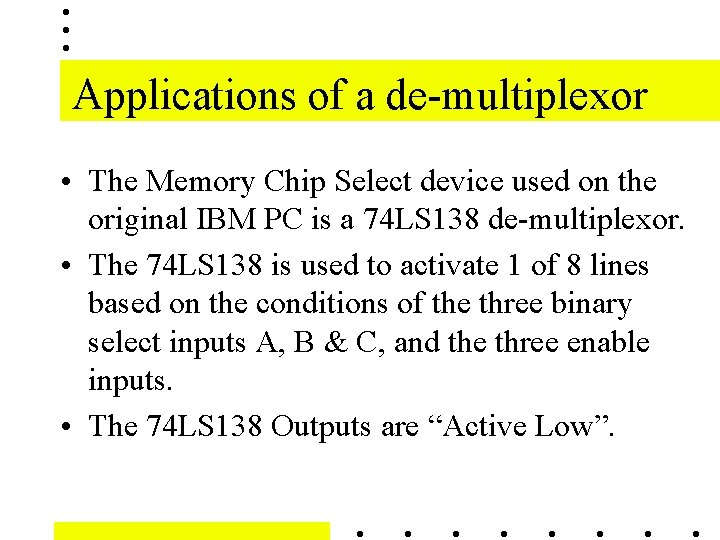

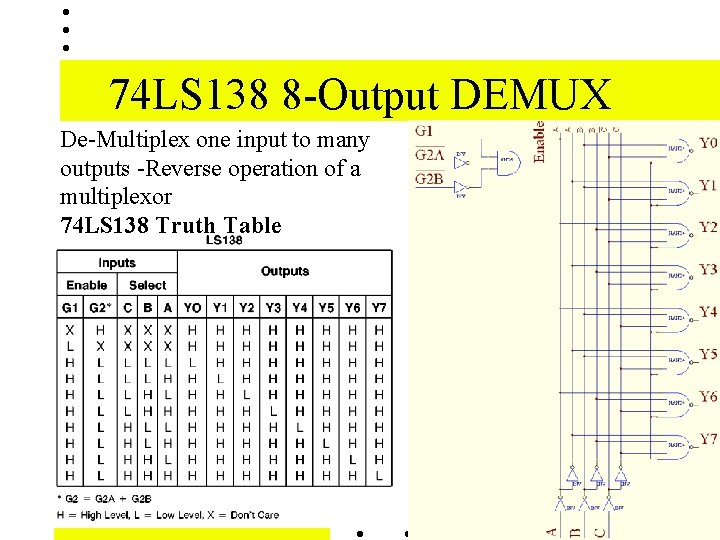

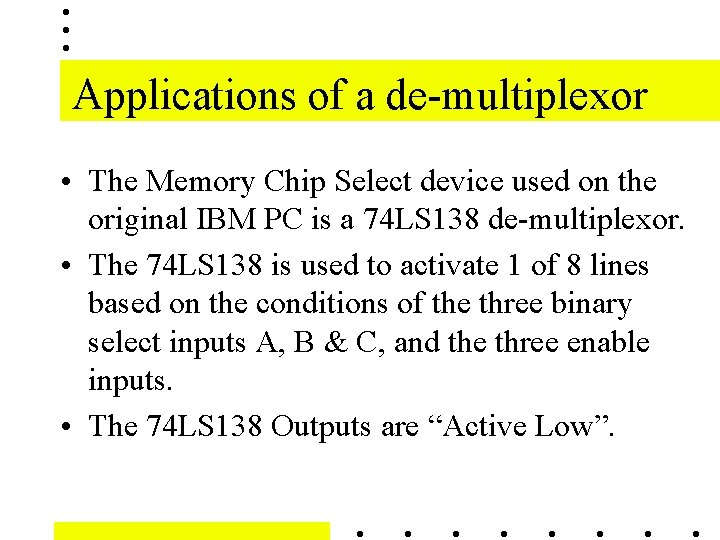

Applications of a de-multiplexor • The Memory Chip Select device used on the original IBM PC is a 74 LS 138 de-multiplexor. • The 74 LS 138 is used to activate 1 of 8 lines based on the conditions of the three binary select inputs A, B & C, and the three enable inputs. • The 74 LS 138 Outputs are “Active Low”.

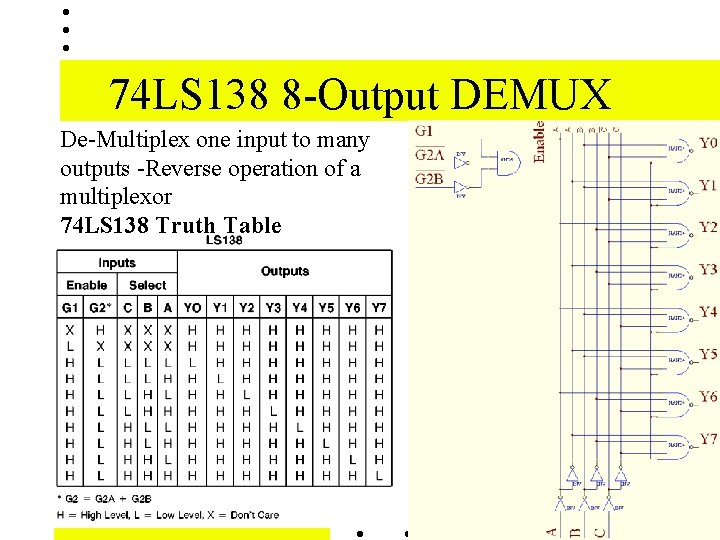

74 LS 138 8 -Output DEMUX De-Multiplex one input to many outputs -Reverse operation of a multiplexor 74 LS 138 Truth Table

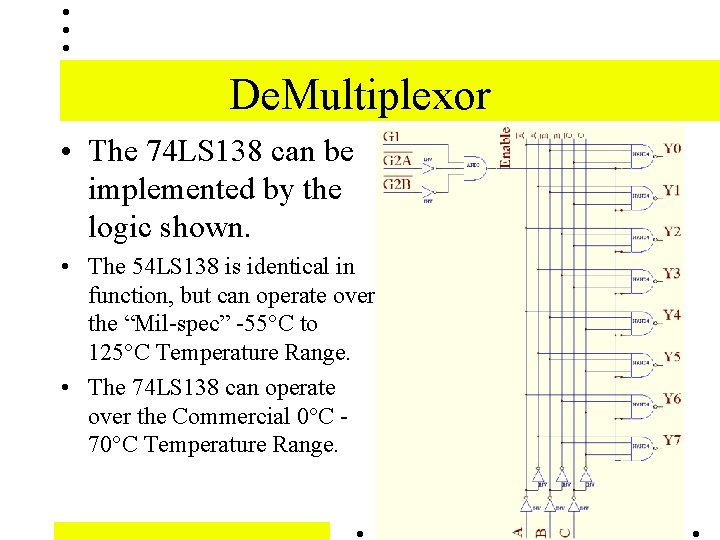

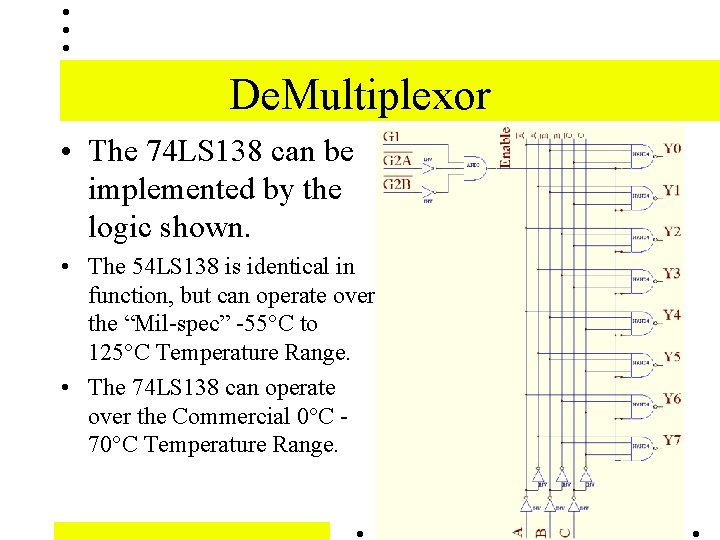

De. Multiplexor • The 74 LS 138 can be implemented by the logic shown. • The 54 LS 138 is identical in function, but can operate over the “Mil-spec” -55°C to 125°C Temperature Range. • The 74 LS 138 can operate over the Commercial 0°C 70°C Temperature Range.

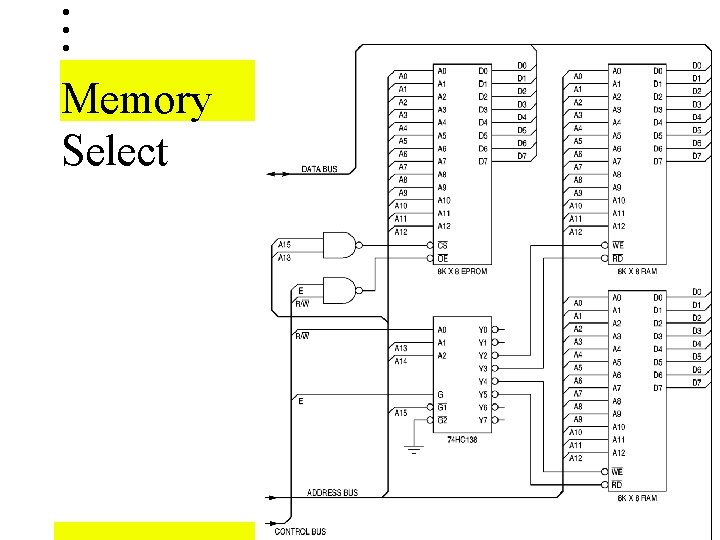

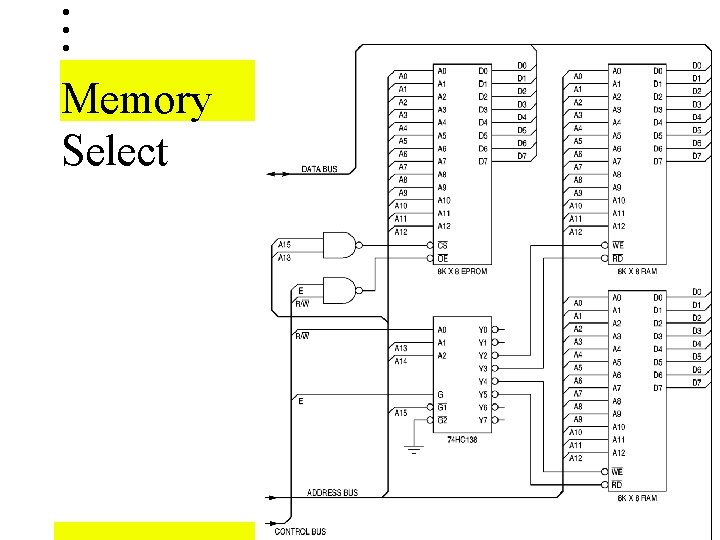

Memory Select

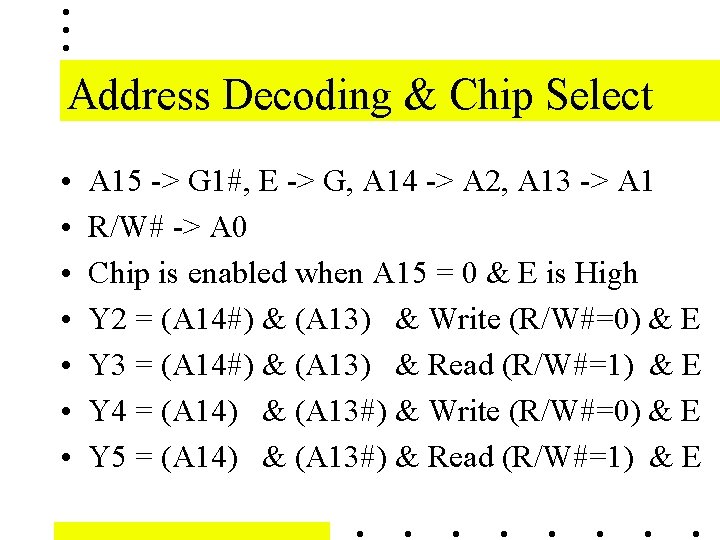

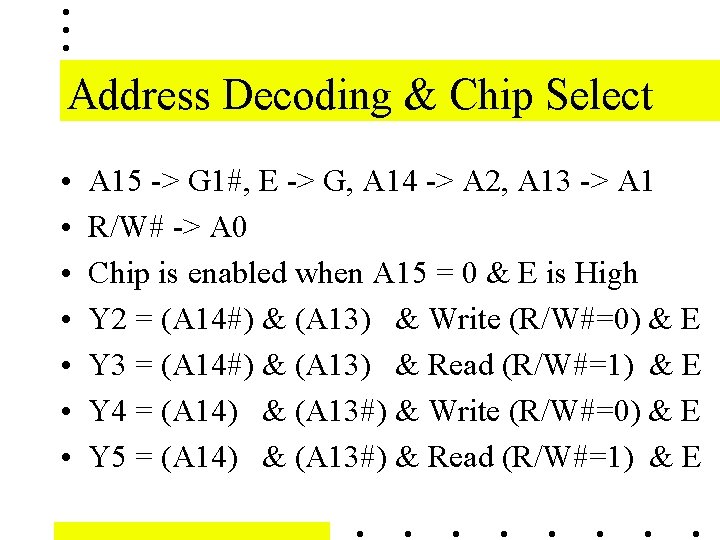

Address Decoding & Chip Select • • A 15 -> G 1#, E -> G, A 14 -> A 2, A 13 -> A 1 R/W# -> A 0 Chip is enabled when A 15 = 0 & E is High Y 2 = (A 14#) & (A 13) & Write (R/W#=0) & E Y 3 = (A 14#) & (A 13) & Read (R/W#=1) & E Y 4 = (A 14) & (A 13#) & Write (R/W#=0) & E Y 5 = (A 14) & (A 13#) & Read (R/W#=1) & E

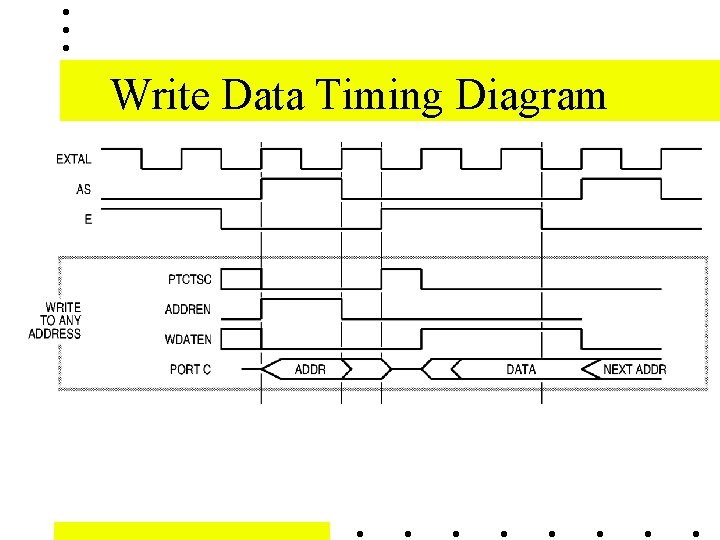

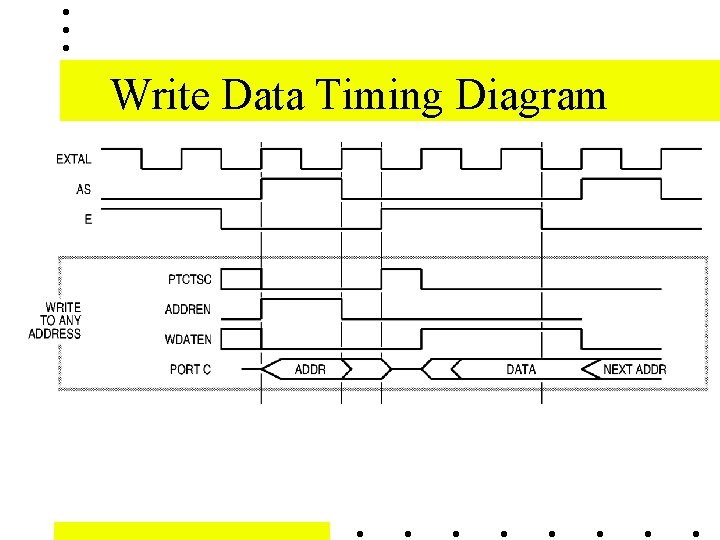

Write Data Timing Diagram

Serial Peripheral Interface (SPI) During an SPI transfer, data is simultaneously transmitted (shifted out serially) and received (shifted in serially). A serial clock line synchronises shifting and sampling of the information on the two serial data lines. A slave select line allows individual selection of a slave SPI device; slave devices that are not selected do not interfere with SPI bus activities. On a master SPI device, the slave select line can optionally be used to indicate a multiple-master bus contention.

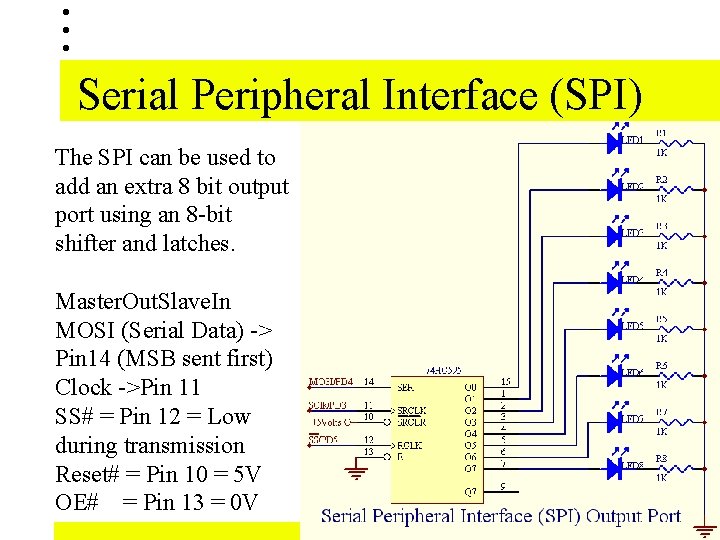

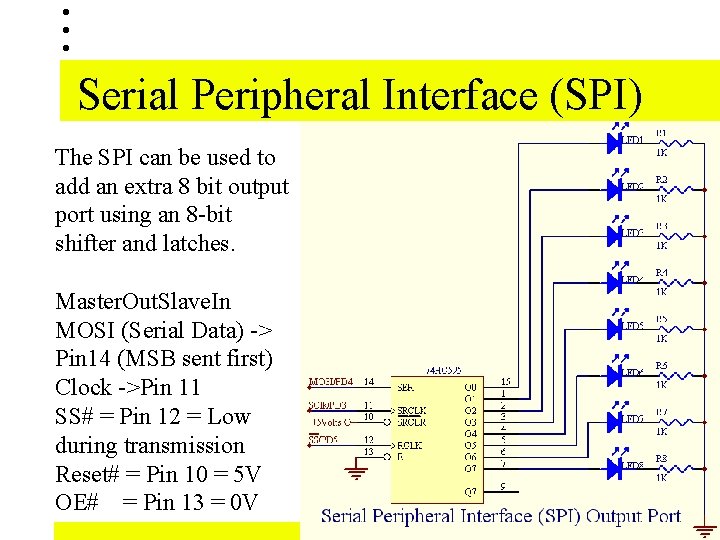

Serial Peripheral Interface (SPI) The SPI can be used to add an extra 8 bit output port using an 8 -bit shifter and latches. Master. Out. Slave. In MOSI (Serial Data) -> Pin 14 (MSB sent first) Clock ->Pin 11 SS# = Pin 12 = Low during transmission Reset# = Pin 10 = 5 V OE# = Pin 13 = 0 V

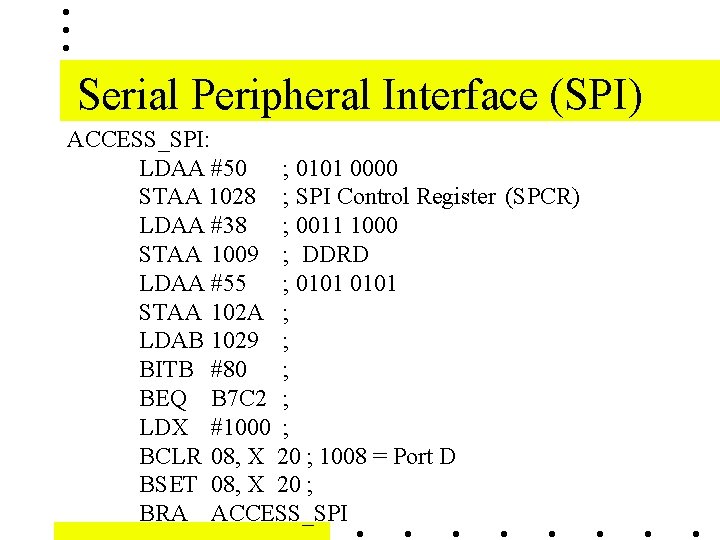

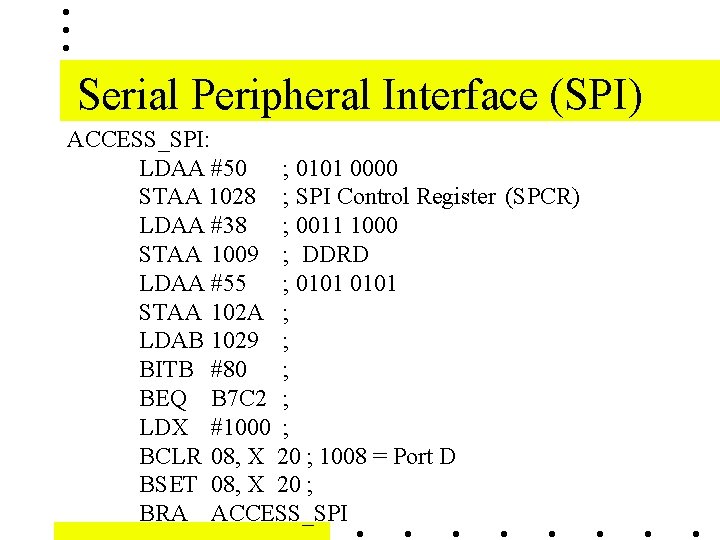

Serial Peripheral Interface (SPI) ACCESS_SPI: LDAA #50 ; 0101 0000 STAA 1028 ; SPI Control Register (SPCR) LDAA #38 ; 0011 1000 STAA 1009 ; DDRD LDAA #55 ; 0101 STAA 102 A ; LDAB 1029 ; BITB #80 ; BEQ B 7 C 2 ; LDX #1000 ; BCLR 08, X 20 ; 1008 = Port D BSET 08, X 20 ; BRA ACCESS_SPI

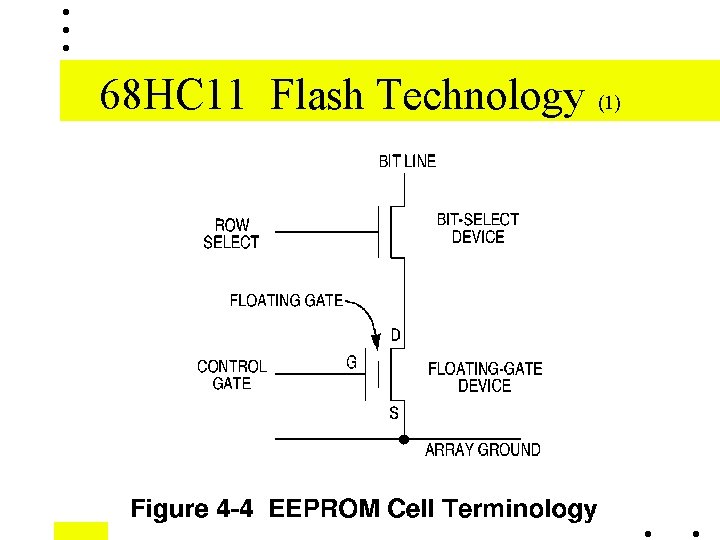

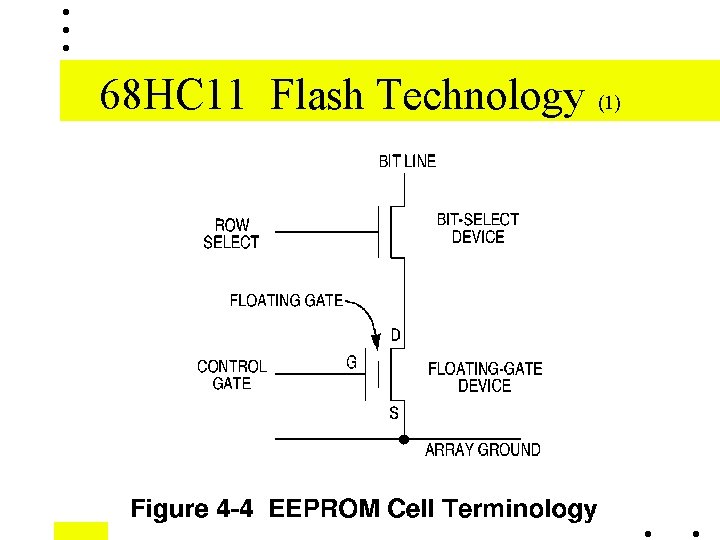

68 HC 11 Flash Technology (1)

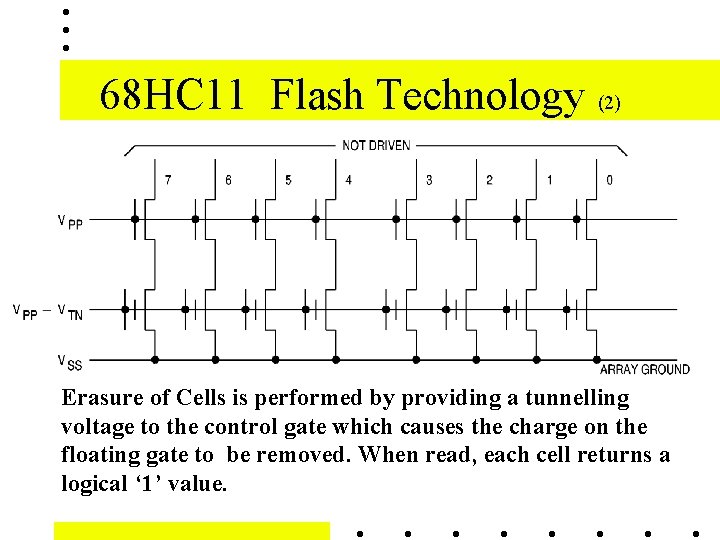

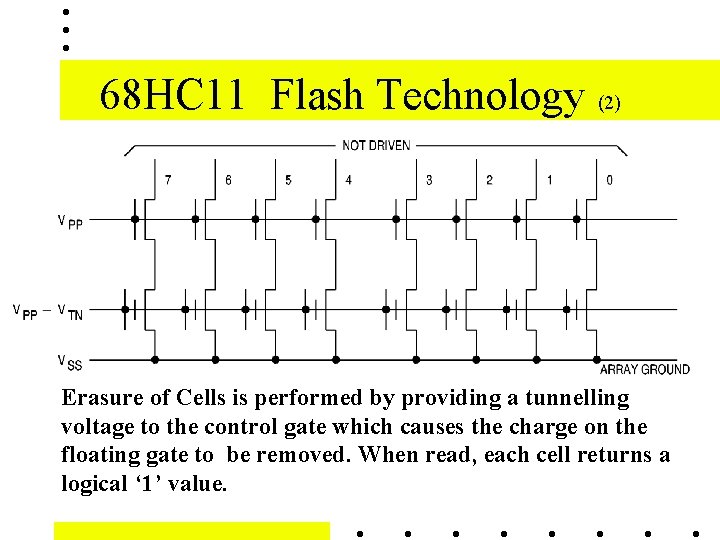

68 HC 11 Flash Technology (2) Erasure of Cells is performed by providing a tunnelling voltage to the control gate which causes the charge on the floating gate to be removed. When read, each cell returns a logical ‘ 1’ value.

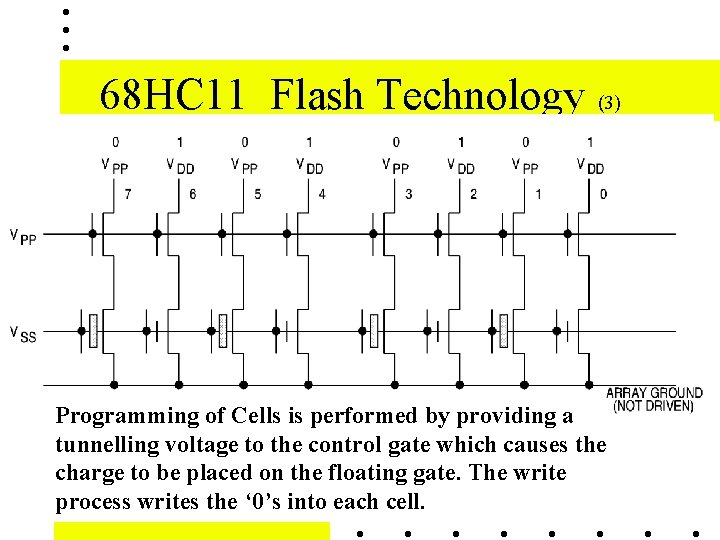

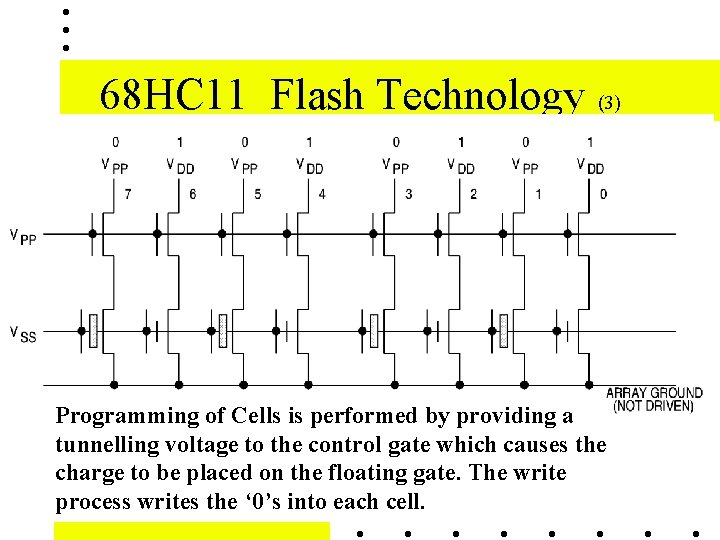

68 HC 11 Flash Technology (3) Programming of Cells is performed by providing a tunnelling voltage to the control gate which causes the charge to be placed on the floating gate. The write process writes the ‘ 0’s into each cell.

68 HC 11 I/O & Control Bits (2)

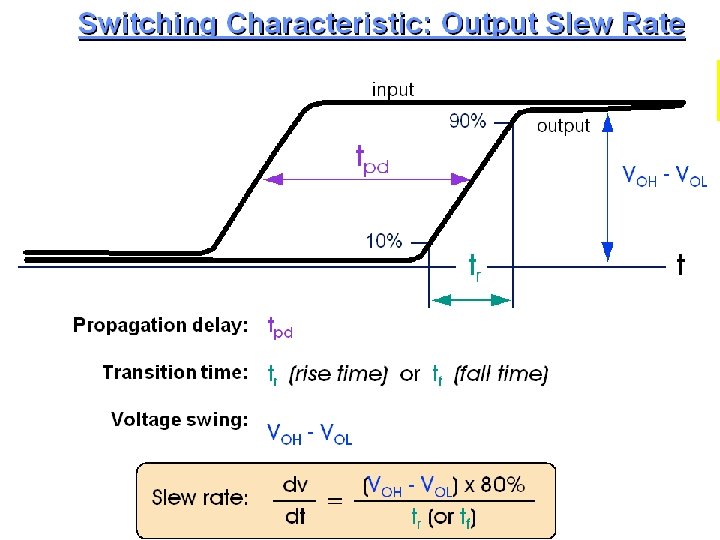

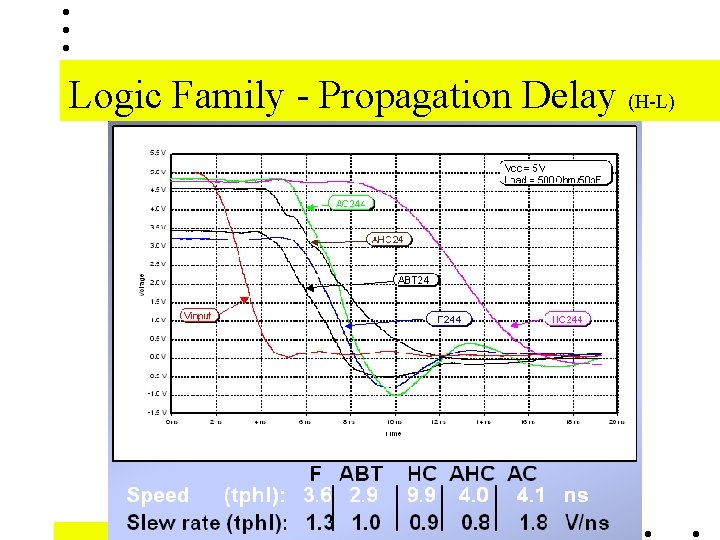

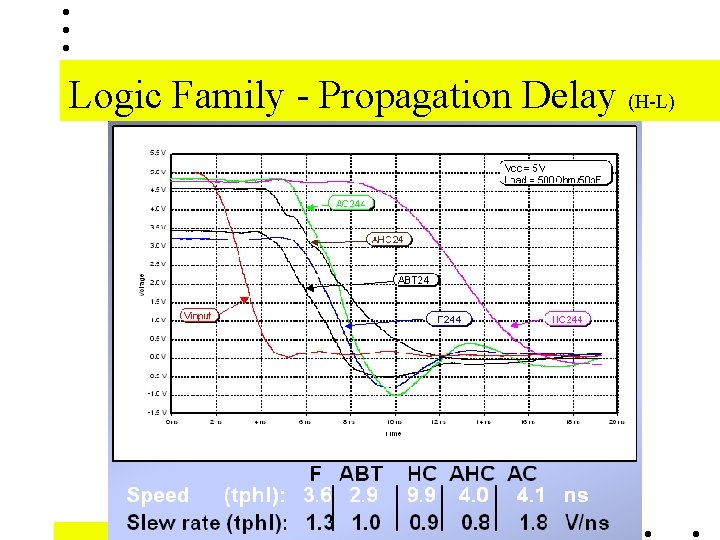

Logic Family - Propagation Delay (H-L)

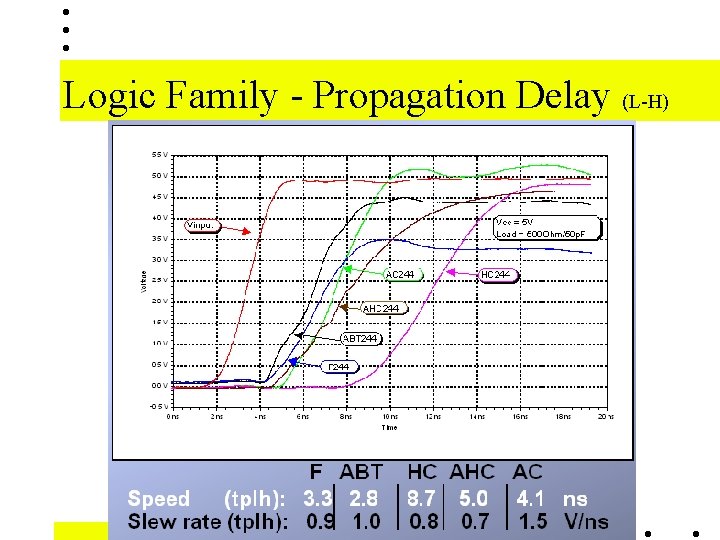

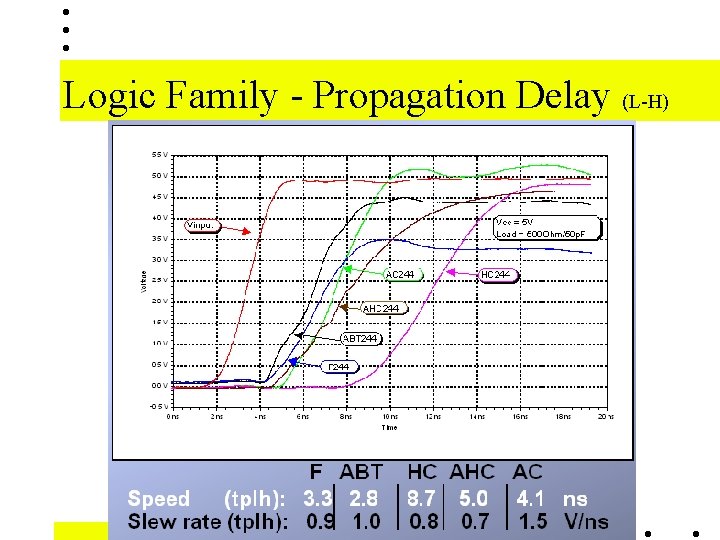

Logic Family - Propagation Delay (L-H)

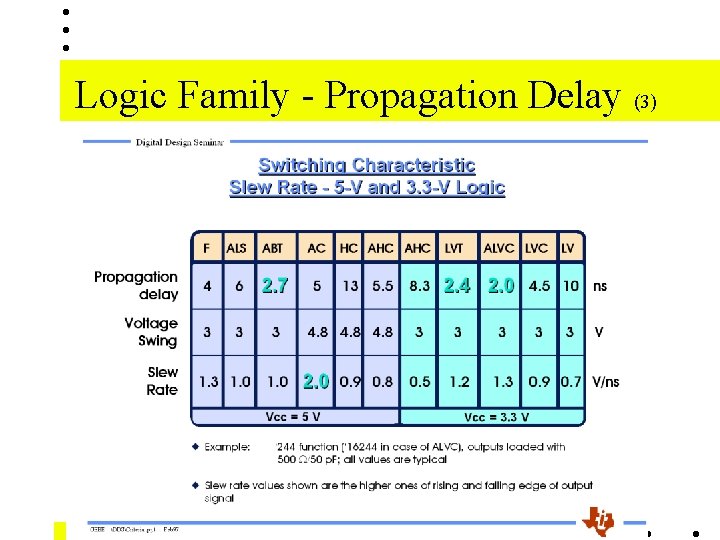

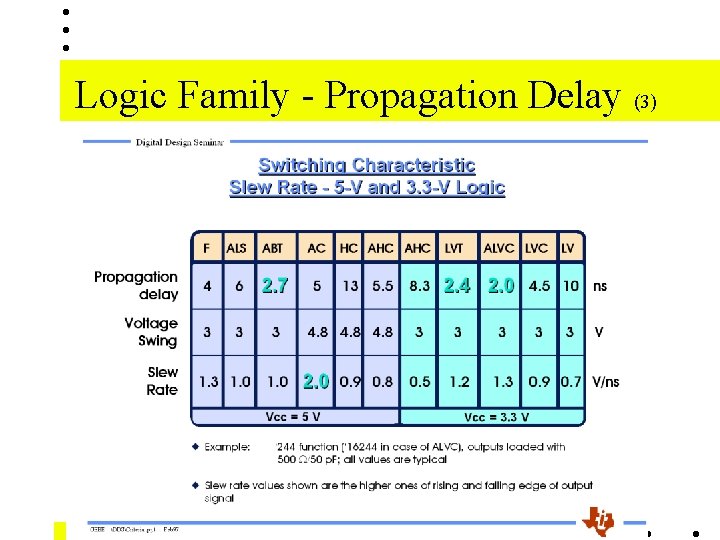

Logic Family - Propagation Delay (3)

Bus Design Rules Bus lines have very low line impedances (20. . 40 Ohms). • Bus lines have to be terminated to prevent line reflections (signal distortion, circuit malfunctions due to undershoots). • Take care of propagation times (25 ns/m). Settling time of signals on TTL-type buses is 2 x tp (no incident wave switching). • Take care of control lines (clock, read, write, etc. ). • Provide shielding between control lines and data / address lines.

Bus Design Rules • A multiplexed data and address bus reduces design problems (50% less signal lines and 50% less line driver). • Driver output current is 100 m. A/line. Provide adequate and low inductance GND return path (simultaneous switching)! • Rule of thumb: 25% of all backplane connector pins have to be GND lines! • Use multilayer boards with separate GND and Vcc plane for backplanes.

Acknowledgements • I used Altium Protel 98 and Protel DXP to create these schematic diagrams • Logic Timing Diagrams are from Texas Instruments (TI) Logic Selection Guide Digital Design Seminar • National Semiconductor data sheets 74 LS 138. • Motorola 11 rm. pdf Reference Manual