Multiplexers MUXs also called a data selector Input

- Slides: 47

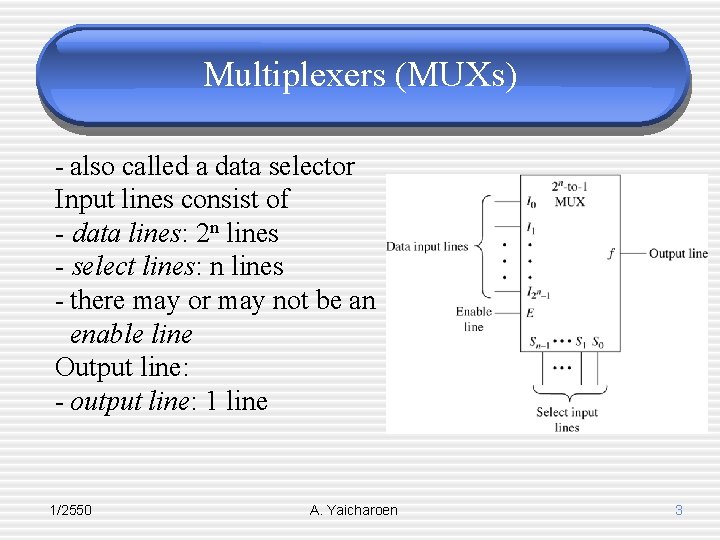

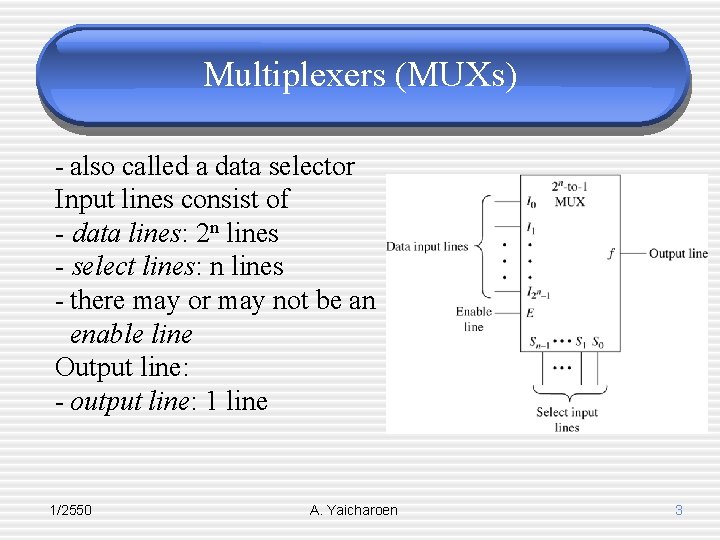

Multiplexers (MUXs) - also called a data selector Input lines consist of - data lines: 2 n lines - select lines: n lines - there may or may not be an enable line Output line: - output line: 1 line 1/2550 A. Yaicharoen 3

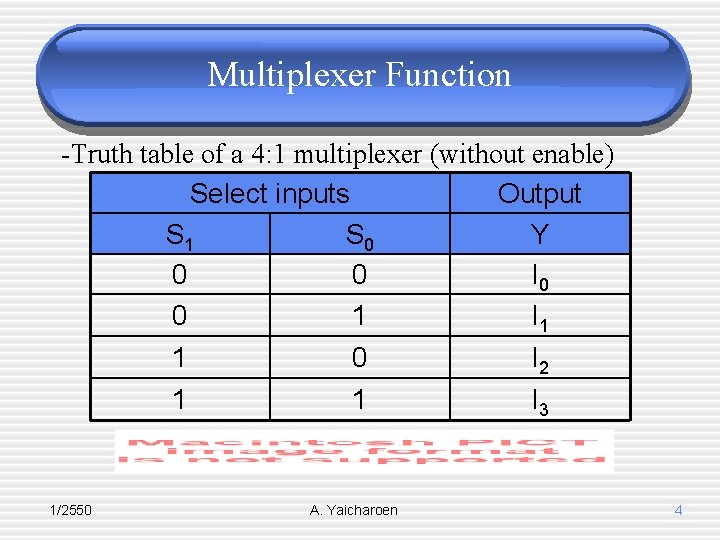

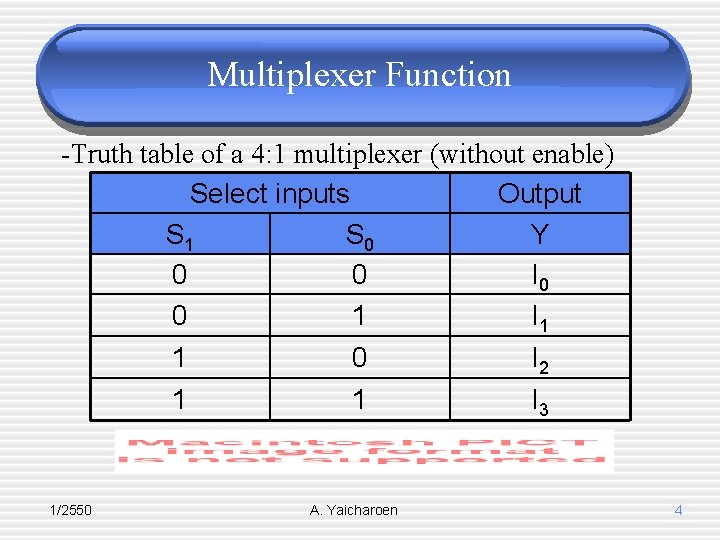

Multiplexer Function -Truth table of a 4: 1 multiplexer (without enable) Select inputs Output S 1 S 0 Y 0 0 I 0 0 1 I 1 1 0 I 2 1 1 I 3 1/2550 A. Yaicharoen 4

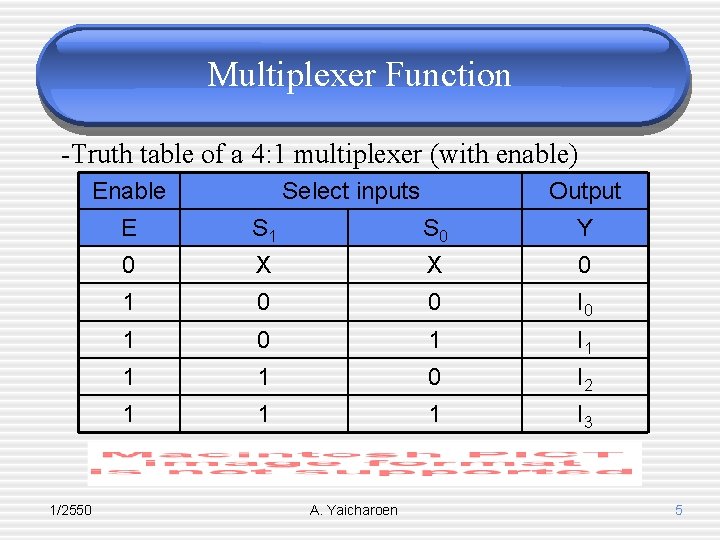

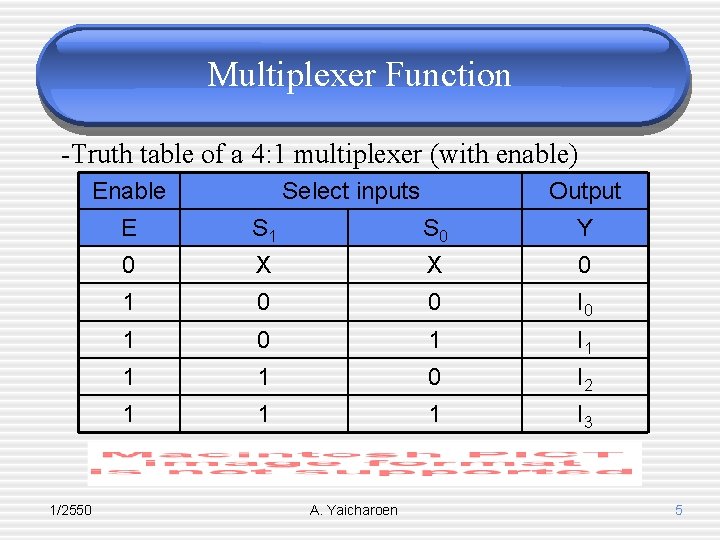

Multiplexer Function -Truth table of a 4: 1 multiplexer (with enable) Enable 1/2550 Select inputs Output E S 1 S 0 Y 0 X X 0 1 0 0 I 0 1 I 1 1 1 0 I 2 1 1 1 I 3 A. Yaicharoen 5

Logic Circuit Design using Multiplexer Advantages q No need for logic simplification q Minimize the IC package count q Simplify the logic design 1/2550 A. Yaicharoen 6

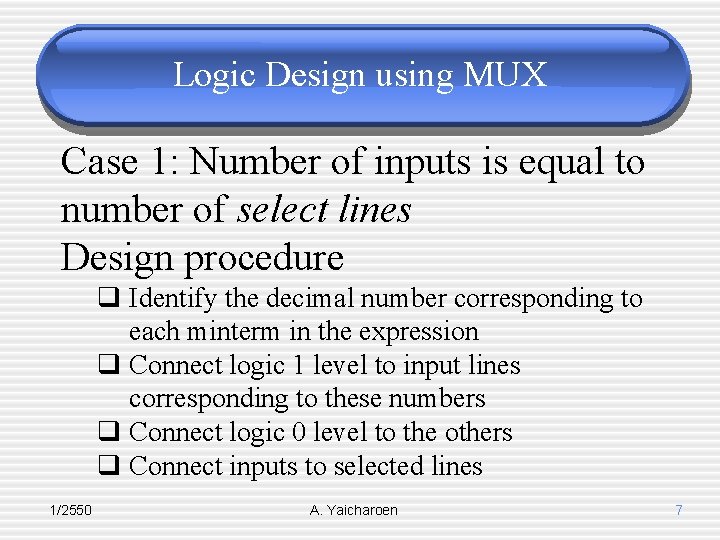

Logic Design using MUX Case 1: Number of inputs is equal to number of select lines Design procedure q Identify the decimal number corresponding to each minterm in the expression q Connect logic 1 level to input lines corresponding to these numbers q Connect logic 0 level to the others q Connect inputs to selected lines 1/2550 A. Yaicharoen 7

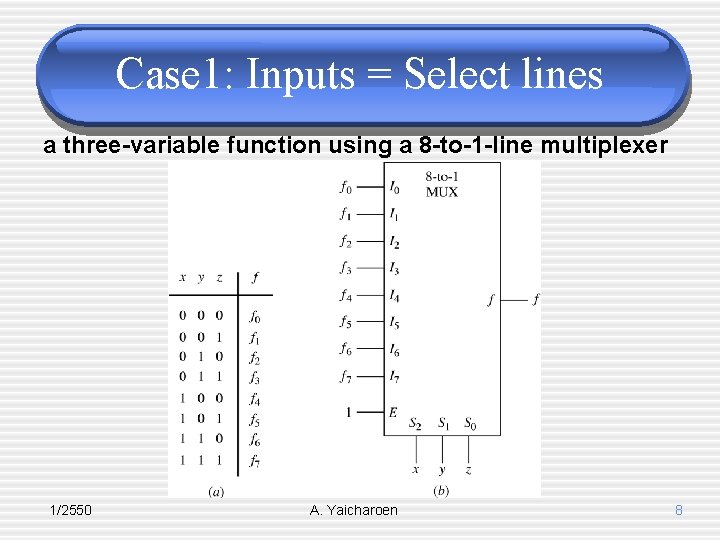

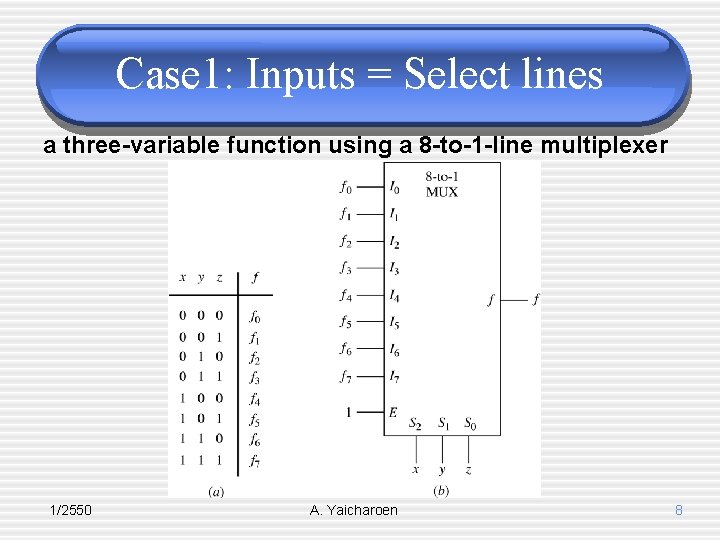

Case 1: Inputs = Select lines a three-variable function using a 8 -to-1 -line multiplexer 1/2550 A. Yaicharoen 8

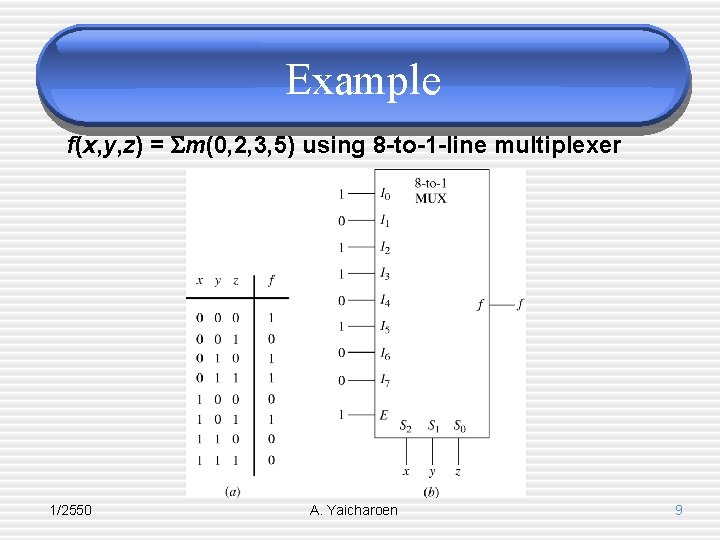

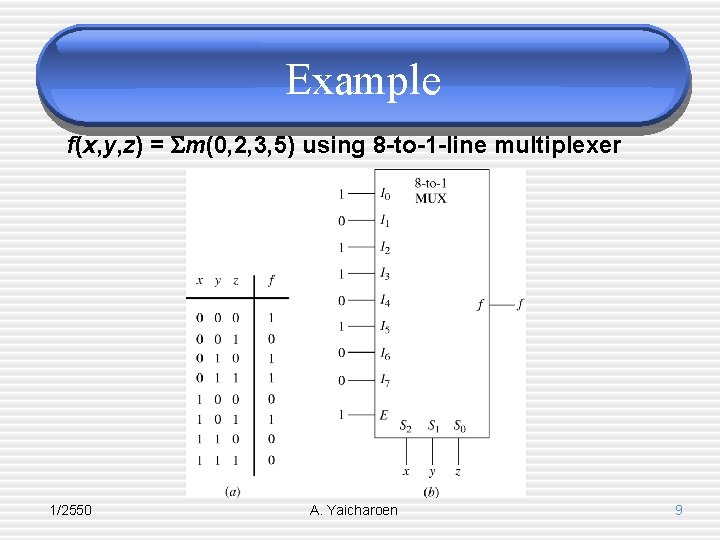

Example f(x, y, z) = m(0, 2, 3, 5) using 8 -to-1 -line multiplexer 1/2550 A. Yaicharoen 9

Logic Design using MUX Case 2: Number of inputs is higher than number of select lines Procedure 2. 1: Reduce the number of inputs to the number of select lines by • inspection • k-map 1/2550 A. Yaicharoen 10

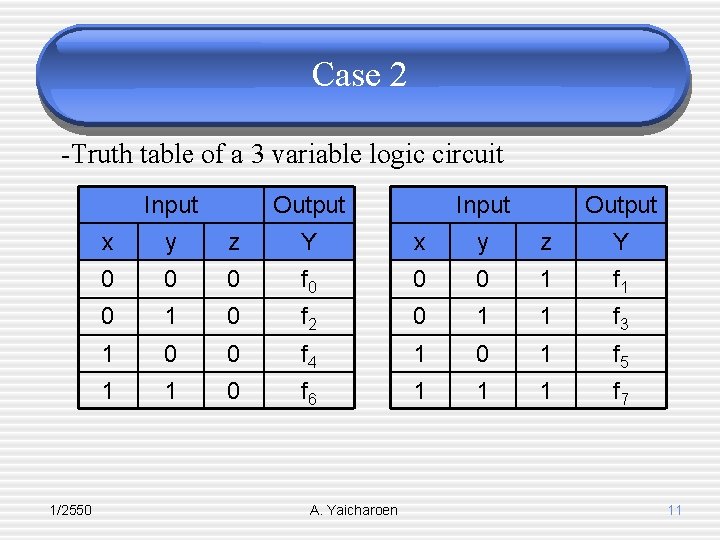

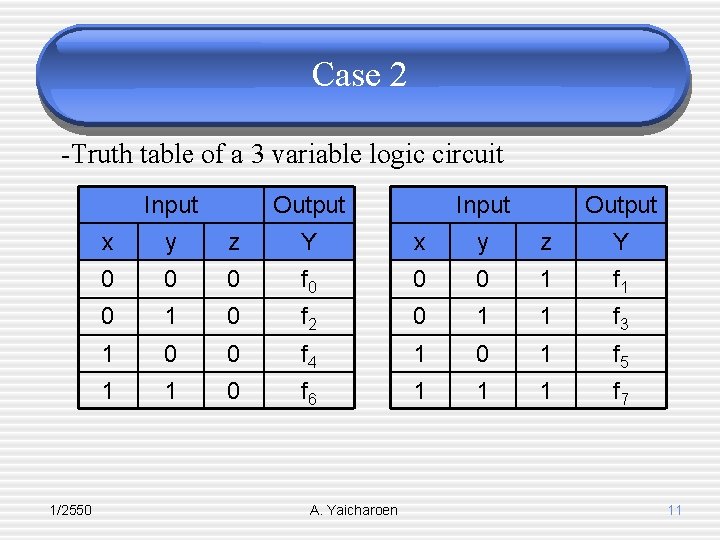

Case 2 -Truth table of a 3 variable logic circuit Input 1/2550 Output Input Output x y z Y 0 0 0 f 0 0 0 1 f 1 0 f 2 0 1 1 f 3 1 0 0 f 4 1 0 1 f 5 1 1 0 f 6 1 1 1 f 7 A. Yaicharoen 11

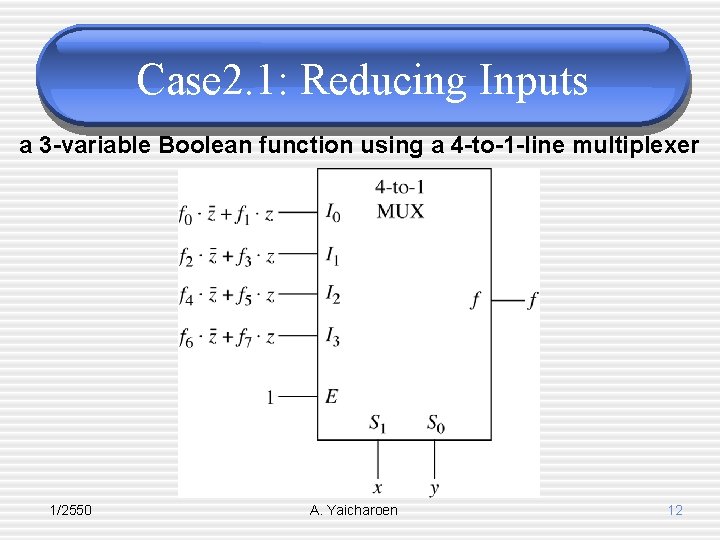

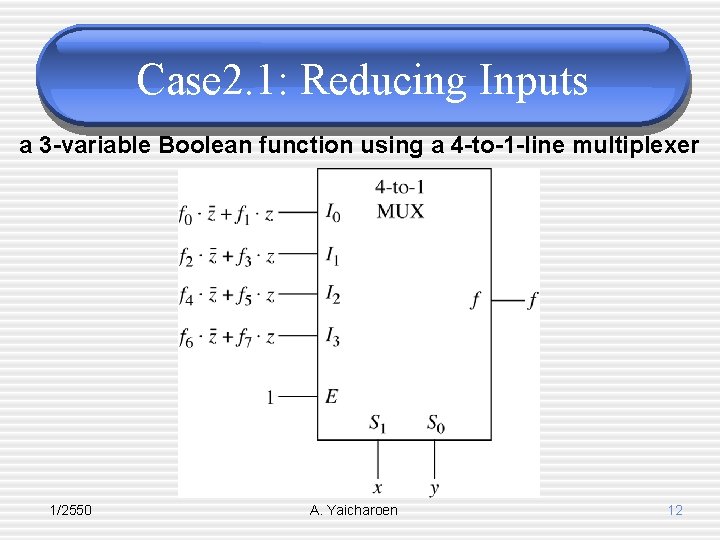

Case 2. 1: Reducing Inputs a 3 -variable Boolean function using a 4 -to-1 -line multiplexer 1/2550 A. Yaicharoen 12

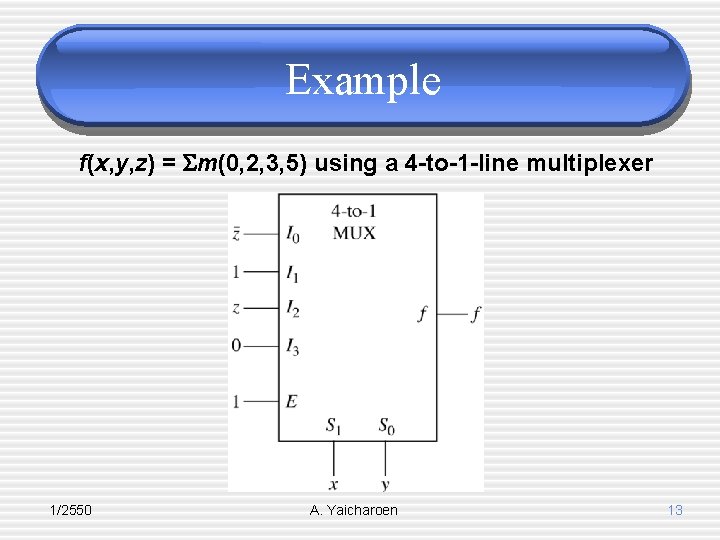

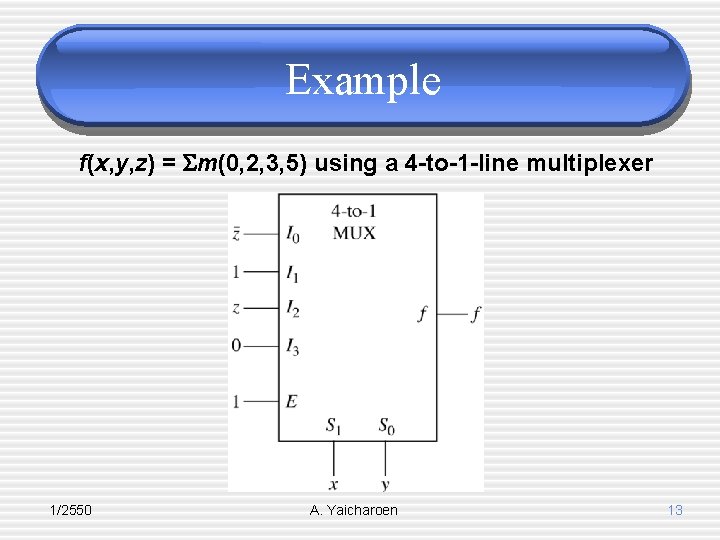

Example f(x, y, z) = m(0, 2, 3, 5) using a 4 -to-1 -line multiplexer 1/2550 A. Yaicharoen 13

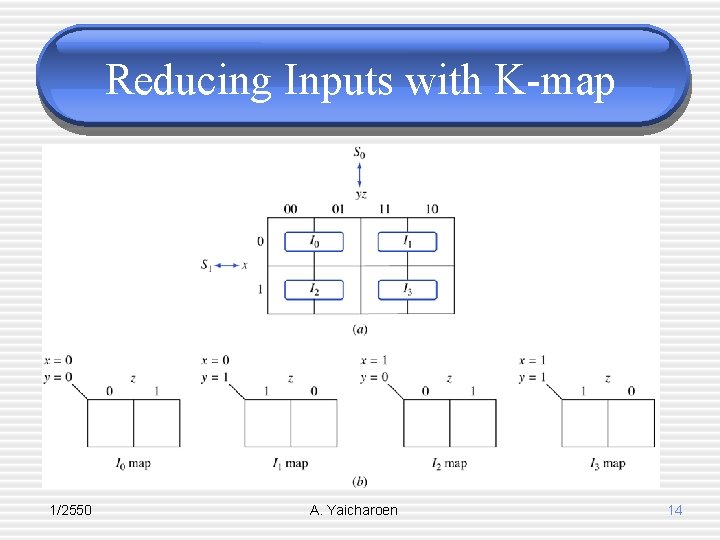

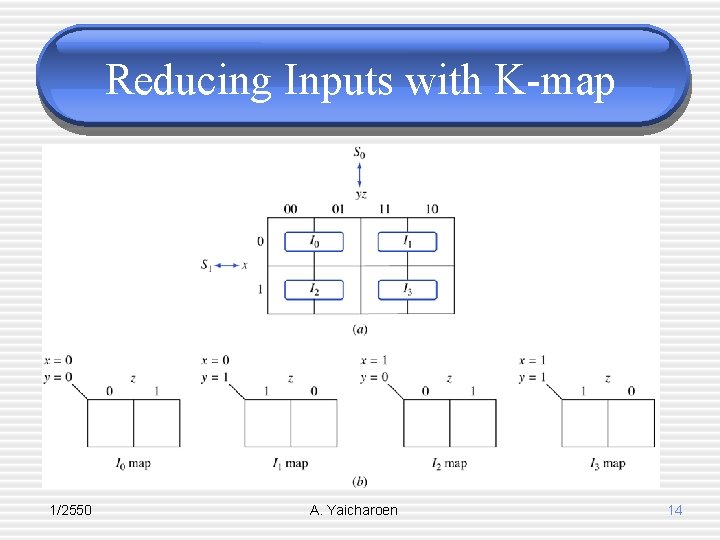

Reducing Inputs with K-map 1/2550 A. Yaicharoen 14

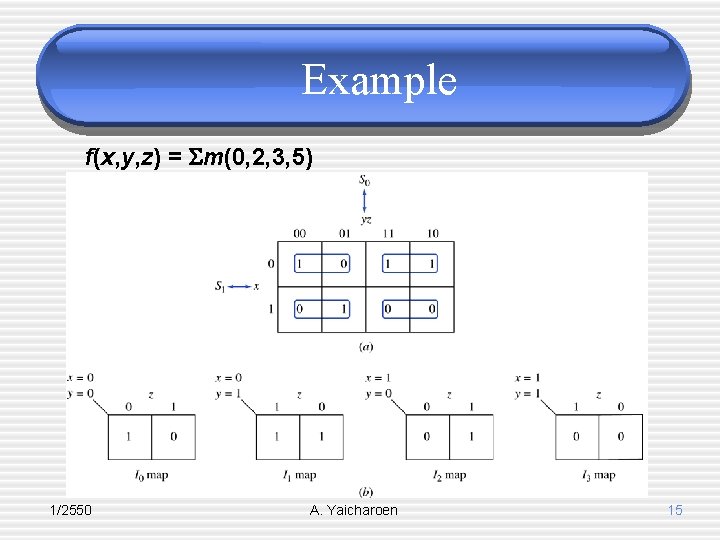

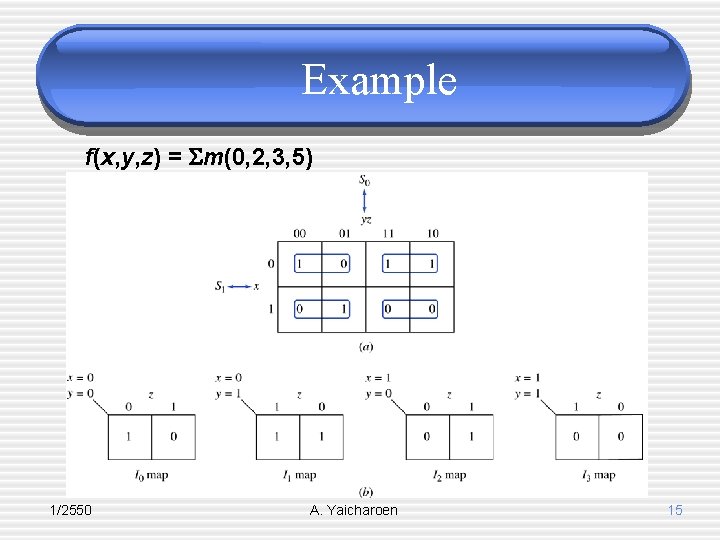

Example f(x, y, z) = m(0, 2, 3, 5) 1/2550 A. Yaicharoen 15

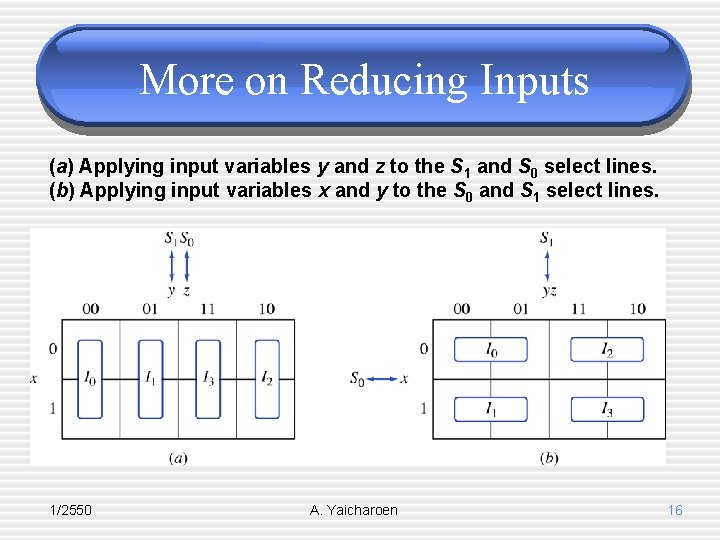

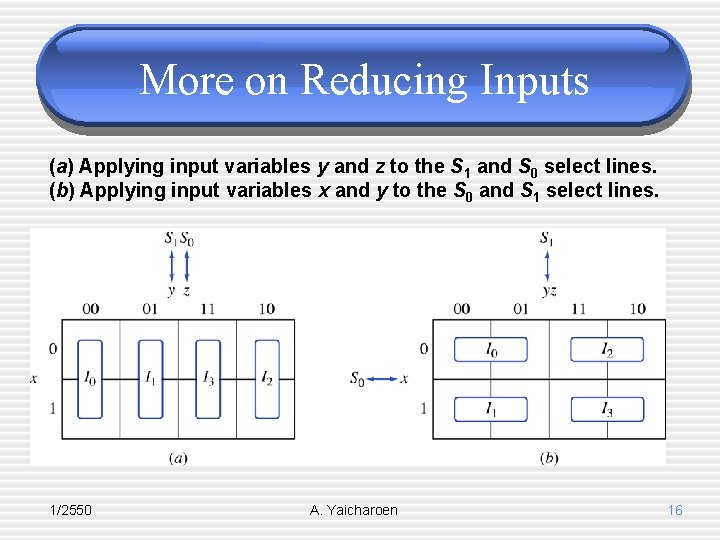

More on Reducing Inputs (a) Applying input variables y and z to the S 1 and S 0 select lines. (b) Applying input variables x and y to the S 0 and S 1 select lines. 1/2550 A. Yaicharoen 16

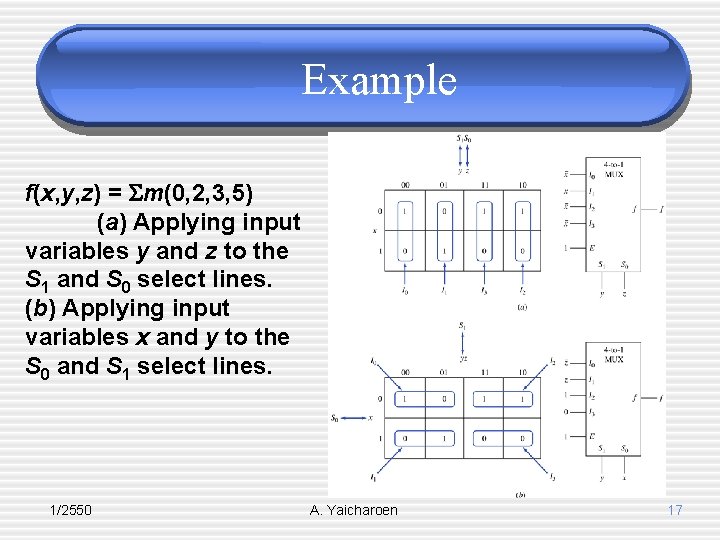

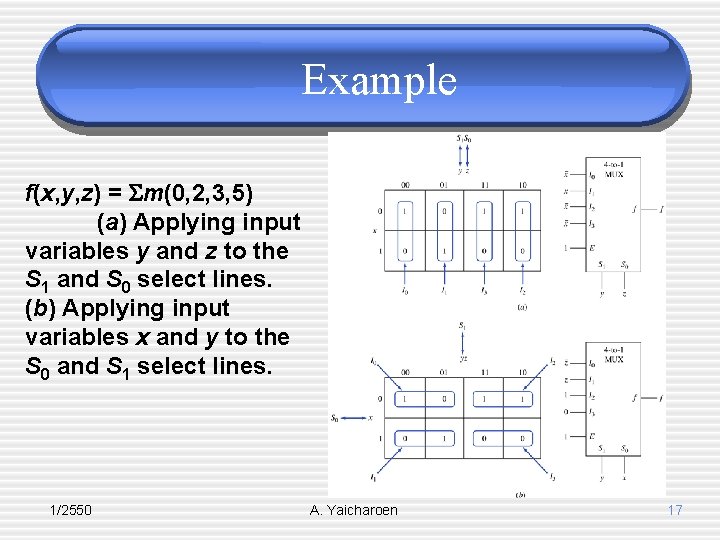

Example f(x, y, z) = m(0, 2, 3, 5) (a) Applying input variables y and z to the S 1 and S 0 select lines. (b) Applying input variables x and y to the S 0 and S 1 select lines. 1/2550 A. Yaicharoen 17

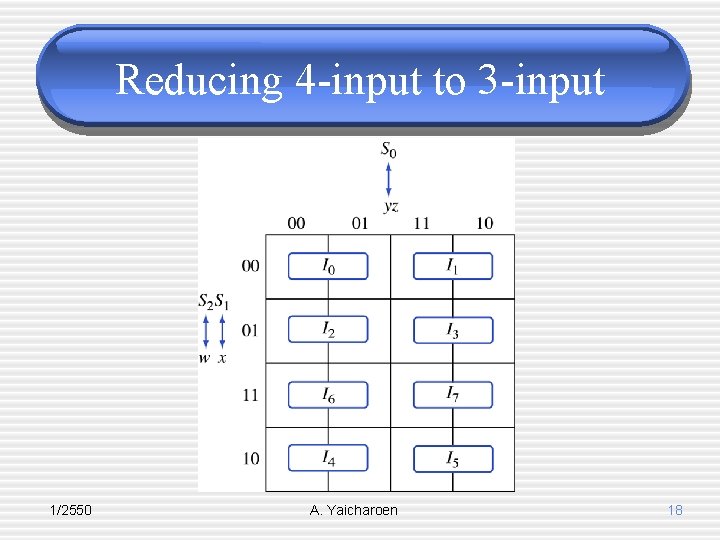

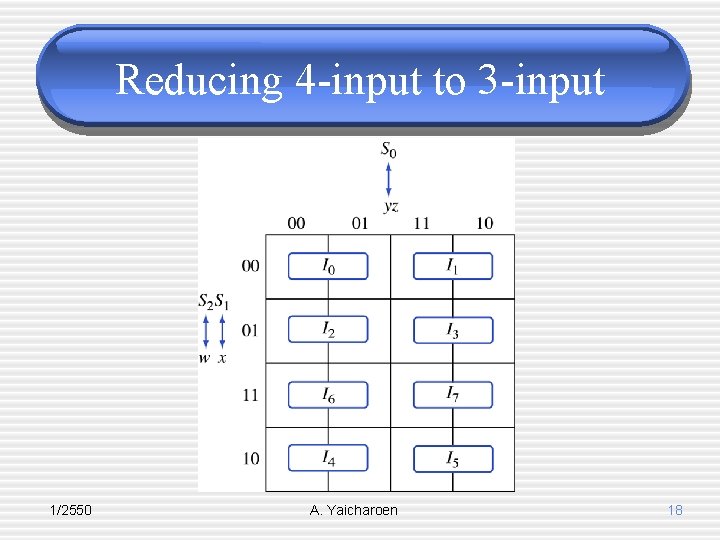

Reducing 4 -input to 3 -input 1/2550 A. Yaicharoen 18

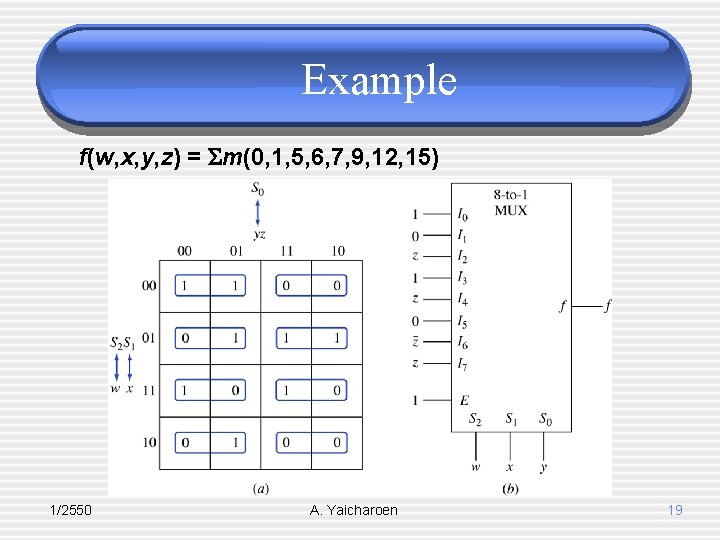

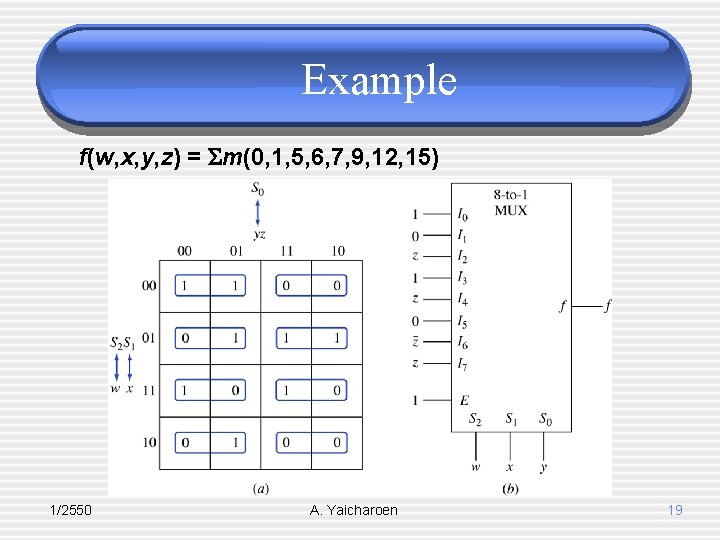

Example f(w, x, y, z) = m(0, 1, 5, 6, 7, 9, 12, 15) 1/2550 A. Yaicharoen 19

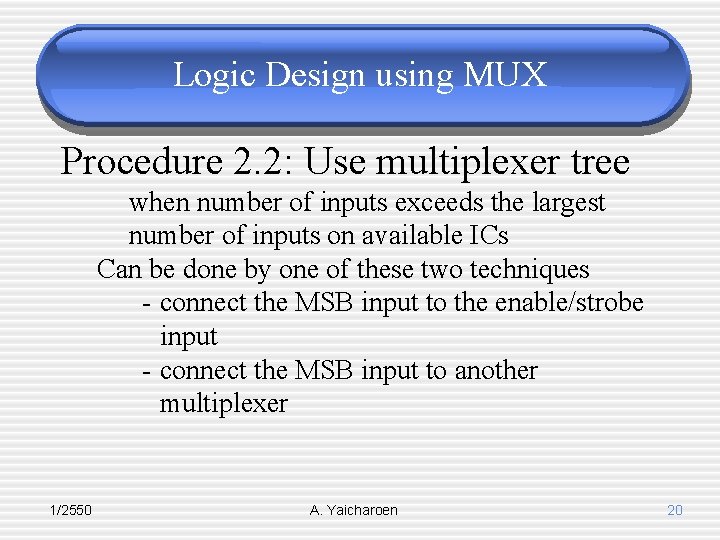

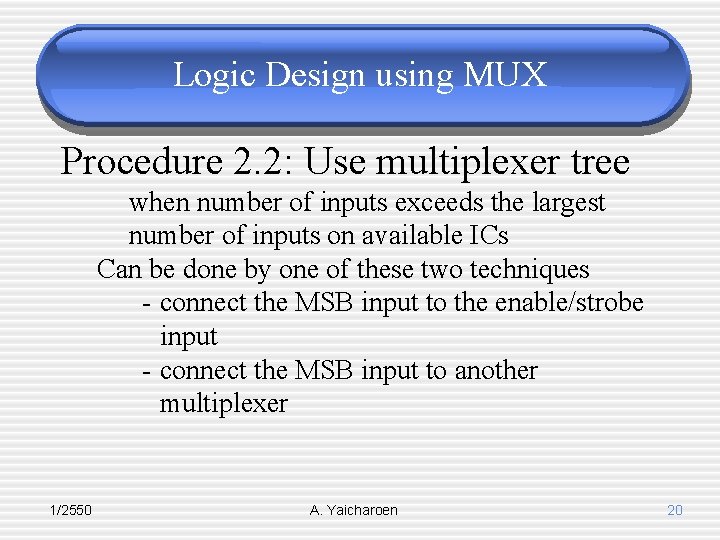

Logic Design using MUX Procedure 2. 2: Use multiplexer tree when number of inputs exceeds the largest number of inputs on available ICs Can be done by one of these two techniques - connect the MSB input to the enable/strobe input - connect the MSB input to another multiplexer 1/2550 A. Yaicharoen 20

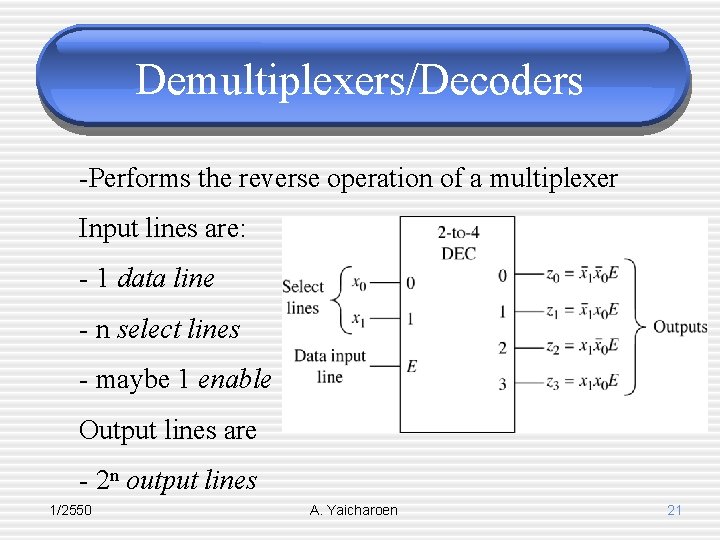

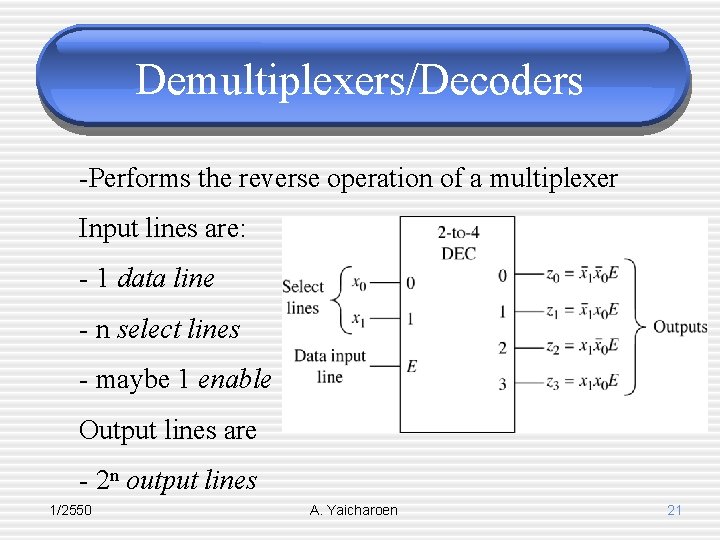

Demultiplexers/Decoders -Performs the reverse operation of a multiplexer Input lines are: - 1 data line - n select lines - maybe 1 enable Output lines are - 2 n output lines 1/2550 A. Yaicharoen 21

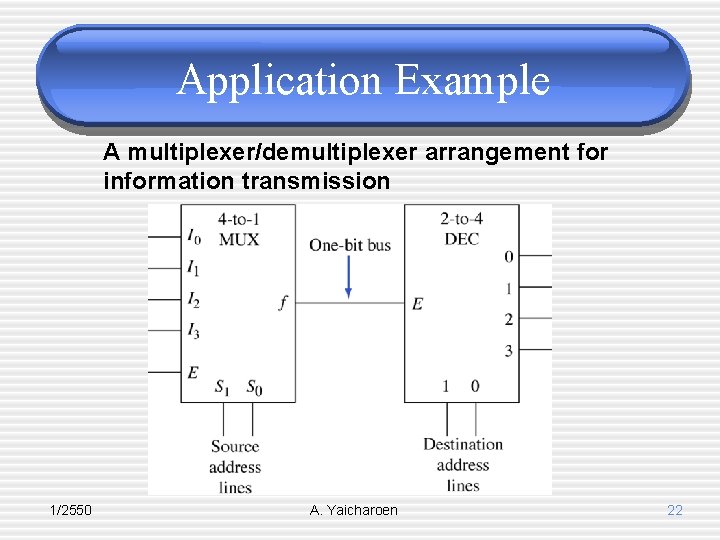

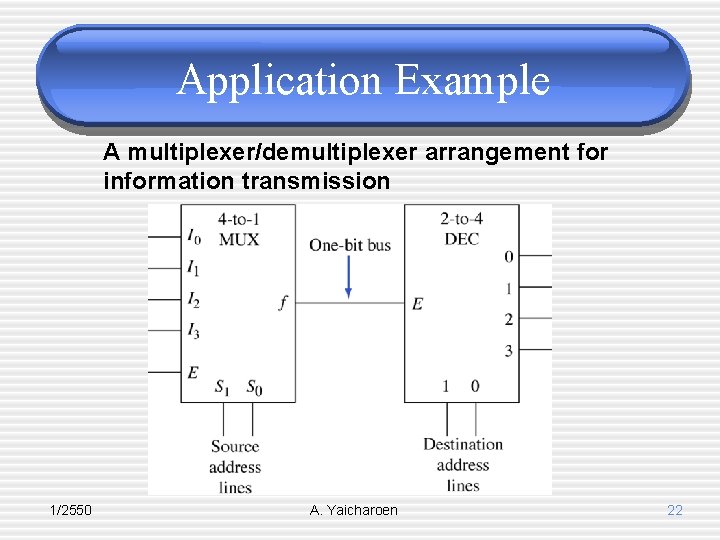

Application Example A multiplexer/demultiplexer arrangement for information transmission 1/2550 A. Yaicharoen 22

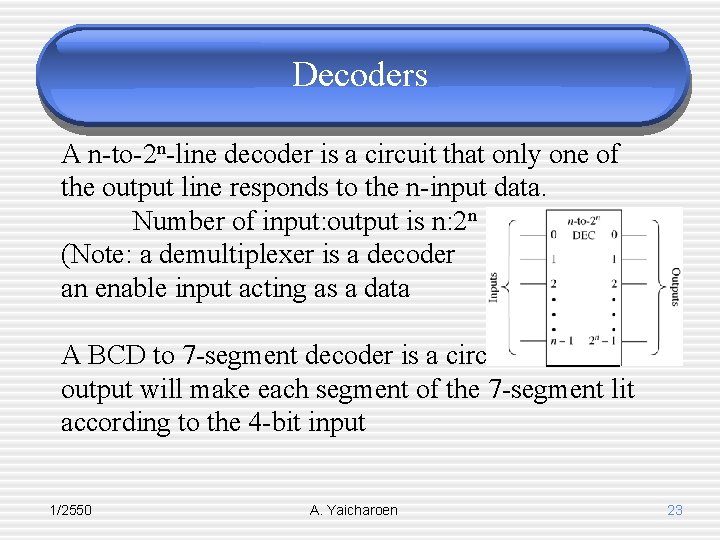

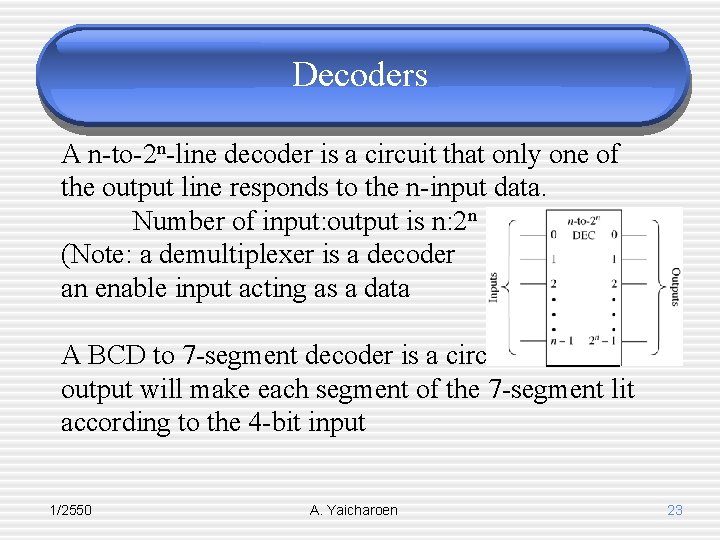

Decoders A n-to-2 n-line decoder is a circuit that only one of the output line responds to the n-input data. Number of input: output is n: 2 n (Note: a demultiplexer is a decoder with an enable input acting as a data input line A BCD to 7 -segment decoder is a circuit that 7 -bit output will make each segment of the 7 -segment lit according to the 4 -bit input 1/2550 A. Yaicharoen 23

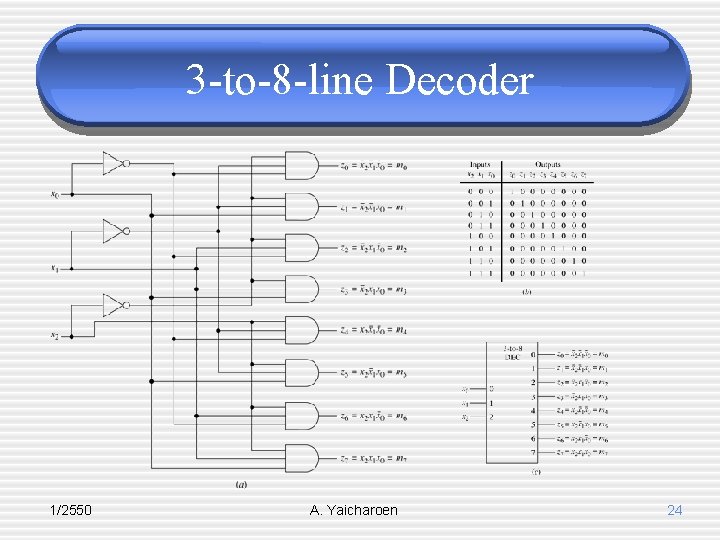

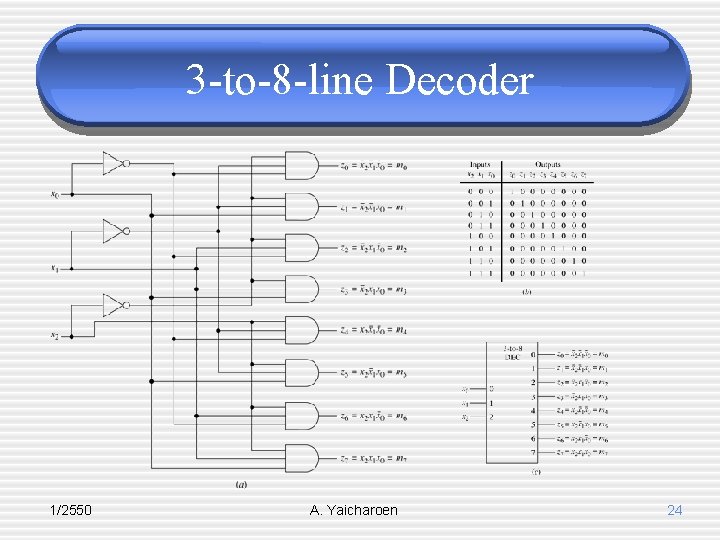

3 -to-8 -line Decoder 1/2550 A. Yaicharoen 24

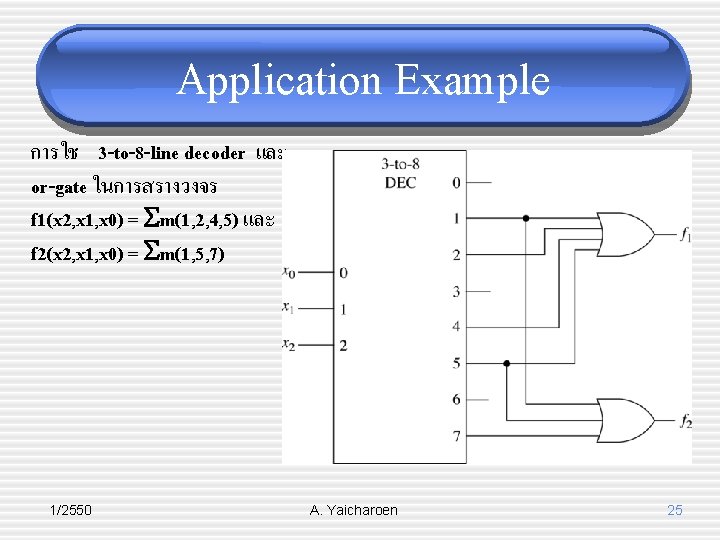

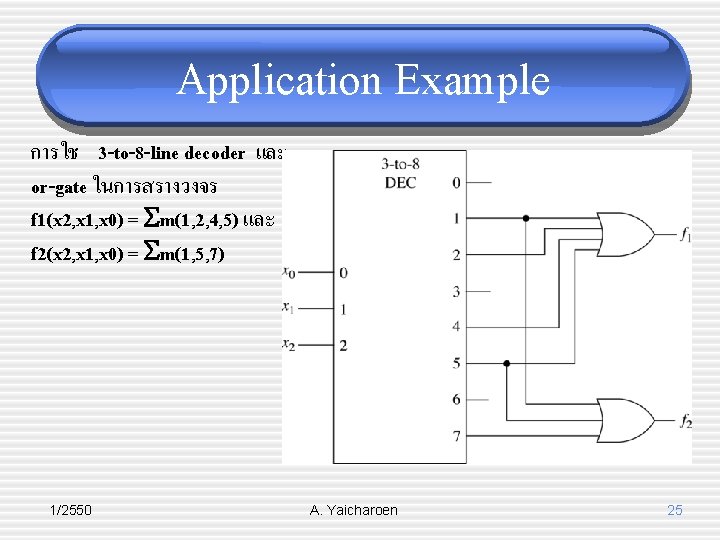

Application Example การใช 3 -to-8 -line decoder และ or-gate ในการสรางวงจร f 1(x 2, x 1, x 0) = m(1, 2, 4, 5) และ f 2(x 2, x 1, x 0) = m(1, 5, 7) 1/2550 A. Yaicharoen 25

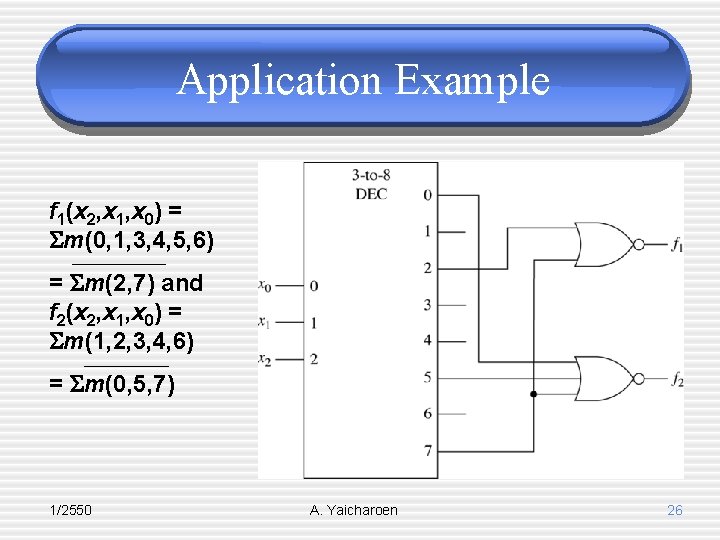

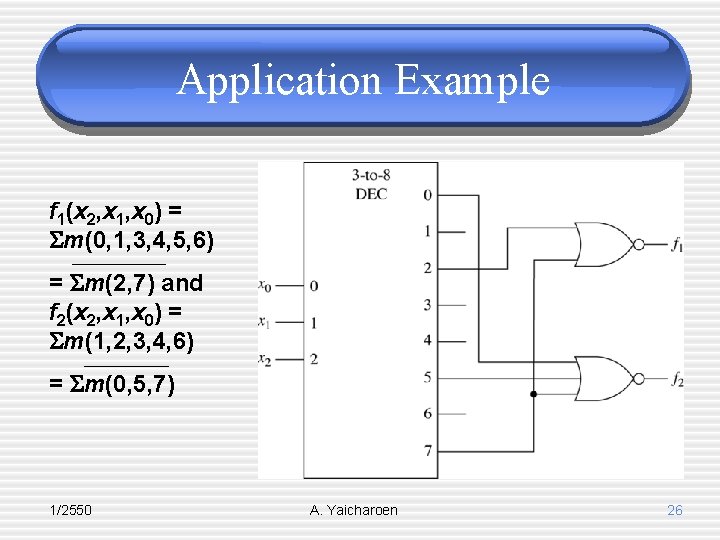

Application Example f 1(x 2, x 1, x 0) = m(0, 1, 3, 4, 5, 6) = m(2, 7) and f 2(x 2, x 1, x 0) = m(1, 2, 3, 4, 6) = m(0, 5, 7) 1/2550 A. Yaicharoen 26

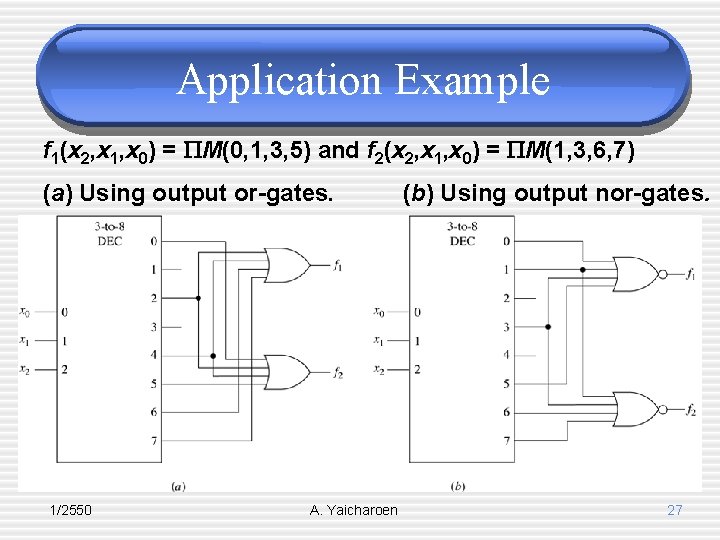

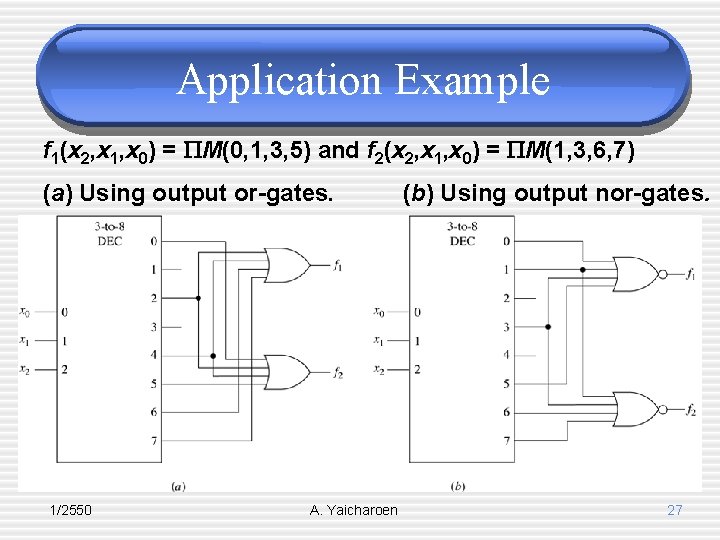

Application Example f 1(x 2, x 1, x 0) = M(0, 1, 3, 5) and f 2(x 2, x 1, x 0) = M(1, 3, 6, 7) (a) Using output or-gates. 1/2550 A. Yaicharoen (b) Using output nor-gates. 27

3 -to-8 -line decoder using nand-gates 1/2550 A. Yaicharoen 28

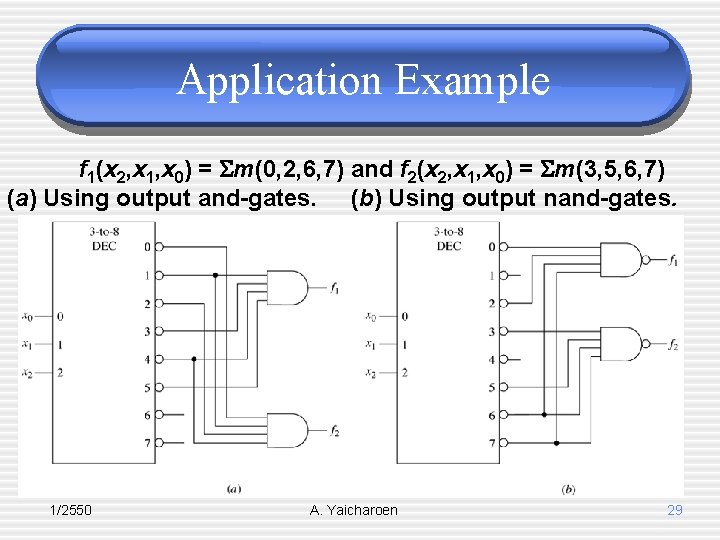

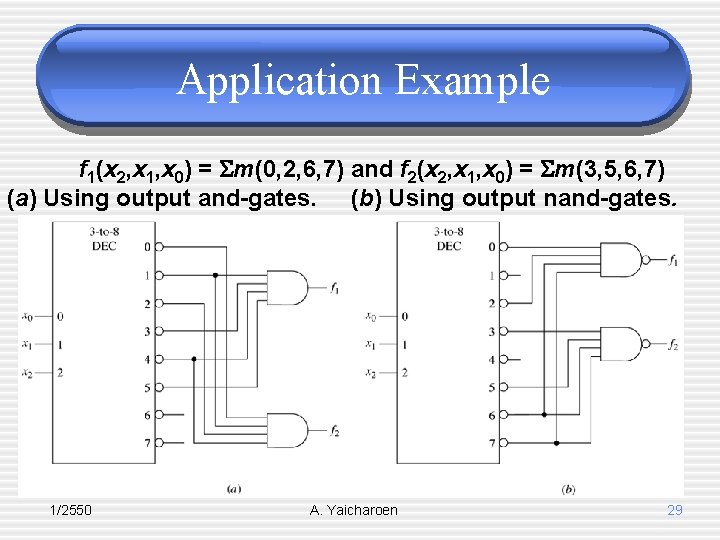

Application Example f 1(x 2, x 1, x 0) = m(0, 2, 6, 7) and f 2(x 2, x 1, x 0) = m(3, 5, 6, 7) (a) Using output and-gates. (b) Using output nand-gates. 1/2550 A. Yaicharoen 29

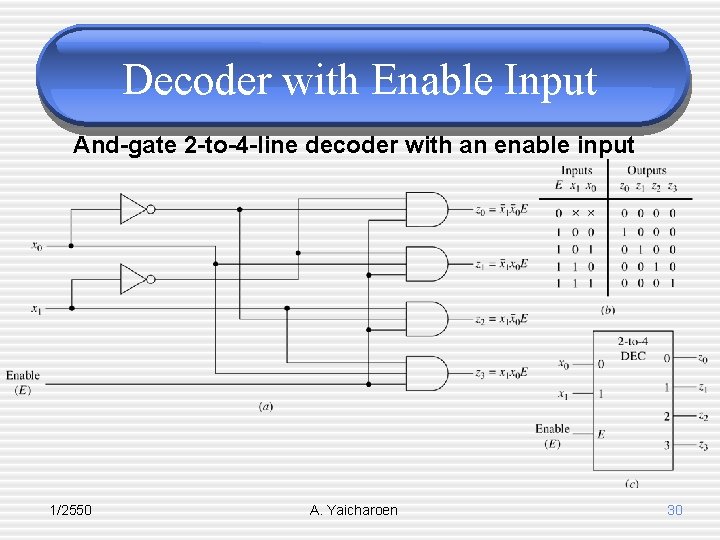

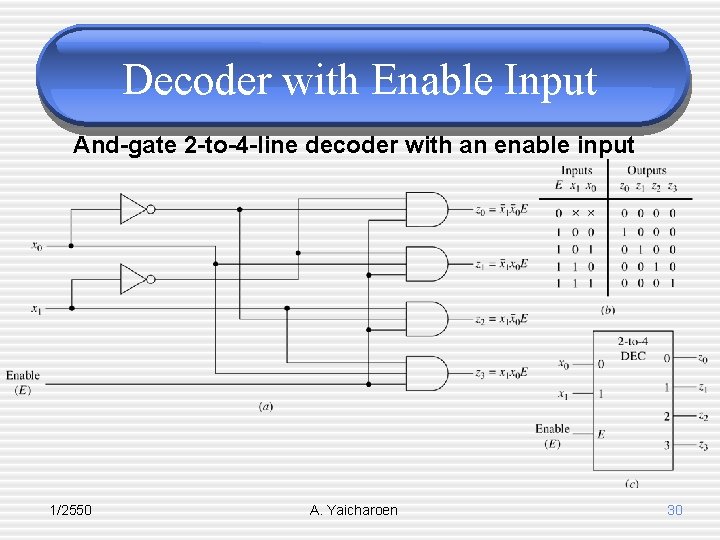

Decoder with Enable Input And-gate 2 -to-4 -line decoder with an enable input 1/2550 A. Yaicharoen 30

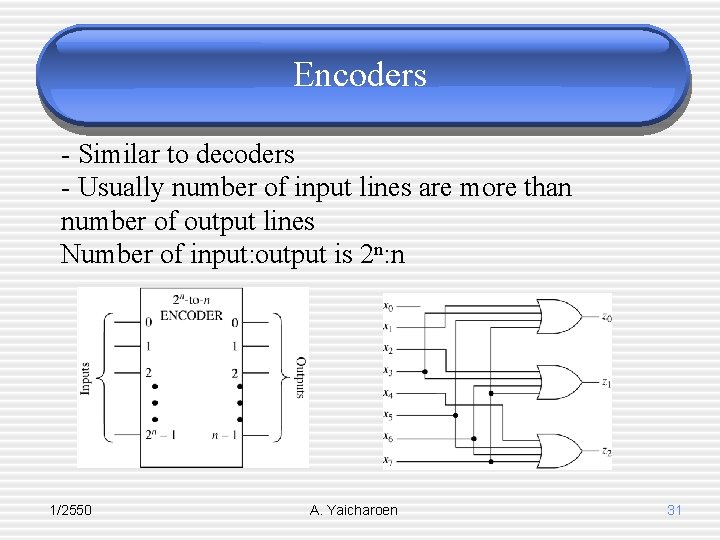

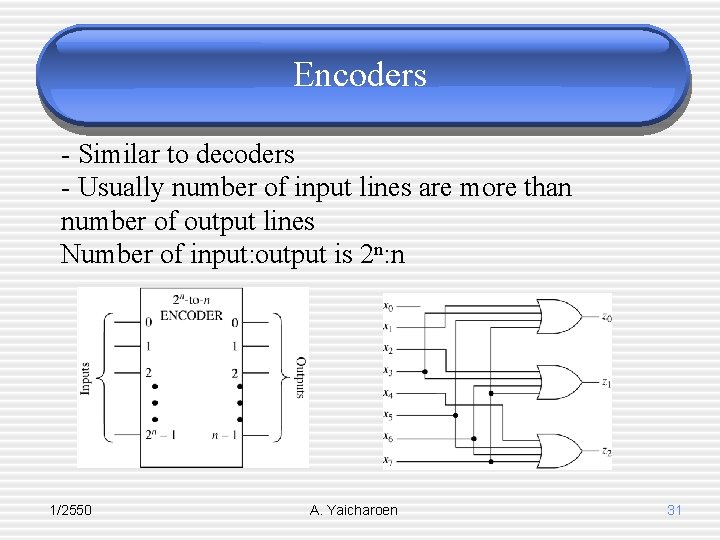

Encoders - Similar to decoders - Usually number of input lines are more than number of output lines Number of input: output is 2 n: n 1/2550 A. Yaicharoen 31

Binary Adders Binary Half-Adder 1/2550 Binary Full-Adder A. Yaicharoen 32

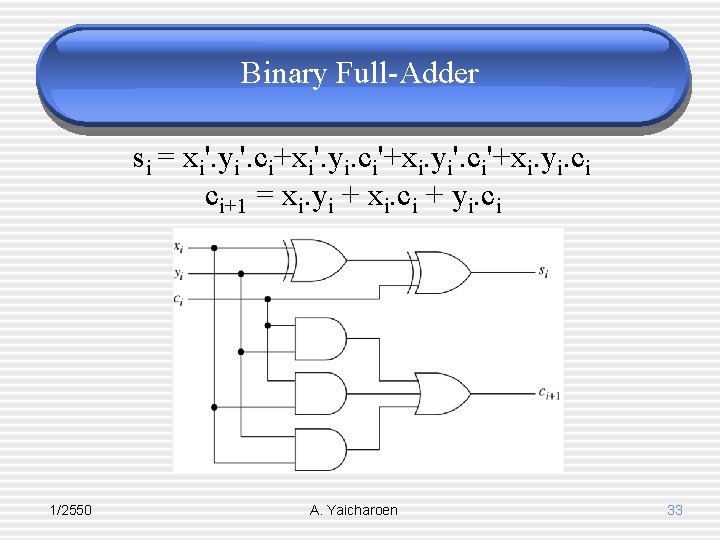

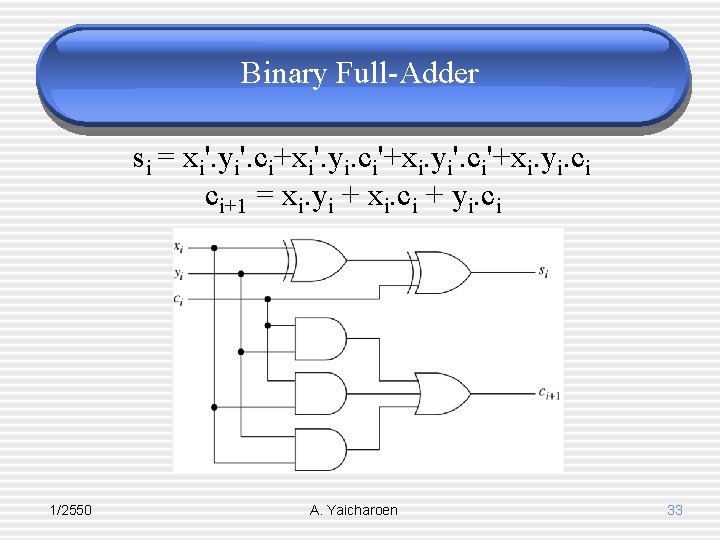

Binary Full-Adder si = xi'. yi'. ci+xi'. yi. ci'+xi. yi'. ci'+xi. yi. ci ci+1 = xi. yi + xi. ci + yi. ci 1/2550 A. Yaicharoen 33

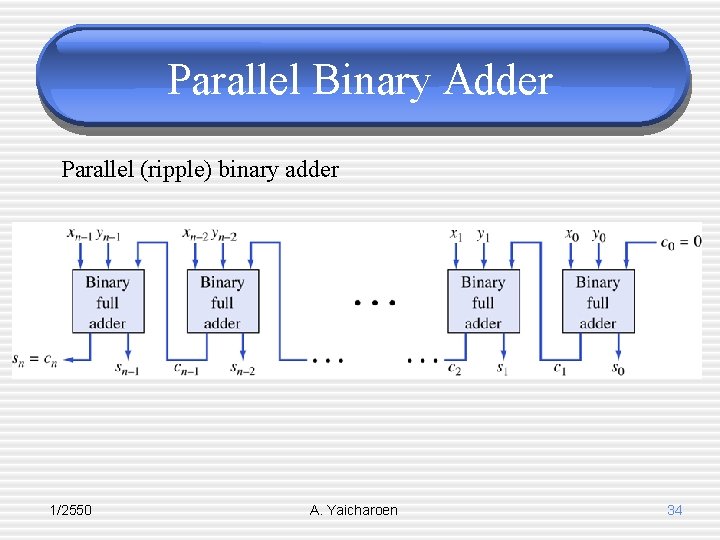

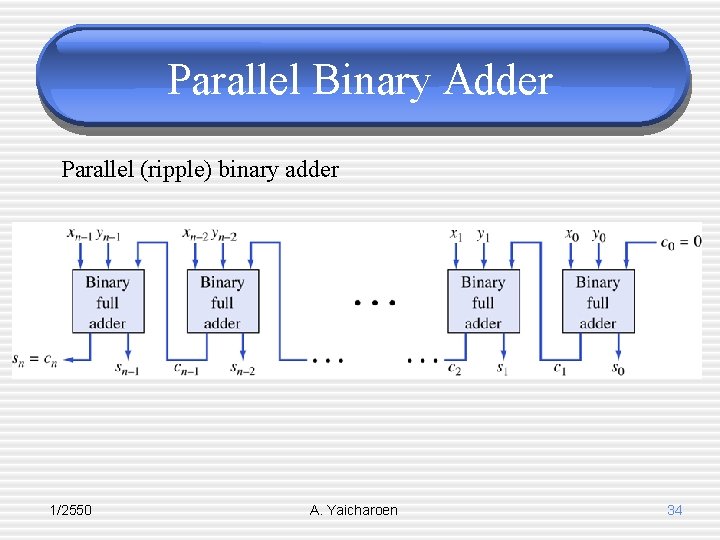

Parallel Binary Adder Parallel (ripple) binary adder 1/2550 A. Yaicharoen 34

Binary Subtractor Binary Half-Subtractor 1/2550 A. Yaicharoen Binary Full-Subtractor 35

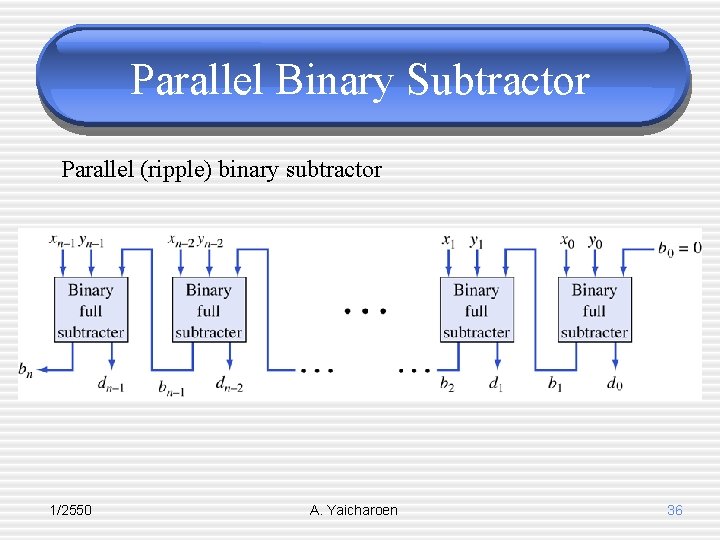

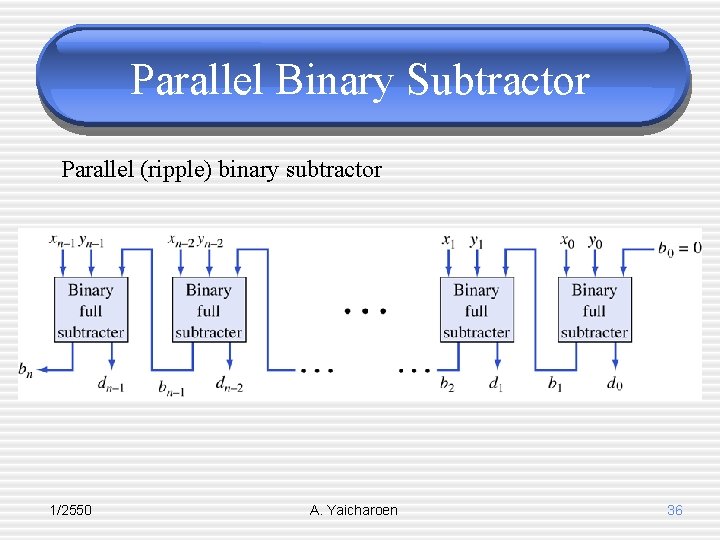

Parallel Binary Subtractor Parallel (ripple) binary subtractor 1/2550 A. Yaicharoen 36

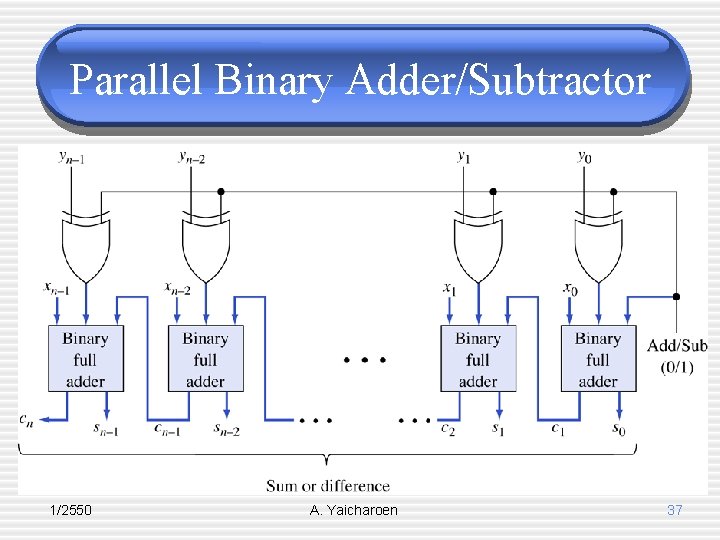

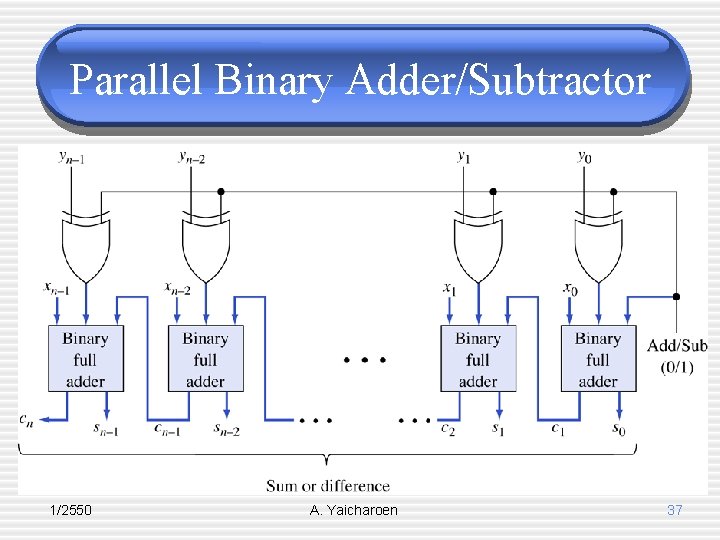

Parallel Binary Adder/Subtractor 1/2550 A. Yaicharoen 37

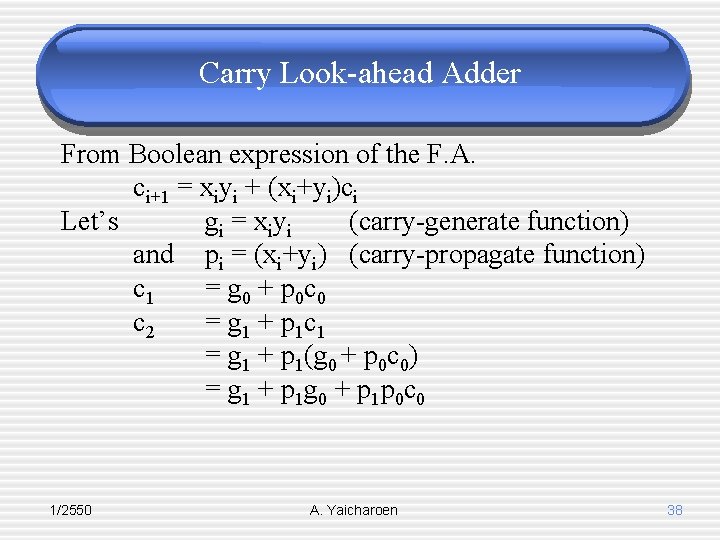

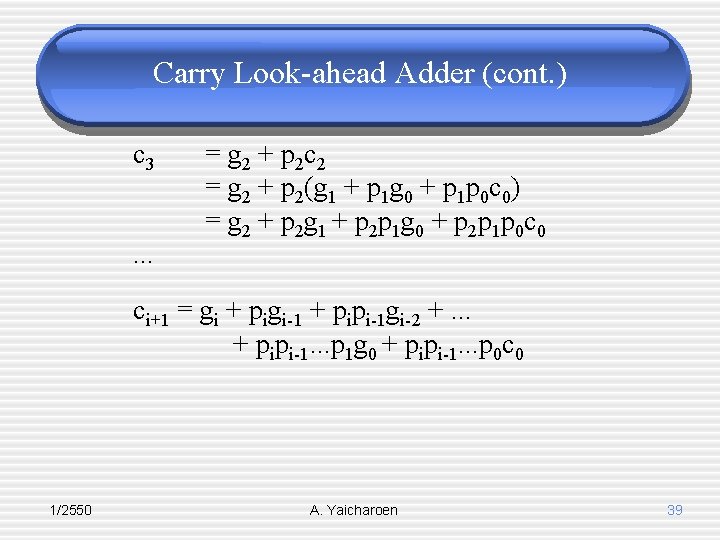

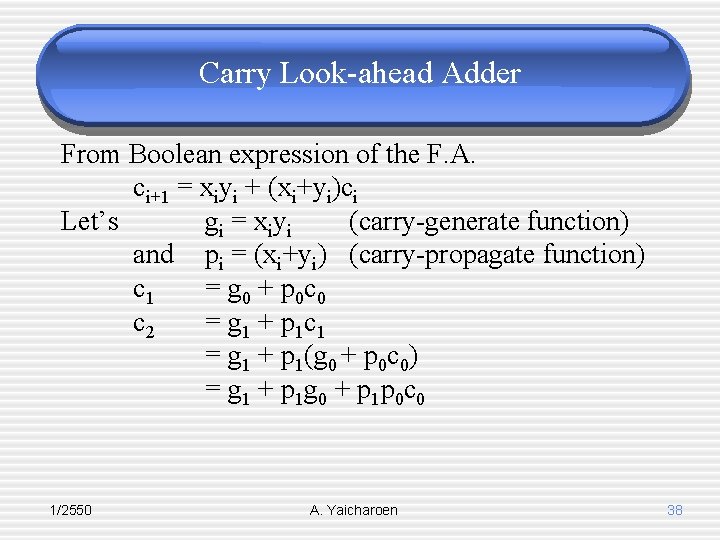

Carry Look-ahead Adder From Boolean expression of the F. A. ci+1 = xiyi + (xi+yi)ci Let’s gi = xiyi (carry-generate function) and pi = (xi+yi) (carry-propagate function) c 1 = g 0 + p 0 c 0 c 2 = g 1 + p 1 c 1 = g 1 + p 1(g 0 + p 0 c 0) = g 1 + p 1 g 0 + p 1 p 0 c 0 1/2550 A. Yaicharoen 38

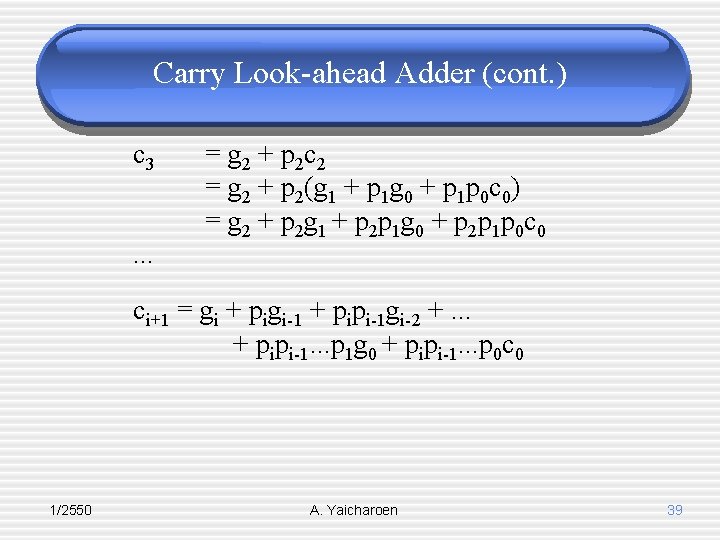

Carry Look-ahead Adder (cont. ) c 3. . . = g 2 + p 2 c 2 = g 2 + p 2(g 1 + p 1 g 0 + p 1 p 0 c 0) = g 2 + p 2 g 1 + p 2 p 1 g 0 + p 2 p 1 p 0 c 0 ci+1 = gi + pigi-1 + pipi-1 gi-2 +. . . + pipi-1. . . p 1 g 0 + pipi-1. . . p 0 c 0 1/2550 A. Yaicharoen 39

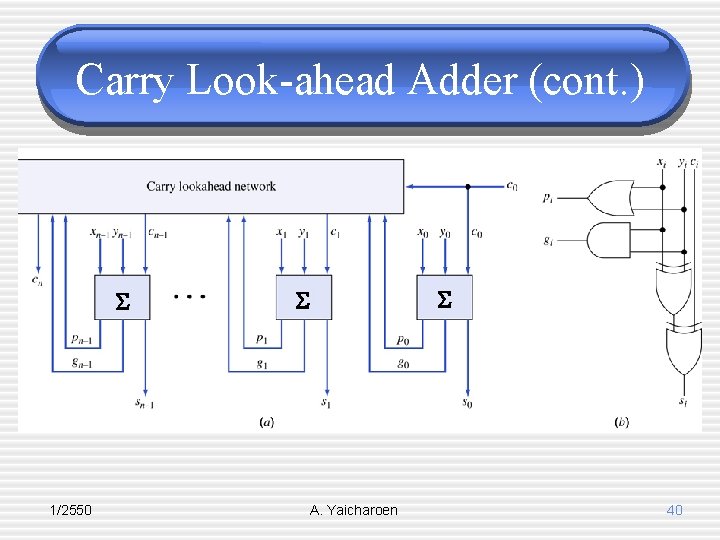

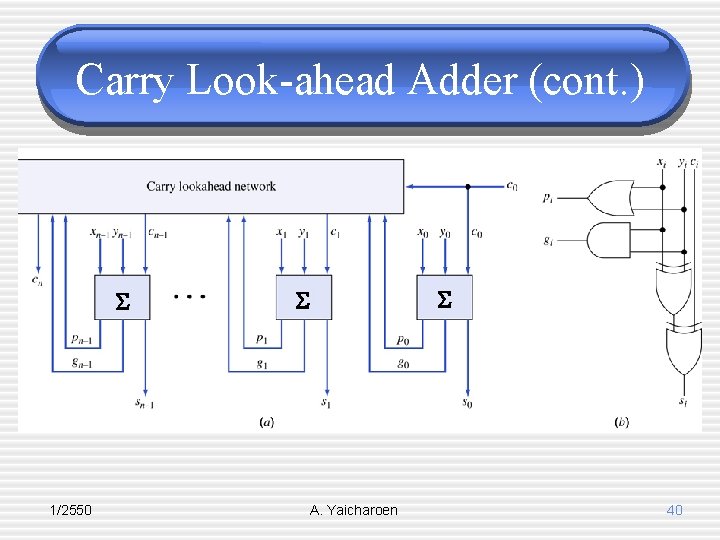

Carry Look-ahead Adder (cont. ) 1/2550 A. Yaicharoen 40

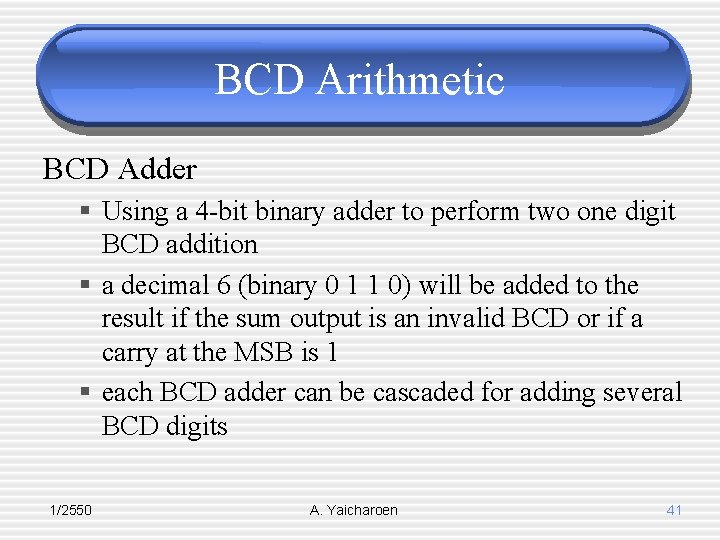

BCD Arithmetic BCD Adder § Using a 4 -bit binary adder to perform two one digit BCD addition § a decimal 6 (binary 0 1 1 0) will be added to the result if the sum output is an invalid BCD or if a carry at the MSB is 1 § each BCD adder can be cascaded for adding several BCD digits 1/2550 A. Yaicharoen 41

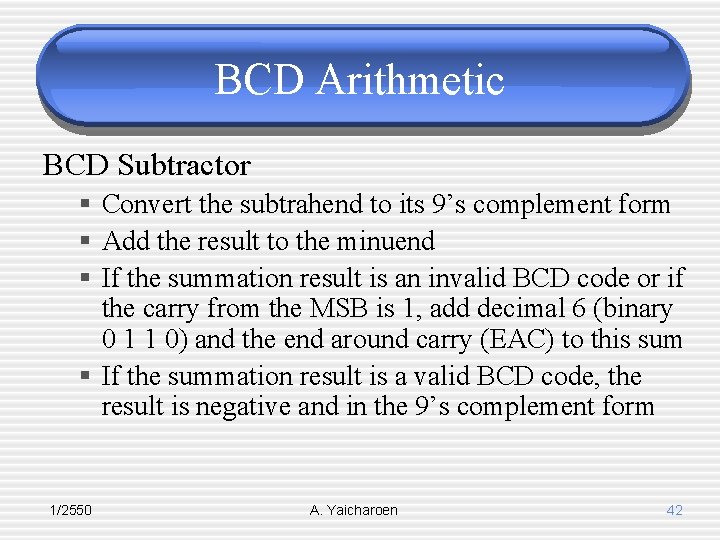

BCD Arithmetic BCD Subtractor § Convert the subtrahend to its 9’s complement form § Add the result to the minuend § If the summation result is an invalid BCD code or if the carry from the MSB is 1, add decimal 6 (binary 0 1 1 0) and the end around carry (EAC) to this sum § If the summation result is a valid BCD code, the result is negative and in the 9’s complement form 1/2550 A. Yaicharoen 42

Nine’s Complementer Circuit A 9’s complementer circuit is § a circuit designed to convert a decimal digit (in BCD code) to its 9’s complement § created by adding binary 1 0 to the 1’s complement of the number (ignore the carry) (Proof is left as a student exercise) 1/2550 A. Yaicharoen 43

Arithmetic Logic Unit (ALU) • performs arithmetic and logic operations • (depends on the selected mode) Read details and example in section 6. 6 1/2550 A. Yaicharoen 44

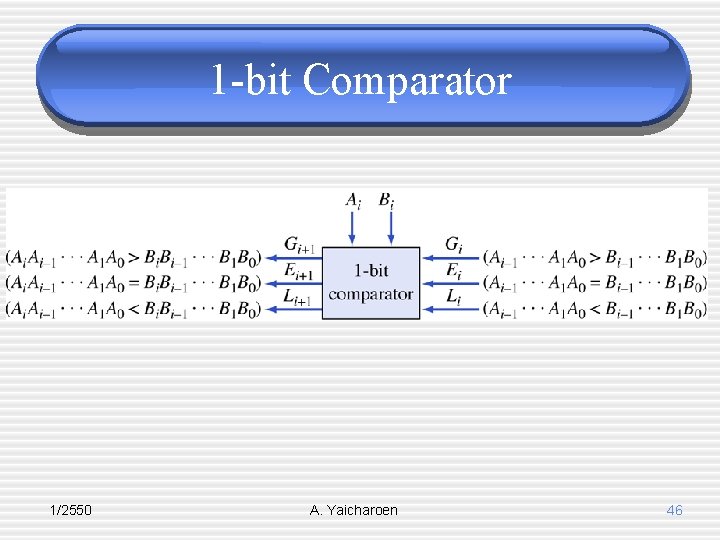

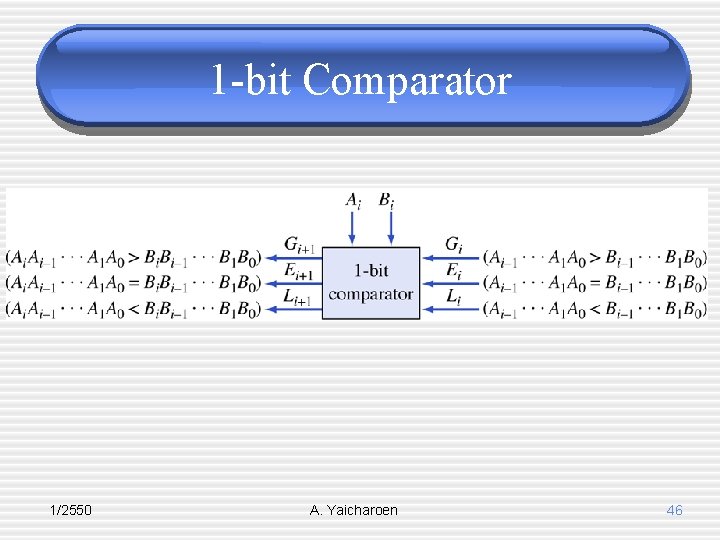

Comparators A comparator is a circuit that compares the magnitudes of two binary numbers Input: Ai, Bi, Gi, Ei, Li Gi= 1 when Ai-1 Ai-2. . . A 1 A 0 > Bi-1 Bi-2. . . B 1 B 0 Ei= 1 when Ai-1 Ai-2. . . A 1 A 0 = Bi-1 Bi-2. . . B 1 B 0 Li= 1 when Ai-1 Ai-2. . . A 1 A 0 < Bi-1 Bi-2. . . B 1 B 0 Output: Gi+1, Ei+1, Li+1 Gi+1= 1 when Ai. Ai-1. . . A 1 A 0 > Bi. Bi-1. . . B 1 B 0 Ei+1= 1 when Ai. Ai-1. . . A 1 A 0 = Bi. Bi-1. . . B 1 B 0 Li+1= 1 when Ai. Ai-1. . . A 1 A 0 < Bi. Bi-1. . . B 1 B 0 1/2550 A. Yaicharoen 45

1 -bit Comparator 1/2550 A. Yaicharoen 46

Other MSI Circuits • Parity generators/checkers • Code converters § BCD-to-binary converter § Binary-to-BCD converter • Priority encoders § Decimal-to-BCD encoder § Octal-to-binary Encoder • Decoder/drivers for display devices § BCD-to-decimal decoder/driver § BCD-to-7 -segment decoder/driver 1/2550 A. Yaicharoen 47