EEL 4712 Digital Design Instructor l Farimah Farahmandi

- Slides: 18

EEL 4712 Digital Design

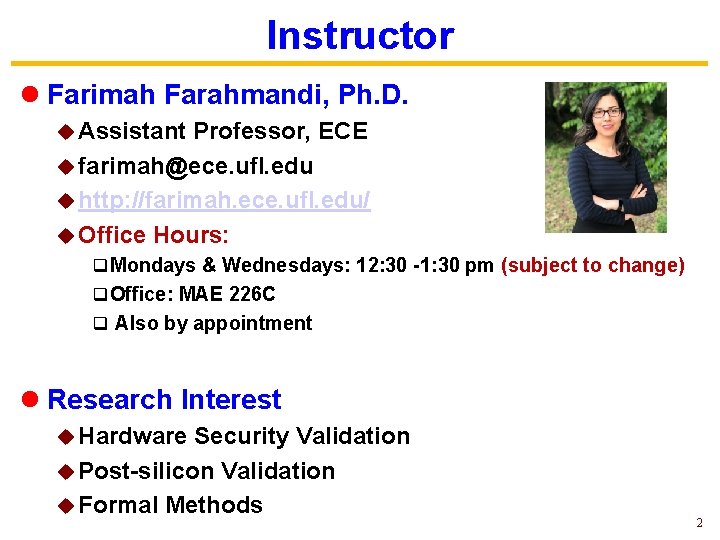

Instructor l Farimah Farahmandi, Ph. D. u Assistant Professor, ECE u farimah@ece. ufl. edu u http: //farimah. ece. ufl. edu/ u Office Hours: q Mondays & Wednesdays: 12: 30 -1: 30 pm (subject to change) q Office: MAE 226 C q Also by appointment l Research Interest u Hardware Security Validation u Post-silicon Validation u Formal Methods 2

Teaching Assistants l Jonathan Cruz, Ph. D. Student u Email: jonc 205@ufl. edu u Office hours: Wed & Thu: 9: 00 -10: 00 am u Room: NEB 288 l Muhtadi (Zaki) Choudhury, Ph. D. Student muhtadichoudhury@ufl. edu u Email: u Office hours: Tue & Fri: 2: 00 -3: 00 pm u Room: NEB 288 l John Kearney, Undergraduate Student u Email: jkearney@ufl. edu u Office hours: Mon & Fri: 9: 00 -10: 00 am u Room: NEB 288 3

Teaching Assistants l Carlos Matos, Undergraduate Student carlosm 04@ufl. edu u Email: u Office hours: Tue 1: 00 -2: 00 pm & Thu 5: 00 -6: 00 pm u Room: NEB 288 l Arvind Shankar, Undergraduate Student arvind. shankar@ufl. edu u Email: u Office hours: Wed & Tue: 3: 00 -4: 00 pm u Room: NEB 288 4

Lecture and Lab Sessions l Course Page u http: //farimah. ece. ufl. edu/teaching/eel 4712/ q Visit regularly for updates and announcements u Canvas E-learning q http: //elearning. ufl. edu/ q Login with Gator. Link account l Lectures u Mon/Wed/Fri 10: 40 – 11: 30 am LAR 310 l Lab Sessions Mon, Period E 2 - E 3 (8: 20 PM - 10: 10 PM) (John) Tue, Period 9 - 10 (4: 05 PM - 6: 00 PM) (Carlos) Wed, Period 9 - 10 (4: 05 PM - 6: 00 PM) (Arvind) Thu, Period 11 - E 1 (6: 15 PM - 8: 10 PM) (Arvind) Thu, Period E 2 - E 3 (8: 20 PM - 10: 10 PM) (John) Fri, Period 6 - 7 (12: 50 PM - 2: 45 PM) (John) Fri, Period 8 - 9 (3: 00 PM - 4: 55 PM) (Carlos) 5

Prerequisite l EEL 3701 l Requires basic knowledge of: u Boolean logic u Sequential and combinational components u Logic minimization u State machines u Assembly programming l Assumes basic knowledge of VHDL l Please check with the instructor if you do not have the required pre-requisite 6

Lab Assignments l Linked off main website/Canvas l Provide practical applications of concepts covered in lectures l All labs will use DE 10 -Lite FPGA board u http: //www. terasic. com. tw/cgi- bin/page/archive. pl? Language=English&No=1021 u Altera MAX 10 FPGA l Each lab (after lab 0) will have a pre-lab assignment and an in-lab assignment u Some may have a post-lab assignment u See each lab for submission instructions l Lab quizzes u Will test basic understanding of concepts 7

Lab Assignments l Labs will require effort outside of lab u Pre-lab assignments will be due at the beginning of q Lab 0 will be posted on website soon. Start immediately. lab l Labs will be VHDL intensive u Spend time outside of lab exercises practicing l Altera Quartus Prime u Download free version (lite edition) q https: //dl. altera. com/? edition=lite q You only need MAX 10 FPGA device support q 15. 1. 2 definitely supports board, not sure about later versions u Do tutorials in appendix of the book! l Labs will also use Digilent Analog Discovery u https: //mil. ufl. edu/3701/dad-nad. html u Logic analyzer for debugging outside of lab 8

Reading Material l Textbook: u Brown, S. D. and Vranesic, Z. G. , "Fundamentals of Digital Logic with VHDL Design", Second or Third Edition, Mc. Graw-Hill l Recommended Textbooks: u Katz, Randy, and Gaetano Borriello. Contemporary Logic Design. 2 nd Edition, Upper Saddle River, NJ: Pearson Prentice Hall, Inc u Digital Design Principles and Practices, John Wakerly, 5 th Edition, Pearson l Supplemented materials u Will also post slides when used 9

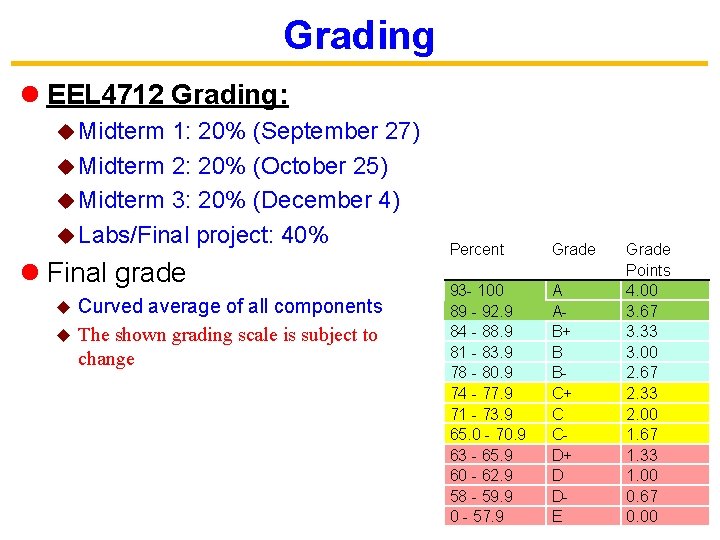

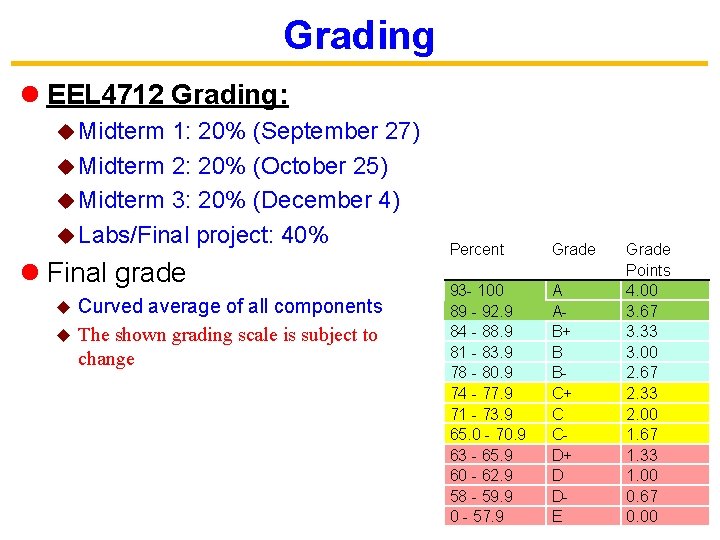

Grading l EEL 4712 Grading: u Midterm 1: 20% (September 27) u Midterm 2: 20% (October 25) u Midterm 3: 20% (December 4) u Labs/Final project: 40% l Final grade Curved average of all components u The shown grading scale is subject to change u Percent Grade 93 - 100 89 - 92. 9 84 - 88. 9 81 - 83. 9 78 - 80. 9 74 - 77. 9 71 - 73. 9 65. 0 - 70. 9 63 - 65. 9 60 - 62. 9 58 - 59. 9 0 - 57. 9 A AB+ B BC+ C CD+ D DE Grade Points 4. 00 3. 67 3. 33 3. 00 2. 67 2. 33 2. 00 1. 67 1. 33 1. 00 0. 67 0. 00 10

Academic Dishonesty l Unless told otherwise, assignments must be done individually u All assignments will be checked for cheating l Collaboration is allowed (and encouraged), but within limits u Can discuss problems, how to use tools etc. u Cannot show code, solutions, etc. l Cheating penalties u First instance - 0 on corresponding assignment u Second - 0 for entire class u Software is used to check lab assignments and projects 11

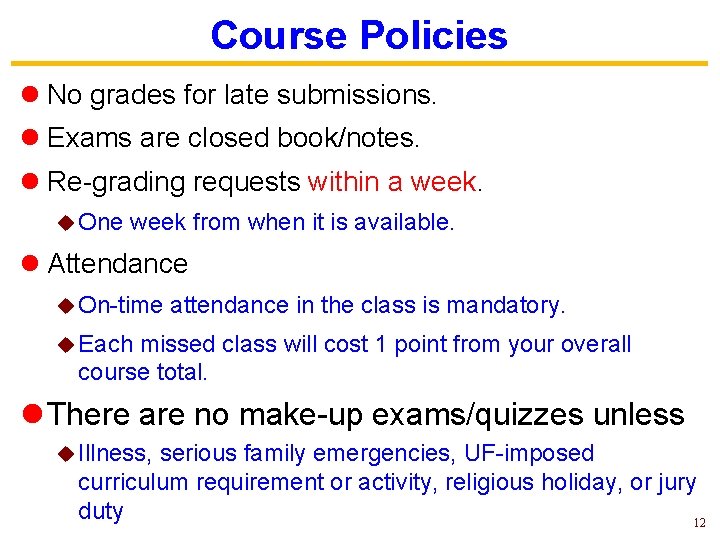

Course Policies l No grades for late submissions. l Exams are closed book/notes. l Re-grading requests within a week. u One week from when it is available. l Attendance u On-time attendance in the class is mandatory. u Each missed class will cost 1 point from your overall course total. l There are no make-up exams/quizzes unless u Illness, serious family emergencies, UF-imposed curriculum requirement or activity, religious holiday, or jury duty 12

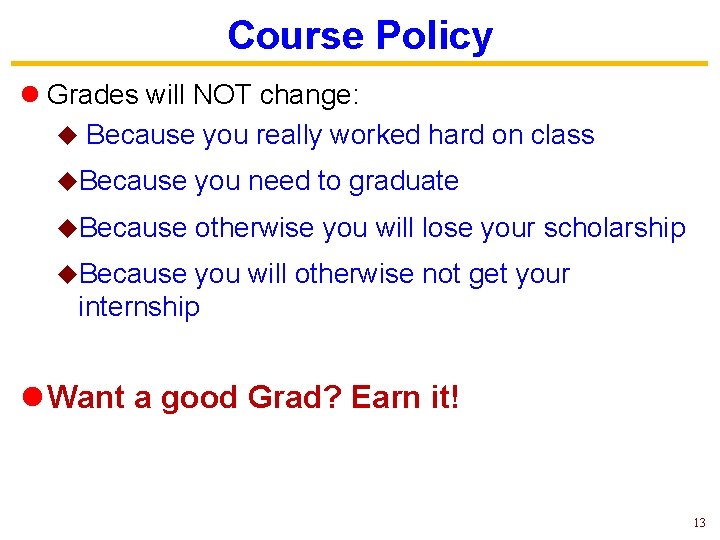

Course Policy l Grades will NOT change: u Because you really worked hard on class u. Because you need to graduate u. Because otherwise you will lose your scholarship u. Because you will otherwise not get your internship l Want a good Grad? Earn it! 13

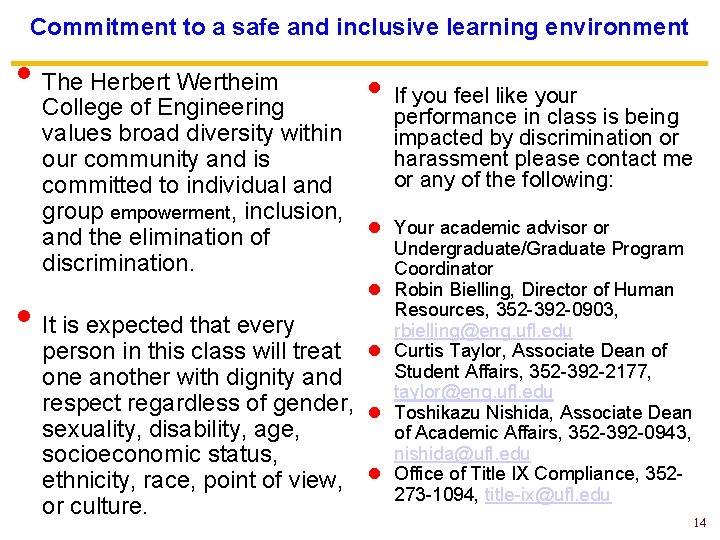

Commitment to a safe and inclusive learning environment • The Herbert Wertheim • Ifperformance you feel like your in class is being College of Engineering values broad diversity within our community and is committed to individual and group empowerment, inclusion, l and the elimination of discrimination. • It is expected that every l person in this class will treat l one another with dignity and respect regardless of gender, l sexuality, disability, age, socioeconomic status, ethnicity, race, point of view, l or culture. impacted by discrimination or harassment please contact me or any of the following: Your academic advisor or Undergraduate/Graduate Program Coordinator Robin Bielling, Director of Human Resources, 352 -392 -0903, rbielling@eng. ufl. edu Curtis Taylor, Associate Dean of Student Affairs, 352 -392 -2177, taylor@eng. ufl. edu Toshikazu Nishida, Associate Dean of Academic Affairs, 352 -392 -0943, nishida@ufl. edu Office of Title IX Compliance, 352273 -1094, title-ix@ufl. edu 14

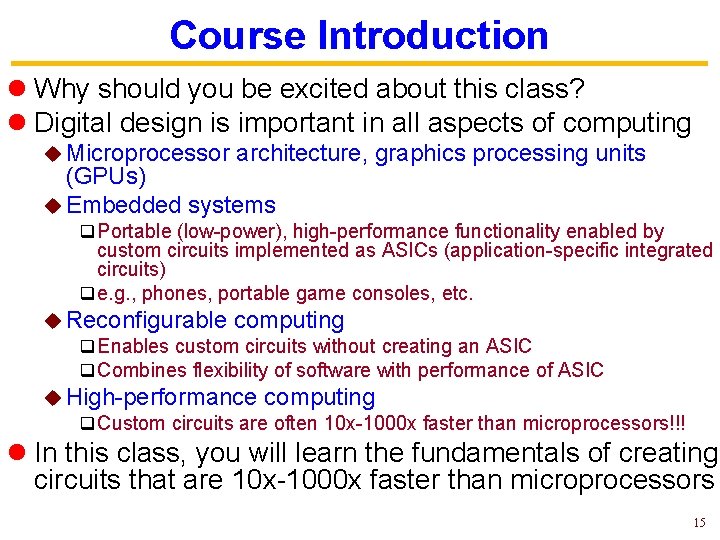

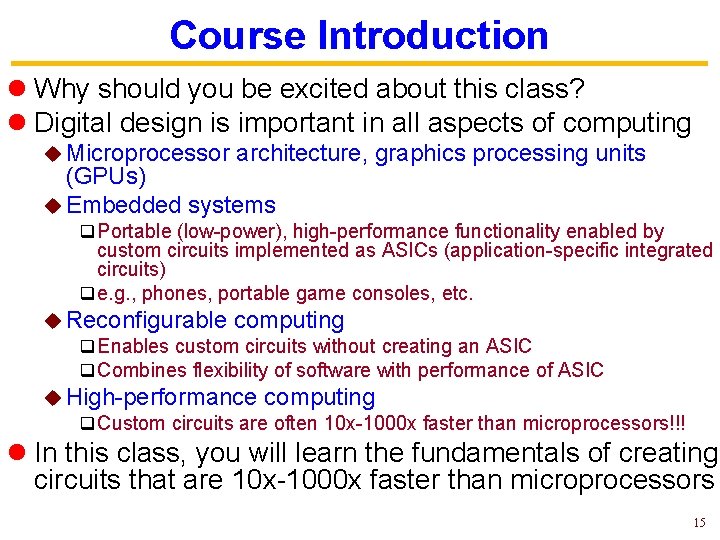

Course Introduction l Why should you be excited about this class? l Digital design is important in all aspects of computing u Microprocessor architecture, graphics processing units (GPUs) u Embedded systems q Portable (low-power), high-performance functionality enabled by custom circuits implemented as ASICs (application-specific integrated circuits) q e. g. , phones, portable game consoles, etc. u Reconfigurable computing q Enables custom circuits without creating an ASIC q Combines flexibility of software with performance of ASIC u High-performance computing q Custom circuits are often 10 x-1000 x faster than microprocessors!!! l In this class, you will learn the fundamentals of creating circuits that are 10 x-1000 x faster than microprocessors 15

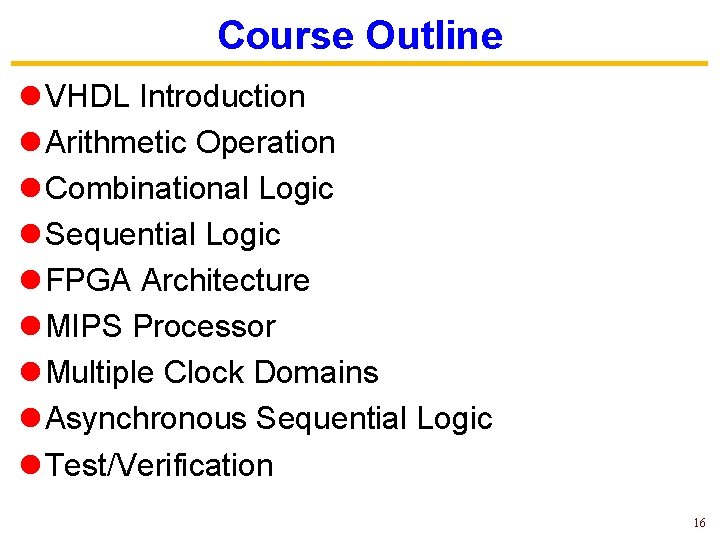

Course Outline l VHDL Introduction l Arithmetic Operation l Combinational Logic l Sequential Logic l FPGA Architecture l MIPS Processor l Multiple Clock Domains l Asynchronous Sequential Logic l Test/Verification 16

Reminder l Start reading details of lab 0 (will be posted soon) l Review chapter 6 u. Combinational logic 17

Thank You!