EEL 4712 Digital Design Bus and Arbiter Tristate

EEL 4712 Digital Design (Bus and Arbiter)

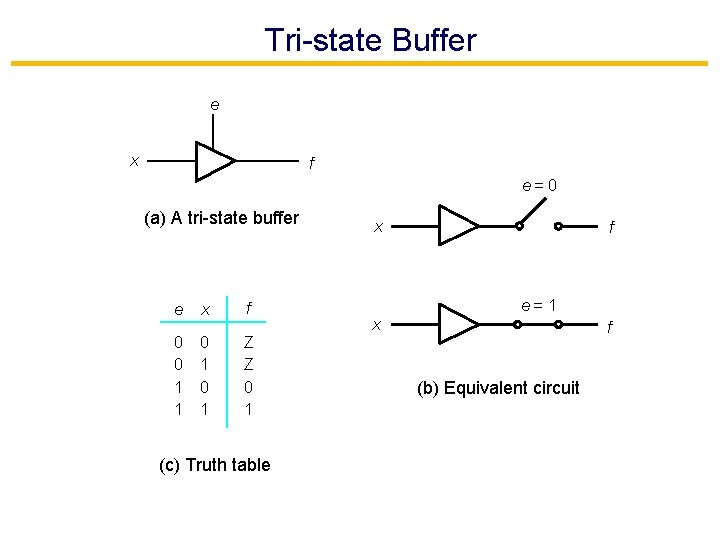

Tri-state Buffer e x f e= 0 (a) A tri-state buffer e x f 0 0 1 1 Z Z 0 1 0 1 (c) Truth table x x f e= 1 f (b) Equivalent circuit

Four types of Tri-state Buffers

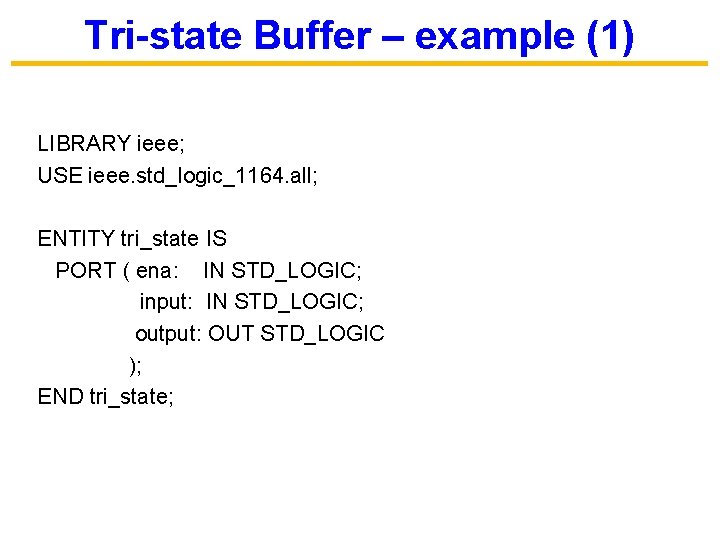

Tri-state Buffer – example (1) LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY tri_state IS PORT ( ena: IN STD_LOGIC; input: IN STD_LOGIC; output: OUT STD_LOGIC ); END tri_state;

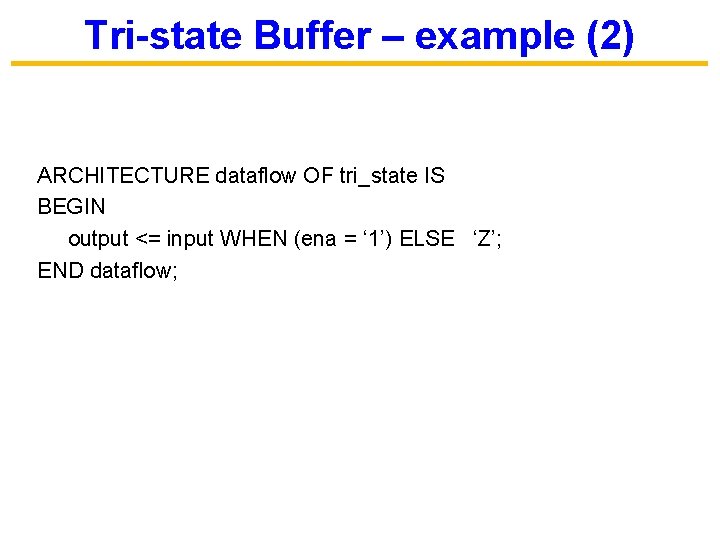

Tri-state Buffer – example (2) ARCHITECTURE dataflow OF tri_state IS BEGIN output <= input WHEN (ena = ‘ 1’) ELSE ‘Z’; END dataflow;

Wire and Buses

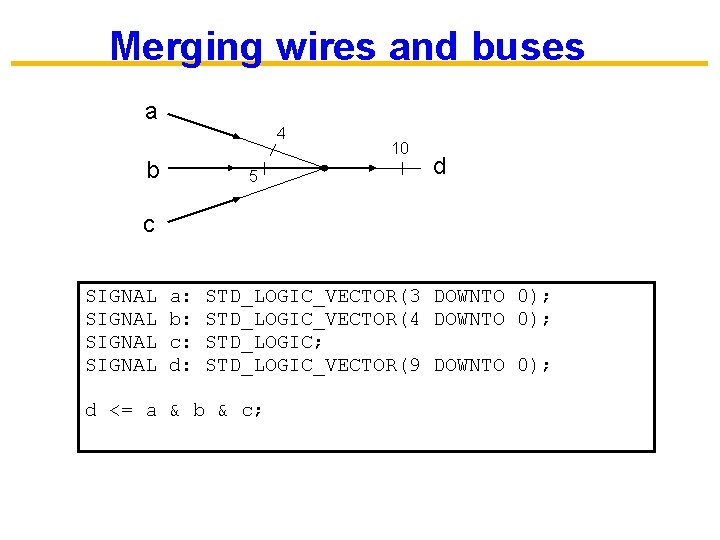

Merging wires and buses a 4 b 5 10 d c SIGNAL a: b: c: d: STD_LOGIC_VECTOR(3 DOWNTO 0); STD_LOGIC_VECTOR(4 DOWNTO 0); STD_LOGIC_VECTOR(9 DOWNTO 0); d <= a & b & c;

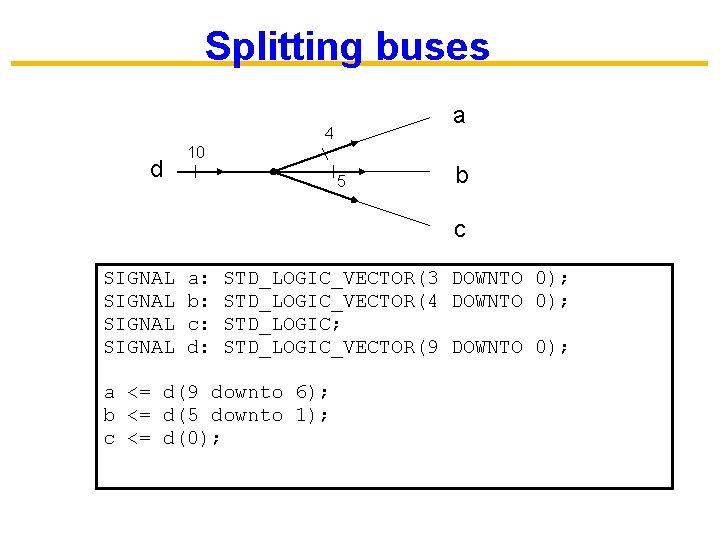

Splitting buses a 4 d 10 5 b c SIGNAL a: b: c: d: STD_LOGIC_VECTOR(3 DOWNTO 0); STD_LOGIC_VECTOR(4 DOWNTO 0); STD_LOGIC_VECTOR(9 DOWNTO 0); a <= d(9 downto 6); b <= d(5 downto 1); c <= d(0);

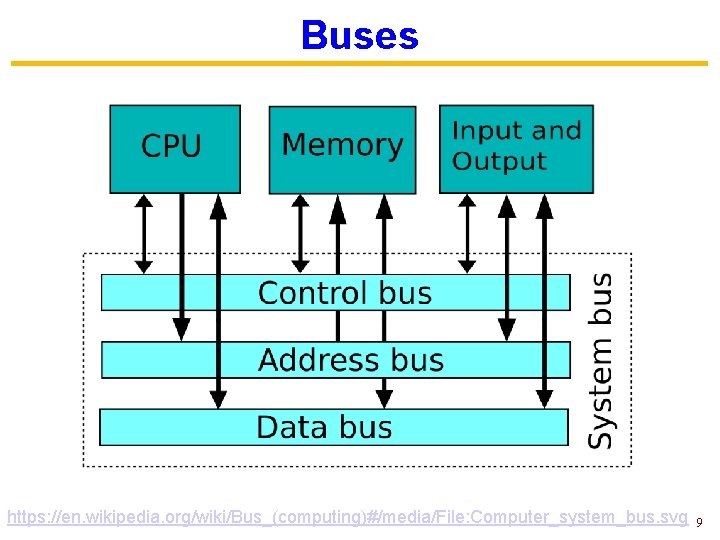

Buses https: //en. wikipedia. org/wiki/Bus_(computing)#/media/File: Computer_system_bus. svg 9

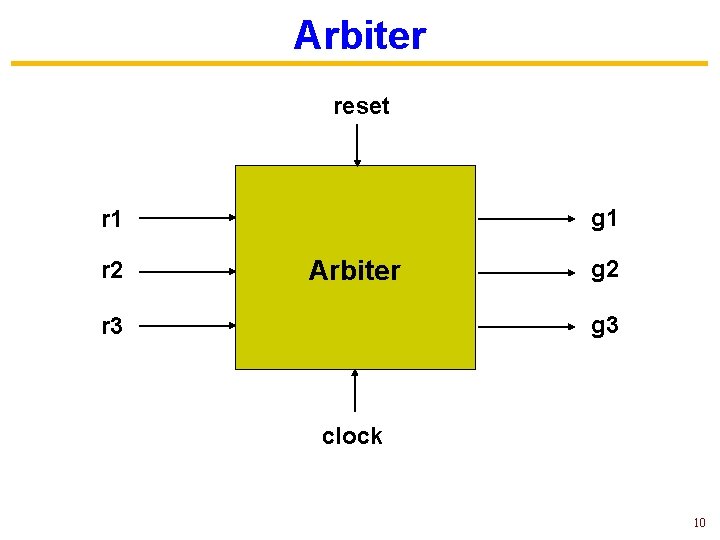

Arbiter reset g 1 r 2 Arbiter g 2 g 3 r 3 clock 10

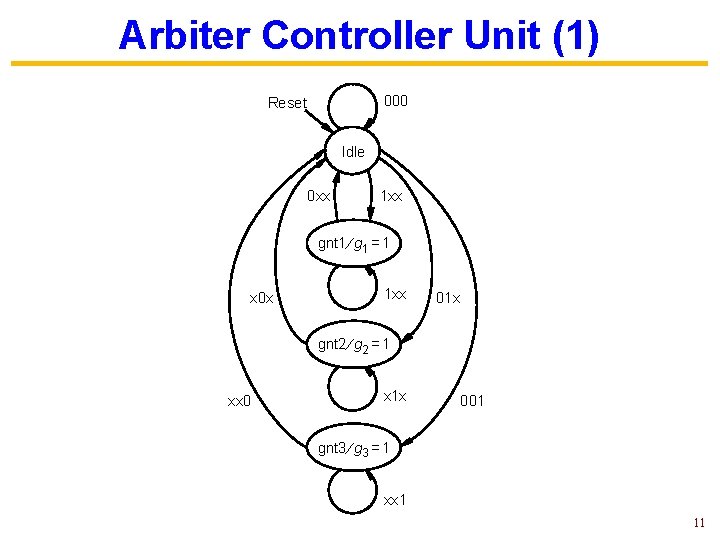

Arbiter Controller Unit (1) 000 Reset Idle 0 xx 1 xx gnt 1 ¤ g 1 = 1 x 0 x 1 xx 01 x gnt 2 ¤ g 2 = 1 xx 0 x 1 x 001 gnt 3 ¤ g 3 = 1 xx 1 11

Arbiter Controller Unit (2) 000 Reset Idle 0 xx 1 xx gnt 1 ¤ g 1 = 1 x 0 x 1 xx 01 x gnt 2 ¤ g 2 = 1 xx 0 x 1 x 001 gnt 3 ¤ g 3 = 1 xx 1 12

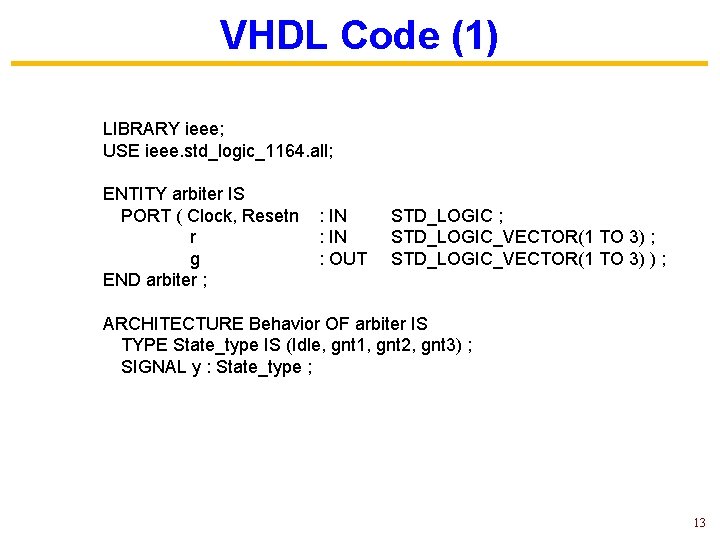

VHDL Code (1) LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY arbiter IS PORT ( Clock, Resetn r g END arbiter ; : IN : OUT STD_LOGIC ; STD_LOGIC_VECTOR(1 TO 3) ) ; ARCHITECTURE Behavior OF arbiter IS TYPE State_type IS (Idle, gnt 1, gnt 2, gnt 3) ; SIGNAL y : State_type ; 13

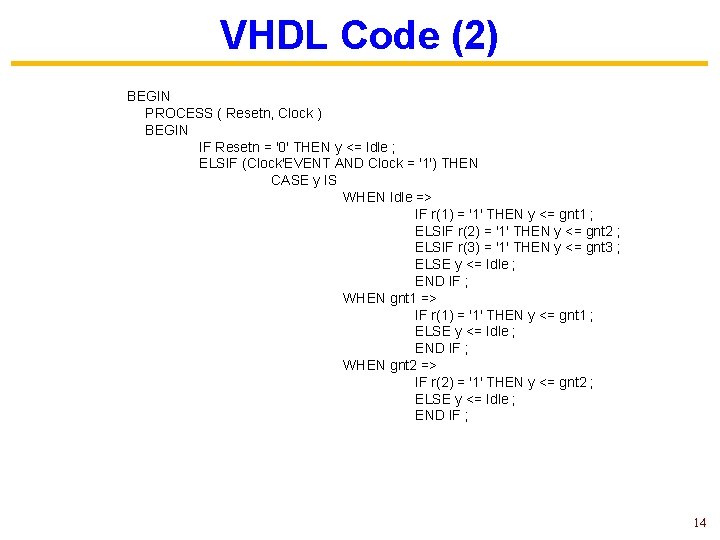

VHDL Code (2) BEGIN PROCESS ( Resetn, Clock ) BEGIN IF Resetn = '0' THEN y <= Idle ; ELSIF (Clock'EVENT AND Clock = '1') THEN CASE y IS WHEN Idle => IF r(1) = '1' THEN y <= gnt 1 ; ELSIF r(2) = '1' THEN y <= gnt 2 ; ELSIF r(3) = '1' THEN y <= gnt 3 ; ELSE y <= Idle ; END IF ; WHEN gnt 1 => IF r(1) = '1' THEN y <= gnt 1 ; ELSE y <= Idle ; END IF ; WHEN gnt 2 => IF r(2) = '1' THEN y <= gnt 2 ; ELSE y <= Idle ; END IF ; 14

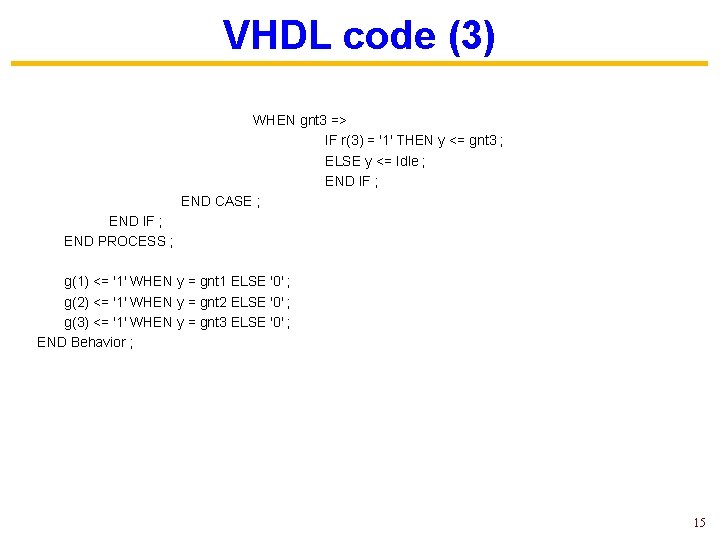

VHDL code (3) WHEN gnt 3 => IF r(3) = '1' THEN y <= gnt 3 ; ELSE y <= Idle ; END IF ; END CASE ; END IF ; END PROCESS ; g(1) <= '1' WHEN y = gnt 1 ELSE '0' ; g(2) <= '1' WHEN y = gnt 2 ELSE '0' ; g(3) <= '1' WHEN y = gnt 3 ELSE '0' ; END Behavior ; 15

References l https: //ece. gmu. edu/coursewebpages/ECE/E CE 545/F 18/ 16

Questions?

- Slides: 17