EEL 4712 Digital Design VHDL Tutorial Abstraction Levels

EEL 4712 Digital Design (VHDL Tutorial)

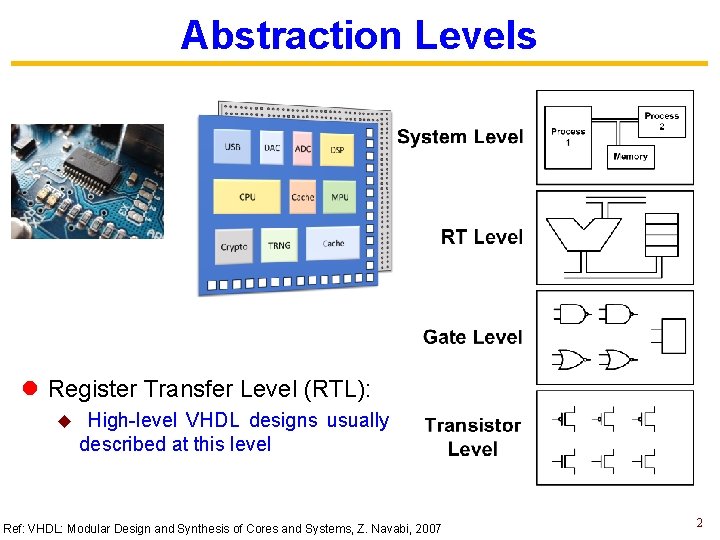

Abstraction Levels l Register Transfer Level (RTL): u High-level VHDL designs usually described at this level Ref: VHDL: Modular Design and Synthesis of Cores and Systems, Z. Navabi, 2007 2

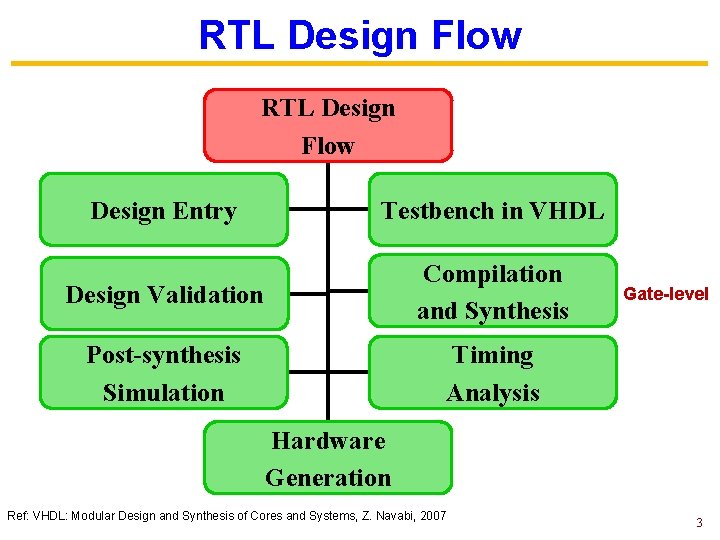

RTL Design Flow Design Entry Testbench in VHDL Design Validation Compilation and Synthesis Post-synthesis Simulation Timing Analysis Gate-level Hardware Generation Ref: VHDL: Modular Design and Synthesis of Cores and Systems, Z. Navabi, 2007 3

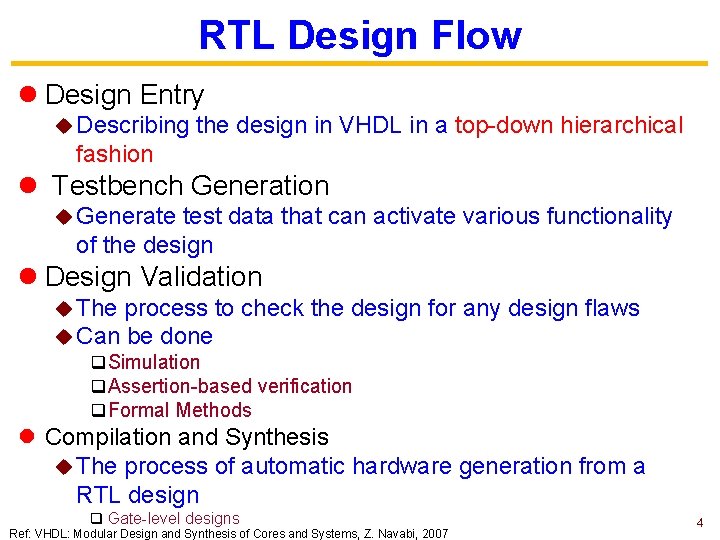

RTL Design Flow l Design Entry u Describing the design in VHDL in a top-down hierarchical fashion l Testbench Generation u Generate test data that can activate various functionality of the design l Design Validation u The process to check the design u Can be done q Simulation q Assertion-based verification q Formal Methods for any design flaws l Compilation and Synthesis u The process of automatic hardware generation from a RTL design q Gate-level designs Ref: VHDL: Modular Design and Synthesis of Cores and Systems, Z. Navabi, 2007 4

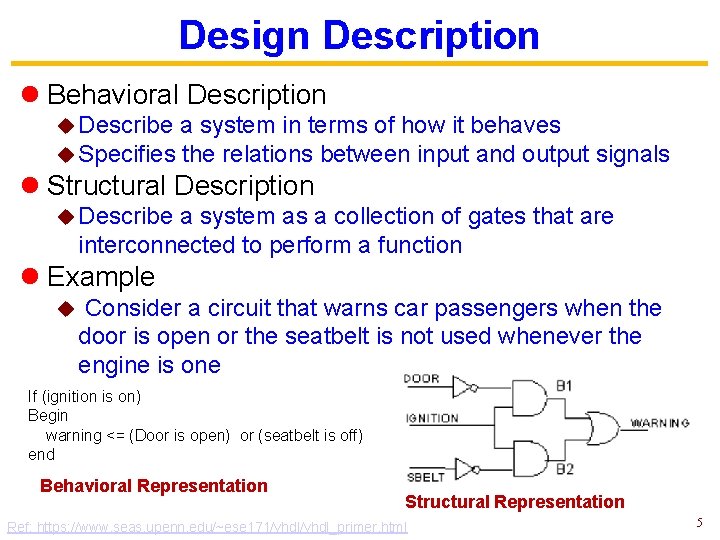

Design Description l Behavioral Description u Describe a system in terms of how it behaves u Specifies the relations between input and output signals l Structural Description u Describe a system as a collection of gates that are interconnected to perform a function l Example u Consider a circuit that warns car passengers when the door is open or the seatbelt is not used whenever the engine is one If (ignition is on) Begin warning <= (Door is open) or (seatbelt is off) end Behavioral Representation Structural Representation Ref: https: //www. seas. upenn. edu/~ese 171/vhdl_primer. html 5

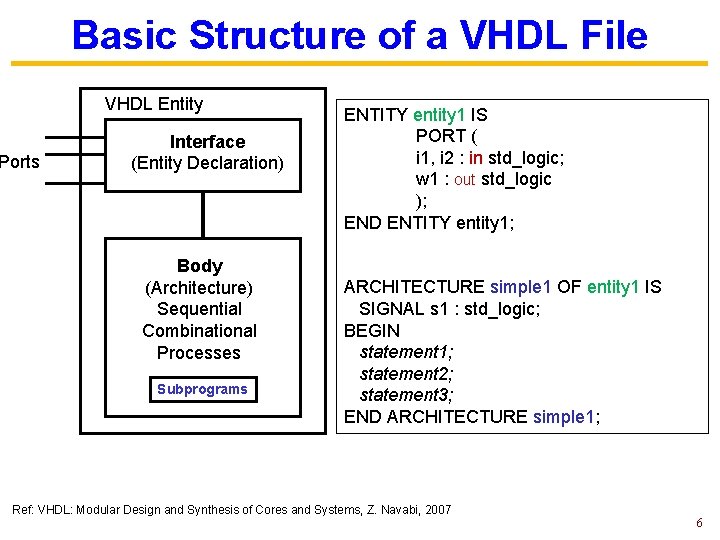

Basic Structure of a VHDL File VHDL Entity Ports Interface (Entity Declaration) Body (Architecture) Sequential Combinational Processes Subprograms ENTITY entity 1 IS PORT ( i 1, i 2 : in std_logic; w 1 : out std_logic ); END ENTITY entity 1; ARCHITECTURE simple 1 OF entity 1 IS SIGNAL s 1 : std_logic; BEGIN statement 1; statement 2; statement 3; END ARCHITECTURE simple 1; Ref: VHDL: Modular Design and Synthesis of Cores and Systems, Z. Navabi, 2007 6

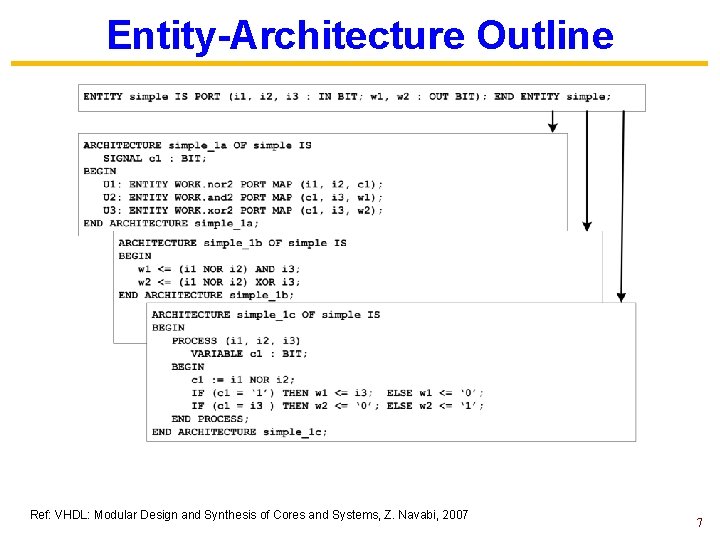

Entity-Architecture Outline Ref: VHDL: Modular Design and Synthesis of Cores and Systems, Z. Navabi, 2007 7

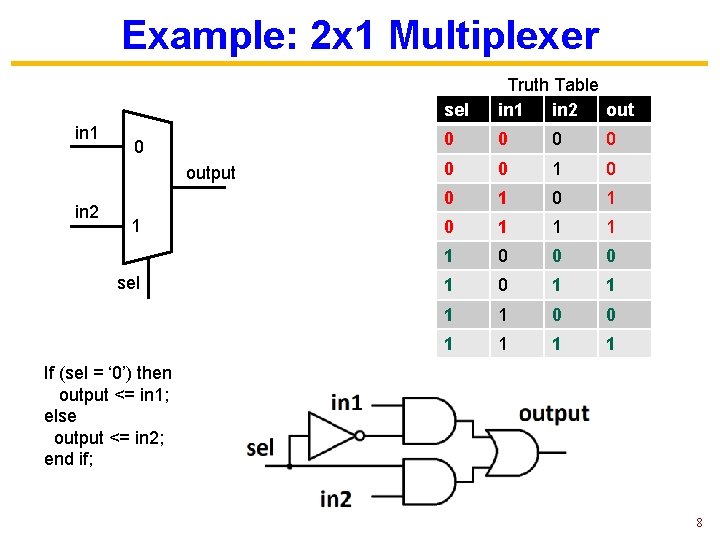

Example: 2 x 1 Multiplexer in 1 0 output in 2 1 sel Truth Table in 1 in 2 out 0 0 0 1 0 1 1 0 0 0 1 1 1 1 0 0 1 1 If (sel = ‘ 0’) then output <= in 1; else output <= in 2; end if; 8

![Entity Ports entity NAME_OF_ENTITY is [ generic_declarations); ] port (signal_names: mode type; : signal_names: Entity Ports entity NAME_OF_ENTITY is [ generic_declarations); ] port (signal_names: mode type; : signal_names:](http://slidetodoc.com/presentation_image_h2/944efad82fccc4ea87c1a30f94ede0a7/image-9.jpg)

Entity Ports entity NAME_OF_ENTITY is [ generic_declarations); ] port (signal_names: mode type; : signal_names: mode type); end [NAME_OF_ENTITY] ; l The NAME_OF_ENTITY is a user-selected identifier l signal_names specify external interface signals. l mode: indicates the signal direction: u u in: indicates that the signal is an input out: indicates that the signal is an output of the entity whose value can only be read by other entities that use it. Buffer: indicates that the signal is an output of the entity whose value can be read inside the entity’s architecture Inout: the signal can be an input or an output. Value Representing l type: a built-in or user-defined signal type Bit: can have the value 0 and 1 u bit_vector: is a vector of bit values (e. g. bit_vector (0 to 7) u std_logic, std_ulogic, std_logic_vector, std_ulogic_vector can have 9 values to indicate the value and strength of a signal. Std_ulogic and std_logic are preferred over the bit or bit_vector types. u Boolean: can have the value TRUE and FALSE u Integer: can have a range of integer values u Real: can have a range of real values u Character: any printing character u Time: to indicate time Ref: https: //www. seas. upenn. edu/~ese 171/vhdl_primer. html u 'U' Uninitialized 'X' Forcing Unknown '0' Forcing 0 '1' Forcing 1 'Z' High Impedance 'W' Weak Unknown 'L' Weak 0 'H' Weak 1 '-' Don’t care 9

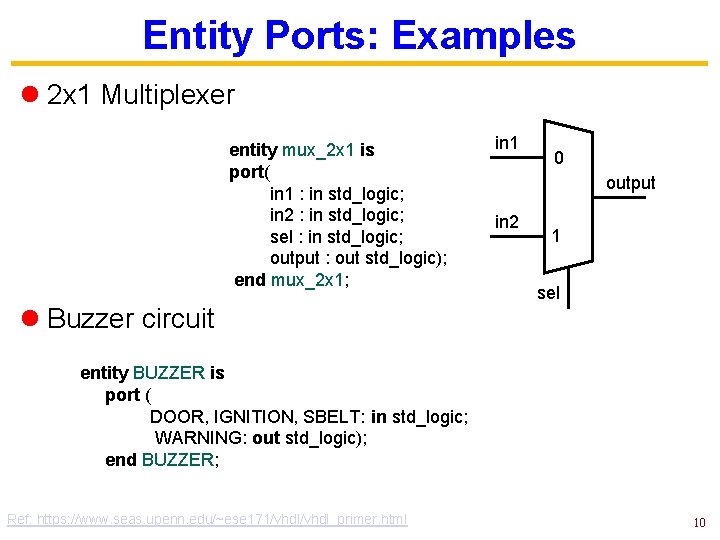

Entity Ports: Examples l 2 x 1 Multiplexer entity mux_2 x 1 is port( in 1 : in std_logic; in 2 : in std_logic; sel : in std_logic; output : out std_logic); end mux_2 x 1; l Buzzer circuit in 1 0 output in 2 1 sel entity BUZZER is port ( DOOR, IGNITION, SBELT: in std_logic; WARNING: out std_logic); end BUZZER; Ref: https: //www. seas. upenn. edu/~ese 171/vhdl_primer. html 10

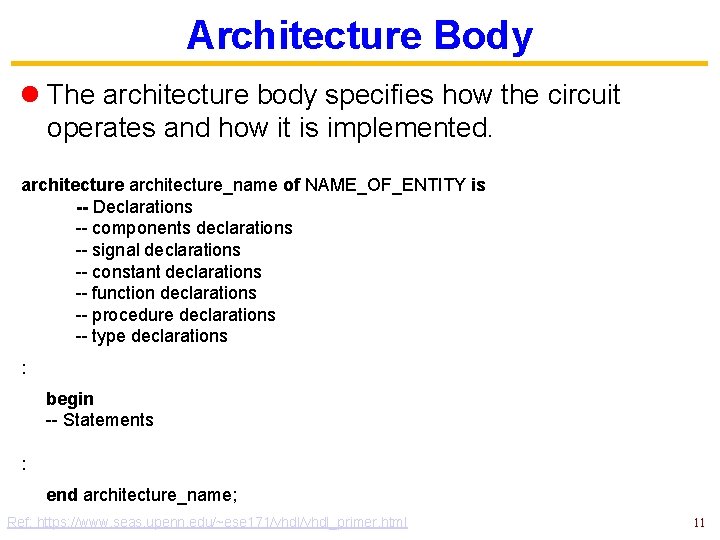

Architecture Body l The architecture body specifies how the circuit operates and how it is implemented. architecture_name of NAME_OF_ENTITY is -- Declarations -- components declarations -- signal declarations -- constant declarations -- function declarations -- procedure declarations -- type declarations : begin -- Statements : end architecture_name; Ref: https: //www. seas. upenn. edu/~ese 171/vhdl_primer. html 11

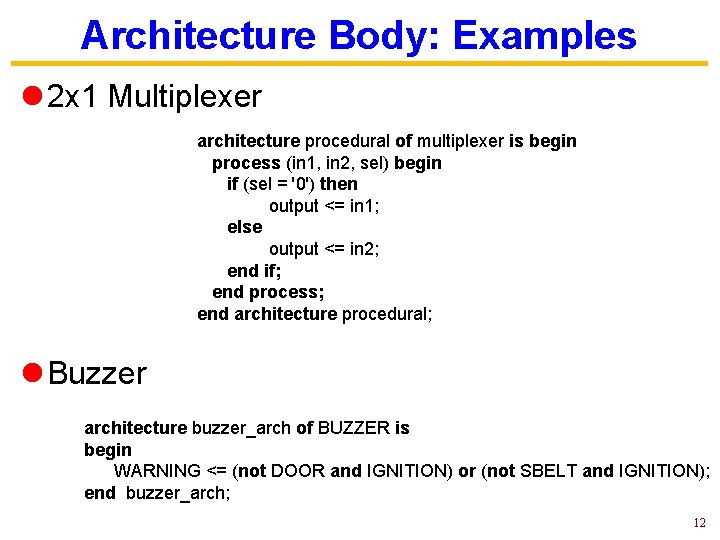

Architecture Body: Examples l 2 x 1 Multiplexer architecture procedural of multiplexer is begin process (in 1, in 2, sel) begin if (sel = '0') then output <= in 1; else output <= in 2; end if; end process; end architecture procedural; l Buzzer architecture buzzer_arch of BUZZER is begin WARNING <= (not DOOR and IGNITION) or (not SBELT and IGNITION); end buzzer_arch; 12

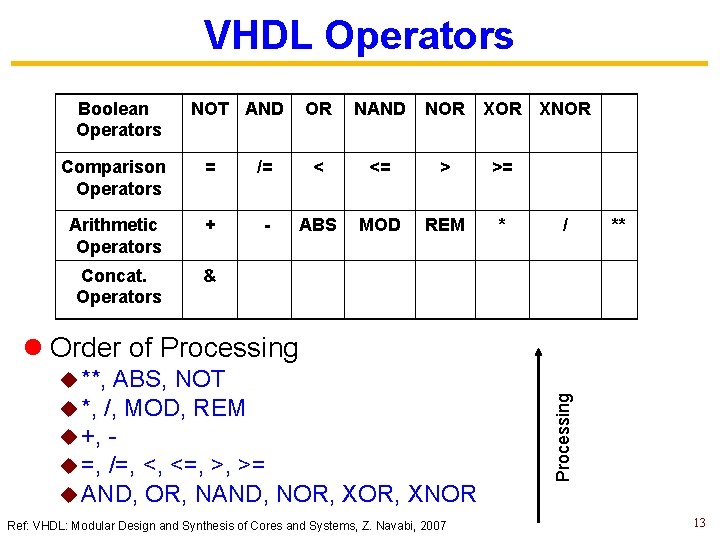

VHDL Operators Boolean Operators NOT AND OR NAND NOR XNOR Comparison Operators = /= < <= > >= Arithmetic Operators + - ABS MOD REM * Concat. Operators & / ** u **, ABS, NOT u *, /, MOD, REM u +, u =, /=, <, <=, >, >= u AND, OR, NAND, NOR, XNOR Ref: VHDL: Modular Design and Synthesis of Cores and Systems, Z. Navabi, 2007 Processing l Order of Processing 13

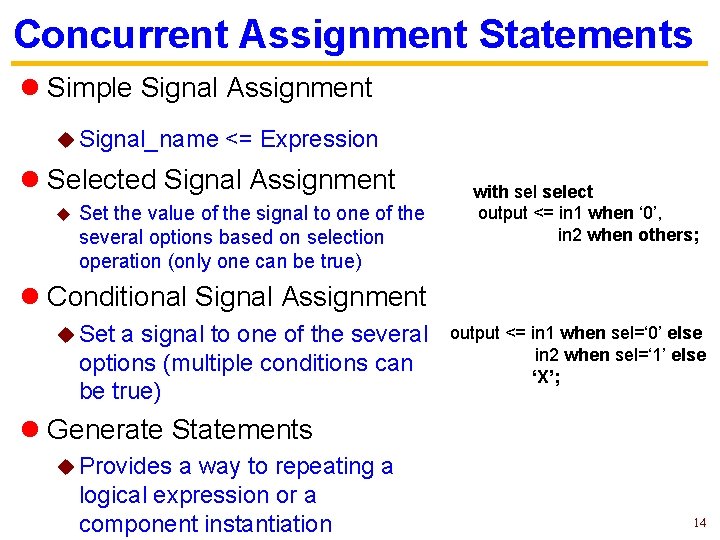

Concurrent Assignment Statements l Simple Signal Assignment u Signal_name <= Expression l Selected Signal Assignment u Set the value of the signal to one of the several options based on selection operation (only one can be true) with select output <= in 1 when ‘ 0’, in 2 when others; l Conditional Signal Assignment u Set a signal to one of the several options (multiple conditions can be true) output <= in 1 when sel=‘ 0’ else in 2 when sel=‘ 1’ else ‘X’; l Generate Statements u Provides a way to repeating a logical expression or a component instantiation 14

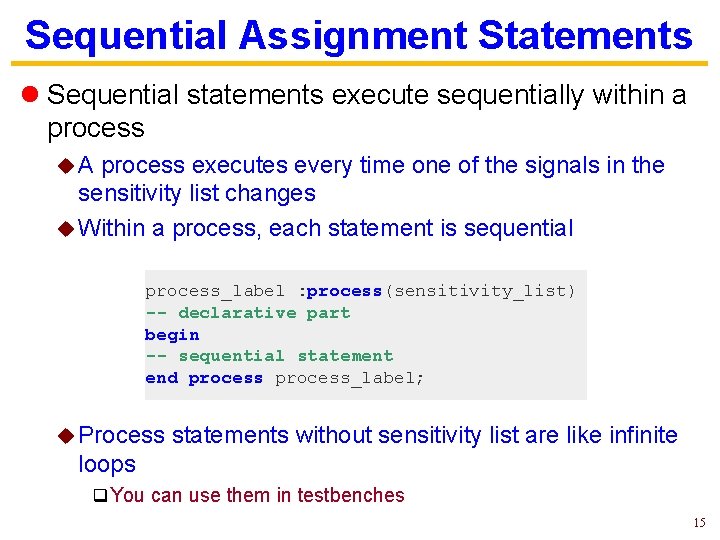

Sequential Assignment Statements l Sequential statements execute sequentially within a process u. A process executes every time one of the signals in the sensitivity list changes u Within a process, each statement is sequential process_label : process(sensitivity_list) -- declarative part begin -- sequential statement end process_label; u Process statements without sensitivity list are like infinite loops q You can use them in testbenches 15

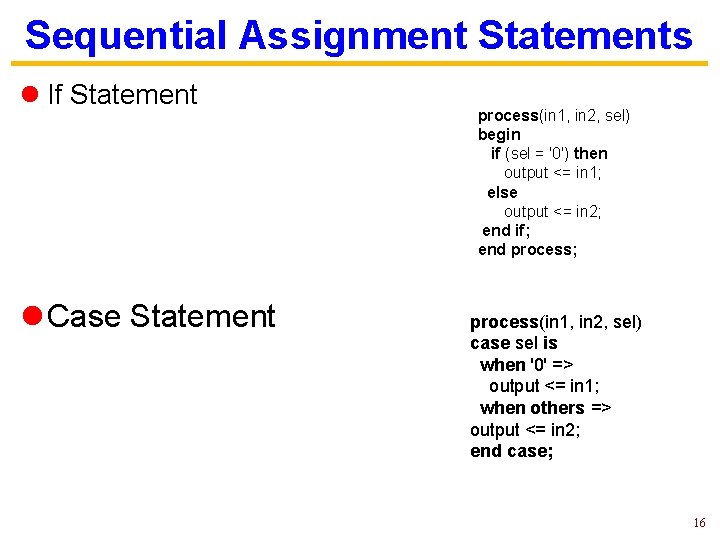

Sequential Assignment Statements l If Statement l Case Statement process(in 1, in 2, sel) begin if (sel = '0') then output <= in 1; else output <= in 2; end if; end process; process(in 1, in 2, sel) case sel is when '0' => output <= in 1; when others => output <= in 2; end case; 16

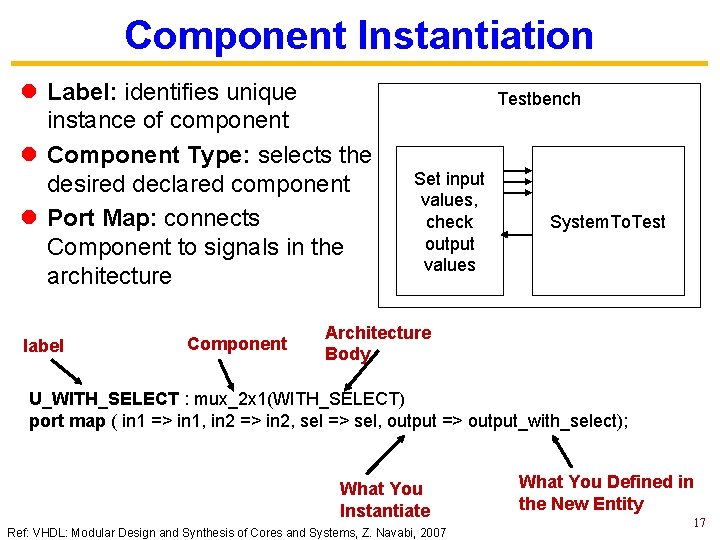

Component Instantiation l Label: identifies unique instance of component l Component Type: selects the desired declared component l Port Map: connects Component to signals in the architecture label Component Testbench Set input values, check output values System. To. Test Architecture Body U_WITH_SELECT : mux_2 x 1(WITH_SELECT) port map ( in 1 => in 1, in 2 => in 2, sel => sel, output => output_with_select); What You Instantiate Ref: VHDL: Modular Design and Synthesis of Cores and Systems, Z. Navabi, 2007 What You Defined in the New Entity 17

Questions?

- Slides: 18