ECE 448 Lecture 6 SequentialCircuit Building Blocks Part

ECE 448 Lecture 6 Sequential-Circuit Building Blocks Part 2 ECE 448 – FPGA and ASIC Design with VHDL George Mason University

Reading Required • P. Chu, FPGA Prototyping by VHDL Examples Chapter 4, Regular Sequential Circuit Recommended • S. Brown and Z. Vranesic, Fundamentals of Digital Logic with VHDL Design Chapter 7, Flip-Flops, Registers, Counters, and a Simple Processor ECE 448 – FPGA and ASIC Design with VHDL 2

Counters ECE 448 – FPGA and ASIC Design with VHDL 3

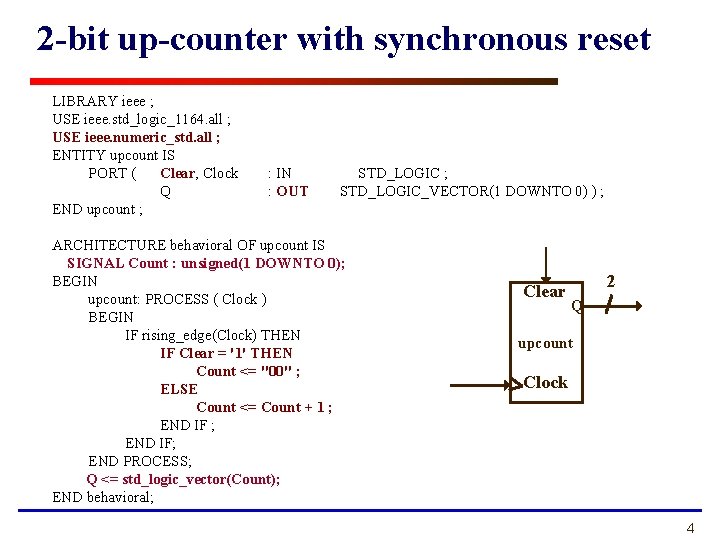

2 -bit up-counter with synchronous reset LIBRARY ieee ; USE ieee. std_logic_1164. all ; USE ieee. numeric_std. all ; ENTITY upcount IS PORT ( Clear, Clock Q END upcount ; : IN : OUT STD_LOGIC ; STD_LOGIC_VECTOR(1 DOWNTO 0) ) ; ARCHITECTURE behavioral OF upcount IS SIGNAL Count : unsigned(1 DOWNTO 0); BEGIN upcount: PROCESS ( Clock ) BEGIN IF rising_edge(Clock) THEN IF Clear = '1' THEN Count <= "00" ; ELSE Count <= Count + 1 ; END IF; END PROCESS; Q <= std_logic_vector(Count); END behavioral; Clear 2 Q upcount Clock 4

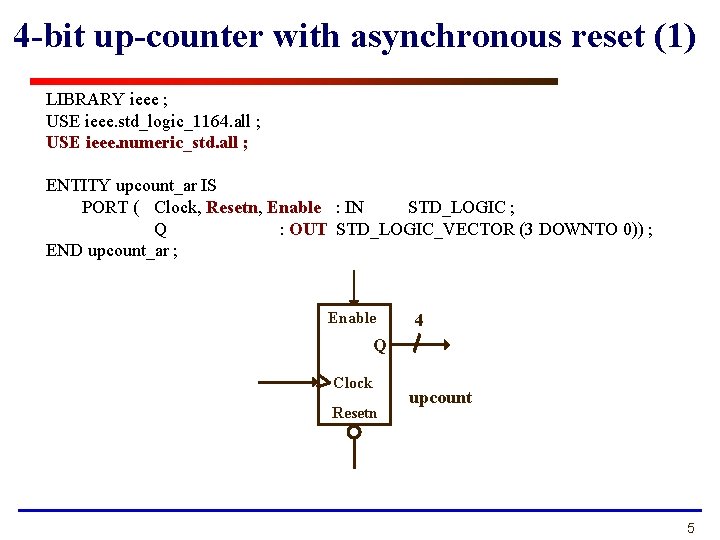

4 -bit up-counter with asynchronous reset (1) LIBRARY ieee ; USE ieee. std_logic_1164. all ; USE ieee. numeric_std. all ; ENTITY upcount_ar IS PORT ( Clock, Resetn, Enable : IN STD_LOGIC ; Q : OUT STD_LOGIC_VECTOR (3 DOWNTO 0)) ; END upcount_ar ; Enable 4 Q Clock Resetn upcount 5

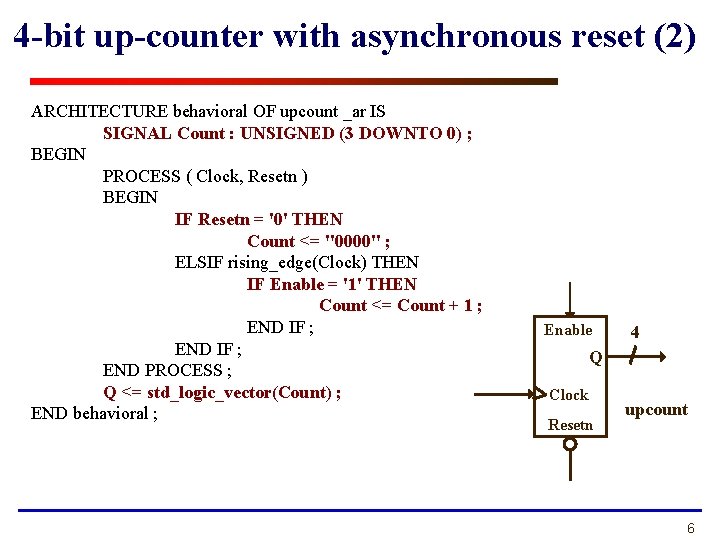

4 -bit up-counter with asynchronous reset (2) ARCHITECTURE behavioral OF upcount _ar IS SIGNAL Count : UNSIGNED (3 DOWNTO 0) ; BEGIN PROCESS ( Clock, Resetn ) BEGIN IF Resetn = '0' THEN Count <= "0000" ; ELSIF rising_edge(Clock) THEN IF Enable = '1' THEN Count <= Count + 1 ; END IF ; END PROCESS ; Q <= std_logic_vector(Count) ; END behavioral ; Enable 4 Q Clock Resetn upcount 6

Shift Registers ECE 448 – FPGA and ASIC Design with VHDL 7

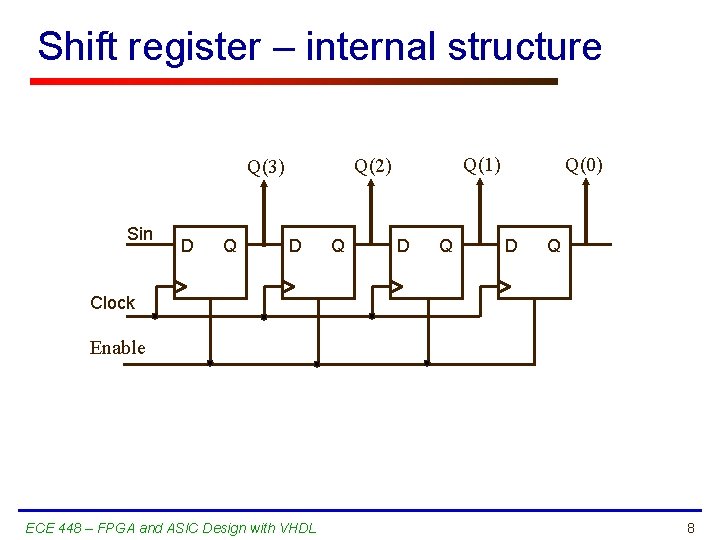

Shift register – internal structure Sin D Q Q(1) Q(2) Q(3) D Q Q(0) D Q Clock Enable ECE 448 – FPGA and ASIC Design with VHDL 8

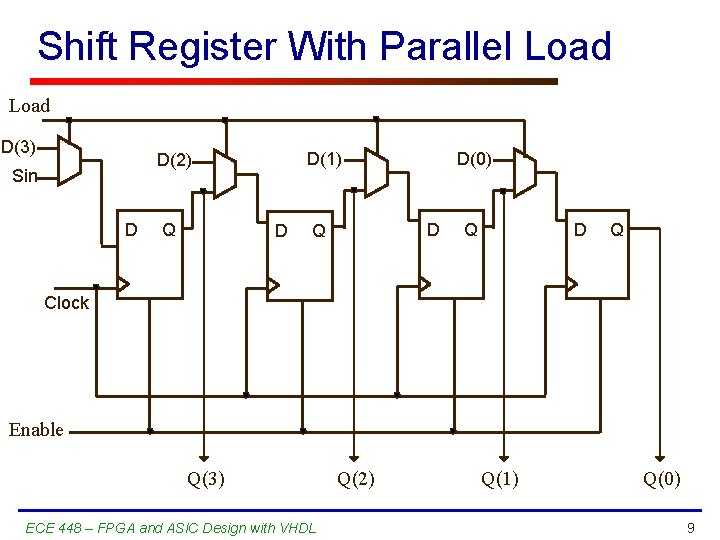

Shift Register With Parallel Load D(3) D(1) D(2) Sin D Q D D(0) D Q Q D Q Clock Enable Q(3) ECE 448 – FPGA and ASIC Design with VHDL Q(2) Q(1) Q(0) 9

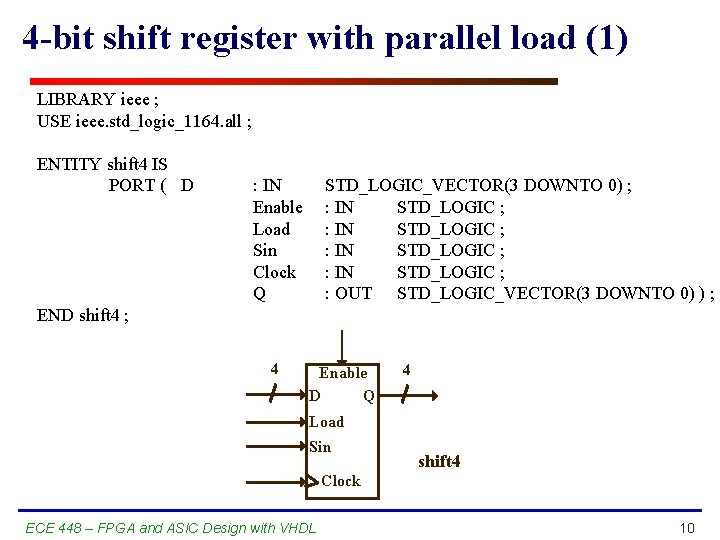

4 -bit shift register with parallel load (1) LIBRARY ieee ; USE ieee. std_logic_1164. all ; ENTITY shift 4 IS PORT ( D : IN Enable Load Sin Clock Q STD_LOGIC_VECTOR(3 DOWNTO 0) ; : IN STD_LOGIC ; : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ) ; END shift 4 ; 4 Enable D Q 4 Load Sin shift 4 Clock ECE 448 – FPGA and ASIC Design with VHDL 10

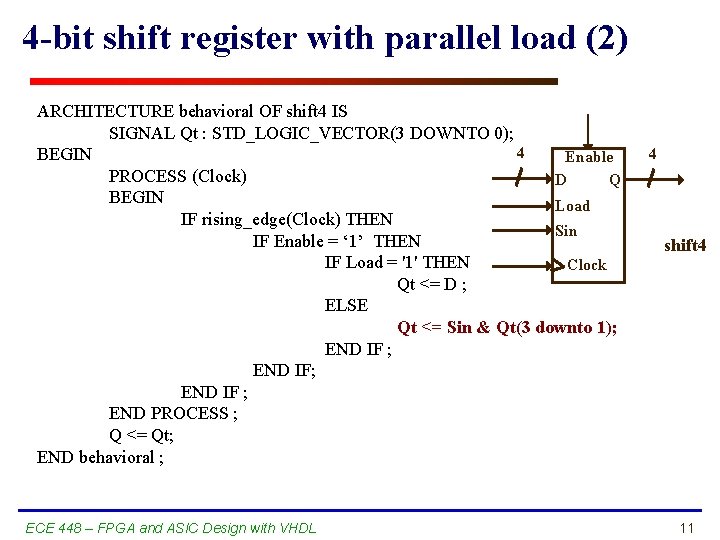

4 -bit shift register with parallel load (2) ARCHITECTURE behavioral OF shift 4 IS SIGNAL Qt : STD_LOGIC_VECTOR(3 DOWNTO 0); 4 BEGIN Enable PROCESS (Clock) D Q BEGIN Load IF rising_edge(Clock) THEN Sin IF Enable = ‘ 1’ THEN IF Load = '1' THEN Clock Qt <= D ; ELSE Qt <= Sin & Qt(3 downto 1); END IF ; END PROCESS ; Q <= Qt; END behavioral ; ECE 448 – FPGA and ASIC Design with VHDL 4 shift 4 11

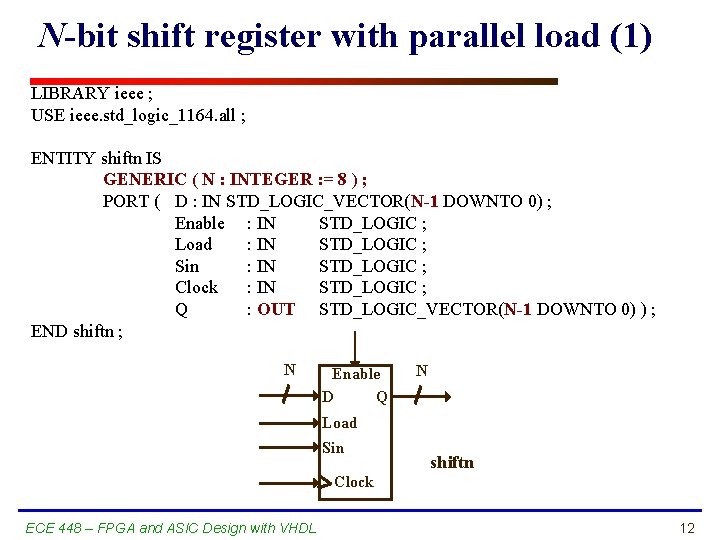

N-bit shift register with parallel load (1) LIBRARY ieee ; USE ieee. std_logic_1164. all ; ENTITY shiftn IS GENERIC ( N : INTEGER : = 8 ) ; PORT ( D : IN STD_LOGIC_VECTOR(N-1 DOWNTO 0) ; Enable : IN STD_LOGIC ; Load : IN STD_LOGIC ; Sin : IN STD_LOGIC ; Clock : IN STD_LOGIC ; Q : OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0) ) ; END shiftn ; N Enable D Q N Load Sin shiftn Clock ECE 448 – FPGA and ASIC Design with VHDL 12

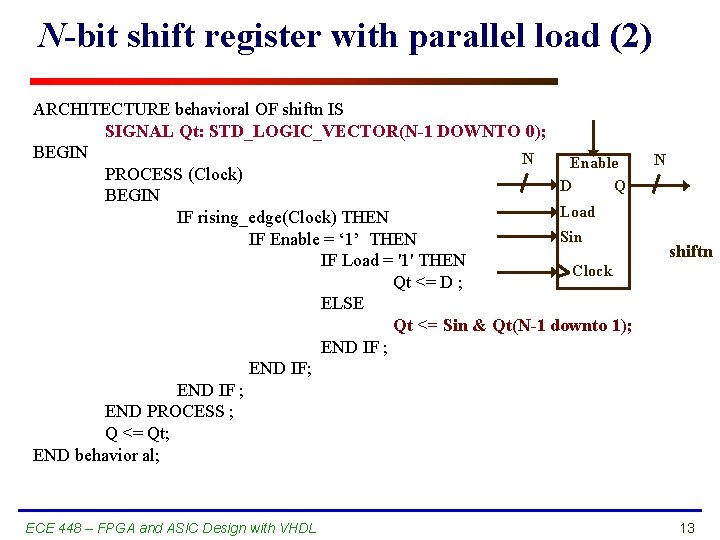

N-bit shift register with parallel load (2) ARCHITECTURE behavioral OF shiftn IS SIGNAL Qt: STD_LOGIC_VECTOR(N-1 DOWNTO 0); BEGIN N Enable PROCESS (Clock) D Q BEGIN Load IF rising_edge(Clock) THEN Sin IF Enable = ‘ 1’ THEN IF Load = '1' THEN Clock Qt <= D ; ELSE Qt <= Sin & Qt(N-1 downto 1); END IF ; END PROCESS ; Q <= Qt; END behavior al; ECE 448 – FPGA and ASIC Design with VHDL N shiftn 13

Generic Component Instantiation ECE 448 – FPGA and ASIC Design with VHDL 14

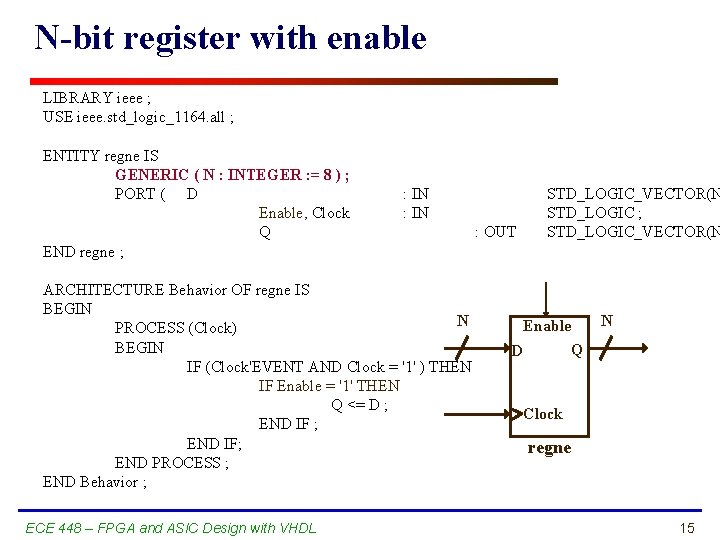

N-bit register with enable LIBRARY ieee ; USE ieee. std_logic_1164. all ; ENTITY regne IS GENERIC ( N : INTEGER : = 8 ) ; PORT ( D Enable, Clock Q END regne ; : IN ARCHITECTURE Behavior OF regne IS BEGIN N PROCESS (Clock) BEGIN IF (Clock'EVENT AND Clock = '1' ) THEN IF Enable = '1' THEN Q <= D ; END IF; END PROCESS ; END Behavior ; ECE 448 – FPGA and ASIC Design with VHDL : OUT STD_LOGIC_VECTOR(N STD_LOGIC ; STD_LOGIC_VECTOR(N N Enable Q D Clock regne 15

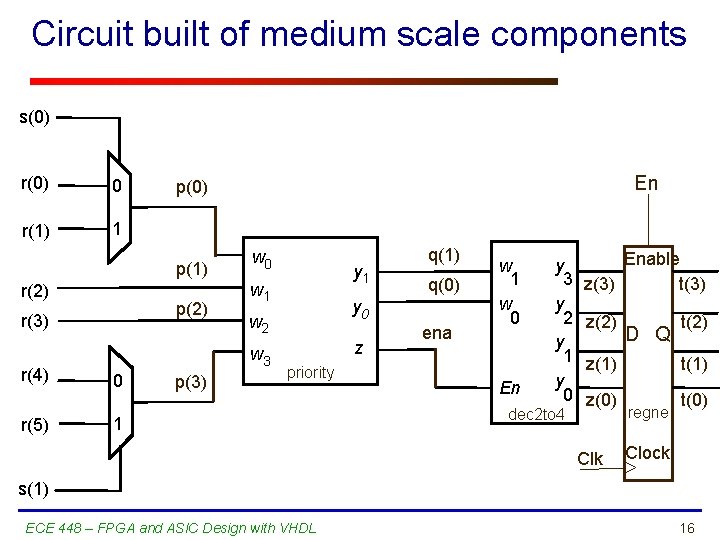

Circuit built of medium scale components s(0) r(0) 0 r(1) 1 p(1) r(2) p(2) r(3) r(4) r(5) En p(0) w 0 w 1 p(3) q(0) y 0 w 2 w 3 0 y 1 q(1) z priority 1 ena w 1 w 0 En y 3 y 2 y 1 y 0 dec 2 to 4 Enable z(3) t(3) z(2) D Q z(1) z(0) Clk t(2) t(1) regne t(0) Clock s(1) ECE 448 – FPGA and ASIC Design with VHDL 16

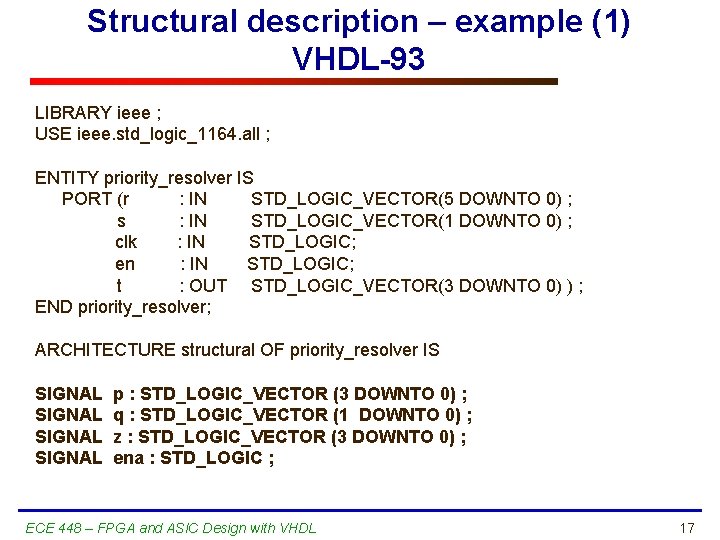

Structural description – example (1) VHDL-93 LIBRARY ieee ; USE ieee. std_logic_1164. all ; ENTITY priority_resolver IS PORT (r : IN STD_LOGIC_VECTOR(5 DOWNTO 0) ; s : IN STD_LOGIC_VECTOR(1 DOWNTO 0) ; clk : IN STD_LOGIC; en : IN STD_LOGIC; t : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ) ; END priority_resolver; ARCHITECTURE structural OF priority_resolver IS SIGNAL p : STD_LOGIC_VECTOR (3 DOWNTO 0) ; q : STD_LOGIC_VECTOR (1 DOWNTO 0) ; z : STD_LOGIC_VECTOR (3 DOWNTO 0) ; ena : STD_LOGIC ; ECE 448 – FPGA and ASIC Design with VHDL 17

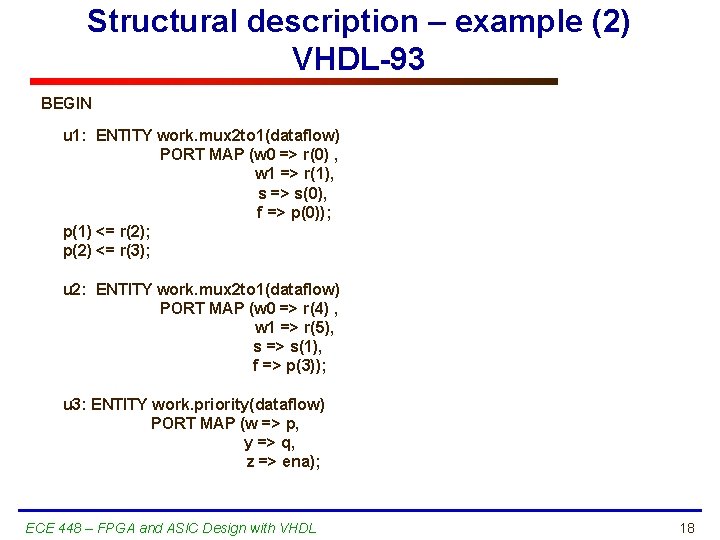

Structural description – example (2) VHDL-93 BEGIN u 1: ENTITY work. mux 2 to 1(dataflow) PORT MAP (w 0 => r(0) , w 1 => r(1), s => s(0), f => p(0)); p(1) <= r(2); p(2) <= r(3); u 2: ENTITY work. mux 2 to 1(dataflow) PORT MAP (w 0 => r(4) , w 1 => r(5), s => s(1), f => p(3)); u 3: ENTITY work. priority(dataflow) PORT MAP (w => p, y => q, z => ena); ECE 448 – FPGA and ASIC Design with VHDL 18

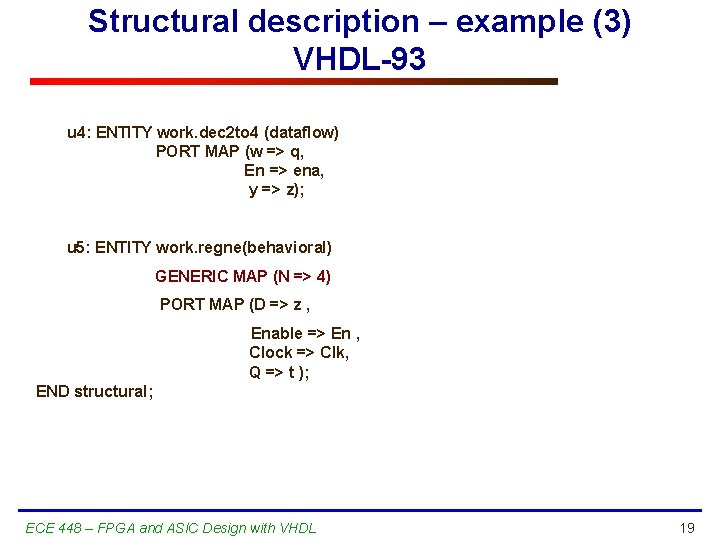

Structural description – example (3) VHDL-93 u 4: ENTITY work. dec 2 to 4 (dataflow) PORT MAP (w => q, En => ena, y => z); u 5: ENTITY work. regne(behavioral) GENERIC MAP (N => 4) PORT MAP (D => z , Enable => En , Clock => Clk, Q => t ); END structural; ECE 448 – FPGA and ASIC Design with VHDL 19

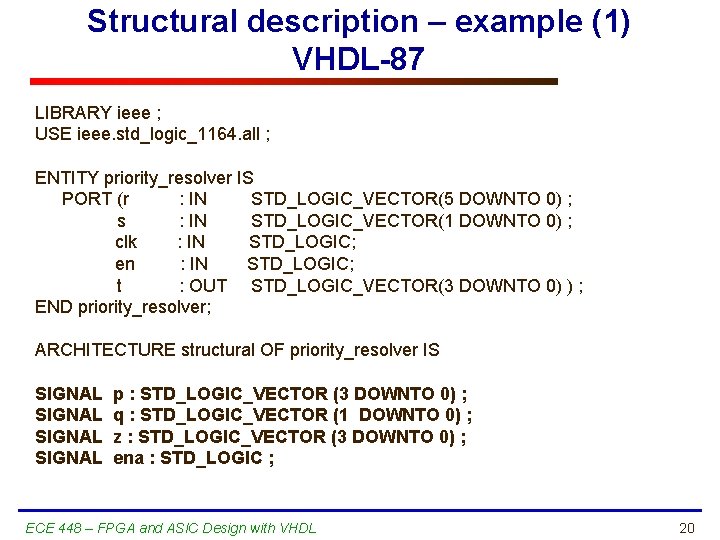

Structural description – example (1) VHDL-87 LIBRARY ieee ; USE ieee. std_logic_1164. all ; ENTITY priority_resolver IS PORT (r : IN STD_LOGIC_VECTOR(5 DOWNTO 0) ; s : IN STD_LOGIC_VECTOR(1 DOWNTO 0) ; clk : IN STD_LOGIC; en : IN STD_LOGIC; t : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ) ; END priority_resolver; ARCHITECTURE structural OF priority_resolver IS SIGNAL p : STD_LOGIC_VECTOR (3 DOWNTO 0) ; q : STD_LOGIC_VECTOR (1 DOWNTO 0) ; z : STD_LOGIC_VECTOR (3 DOWNTO 0) ; ena : STD_LOGIC ; ECE 448 – FPGA and ASIC Design with VHDL 20

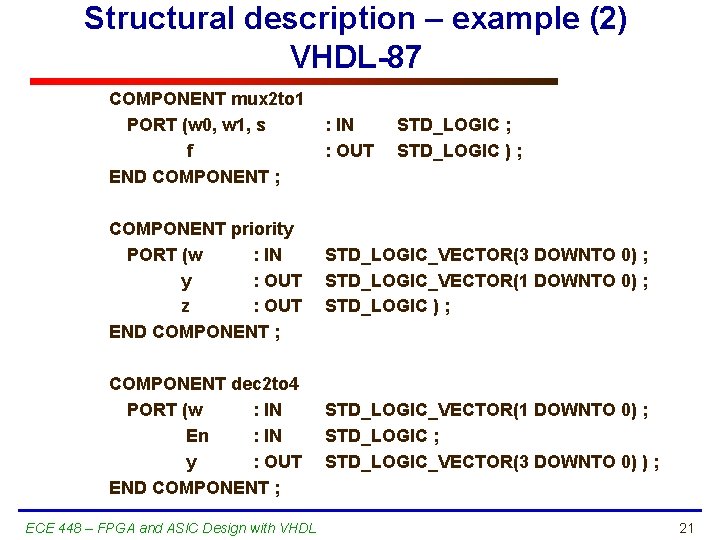

Structural description – example (2) VHDL-87 COMPONENT mux 2 to 1 PORT (w 0, w 1, s f END COMPONENT ; : IN : OUT COMPONENT priority PORT (w : IN y : OUT z : OUT END COMPONENT ; STD_LOGIC_VECTOR(3 DOWNTO 0) ; STD_LOGIC_VECTOR(1 DOWNTO 0) ; STD_LOGIC ) ; COMPONENT dec 2 to 4 PORT (w : IN En : IN y : OUT END COMPONENT ; STD_LOGIC_VECTOR(1 DOWNTO 0) ; STD_LOGIC_VECTOR(3 DOWNTO 0) ) ; ECE 448 – FPGA and ASIC Design with VHDL STD_LOGIC ; STD_LOGIC ) ; 21

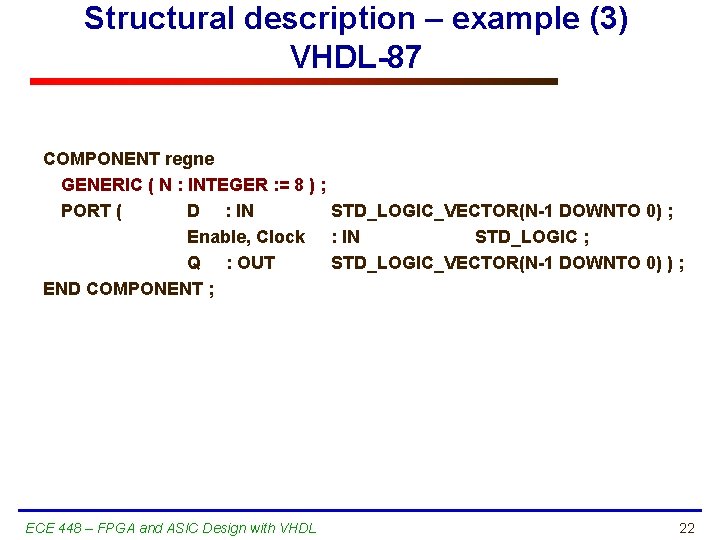

Structural description – example (3) VHDL-87 COMPONENT regne GENERIC ( N : INTEGER : = 8 ) ; PORT ( D : IN STD_LOGIC_VECTOR(N-1 DOWNTO 0) ; Enable, Clock : IN STD_LOGIC ; Q : OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0) ) ; END COMPONENT ; ECE 448 – FPGA and ASIC Design with VHDL 22

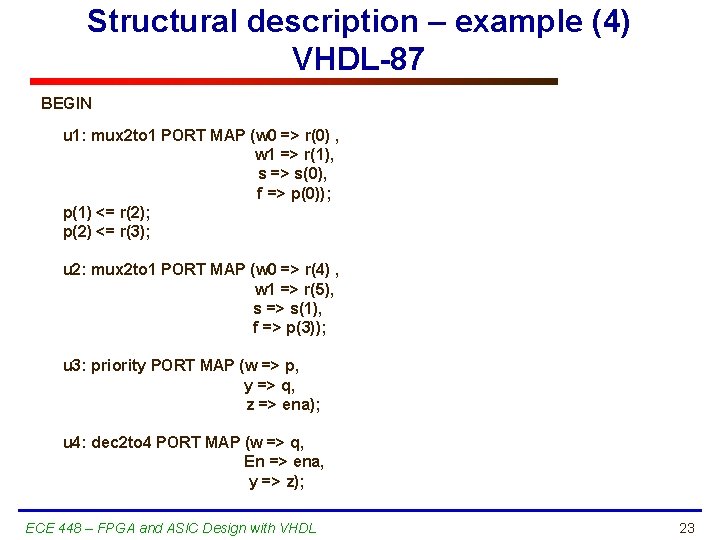

Structural description – example (4) VHDL-87 BEGIN u 1: mux 2 to 1 PORT MAP (w 0 => r(0) , w 1 => r(1), s => s(0), f => p(0)); p(1) <= r(2); p(2) <= r(3); u 2: mux 2 to 1 PORT MAP (w 0 => r(4) , w 1 => r(5), s => s(1), f => p(3)); u 3: priority PORT MAP (w => p, y => q, z => ena); u 4: dec 2 to 4 PORT MAP (w => q, En => ena, y => z); ECE 448 – FPGA and ASIC Design with VHDL 23

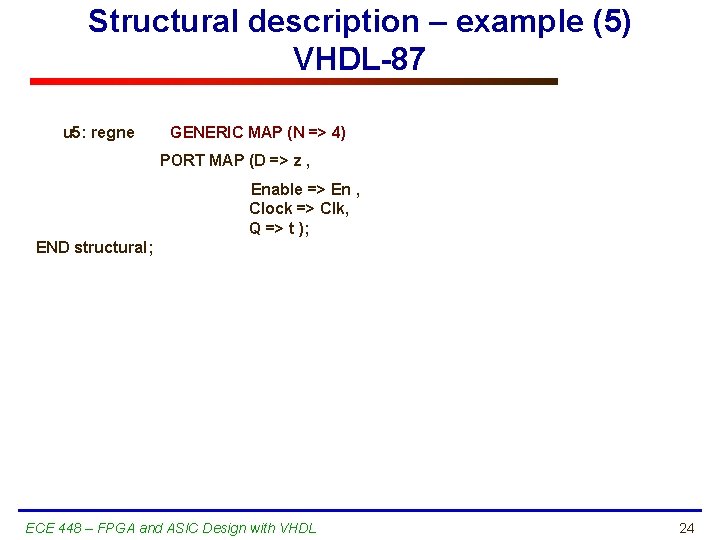

Structural description – example (5) VHDL-87 u 5: regne GENERIC MAP (N => 4) PORT MAP (D => z , Enable => En , Clock => Clk, Q => t ); END structural; ECE 448 – FPGA and ASIC Design with VHDL 24

Mixing Description Styles Inside of an Architecture ECE 448 – FPGA and ASIC Design with VHDL 25

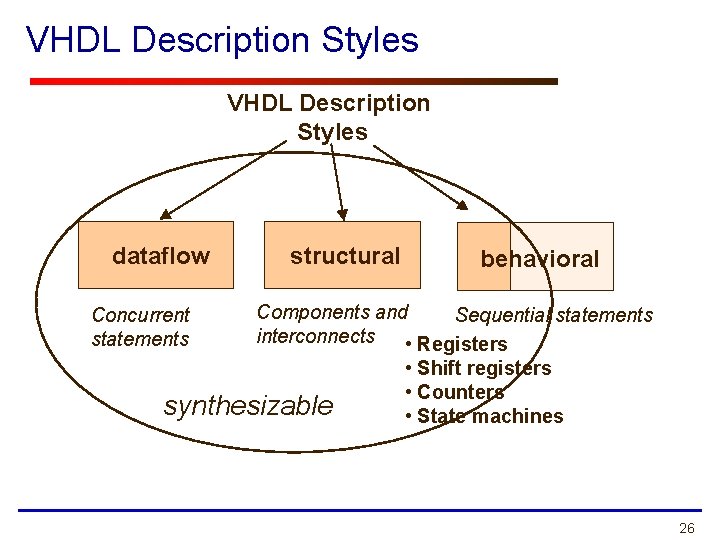

VHDL Description Styles dataflow Concurrent statements structural behavioral Components and Sequential statements interconnects • Registers synthesizable • Shift registers • Counters • State machines 26

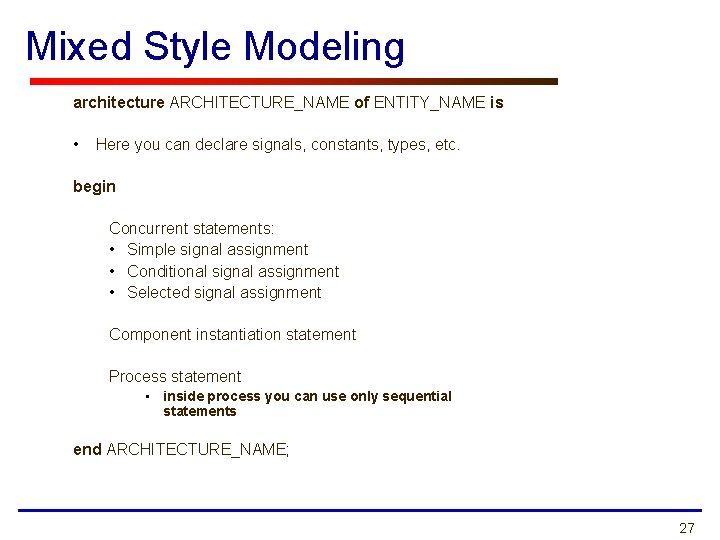

Mixed Style Modeling architecture ARCHITECTURE_NAME of ENTITY_NAME is • Here you can declare signals, constants, types, etc. begin Concurrent statements: • Simple signal assignment • Conditional signal assignment • Selected signal assignment Component instantiation statement Process statement • inside process you can use only sequential statements end ARCHITECTURE_NAME; 27

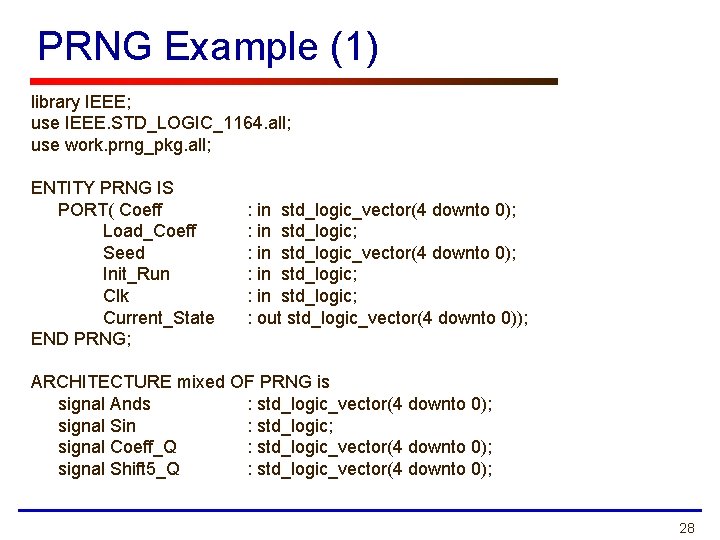

PRNG Example (1) library IEEE; use IEEE. STD_LOGIC_1164. all; use work. prng_pkg. all; ENTITY PRNG IS PORT( Coeff Load_Coeff Seed Init_Run Clk Current_State END PRNG; : in std_logic_vector(4 downto 0); : in std_logic; : out std_logic_vector(4 downto 0)); ARCHITECTURE mixed OF PRNG is signal Ands : std_logic_vector(4 downto 0); signal Sin : std_logic; signal Coeff_Q : std_logic_vector(4 downto 0); signal Shift 5_Q : std_logic_vector(4 downto 0); 28

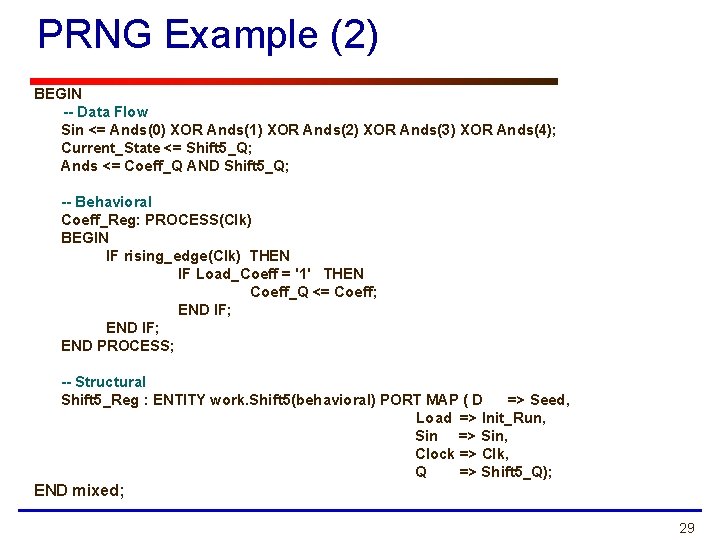

PRNG Example (2) BEGIN -- Data Flow Sin <= Ands(0) XOR Ands(1) XOR Ands(2) XOR Ands(3) XOR Ands(4); Current_State <= Shift 5_Q; Ands <= Coeff_Q AND Shift 5_Q; -- Behavioral Coeff_Reg: PROCESS(Clk) BEGIN IF rising_edge(Clk) THEN IF Load_Coeff = '1' THEN Coeff_Q <= Coeff; END IF; END PROCESS; -- Structural Shift 5_Reg : ENTITY work. Shift 5(behavioral) PORT MAP ( D => Seed, Load => Init_Run, Sin => Sin, Clock => Clk, Q => Shift 5_Q); END mixed; 29

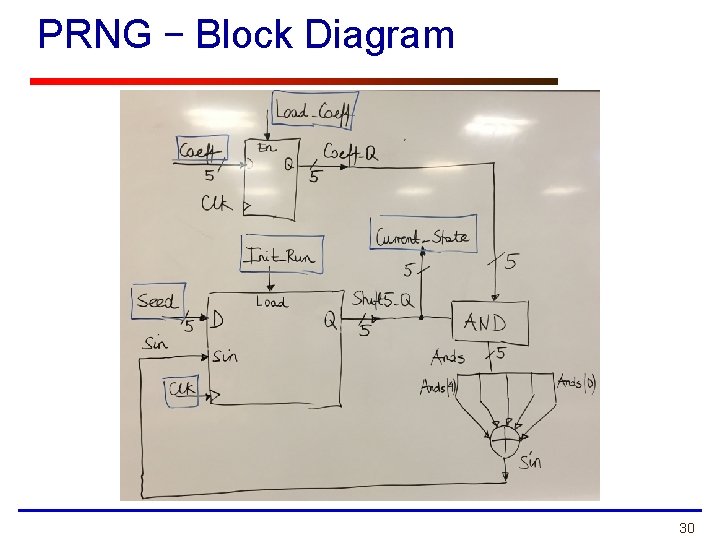

PRNG – Block Diagram 30

Sequential Logic Synthesis for Beginners ECE 448 – FPGA and ASIC Design with VHDL 31

For Beginners Use processes with very simple structure only to describe - registers - shift registers - counters - state machines. Use examples discussed in class as a template. Create generic entities for registers, shift registers, and counters, and instantiate the corresponding components in a higher level circuit using GENERIC MAP PORT MAP. Supplement sequential components with combinational logic described using concurrent statements. 32

Sequential Logic Synthesis for Intermediates ECE 448 – FPGA and ASIC Design with VHDL 33

For Intermmediates 1. 2. 3. Use Processes with IF and CASE statements only. Do not use LOOPS or VARIABLES. Sensitivity list of the PROCESS should include only signals that can by themsleves change the outputs of the sequential circuit (typically, clock and asynchronous set or reset) Do not use PROCESSes without sensitivity list (they can be synthesizable, but make simulation inefficient) 34

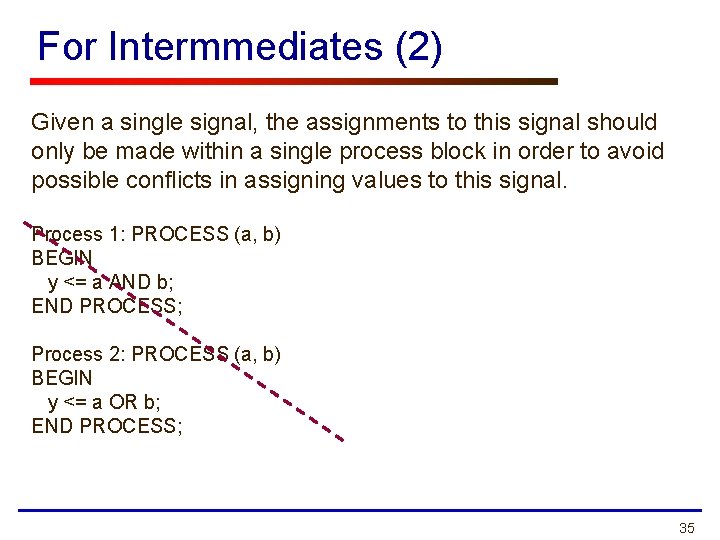

For Intermmediates (2) Given a single signal, the assignments to this signal should only be made within a single process block in order to avoid possible conflicts in assigning values to this signal. Process 1: PROCESS (a, b) BEGIN y <= a AND b; END PROCESS; Process 2: PROCESS (a, b) BEGIN y <= a OR b; END PROCESS; 35

- Slides: 35