ECE 313 Computer Organization Lecture 14 MultiCycle Processor

![Multicycle Execution Step (1) Instruction Fetch IR = Memory[PC]; PC = PC + 4; Multicycle Execution Step (1) Instruction Fetch IR = Memory[PC]; PC = PC + 4;](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-4.jpg)

![Multicycle Execution Step (2) Instruction Decode and Register Fetch A = Reg[IR[25 -21]]; (A Multicycle Execution Step (2) Instruction Decode and Register Fetch A = Reg[IR[25 -21]]; (A](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-5.jpg)

![Multicycle Execution Steps (3) Memory Reference Instructions ALUOut = A + sign-extend(IR[15 -0]); Reg[rs] Multicycle Execution Steps (3) Memory Reference Instructions ALUOut = A + sign-extend(IR[15 -0]); Reg[rs]](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-6.jpg)

![Multicycle Execution Steps (3) ALU Instruction (R-Type) ALUOut = A op B Reg[rs] R-Type Multicycle Execution Steps (3) ALU Instruction (R-Type) ALUOut = A op B Reg[rs] R-Type](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-7.jpg)

![Multicycle Execution Steps (3) Branch Instructions if (A == B) PC = ALUOut; Reg[rs] Multicycle Execution Steps (3) Branch Instructions if (A == B) PC = ALUOut; Reg[rs]](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-8.jpg)

![Multicycle Execution Step (3) Jump Instruction PC = PC[31 -28] concat (IR[25 -0] << Multicycle Execution Step (3) Jump Instruction PC = PC[31 -28] concat (IR[25 -0] <<](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-9.jpg)

![Multicycle Execution Steps (4) Memory Access - Read (lw) MDR = Memory[ALUOut]; Reg[rs] Mem. Multicycle Execution Steps (4) Memory Access - Read (lw) MDR = Memory[ALUOut]; Reg[rs] Mem.](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-10.jpg)

![Multicycle Execution Steps (4) Memory Access - Write (sw) Memory[ALUOut] = B; Reg[rs] PC Multicycle Execution Steps (4) Memory Access - Write (sw) Memory[ALUOut] = B; Reg[rs] PC](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-11.jpg)

![Multicycle Execution Steps (4) ALU Instruction (R-Type) Reg[IR[15: 11]] = ALUOUT Reg[rs] R-Type Result Multicycle Execution Steps (4) ALU Instruction (R-Type) Reg[IR[15: 11]] = ALUOUT Reg[rs] R-Type Result](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-12.jpg)

![Multicycle Execution Steps (5) Memory Read Completion (lw) Reg[IR[20 -16]] = MDR; Reg[rs] Mem. Multicycle Execution Steps (5) Memory Read Completion (lw) Reg[IR[20 -16]] = MDR; Reg[rs] Mem.](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-13.jpg)

- Slides: 19

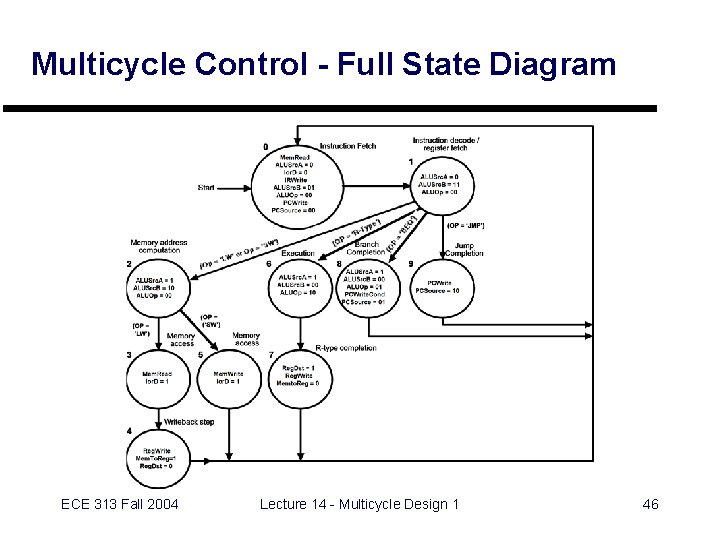

ECE 313 - Computer Organization Lecture 14 - Multi-Cycle Processor Design 1 Fall 2004 Reading: 5. 5 Prof. John Nestor ECE Department Lafayette College Easton, Pennsylvania 18042 nestorj@lafayette. edu Portions of these slides are derived from: Textbook figures © 1998 Morgan Kaufmann Publishers all rights reserved Tod Amon's COD 2 e Slides © 1998 Morgan Kaufmann Publishers all rights reserved Dave Patterson’s CS 152 Slides - Fall 1997 © UCB Rob Rutenbar’s 18 -347 Slides - Fall 1999 CMU ECE 313 Fall 2004 Lecture 14 - Multicycle Design other sources as noted 1 1

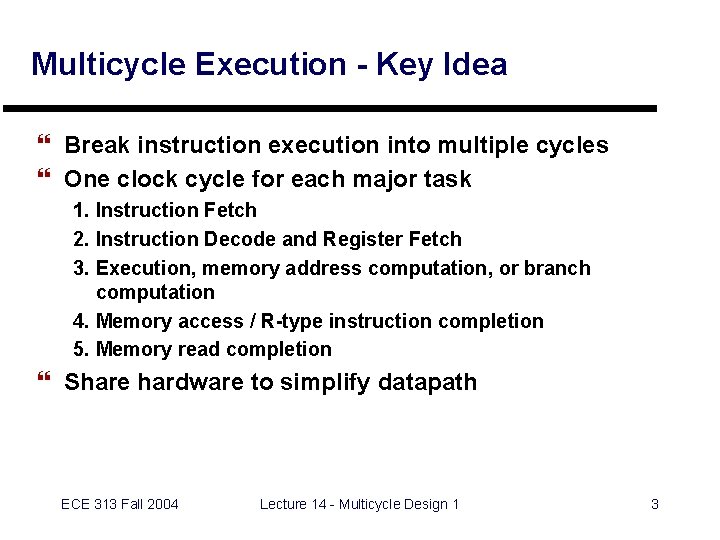

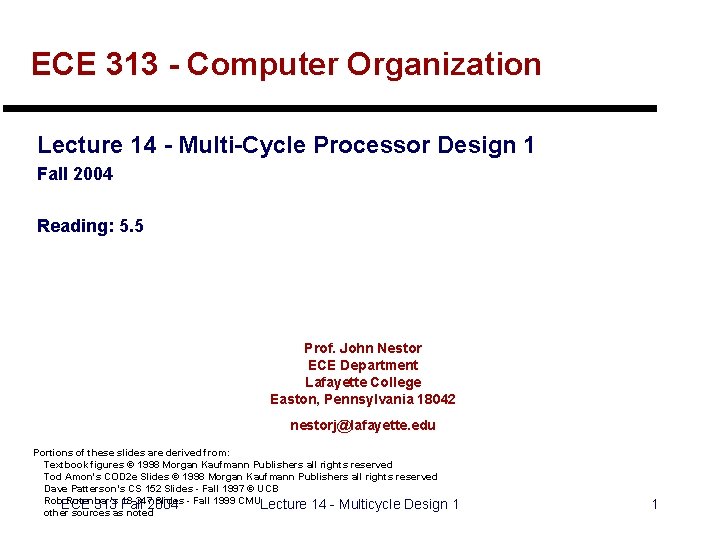

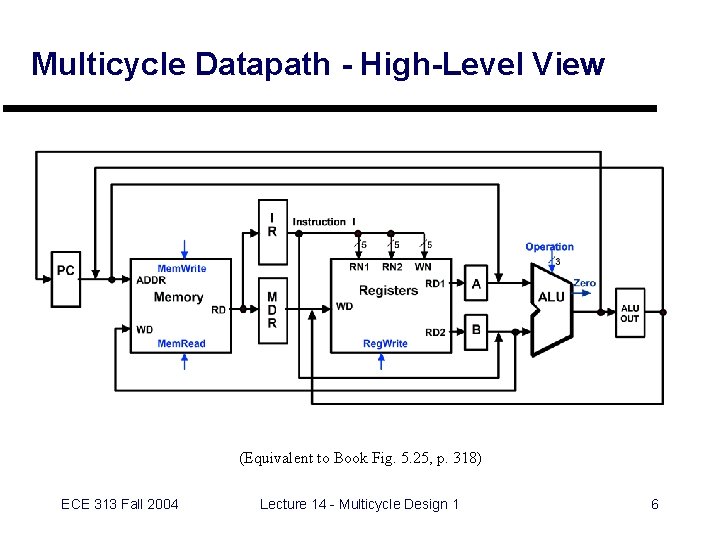

Multicycle Execution - Key Idea } Break instruction execution into multiple cycles } One clock cycle for each major task 1. Instruction Fetch 2. Instruction Decode and Register Fetch 3. Execution, memory address computation, or branch computation 4. Memory access / R-type instruction completion 5. Memory read completion } Share hardware to simplify datapath ECE 313 Fall 2004 Lecture 14 - Multicycle Design 1 3

Multicycle Datapath - High-Level View (Equivalent to Book Fig. 5. 25, p. 318) ECE 313 Fall 2004 Lecture 14 - Multicycle Design 1 6

![Multicycle Execution Step 1 Instruction Fetch IR MemoryPC PC PC 4 Multicycle Execution Step (1) Instruction Fetch IR = Memory[PC]; PC = PC + 4;](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-4.jpg)

Multicycle Execution Step (1) Instruction Fetch IR = Memory[PC]; PC = PC + 4; 4 PC + 4 ECE 313 Fall 2004 Lecture 14 - Multicycle Design 1 11

![Multicycle Execution Step 2 Instruction Decode and Register Fetch A RegIR25 21 A Multicycle Execution Step (2) Instruction Decode and Register Fetch A = Reg[IR[25 -21]]; (A](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-5.jpg)

Multicycle Execution Step (2) Instruction Decode and Register Fetch A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 -15]]; (B = Reg[rt]) ALUOut = (PC + sign-extend(IR[15 -0]) << 2) Reg[rs] Branch Target Address PC + 4 Reg[rt] ECE 313 Fall 2004 Lecture 14 - Multicycle Design 1 12

![Multicycle Execution Steps 3 Memory Reference Instructions ALUOut A signextendIR15 0 Regrs Multicycle Execution Steps (3) Memory Reference Instructions ALUOut = A + sign-extend(IR[15 -0]); Reg[rs]](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-6.jpg)

Multicycle Execution Steps (3) Memory Reference Instructions ALUOut = A + sign-extend(IR[15 -0]); Reg[rs] Mem. Address PC + 4 Reg[rt] ECE 313 Fall 2004 Lecture 14 - Multicycle Design 1 13

![Multicycle Execution Steps 3 ALU Instruction RType ALUOut A op B Regrs RType Multicycle Execution Steps (3) ALU Instruction (R-Type) ALUOut = A op B Reg[rs] R-Type](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-7.jpg)

Multicycle Execution Steps (3) ALU Instruction (R-Type) ALUOut = A op B Reg[rs] R-Type Result PC + 4 Reg[rt] ECE 313 Fall 2004 Lecture 14 - Multicycle Design 1 14

![Multicycle Execution Steps 3 Branch Instructions if A B PC ALUOut Regrs Multicycle Execution Steps (3) Branch Instructions if (A == B) PC = ALUOut; Reg[rs]](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-8.jpg)

Multicycle Execution Steps (3) Branch Instructions if (A == B) PC = ALUOut; Reg[rs] Branch Target Address ECE 313 Fall 2004 Branch Target Address Reg[rt] Lecture 14 - Multicycle Design 1 15

![Multicycle Execution Step 3 Jump Instruction PC PC31 28 concat IR25 0 Multicycle Execution Step (3) Jump Instruction PC = PC[31 -28] concat (IR[25 -0] <<](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-9.jpg)

Multicycle Execution Step (3) Jump Instruction PC = PC[31 -28] concat (IR[25 -0] << 2) Reg[rs] Branch Target Address Jump Address Reg[rt] ECE 313 Fall 2004 Lecture 14 - Multicycle Design 1 16

![Multicycle Execution Steps 4 Memory Access Read lw MDR MemoryALUOut Regrs Mem Multicycle Execution Steps (4) Memory Access - Read (lw) MDR = Memory[ALUOut]; Reg[rs] Mem.](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-10.jpg)

Multicycle Execution Steps (4) Memory Access - Read (lw) MDR = Memory[ALUOut]; Reg[rs] Mem. Address PC + 4 Mem. Data ECE 313 Fall 2004 Reg[rt] Lecture 14 - Multicycle Design 1 17

![Multicycle Execution Steps 4 Memory Access Write sw MemoryALUOut B Regrs PC Multicycle Execution Steps (4) Memory Access - Write (sw) Memory[ALUOut] = B; Reg[rs] PC](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-11.jpg)

Multicycle Execution Steps (4) Memory Access - Write (sw) Memory[ALUOut] = B; Reg[rs] PC + 4 Reg[rt] ECE 313 Fall 2004 Lecture 14 - Multicycle Design 1 18

![Multicycle Execution Steps 4 ALU Instruction RType RegIR15 11 ALUOUT Regrs RType Result Multicycle Execution Steps (4) ALU Instruction (R-Type) Reg[IR[15: 11]] = ALUOUT Reg[rs] R-Type Result](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-12.jpg)

Multicycle Execution Steps (4) ALU Instruction (R-Type) Reg[IR[15: 11]] = ALUOUT Reg[rs] R-Type Result PC + 4 Reg[rt] ECE 313 Fall 2004 Lecture 14 - Multicycle Design 1 19

![Multicycle Execution Steps 5 Memory Read Completion lw RegIR20 16 MDR Regrs Mem Multicycle Execution Steps (5) Memory Read Completion (lw) Reg[IR[20 -16]] = MDR; Reg[rs] Mem.](https://slidetodoc.com/presentation_image_h/0c059515a7f232e0062558a4122143db/image-13.jpg)

Multicycle Execution Steps (5) Memory Read Completion (lw) Reg[IR[20 -16]] = MDR; Reg[rs] Mem. Address PC + 4 Mem. Data ECE 313 Fall 2004 Reg[rt] Lecture 14 - Multicycle Design 1 20

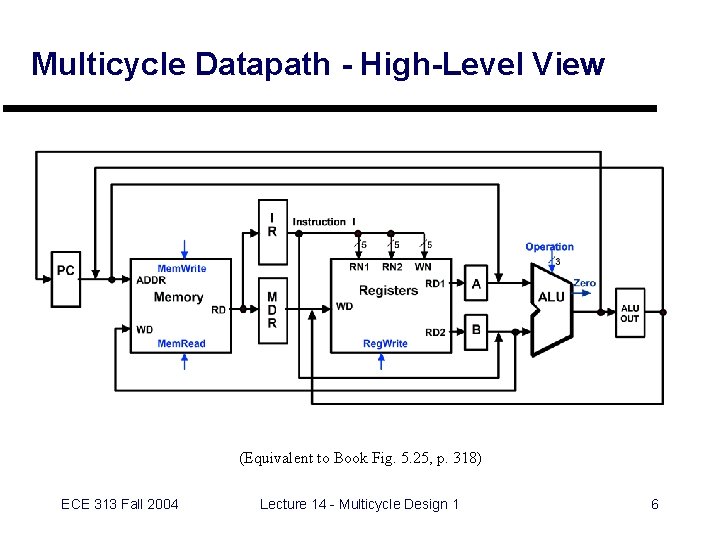

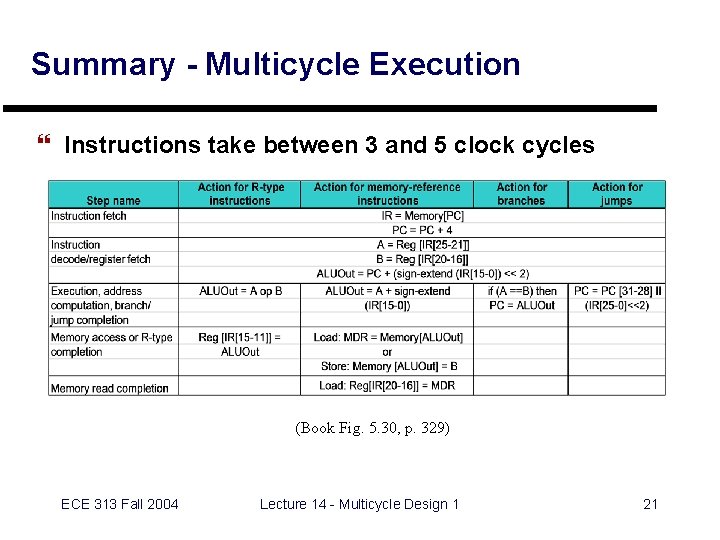

Summary - Multicycle Execution } Instructions take between 3 and 5 clock cycles (Book Fig. 5. 30, p. 329) ECE 313 Fall 2004 Lecture 14 - Multicycle Design 1 21

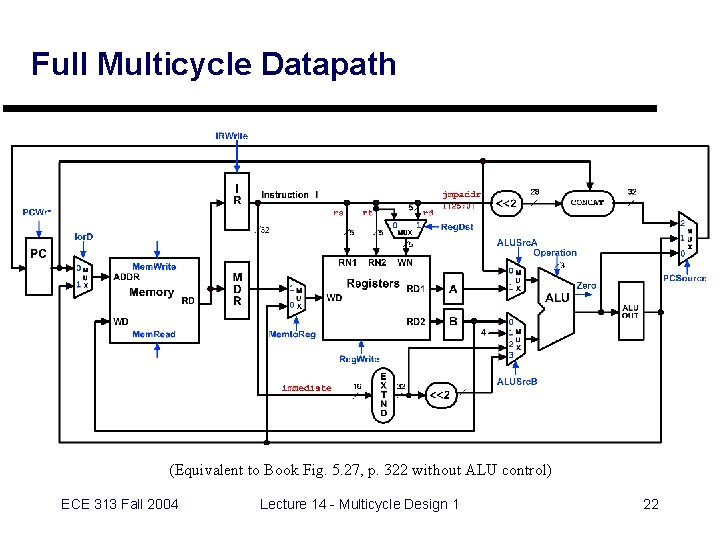

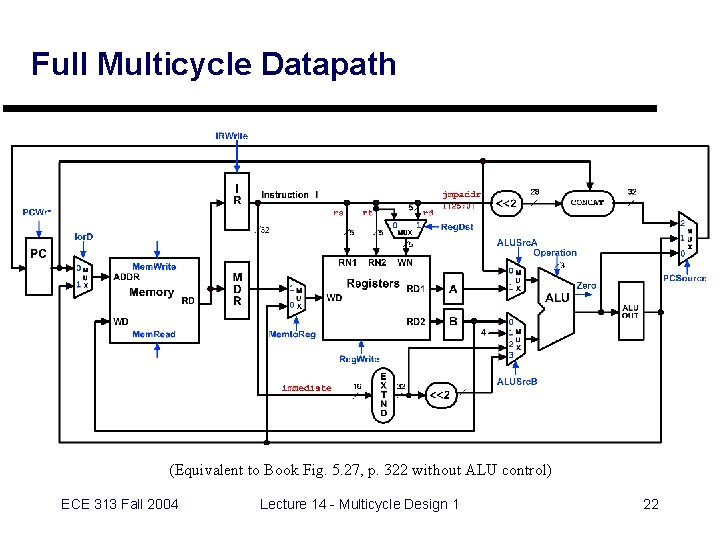

Full Multicycle Datapath (Equivalent to Book Fig. 5. 27, p. 322 without ALU control) ECE 313 Fall 2004 Lecture 14 - Multicycle Design 1 22

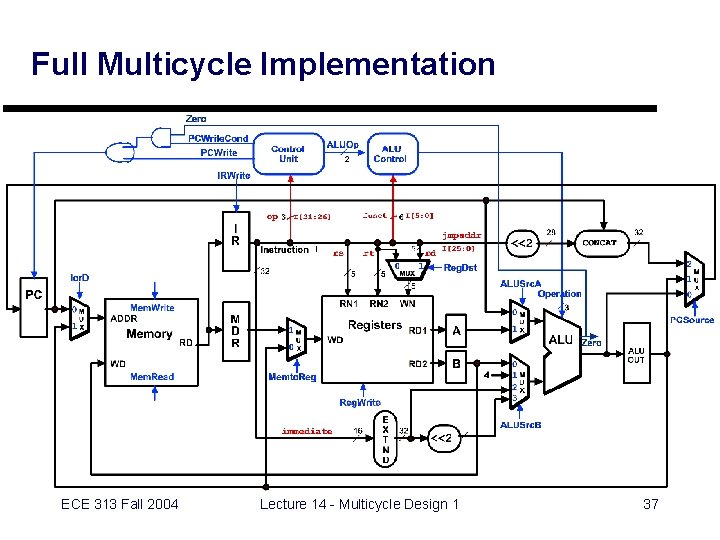

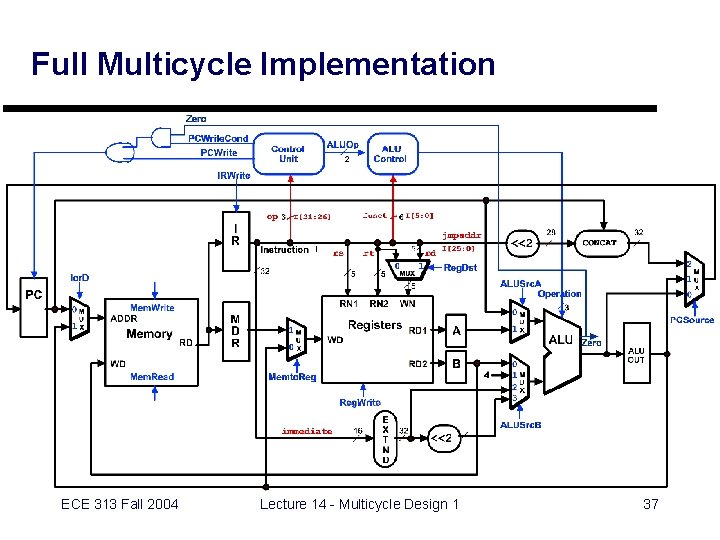

Full Multicycle Implementation ECE 313 Fall 2004 Lecture 14 - Multicycle Design 1 37

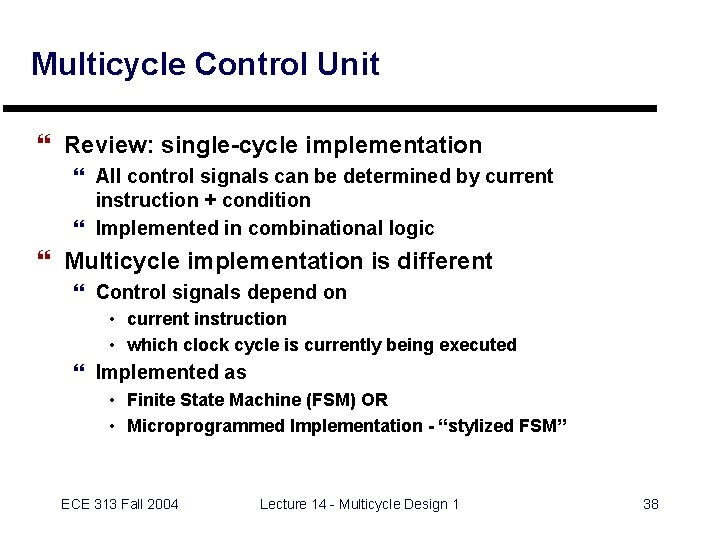

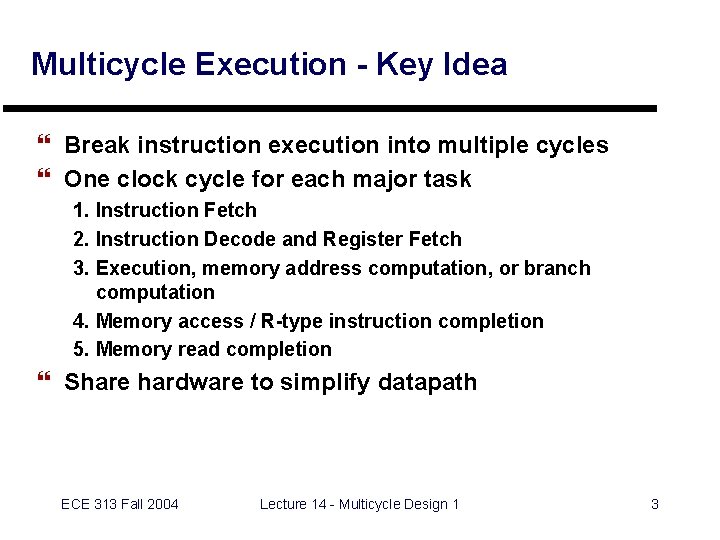

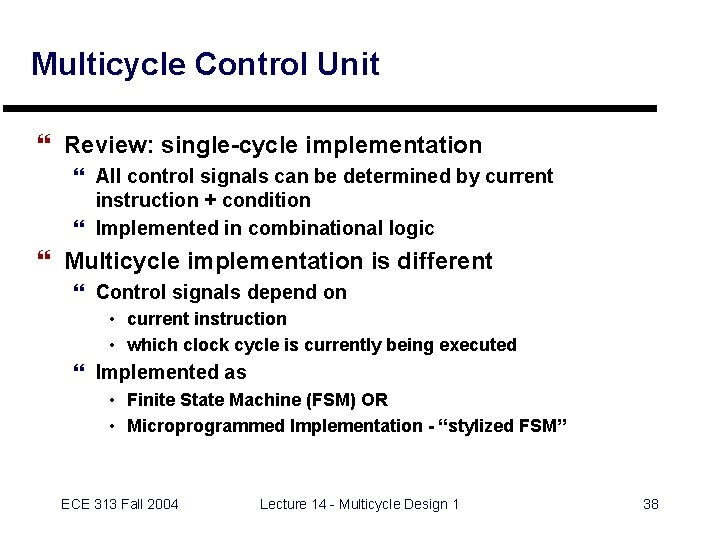

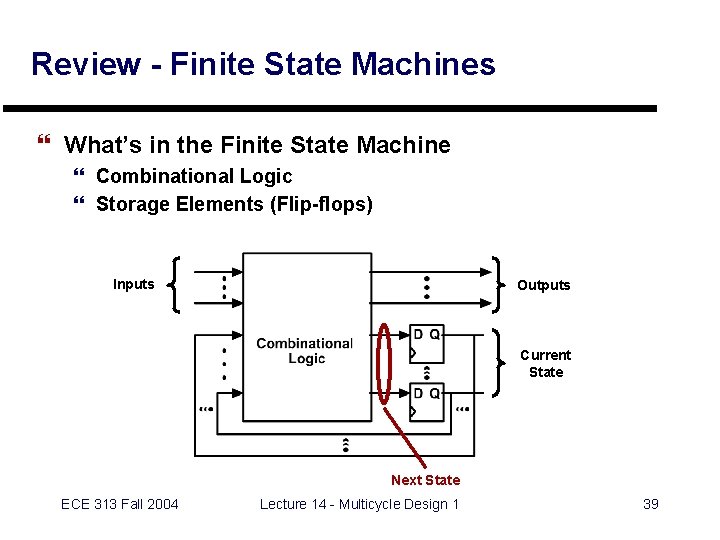

Multicycle Control Unit } Review: single-cycle implementation } All control signals can be determined by current instruction + condition } Implemented in combinational logic } Multicycle implementation is different } Control signals depend on • current instruction • which clock cycle is currently being executed } Implemented as • Finite State Machine (FSM) OR • Microprogrammed Implementation - “stylized FSM” ECE 313 Fall 2004 Lecture 14 - Multicycle Design 1 38

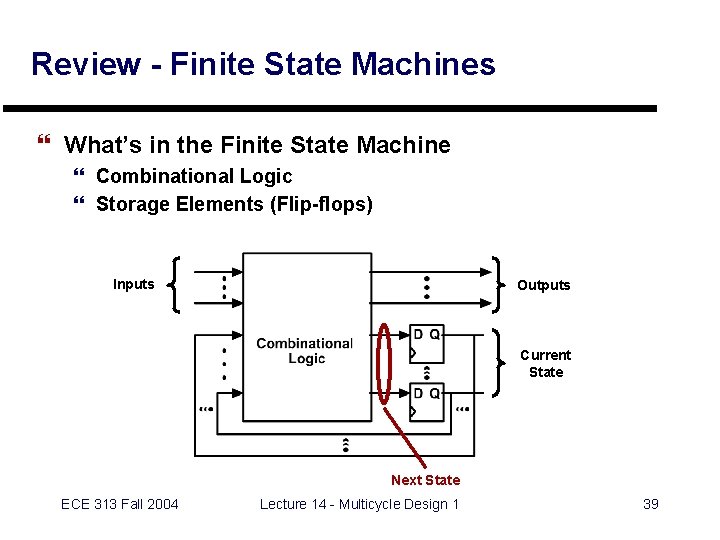

Review - Finite State Machines } What’s in the Finite State Machine } Combinational Logic } Storage Elements (Flip-flops) Inputs Outputs Current State Next State ECE 313 Fall 2004 Lecture 14 - Multicycle Design 1 39

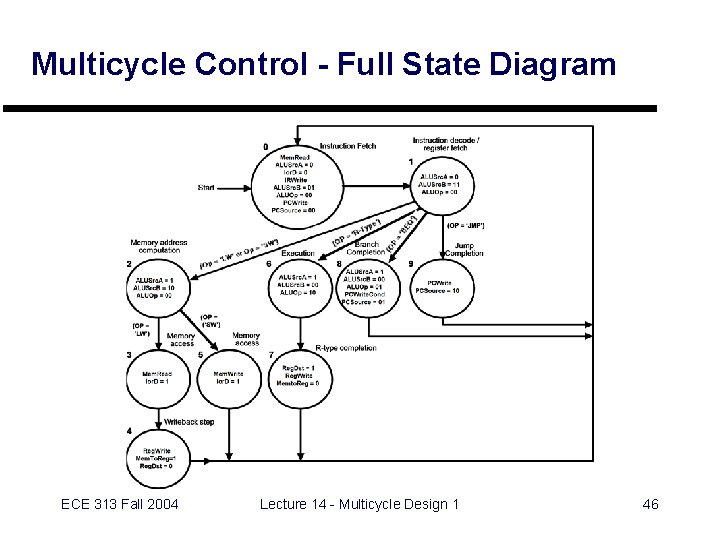

Multicycle Control - Full State Diagram ECE 313 Fall 2004 Lecture 14 - Multicycle Design 1 46