ECE 313 Computer Organization Lecture 3 Instruction Sets

- Slides: 16

ECE 313 - Computer Organization Lecture 3 - Instruction Sets Fall 2004 Reading: 2. 1 -2. 2 Prof. John Nestor ECE Department Lafayette College Easton, Pennsylvania 18042 nestorj@lafayette. edu Portions of these slides are derived from: Textbook figures © 1998 Morgan Kaufmann Publishers all rights reserved Tod Amon's COD 2 e Slides © 1998 Morgan Kaufmann Publishers all rights reserved Dave Patterson’s CS 152 Slides - Fall 1997 © UCB Rob Rutenbar’s 18 -347 Slides - Fall 1999 CMU ECE 313 - Fall 2004 Lecture 3 - Instruction Sets other sources as noted 1

Roadmap for the Term: Major Topics } } } } Computer Systems Overview Technology Trends Instruction Sets (and Software) Logic and Arithmetic Performance Processor Implementation Memory Systems Input/Output ECE 313 - Fall 2004 Lecture 3 - Instruction Sets 2

Outline - Instruction Sets } Instruction Set Overview } Classifying Instruction Set Architectures (ISAs) } Some Example Architectures } CISC vs. RISC Architectures } MIPS Instruction Set } Software Concerns ECE 313 - Fall 2004 Lecture 3 - Instruction Sets 3

What does an ISA Specify? } Supported data types (e. g. byte, short, word, long, float, double) } Memory organization } Registers } Instructions } Function } Operands - number and type • Memory operands • Register operands } Format and encoding ECE 313 - Fall 2004 Lecture 3 - Instruction Sets 5

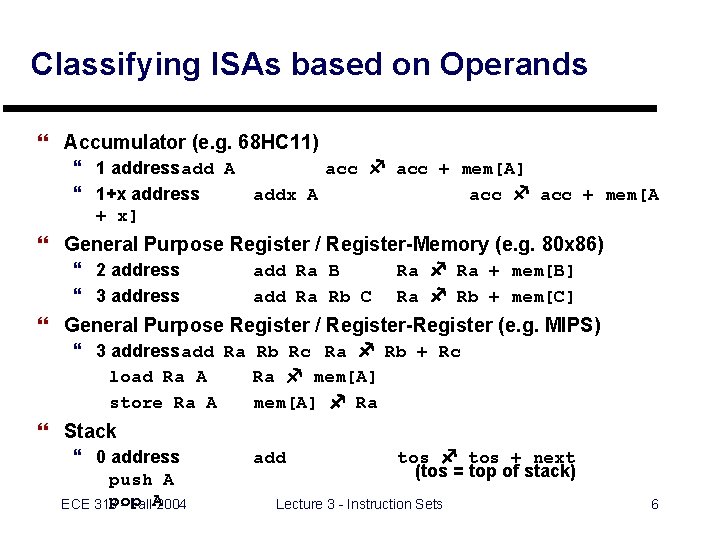

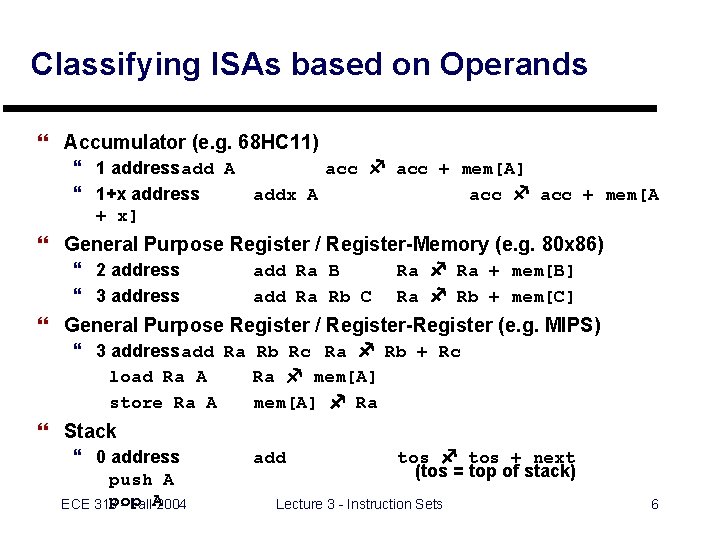

Classifying ISAs based on Operands } Accumulator (e. g. 68 HC 11) } 1 addressadd A acc f acc + mem[A] } 1+x address addx A acc f acc + mem[A + x] } General Purpose Register / Register-Memory (e. g. 80 x 86) } 2 address } 3 address add Ra B add Ra Rb C Ra f Ra + mem[B] Ra f Rb + mem[C] } General Purpose Register / Register-Register (e. g. MIPS) } 3 addressadd Ra Rb Rc Ra f Rb + Rc load Ra A Ra f mem[A] store Ra A mem[A] f Ra } Stack } 0 address push A pop ECE 313 - Fall. A 2004 add tos f tos + next (tos = top of stack) Lecture 3 - Instruction Sets 6

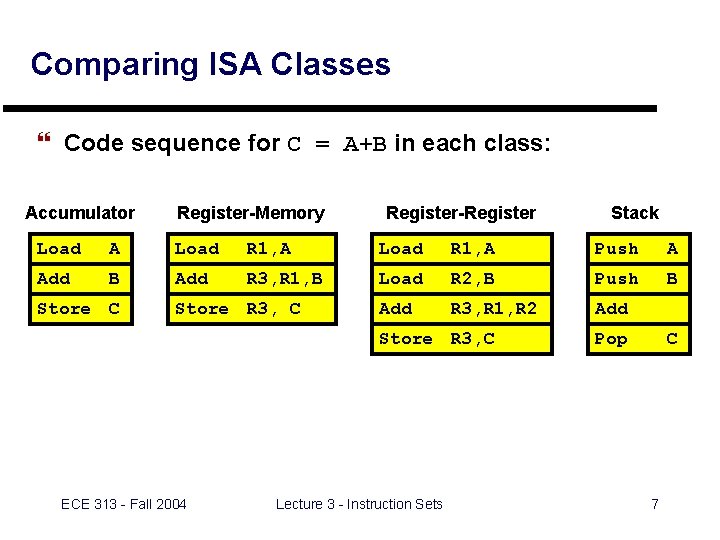

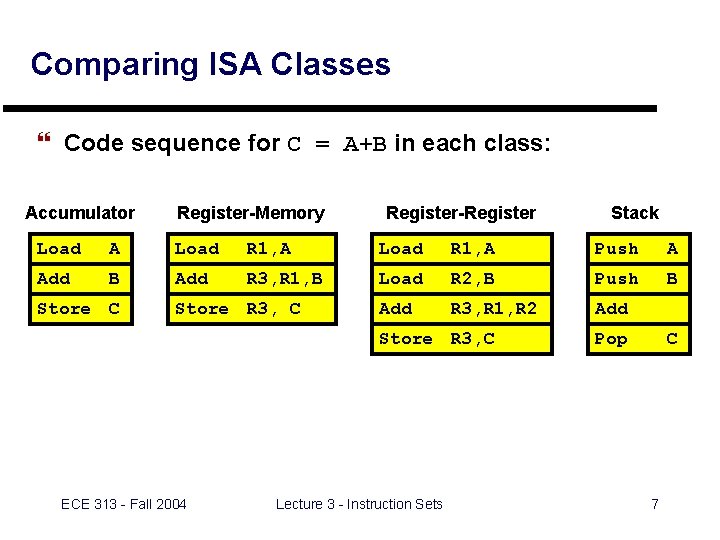

Comparing ISA Classes } Code sequence for C = A+B in each class: Accumulator Register-Memory Register-Register Stack Load A Load R 1, A Push A Add B Add R 3, R 1, B Load R 2, B Push B Store C Store R 3, C Add R 3, R 1, R 2 Add Store R 3, C Pop ECE 313 - Fall 2004 Lecture 3 - Instruction Sets C 7

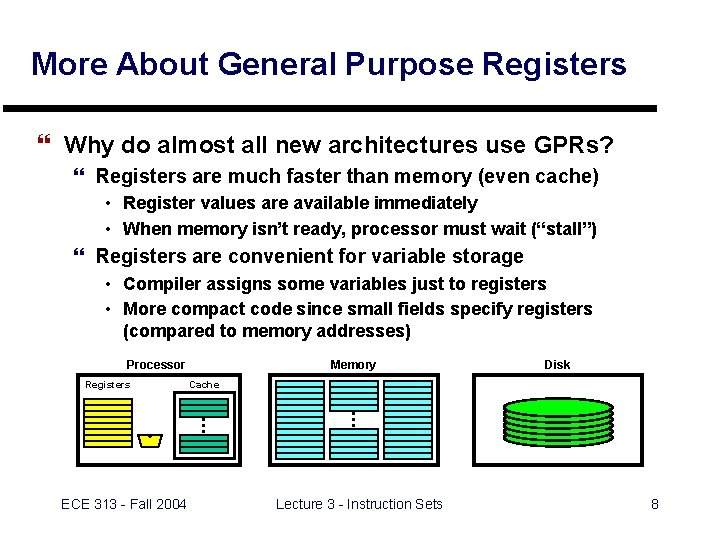

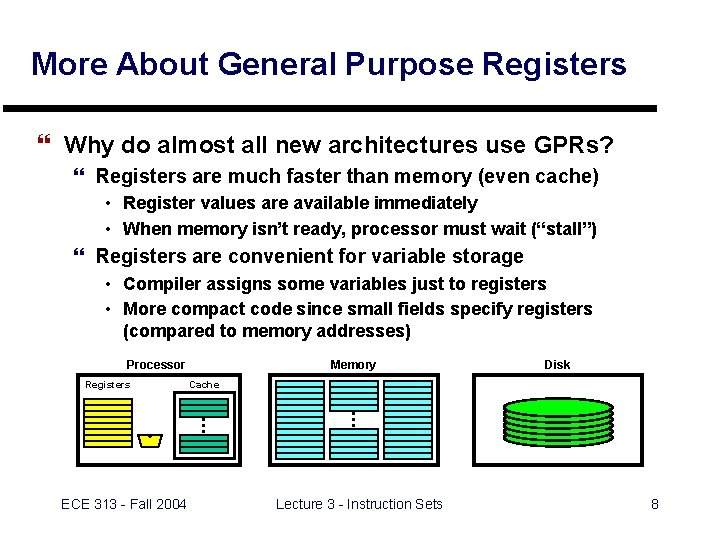

More About General Purpose Registers } Why do almost all new architectures use GPRs? } Registers are much faster than memory (even cache) • Register values are available immediately • When memory isn’t ready, processor must wait (“stall”) } Registers are convenient for variable storage • Compiler assigns some variables just to registers • More compact code since small fields specify registers (compared to memory addresses) Processor Registers ECE 313 - Fall 2004 Memory Disk Cache Lecture 3 - Instruction Sets 8

Outline - Instruction Sets } Instruction Set Overview } Classifying Instruction Set Architectures (ISAs) } Some Example Architectures } CISC vs. RISC Architectures } MIPS Instruction Set } Software Concerns ECE 313 - Fall 2004 Lecture 3 - Instruction Sets 9

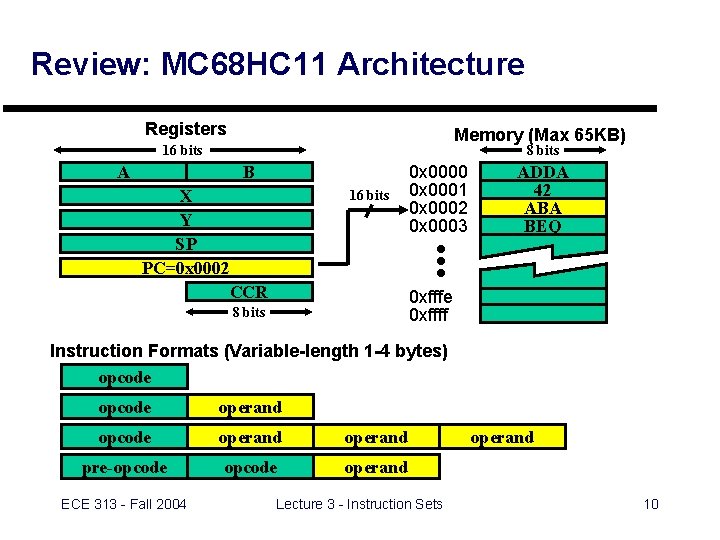

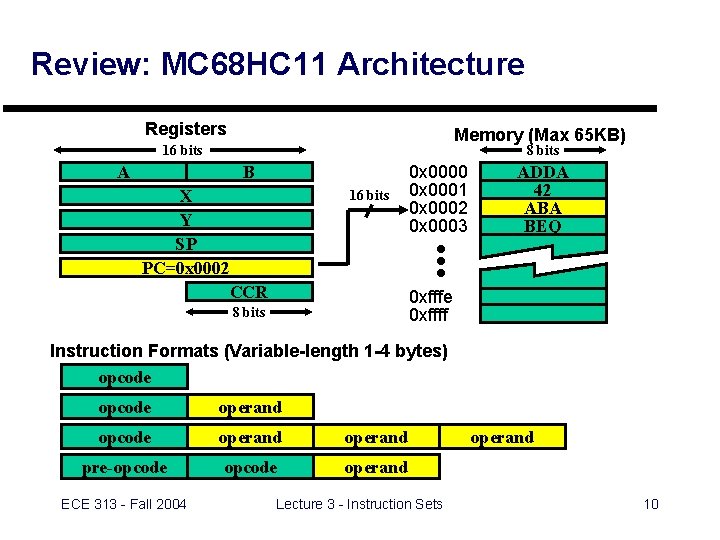

Review: MC 68 HC 11 Architecture Registers Memory (Max 65 KB) 16 bits A 8 bits B X Y SP PC=0 x 0002 CCR 16 bits 0 x 0000 0 x 0001 0 x 0002 0 x 0003 ADDA 42 ABA BEQ 0 xfffe 0 xffff 8 bits Instruction Formats (Variable-length 1 -4 bytes) opcode operand pre-opcode operand ECE 313 - Fall 2004 Lecture 3 - Instruction Sets operand 10

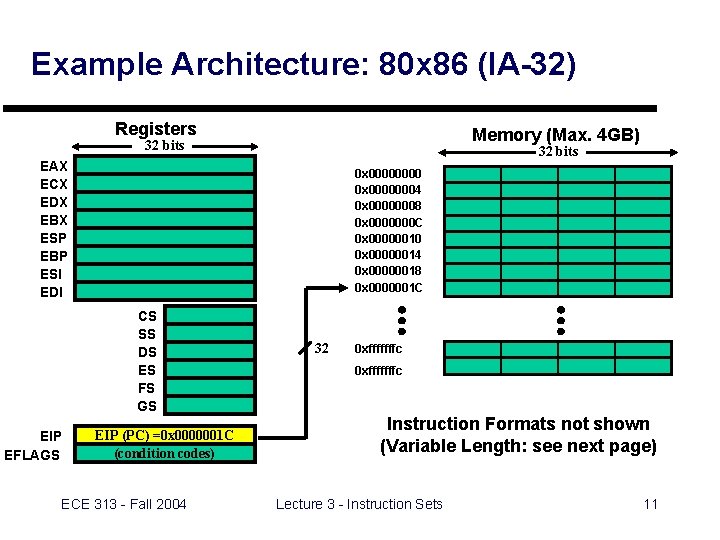

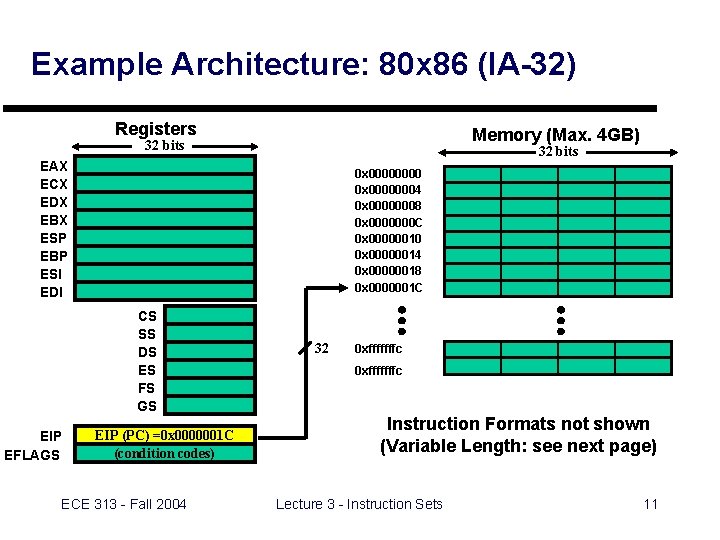

Example Architecture: 80 x 86 (IA-32) Registers Memory (Max. 4 GB) 32 bits EAX ECX EDX EBX ESP EBP ESI EDI 0 x 00000004 0 x 00000008 0 x 0000000 C 0 x 00000010 0 x 00000014 0 x 00000018 0 x 0000001 C CS SS DS ES FS GS EIP EFLAGS EIP (PC) =0 x 0000001 C (condition codes) ECE 313 - Fall 2004 32 0 xfffffffc Instruction Formats not shown (Variable Length: see next page) Lecture 3 - Instruction Sets 11

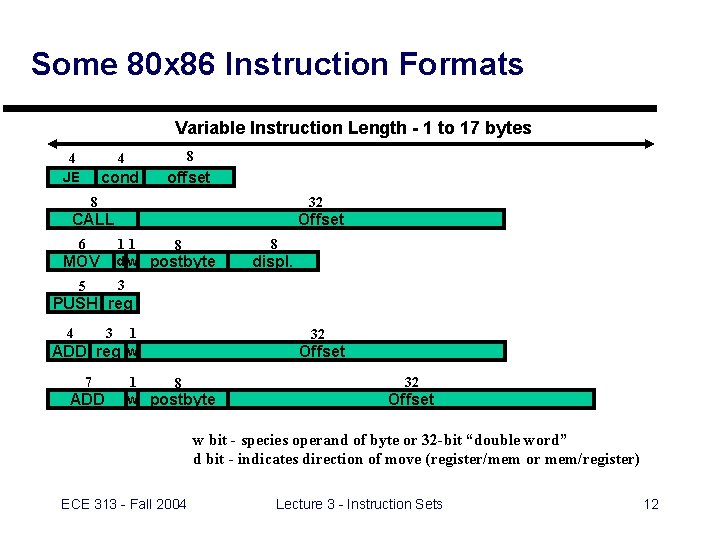

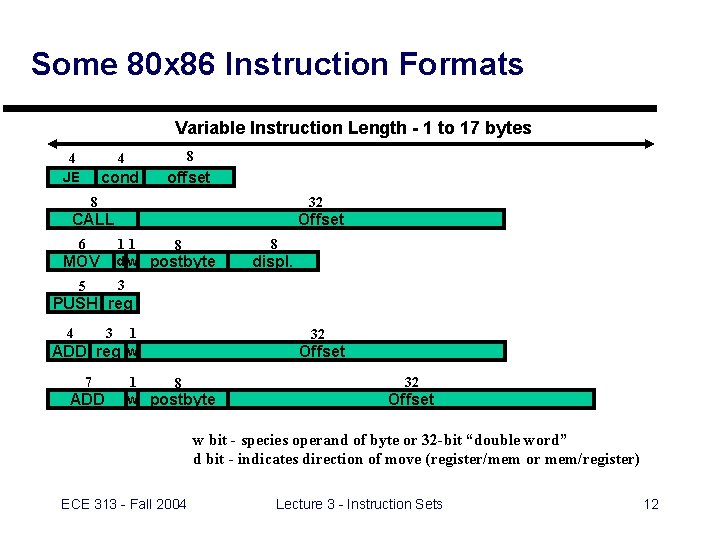

Some 80 x 86 Instruction Formats Variable Instruction Length - 1 to 17 bytes 4 JE 4 8 cond offset 8 32 CALL 6 Offset 11 8 d w postbyte MOV 8 displ. 3 5 PUSH reg 4 1 ADD reg w 3 7 ADD 32 Offset 1 8 w postbyte 32 Offset w bit - species operand of byte or 32 -bit “double word” d bit - indicates direction of move (register/mem or mem/register) ECE 313 - Fall 2004 Lecture 3 - Instruction Sets 12

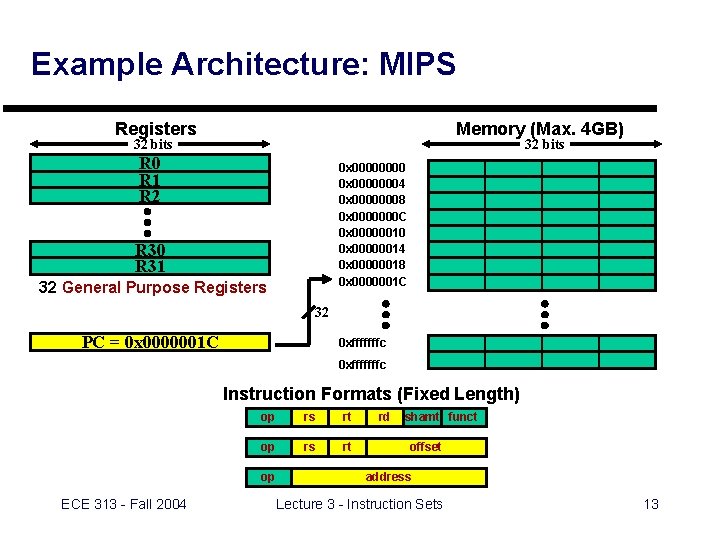

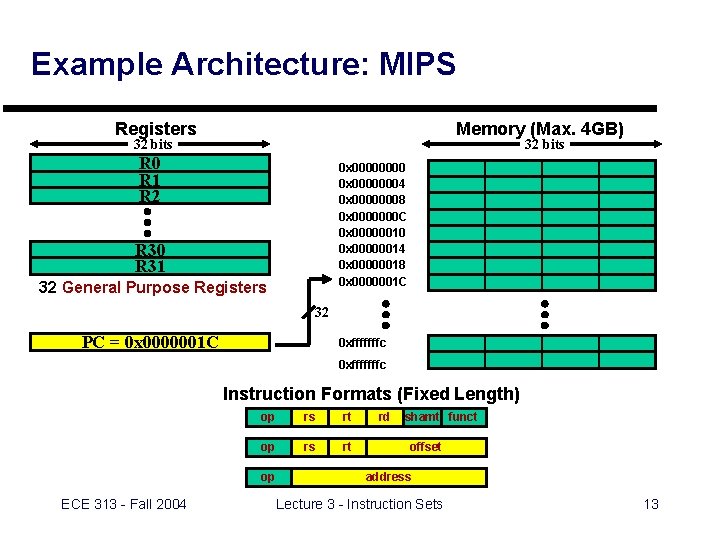

Example Architecture: MIPS Registers Memory (Max. 4 GB) 32 bits R 0 R 1 R 2 0 x 00000004 0 x 00000008 0 x 0000000 C 0 x 00000010 0 x 00000014 0 x 00000018 0 x 0000001 C R 30 R 31 32 General Purpose Registers 32 PC = 0 x 0000001 C 0 xfffffffc Instruction Formats (Fixed Length) op rs rt op ECE 313 - Fall 2004 rd shamt funct offset address Lecture 3 - Instruction Sets 13

Outline - Instruction Sets } Instruction Set Overview } Classifying Instruction Set Architectures (ISAs) } Some Example Architectures } CISC vs. RISC Architectures } MIPS Instruction Set } Software Concerns ECE 313 - Fall 2004 Lecture 3 - Instruction Sets 14

Classifying Architectures: CISC vs. RISC } CISC - Complex Instruction Set } Usually evolved over time (e. g. 8080 ->8086 ->IA-32) } Many instructions targeted to high-level functions } Large number of instruction formats and instructions } RISC - Reduced-Instruction Set Computers } Small number of fixed length instruction formats } Limited access to memory (load/store architecture) Instructions chosen to make implementation easier, faster } Rely on compiler for higher-level functions } Over time, the distinction has blurred ECE 313 - Fall 2004 Lecture 3 - Instruction Sets 15

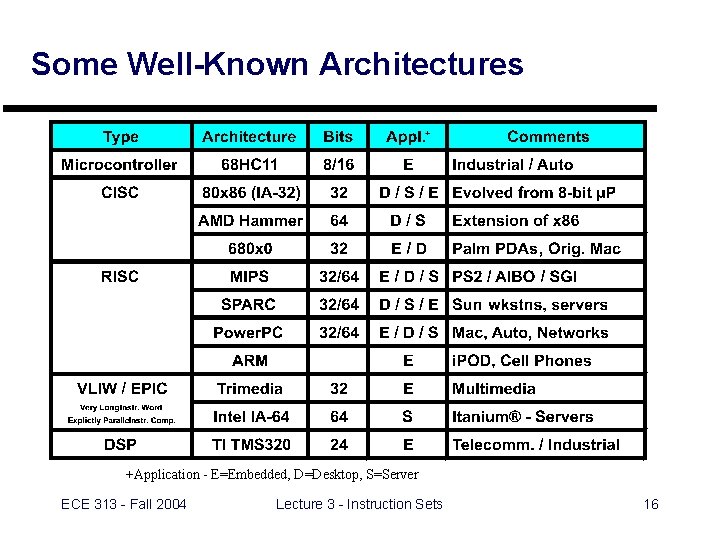

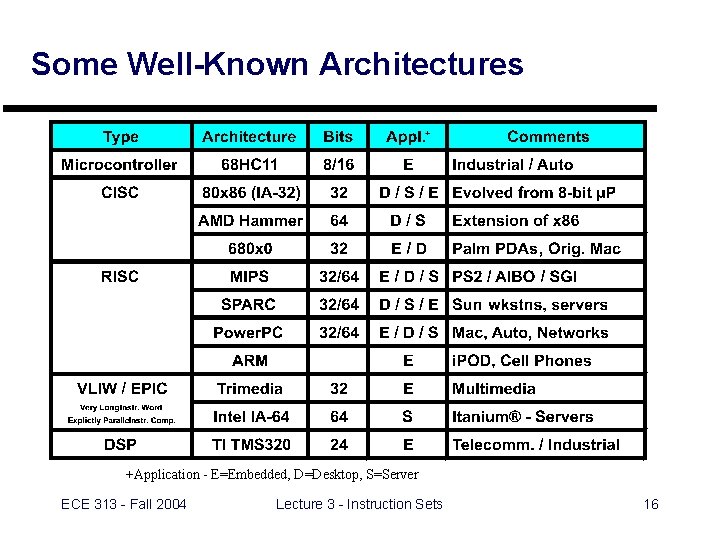

Some Well-Known Architectures +Application - E=Embedded, D=Desktop, S=Server ECE 313 - Fall 2004 Lecture 3 - Instruction Sets 16

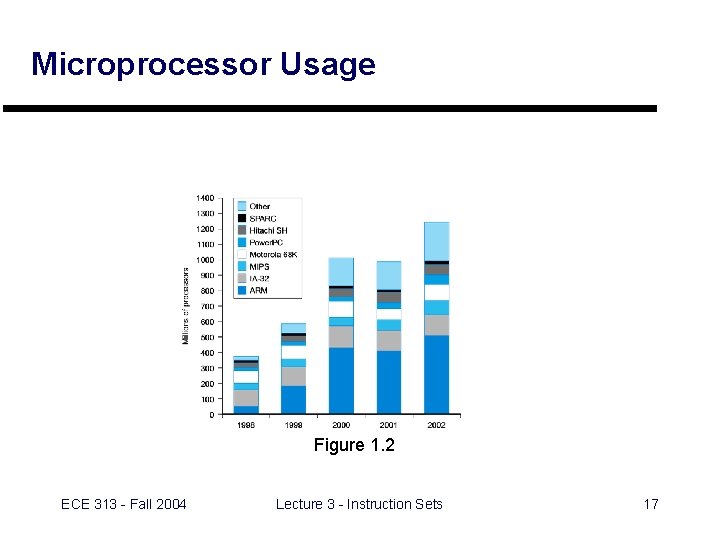

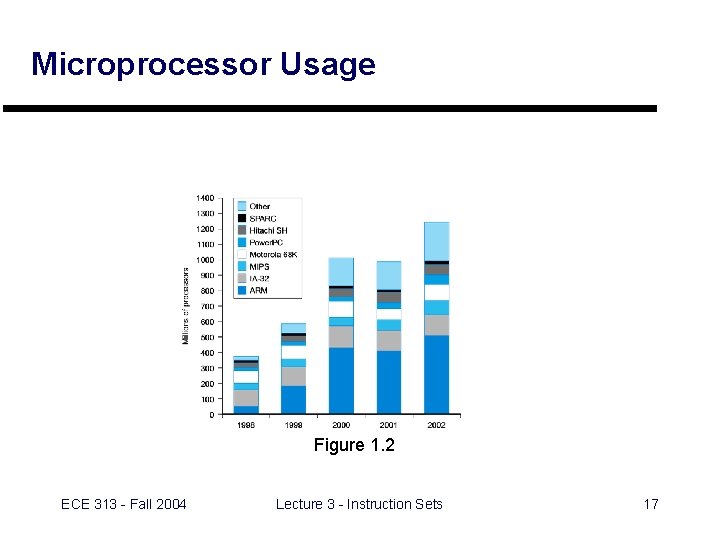

Microprocessor Usage Figure 1. 2 ECE 313 - Fall 2004 Lecture 3 - Instruction Sets 17