Digital Systems Lecture 10 Dr Ing Erwin Sitompul

- Slides: 32

Digital Systems Lecture 10 Dr. -Ing. Erwin Sitompul President University http: //zitompul. wordpress. com 2 0 1 7 President University Erwin Sitompul Digital Systems 10/1

Digital Systems Section 12 Binary Adders President University Erwin Sitompul Digital Systems 10/2

Lecture Digital Systems Binary Adders n Addition of binary data is very fundamental in digital systems. The hardware implementation needs to be determined. n The inputs are: single bit values, carry in n The outputs are: sum, carry out. n After creating a single-bit adder, we can chain multiple adders together. n Overflow must also be considered. Overflow is the situation where the result of addition exceeds the magnitude which can be represented with the allocated number of bits. President University Erwin Sitompul Digital Systems 10/3

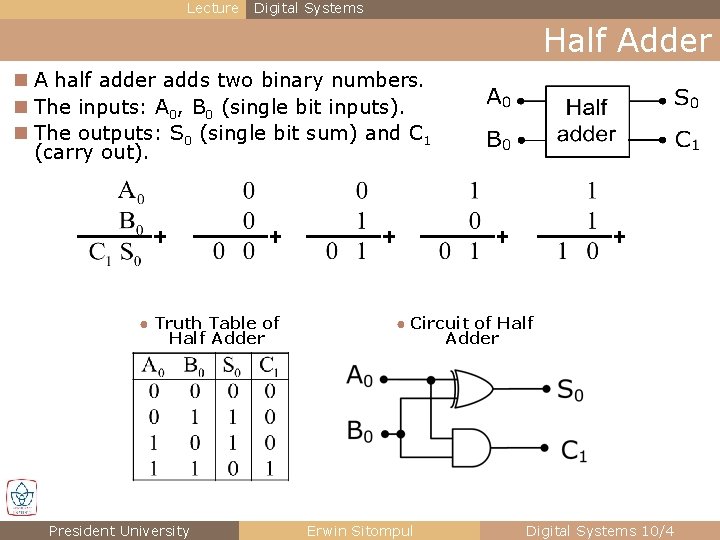

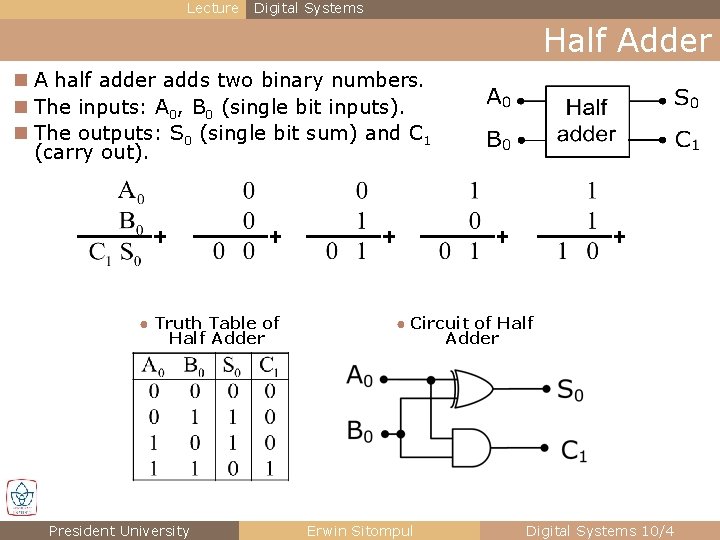

Lecture Digital Systems Half Adder n A half adder adds two binary numbers. n The inputs: A 0, B 0 (single bit inputs). n The outputs: S 0 (single bit sum) and C 1 (carry out). ● Truth Table of Half Adder President University ● Circuit of Half Adder Erwin Sitompul Digital Systems 10/4

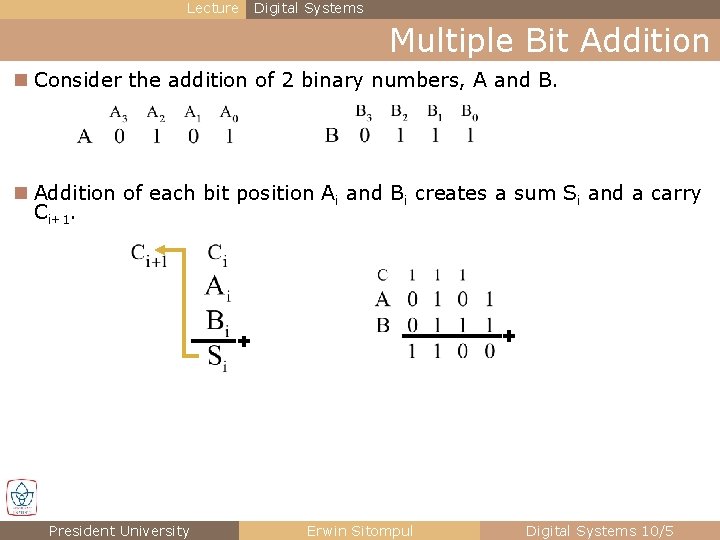

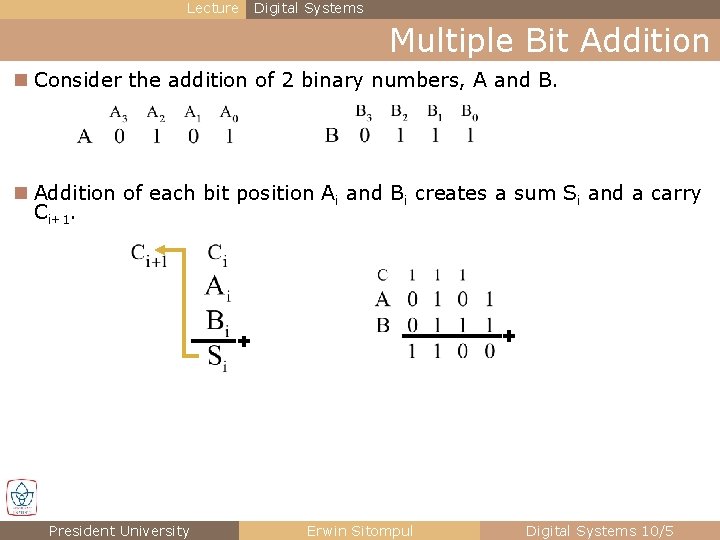

Lecture Digital Systems Multiple Bit Addition n Consider the addition of 2 binary numbers, A and B. n Addition of each bit position Ai and Bi creates a sum Si and a carry Ci+1. President University Erwin Sitompul Digital Systems 10/5

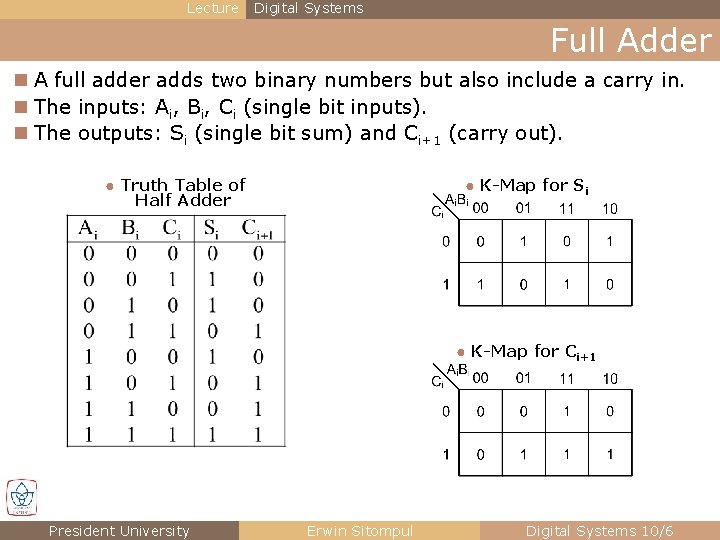

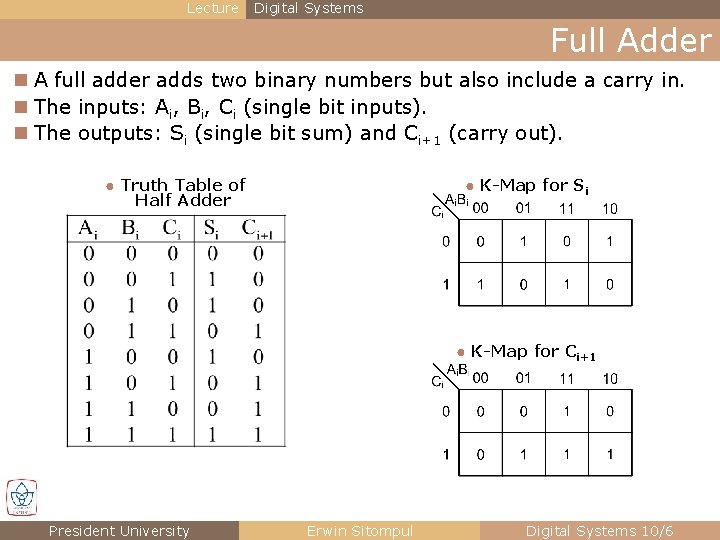

Lecture Digital Systems Full Adder n A full adder adds two binary numbers but also include a carry in. n The inputs: Ai, Bi, Ci (single bit inputs). n The outputs: Si (single bit sum) and Ci+1 (carry out). ● Truth Table of Half Adder ● K-Map for Si ● K-Map for Ci+1 President University Erwin Sitompul Digital Systems 10/6

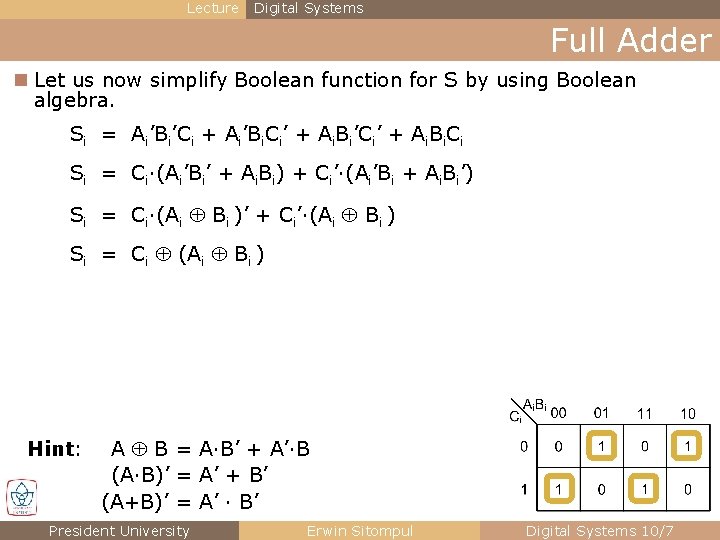

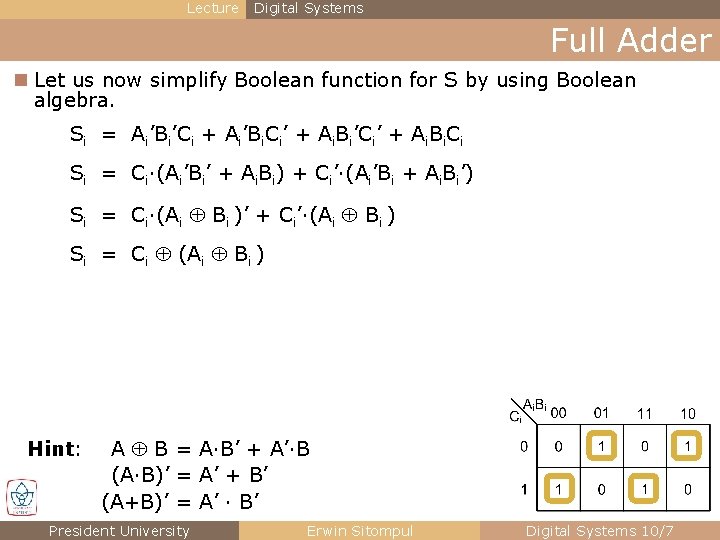

Lecture Digital Systems Full Adder n Let us now simplify Boolean function for S by using Boolean algebra. Si = Ai’Bi’Ci + Ai’Bi. Ci’ + Ai. Bi’Ci’ + Ai. Bi. Ci Si = Ci·(Ai’Bi’ + Ai. Bi) + Ci’·(Ai’Bi + Ai. Bi’) Si = Ci·(Ai Bi )’ + Ci’·(Ai Bi ) Si = Ci (Ai Bi ) Hint: A B = A·B’ + A’·B (A·B)’ = A’ + B’ (A+B)’ = A’ · B’ President University Erwin Sitompul Digital Systems 10/7

Lecture Digital Systems Full Adder n Let us now simplify Boolean function for Ci+1 by using Boolean algebra. Ci+1 = Ai. Bi + Ai. Ci +Bi. Ci (previous result) Ci+1 = Ai. Bi + Ci. Ai’Bi +Ci. Ai. Bi’ (as shown by K-map below) Ci+1 = Ai. Bi + Ci ·(Ai’Bi + Ai. Bi’) Ci+1 = Ai. Bi + Ci ·(Ai Bi) Hint: A B = A·B’ + A’·B (A·B)’ = A’ + B’ (A+B)’ = A’ · B’ President University Erwin Sitompul Digital Systems 10/8

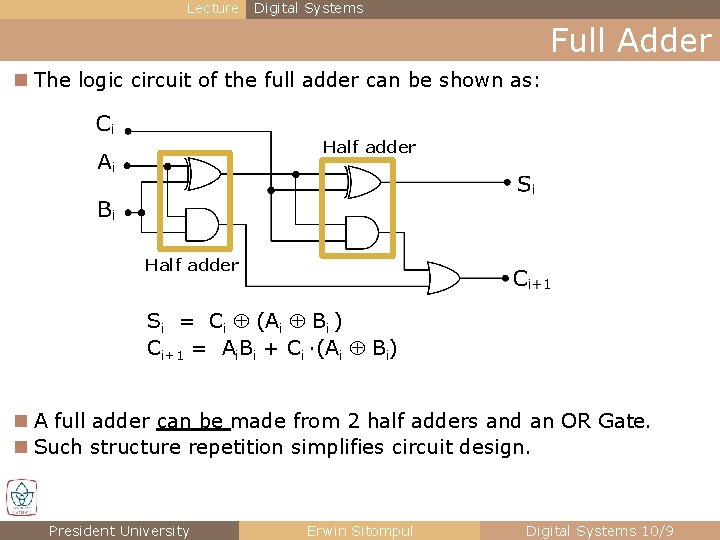

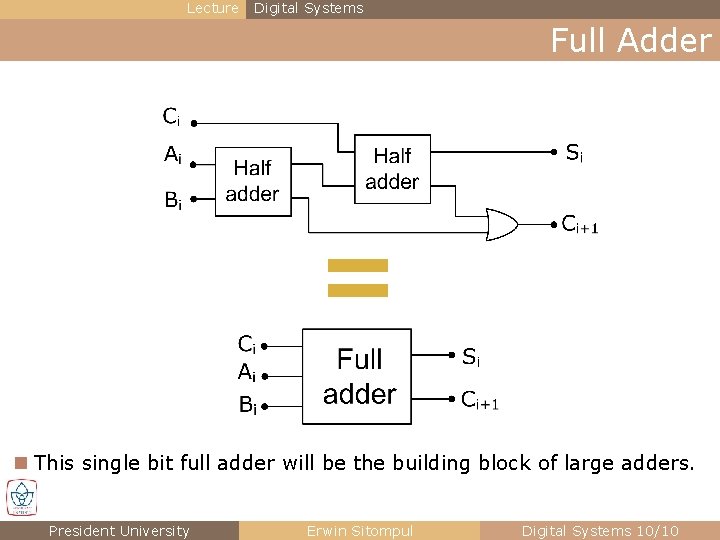

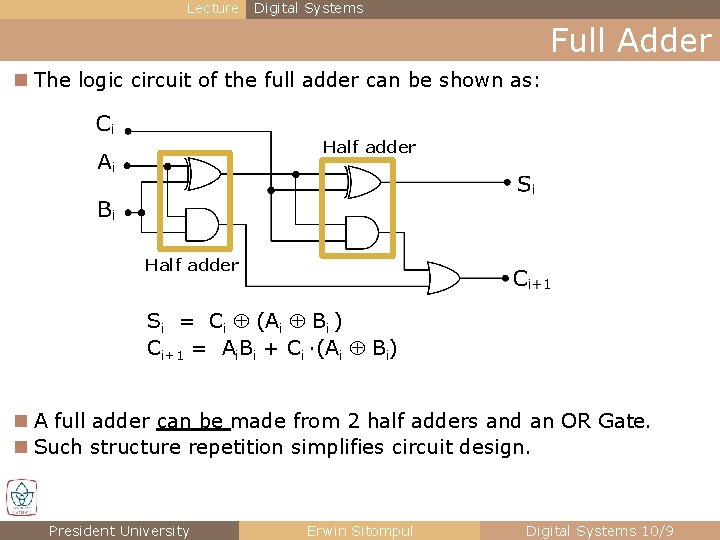

Lecture Digital Systems Full Adder n The logic circuit of the full adder can be shown as: Half adder Si = Ci (Ai Bi ) Ci+1 = Ai. Bi + Ci ·(Ai Bi) n A full adder can be made from 2 half adders and an OR Gate. n Such structure repetition simplifies circuit design. President University Erwin Sitompul Digital Systems 10/9

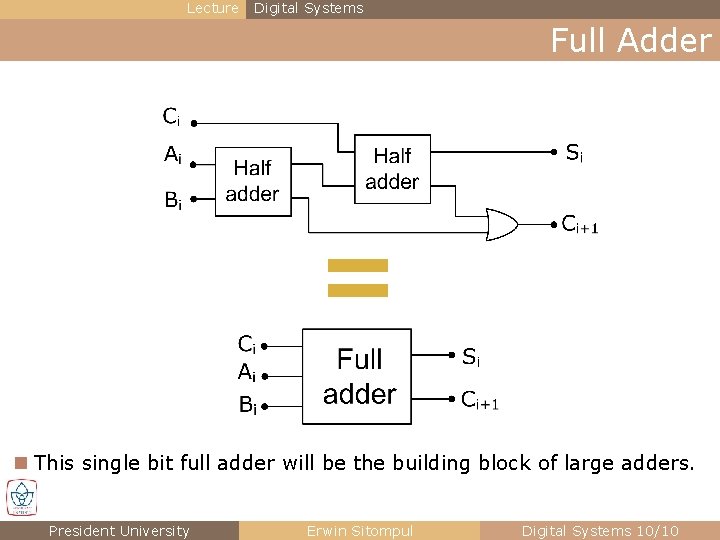

Lecture Digital Systems Full Adder = n This single bit full adder will be the building block of large adders. President University Erwin Sitompul Digital Systems 10/10

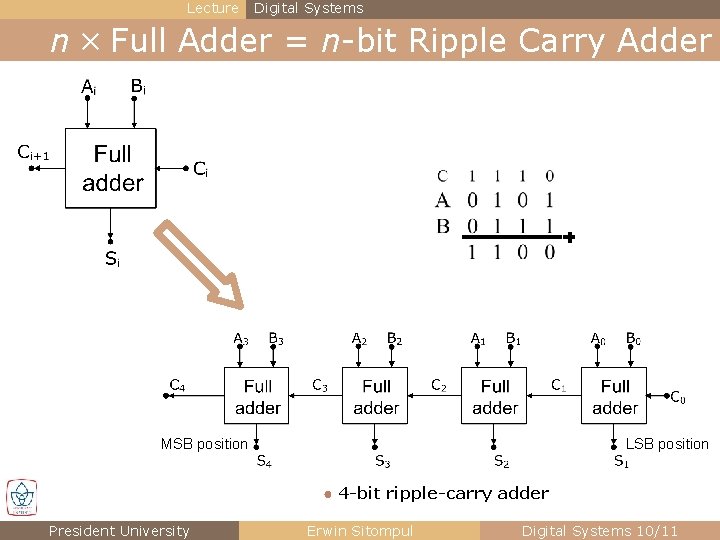

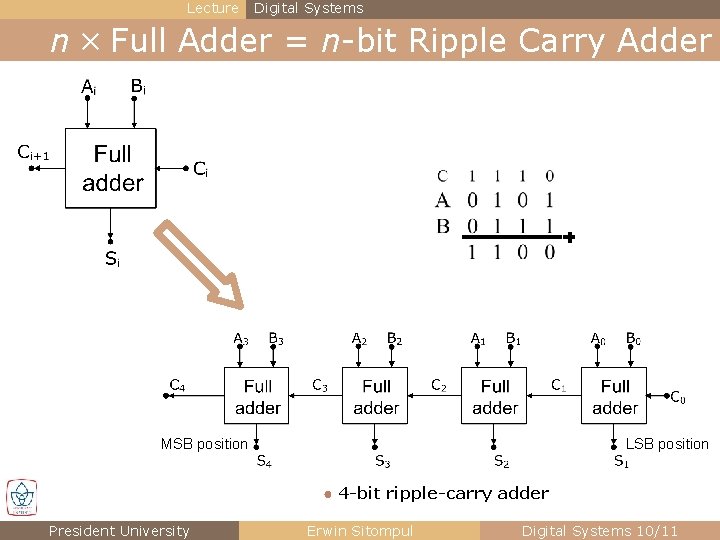

Lecture Digital Systems n × Full Adder = n-bit Ripple Carry Adder MSB position LSB position ● 4 -bit ripple-carry adder President University Erwin Sitompul Digital Systems 10/11

Digital Systems Section 13 Signed Numbers President University Erwin Sitompul Digital Systems 10/12

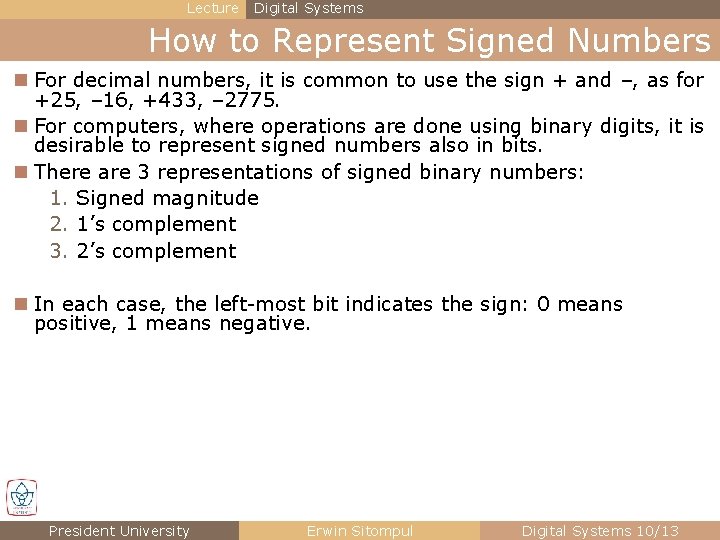

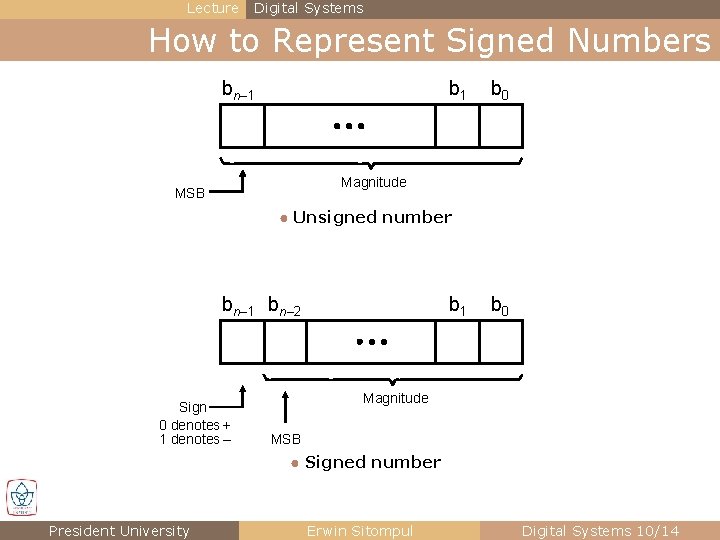

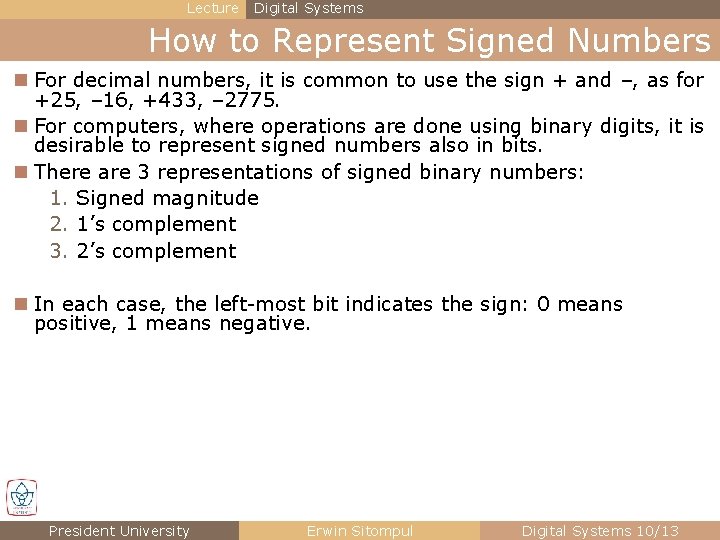

Lecture Digital Systems How to Represent Signed Numbers n For decimal numbers, it is common to use the sign + and –, as for +25, – 16, +433, – 2775. n For computers, where operations are done using binary digits, it is desirable to represent signed numbers also in bits. n There are 3 representations of signed binary numbers: 1. Signed magnitude 2. 1’s complement 3. 2’s complement n In each case, the left-most bit indicates the sign: 0 means positive, 1 means negative. President University Erwin Sitompul Digital Systems 10/13

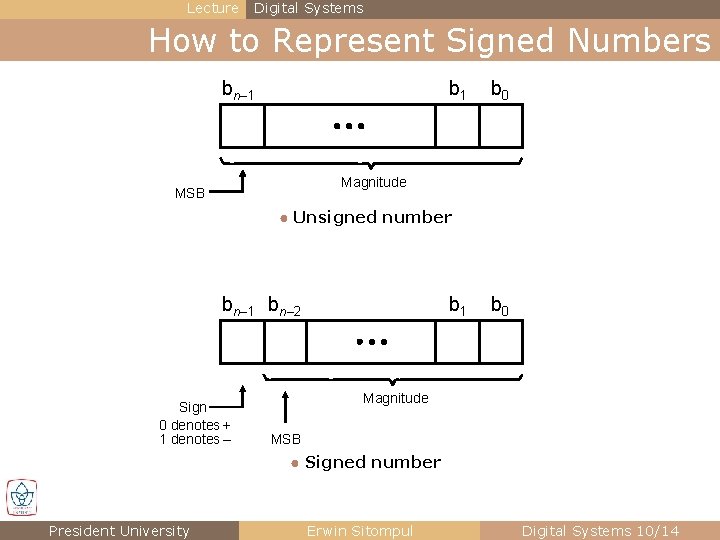

Lecture Digital Systems How to Represent Signed Numbers bn– 1 b 0 Magnitude MSB ● Unsigned number bn– 1 bn– 2 Sign 0 denotes + 1 denotes – b 1 b 0 Magnitude MSB ● Signed number President University Erwin Sitompul Digital Systems 10/14

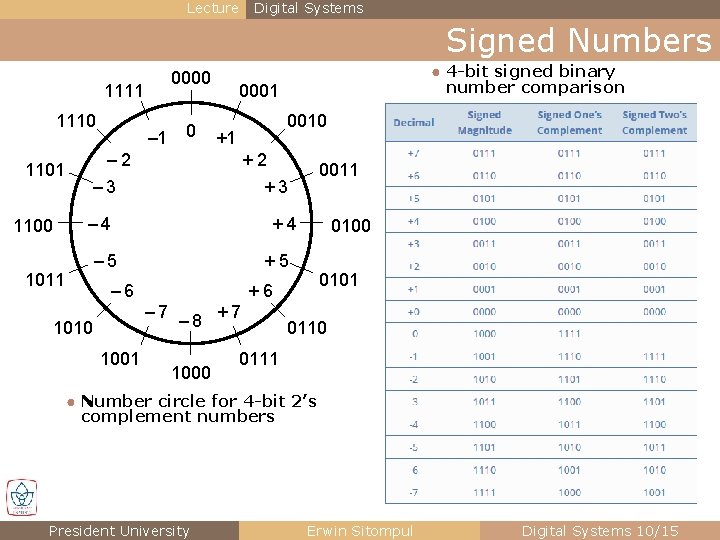

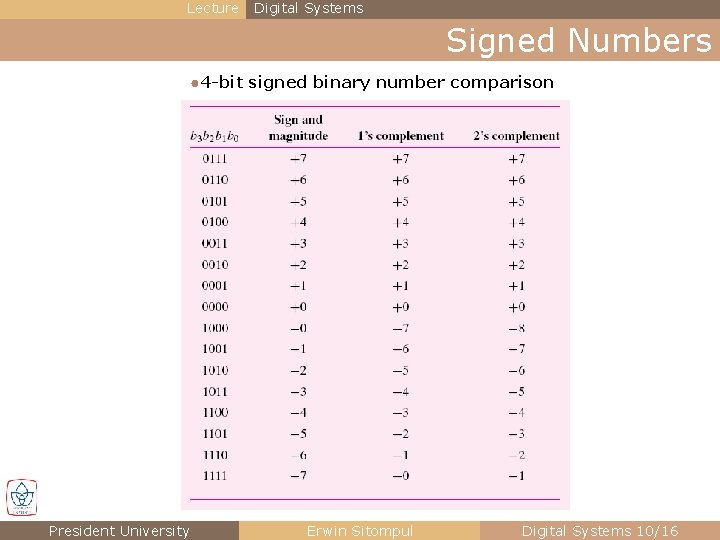

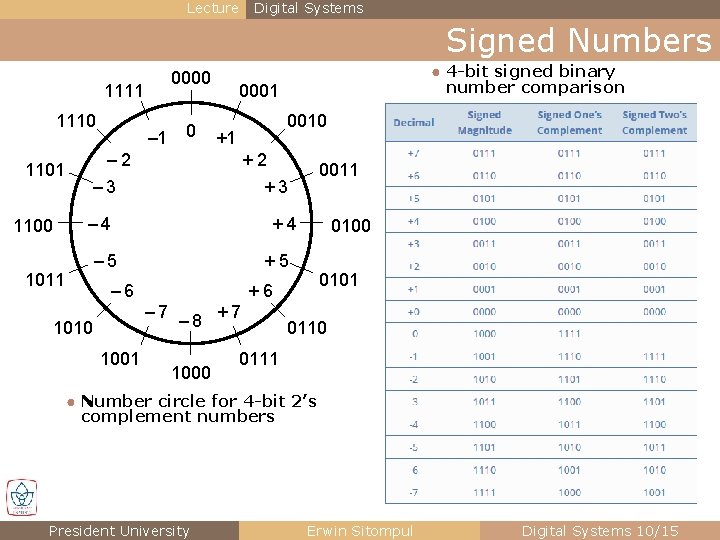

Lecture Digital Systems Signed Numbers 0000 1111 1110 1101 1100 – 1 0 0001 0010 +1 – 2 – 3 +2 +3 – 4 0101 +6 – 7 – 8 +7 1001 0100 +5 – 6 1010 0011 +4 – 5 1011 ● 4 -bit signed binary number comparison 1000 0111 ● Number circle for 4 -bit 2’s complement numbers President University Erwin Sitompul Digital Systems 10/15

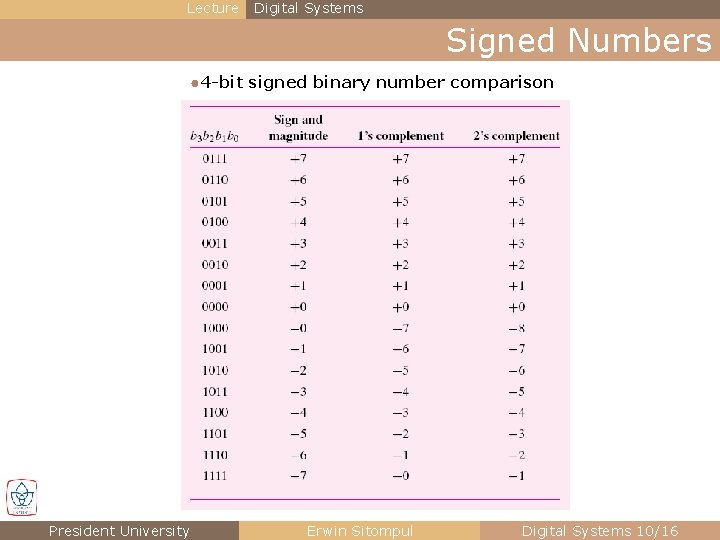

Lecture Digital Systems Signed Numbers ● 4 -bit signed binary number comparison President University Erwin Sitompul Digital Systems 10/16

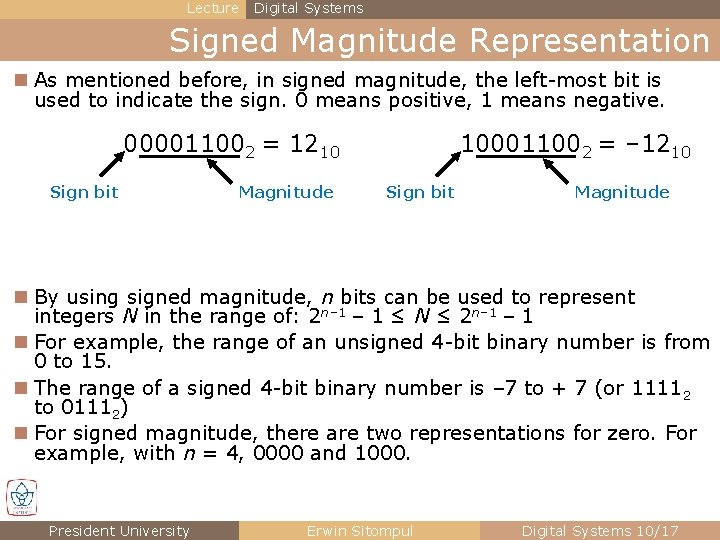

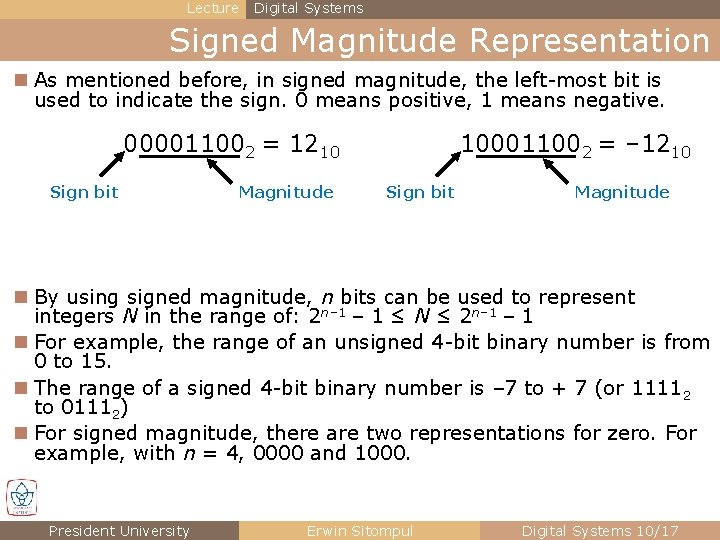

Lecture Digital Systems Signed Magnitude Representation n As mentioned before, in signed magnitude, the left-most bit is used to indicate the sign. 0 means positive, 1 means negative. 000011002 = 1210 Sign bit Magnitude 100011002 = – 1210 Sign bit Magnitude n By using signed magnitude, n bits can be used to represent integers N in the range of: 2 n– 1 ≤ N ≤ 2 n– 1 n For example, the range of an unsigned 4 -bit binary number is from 0 to 15. n The range of a signed 4 -bit binary number is – 7 to + 7 (or 1111 2 to 01112) n For signed magnitude, there are two representations for zero. For example, with n = 4, 0000 and 1000. President University Erwin Sitompul Digital Systems 10/17

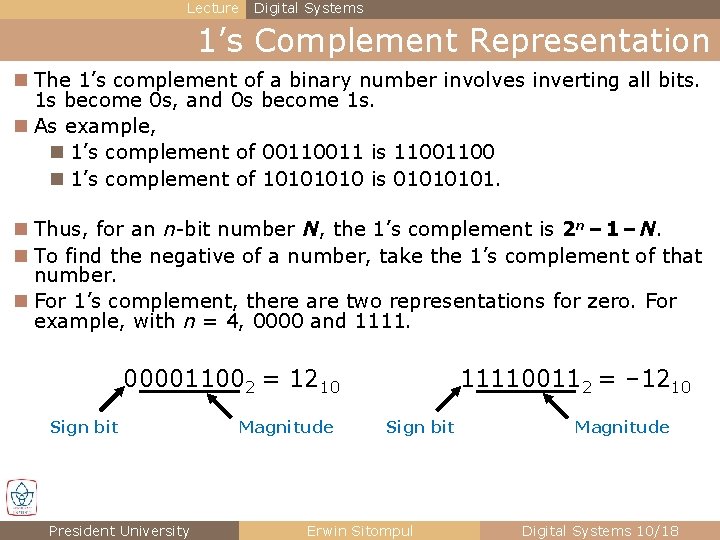

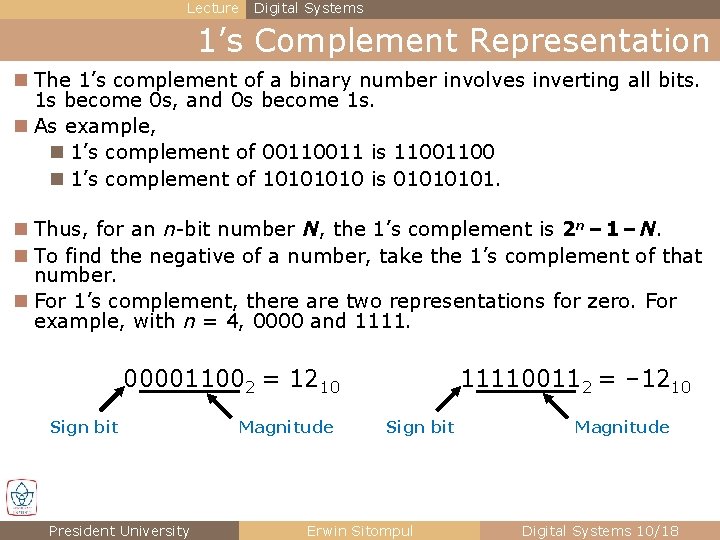

Lecture Digital Systems 1’s Complement Representation n The 1’s complement of a binary number involves inverting all bits. 1 s become 0 s, and 0 s become 1 s. n As example, n 1’s complement of 0011 is 1100 n 1’s complement of 1010 is 0101. n Thus, for an n-bit number N, the 1’s complement is 2 n – 1 – N. n To find the negative of a number, take the 1’s complement of that number. n For 1’s complement, there are two representations for zero. For example, with n = 4, 0000 and 1111. 000011002 = 1210 Sign bit President University Magnitude 111100112 = – 1210 Sign bit Erwin Sitompul Magnitude Digital Systems 10/18

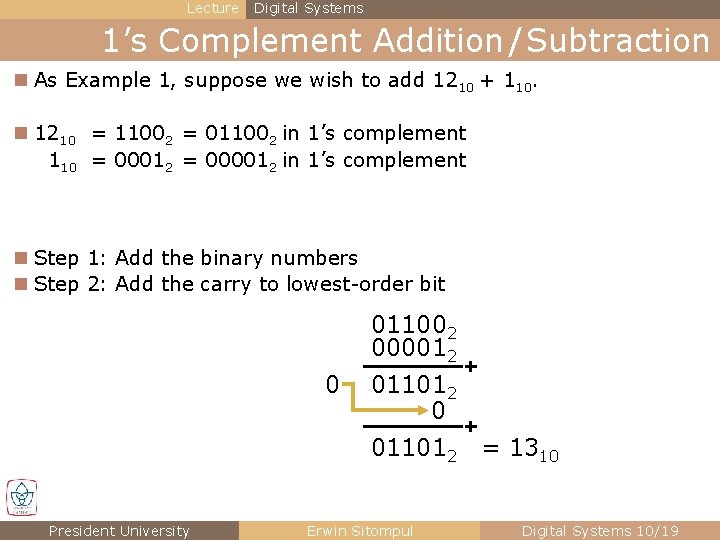

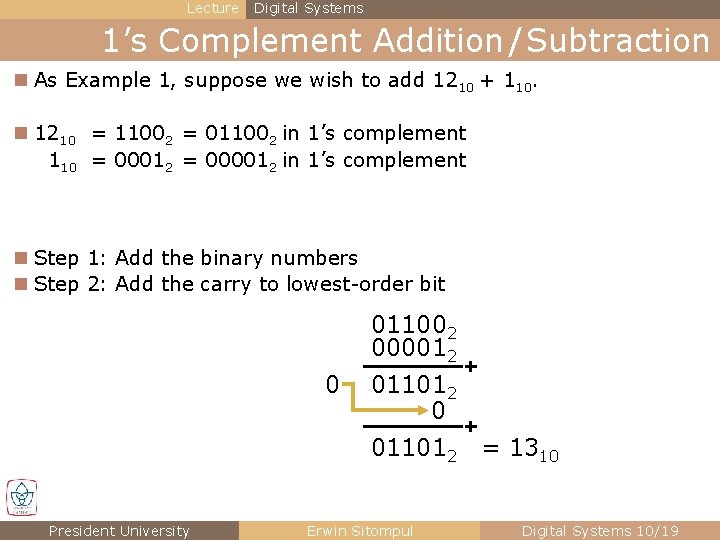

Lecture Digital Systems 1’s Complement Addition / Subtraction n As Example 1, suppose we wish to add 1210 + 110. n 1210 = 11002 = 011002 in 1’s complement 110 = 00012 = 000012 in 1’s complement n Step 1: Add the binary numbers n Step 2: Add the carry to lowest-order bit 011002 000012 0 011012 = 1310 President University Erwin Sitompul Digital Systems 10/19

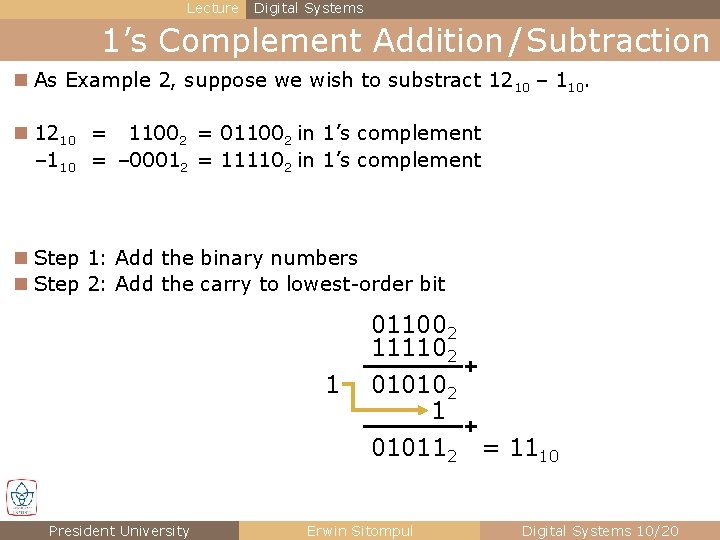

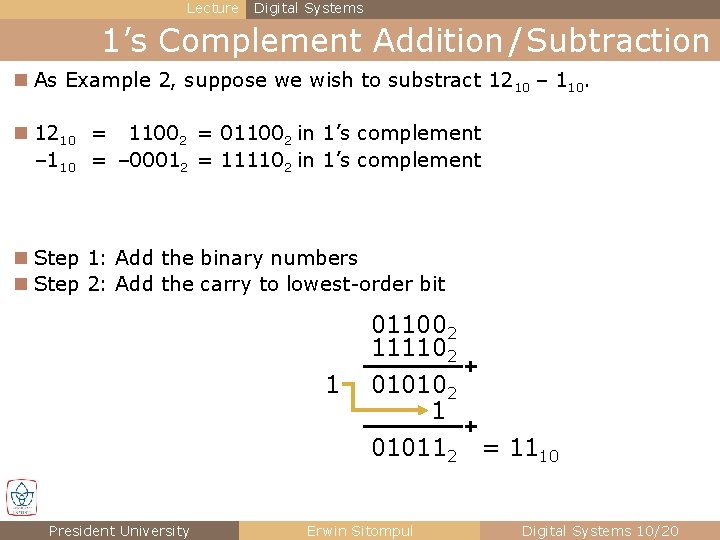

Lecture Digital Systems 1’s Complement Addition / Subtraction n As Example 2, suppose we wish to substract 1210 – 110. n 1210 = 11002 = 011002 in 1’s complement – 110 = – 00012 = 111102 in 1’s complement n Step 1: Add the binary numbers n Step 2: Add the carry to lowest-order bit 011002 111102 1 010112 = 1110 President University Erwin Sitompul Digital Systems 10/20

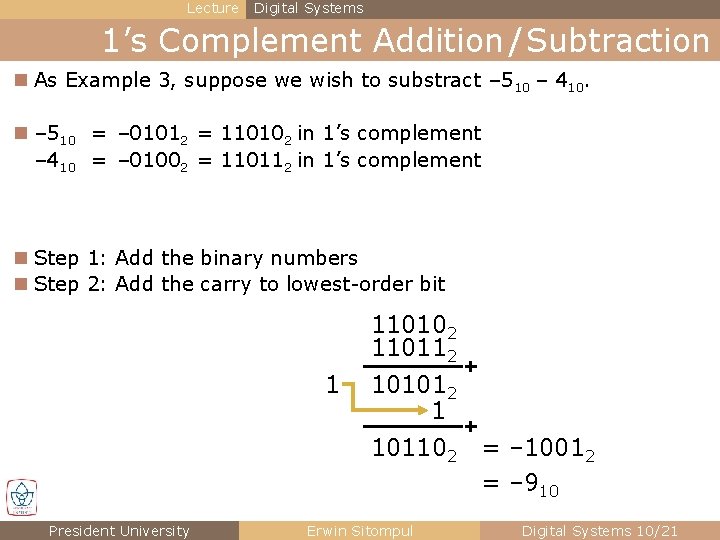

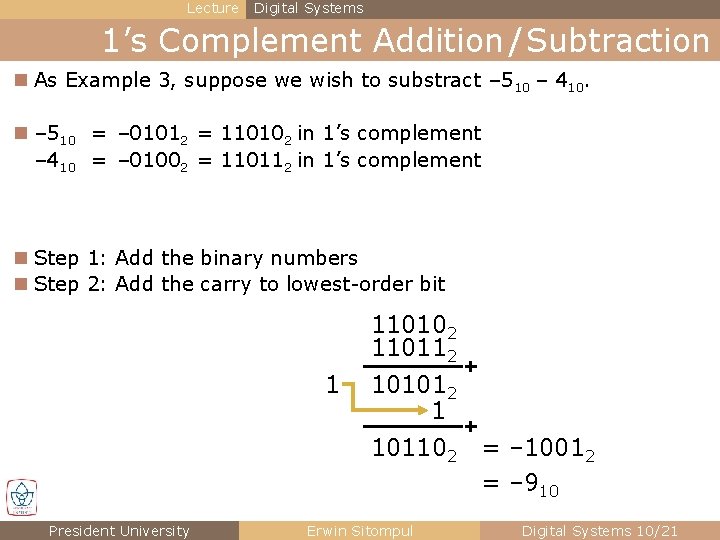

Lecture Digital Systems 1’s Complement Addition / Subtraction n As Example 3, suppose we wish to substract – 510 – 410. n – 510 = – 01012 = 110102 in 1’s complement – 410 = – 01002 = 110112 in 1’s complement n Step 1: Add the binary numbers n Step 2: Add the carry to lowest-order bit 110102 110112 1 101012 1 101102 = – 10012 = – 910 President University Erwin Sitompul Digital Systems 10/21

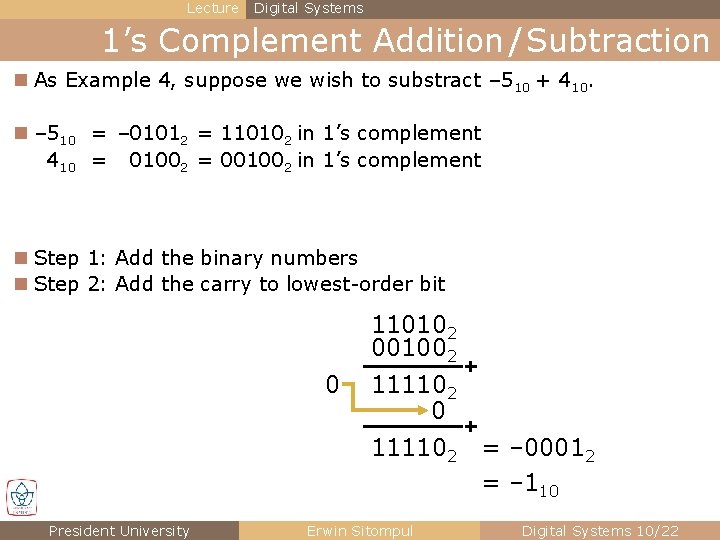

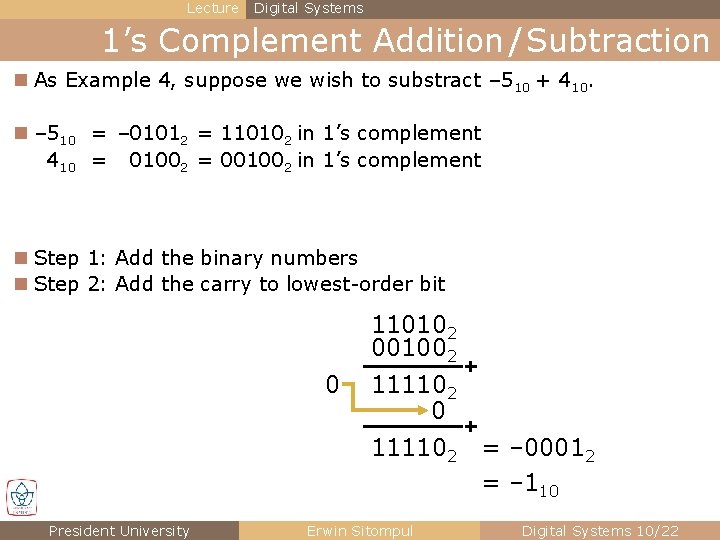

Lecture Digital Systems 1’s Complement Addition / Subtraction n As Example 4, suppose we wish to substract – 510 + 410. n – 510 = – 01012 = 110102 in 1’s complement – 410 = – 01002 = 001002 in 1’s complement n Step 1: Add the binary numbers n Step 2: Add the carry to lowest-order bit 110102 001002 0 111102 = – 00012 = – 110 President University Erwin Sitompul Digital Systems 10/22

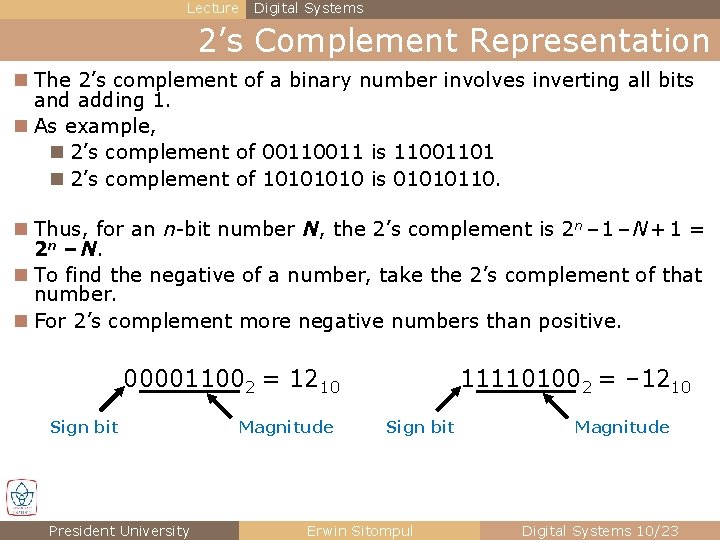

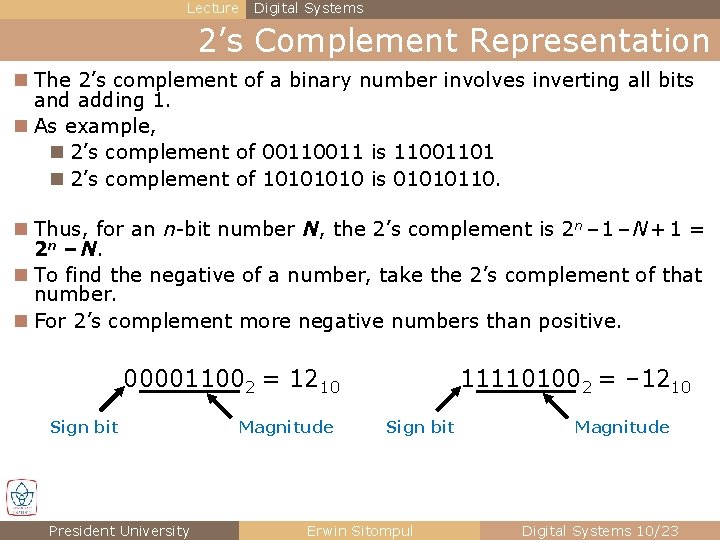

Lecture Digital Systems 2’s Complement Representation n The 2’s complement of a binary number involves inverting all bits and adding 1. n As example, n 2’s complement of 0011 is 11001101 n 2’s complement of 1010 is 01010110. n Thus, for an n-bit number N, the 2’s complement is 2 n – 1 – N + 1 = 2 n – N. n To find the negative of a number, take the 2’s complement of that number. n For 2’s complement more negative numbers than positive. 000011002 = 1210 Sign bit President University Magnitude 111101002 = – 1210 Sign bit Erwin Sitompul Magnitude Digital Systems 10/23

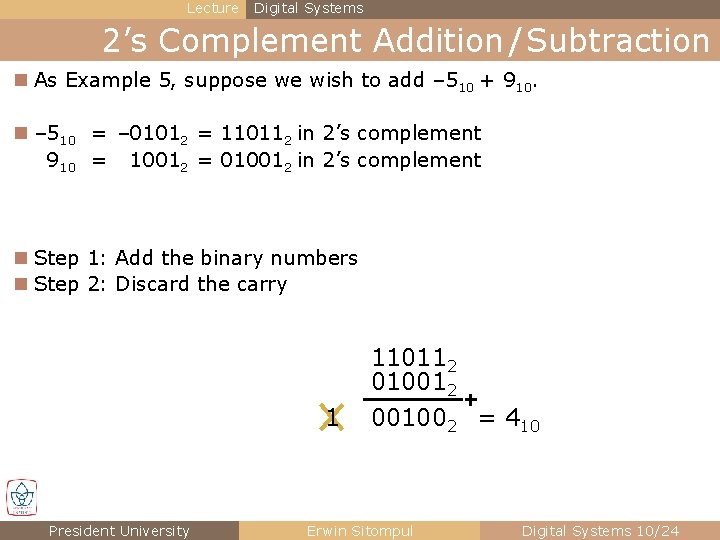

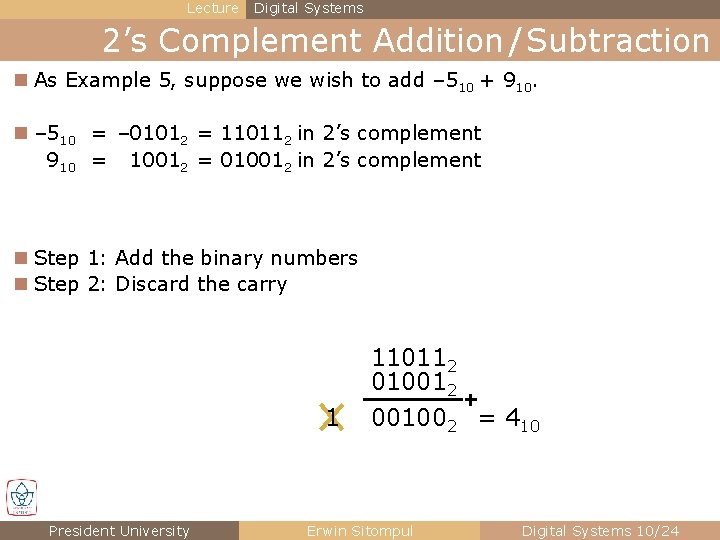

Lecture Digital Systems 2’s Complement Addition / Subtraction n As Example 5, suppose we wish to add – 510 + 910. n – 510 = – 01012 = 110112 in 2’s complement – 910 = – 10012 = 010012 in 2’s complement n Step 1: Add the binary numbers n Step 2: Discard the carry 110112 010012 1 President University 001002 = 410 Erwin Sitompul Digital Systems 10/24

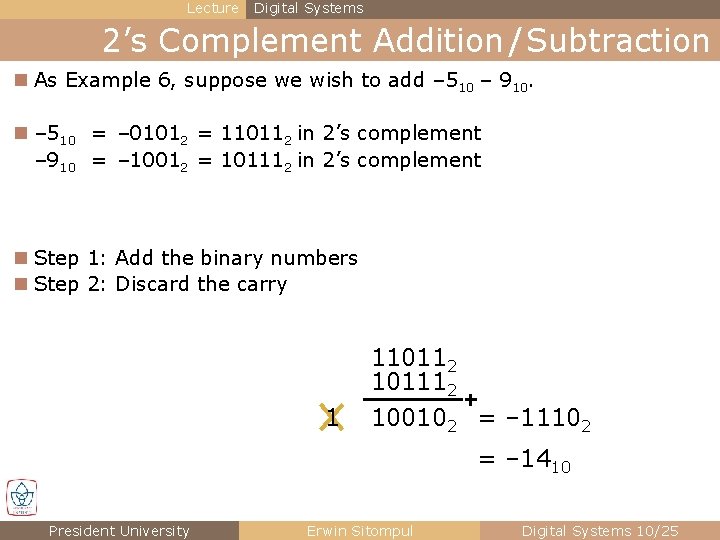

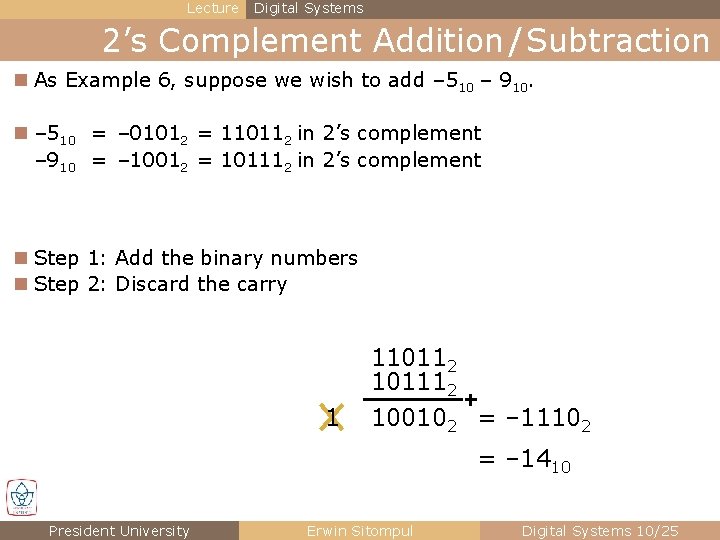

Lecture Digital Systems 2’s Complement Addition / Subtraction n As Example 6, suppose we wish to add – 510 – 910. n – 510 = – 01012 = 110112 in 2’s complement – 910 = – 10012 = 101112 in 2’s complement n Step 1: Add the binary numbers n Step 2: Discard the carry 110112 101112 1 100102 = – 11102 = – 1410 President University Erwin Sitompul Digital Systems 10/25

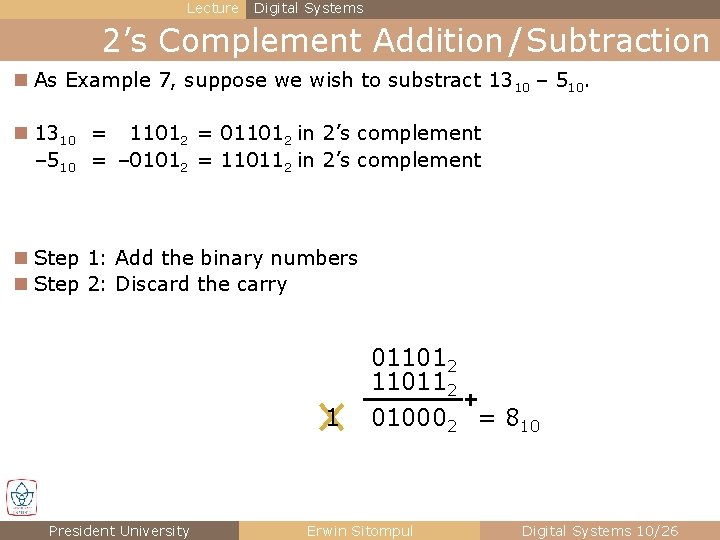

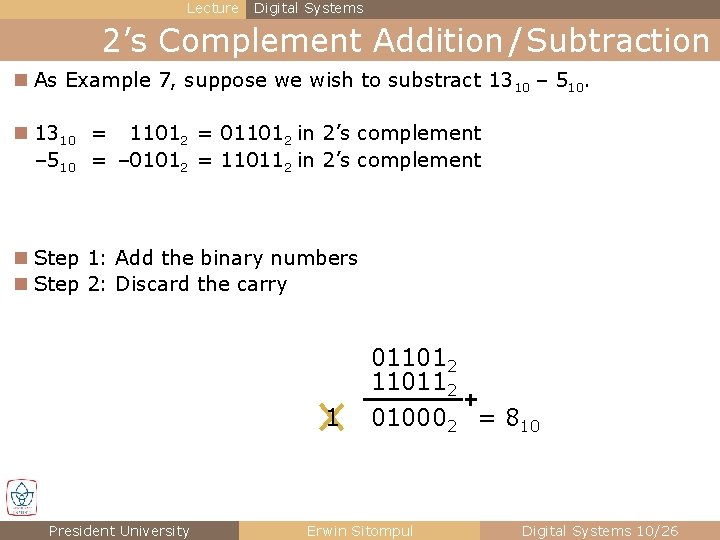

Lecture Digital Systems 2’s Complement Addition / Subtraction n As Example 7, suppose we wish to substract 1310 – 510. n 1310 = – 11012 = 011012 in 2’s complement – 510 = – 01012 = 110112 in 2’s complement n Step 1: Add the binary numbers n Step 2: Discard the carry 011012 110112 1 President University 010002 = 810 Erwin Sitompul Digital Systems 10/26

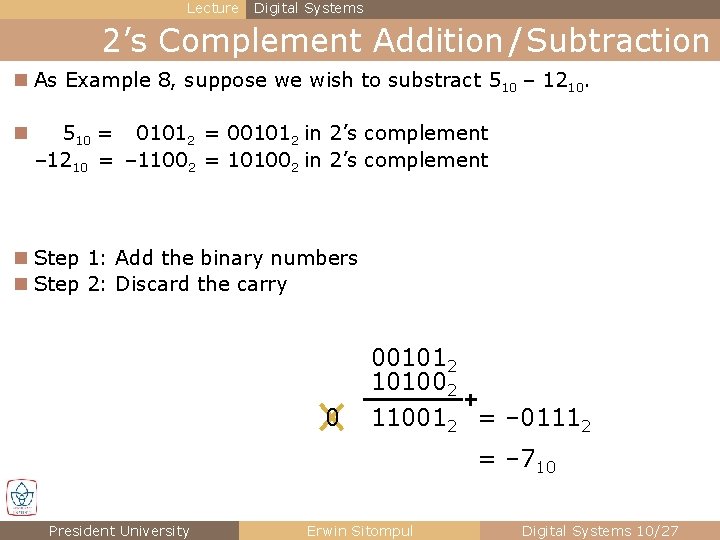

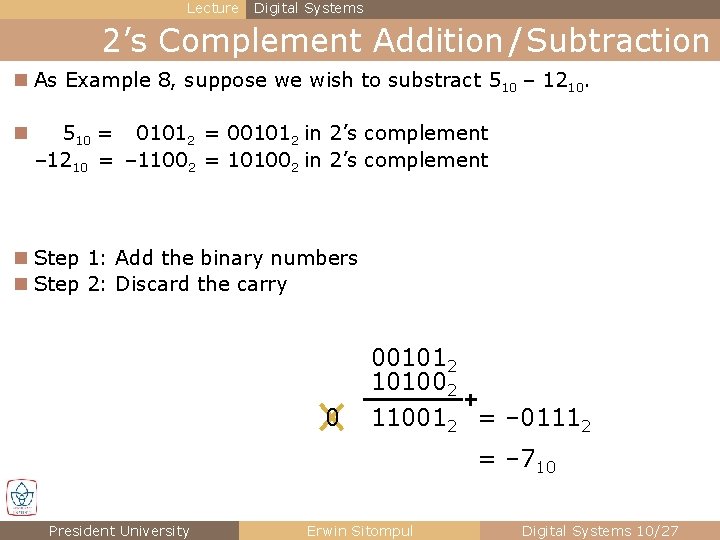

Lecture Digital Systems 2’s Complement Addition / Subtraction n As Example 8, suppose we wish to substract 510 – 1210. n 510 = – 01012 = 001012 in 2’s complement – 1210 = – 11002 = 101002 in 2’s complement n Step 1: Add the binary numbers n Step 2: Discard the carry 001012 101002 0 110012 = – 01112 = – 710 President University Erwin Sitompul Digital Systems 10/27

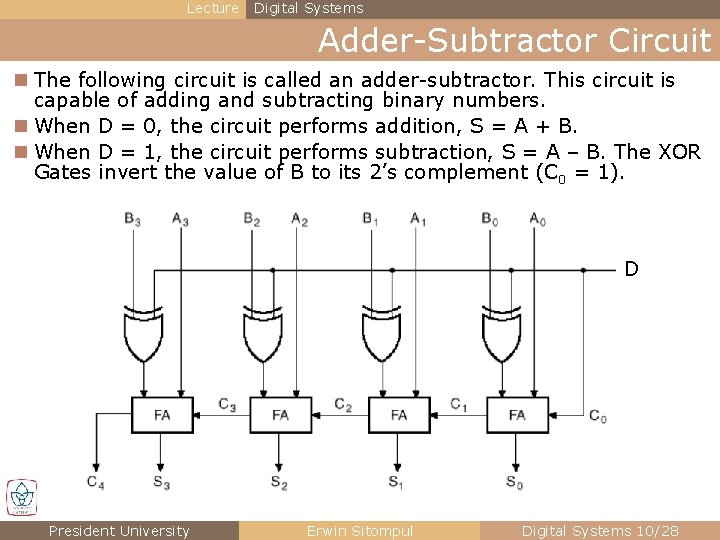

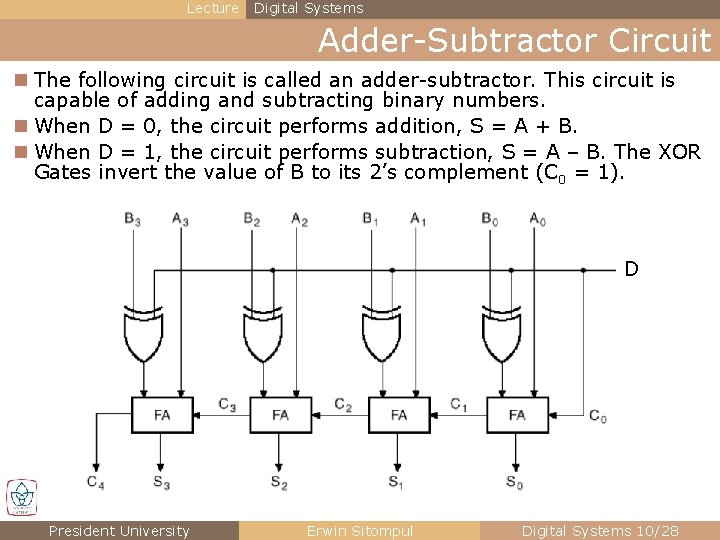

Lecture Digital Systems Adder-Subtractor Circuit n The following circuit is called an adder-subtractor. This circuit is capable of adding and subtracting binary numbers. n When D = 0, the circuit performs addition, S = A + B. n When D = 1, the circuit performs subtraction, S = A – B. The XOR Gates invert the value of B to its 2’s complement (C 0 = 1). D President University Erwin Sitompul Digital Systems 10/28

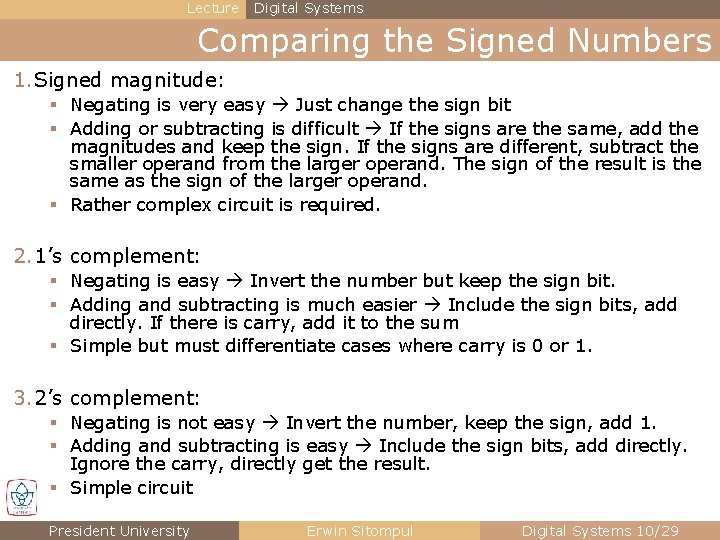

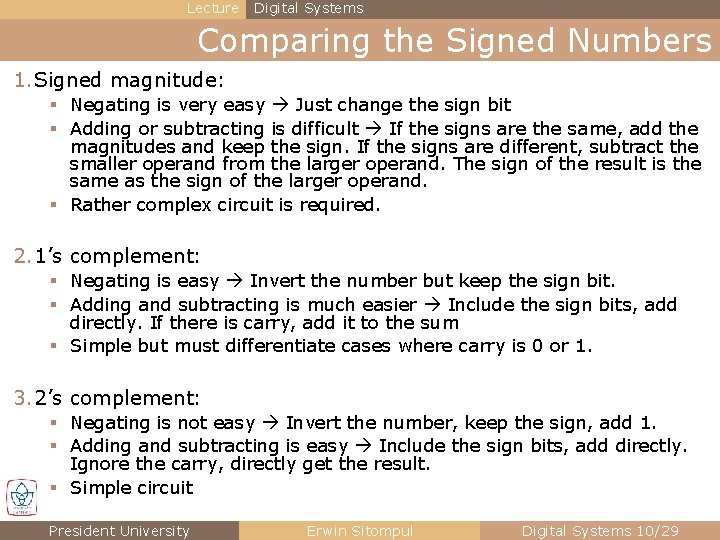

Lecture Digital Systems Comparing the Signed Numbers 1. Signed magnitude: § Negating is very easy Just change the sign bit § Adding or subtracting is difficult If the signs are the same, add the magnitudes and keep the sign. If the signs are different, subtract the smaller operand from the larger operand. The sign of the result is the same as the sign of the larger operand. § Rather complex circuit is required. 2. 1’s complement: § Negating is easy Invert the number but keep the sign bit. § Adding and subtracting is much easier Include the sign bits, add directly. If there is carry, add it to the sum § Simple but must differentiate cases where carry is 0 or 1. 3. 2’s complement: § Negating is not easy Invert the number, keep the sign, add 1. § Adding and subtracting is easy Include the sign bits, add directly. Ignore the carry, directly get the result. § Simple circuit President University Erwin Sitompul Digital Systems 10/29

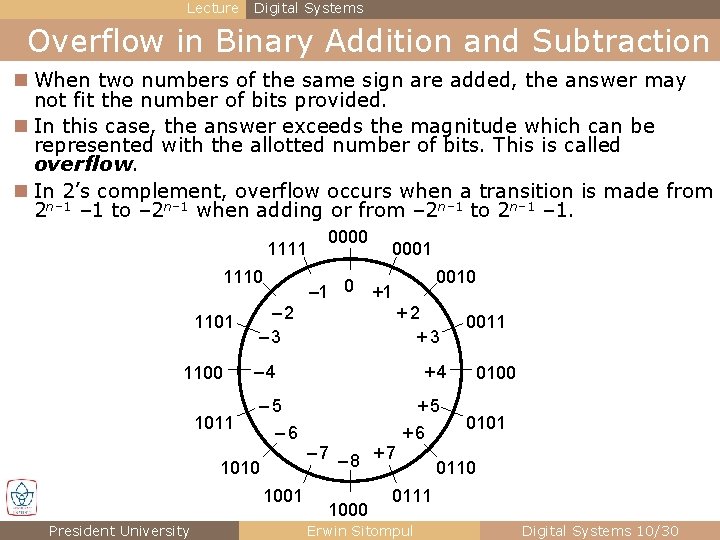

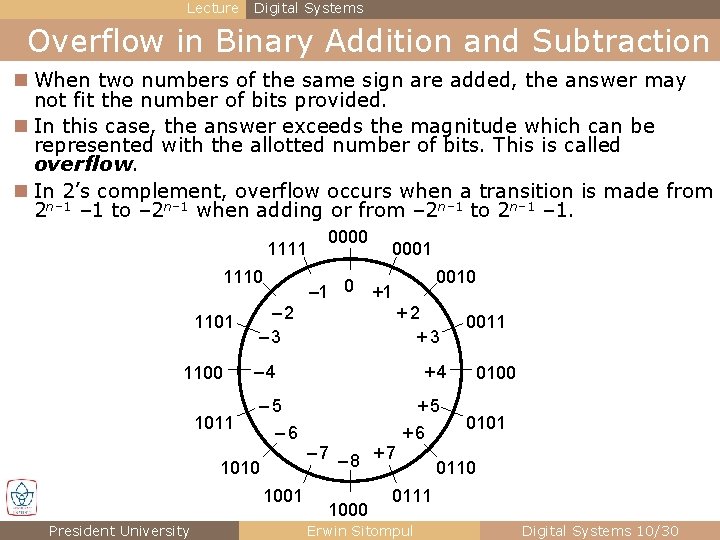

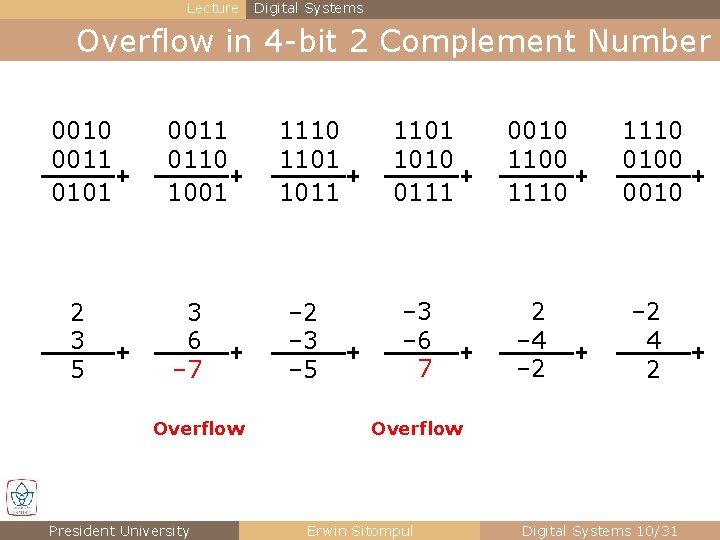

Lecture Digital Systems Overflow in Binary Addition and Subtraction n When two numbers of the same sign are added, the answer may not fit the number of bits provided. n In this case, the answer exceeds the magnitude which can be represented with the allotted number of bits. This is called overflow. n In 2’s complement, overflow occurs when a transition is made from 2 n– 1 to – 2 n– 1 when adding or from – 2 n– 1 to 2 n– 1 – 1. 1111 1110 1101 1100 1011 – 1 0 0001 0010 +1 – 2 – 3 +2 +3 – 4 – 6 1001 0011 +4 – 5 1010 President University 0000 +5 – 7 – 8 +7 1000 +6 0100 0101 0110 0111 Erwin Sitompul Digital Systems 10/30

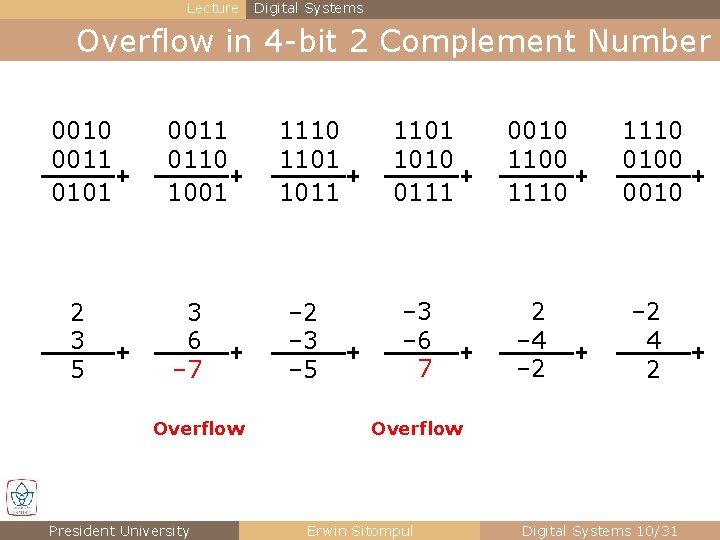

Lecture Digital Systems Overflow in 4 -bit 2 Complement Number 00 0011 0101 2 3 5 01 0011 0110 1001 3 6 – 7 Overflow President University 11 1110 1101 1011 10 1101 1010 0111 00 0010 1100 1110 11 1110 0100 0010 – 2 – 3 – 5 – 3 – 6 7 2 – 4 – 2 4 2 Overflow Erwin Sitompul Digital Systems 10/31

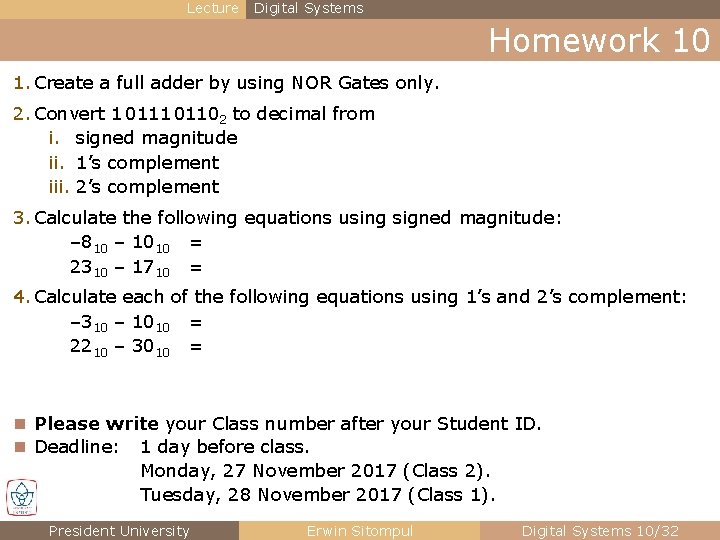

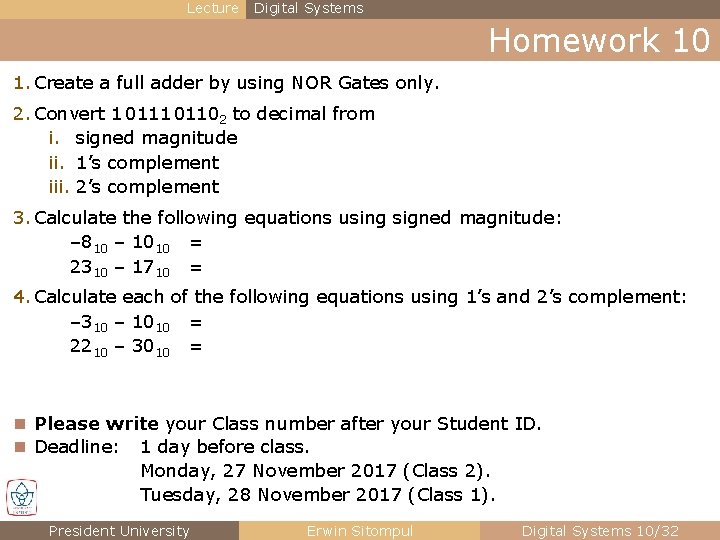

Lecture Digital Systems Homework 10 1. Create a full adder by using NOR Gates only. 2. Convert 1 01102 to decimal from i. signed magnitude ii. 1’s complement iii. 2’s complement 3. Calculate the following equations using signed magnitude: – 810 – 1010 = 2310 – 1710 = 4. Calculate each of the following equations using 1’s and 2’s complement: – 310 – 1010 = 2210 – 3010 = n Please write your Class number after your Student ID. n Deadline: 1 day before class. Monday, 27 November 2017 (Class 2). Tuesday, 28 November 2017 (Class 1). President University Erwin Sitompul Digital Systems 10/32