Digital Systems Lecture 11 Dr Ing Erwin Sitompul

- Slides: 32

Digital Systems Lecture 11 Dr. -Ing. Erwin Sitompul President University http: //zitompul. wordpress. com 2 0 1 7 President University Erwin Sitompul Digital Systems 11/1

Lecture Digital Systems Section 14 Registers President University Erwin Sitompul Digital Systems 11/2

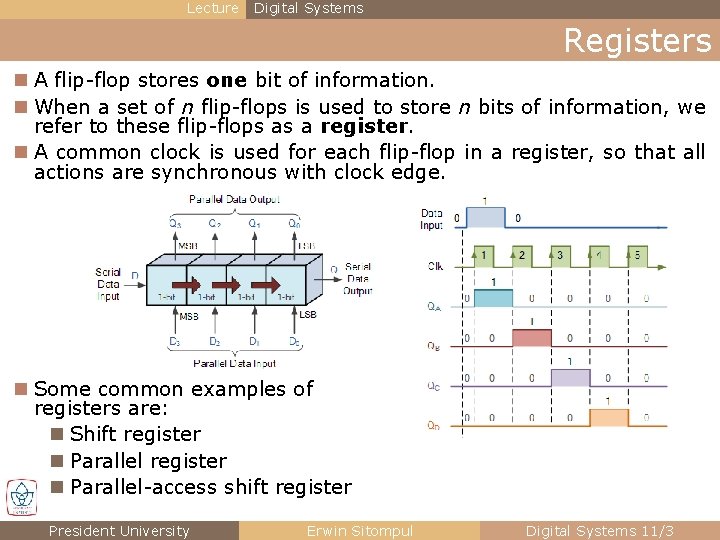

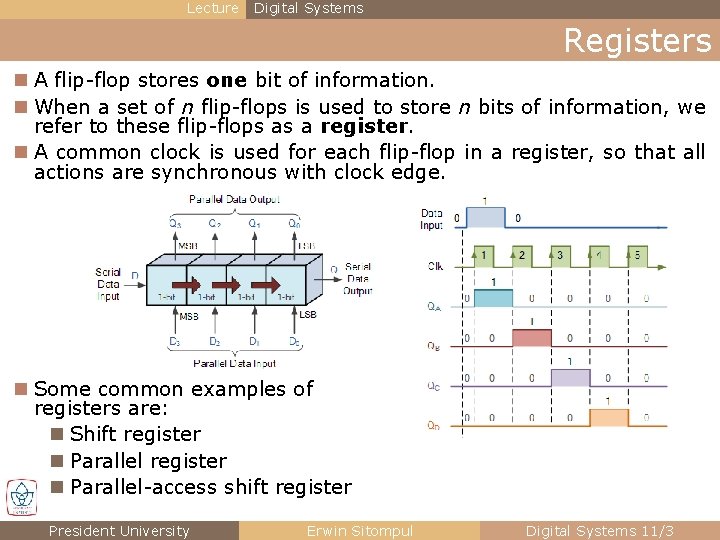

Lecture Digital Systems Registers n A flip-flop stores one bit of information. n When a set of n flip-flops is used to store n bits of information, we refer to these flip-flops as a register. n A common clock is used for each flip-flop in a register, so that all actions are synchronous with clock edge. n Some common examples of registers are: n Shift register n Parallel-access shift register President University Erwin Sitompul Digital Systems 11/3

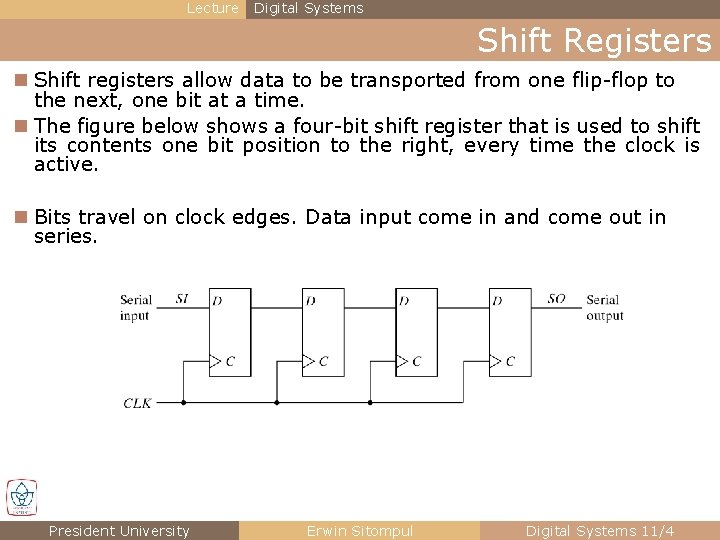

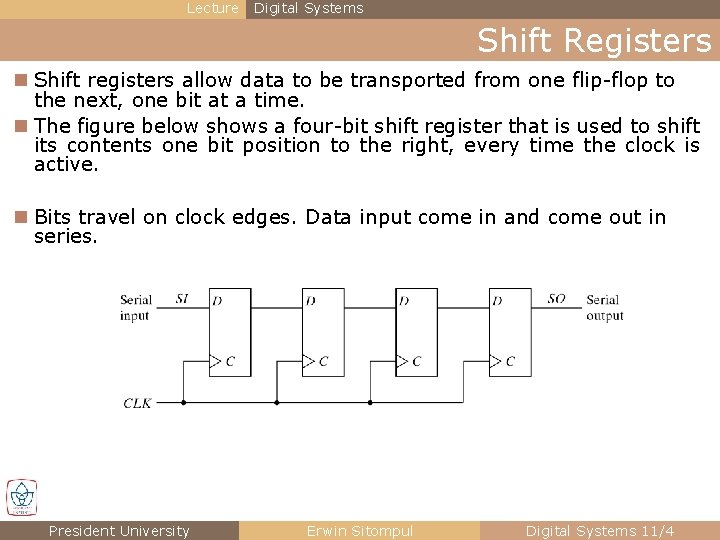

Lecture Digital Systems Shift Registers n Shift registers allow data to be transported from one flip-flop to the next, one bit at a time. n The figure below shows a four-bit shift register that is used to shift its contents one bit position to the right, every time the clock is active. n Bits travel on clock edges. Data input come in and come out in series. President University Erwin Sitompul Digital Systems 11/4

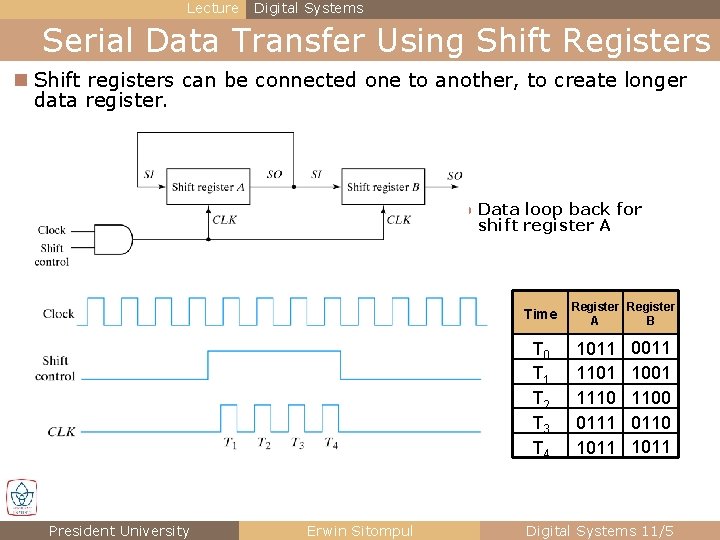

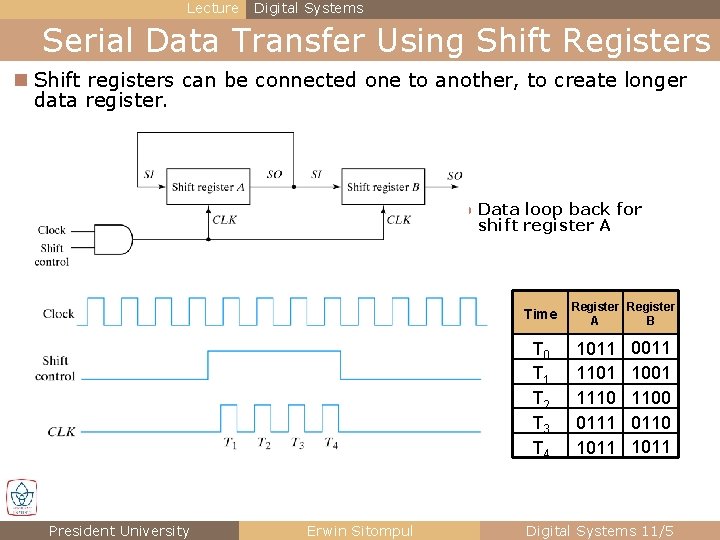

Lecture Digital Systems Serial Data Transfer Using Shift Registers n Shift registers can be connected one to another, to create longer data register. ● Data loop back for shift register A Time T 0 T 1 T 2 T 3 T 4 President University Erwin Sitompul Register A B 1011 1101 1110 0111 1011 0011 1001 1100 0110 1011 Digital Systems 11/5

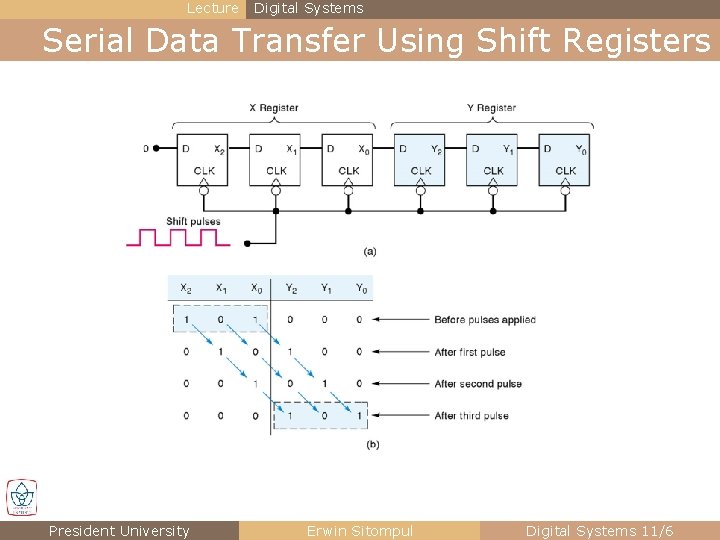

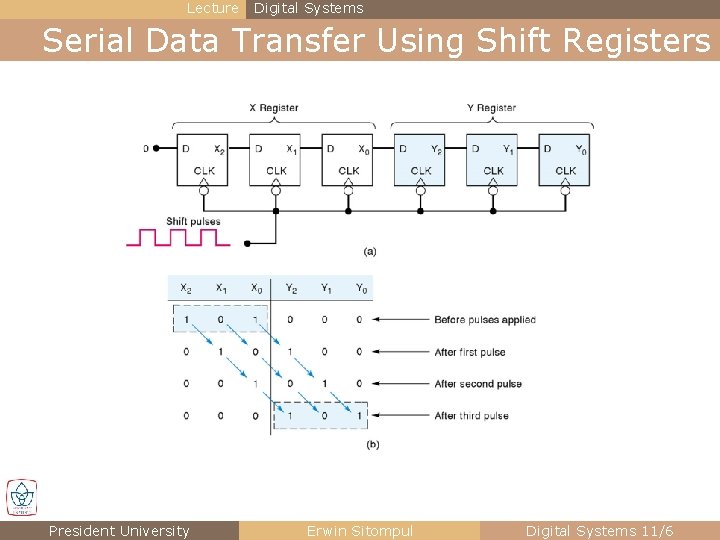

Lecture Digital Systems Serial Data Transfer Using Shift Registers President University Erwin Sitompul Digital Systems 11/6

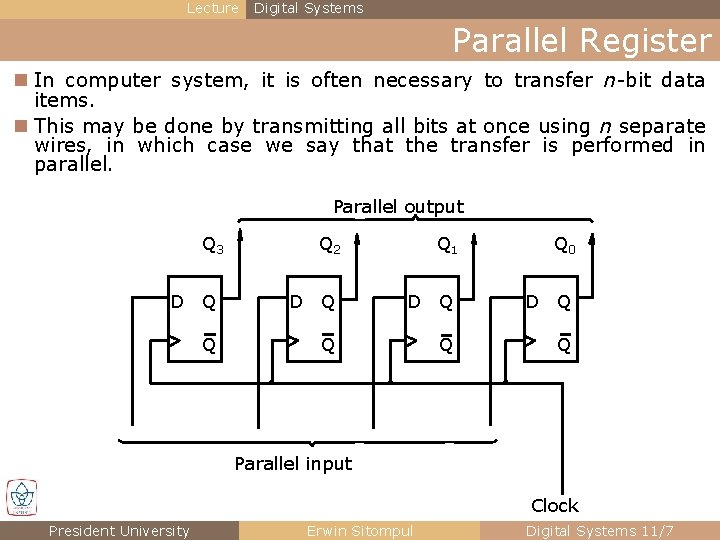

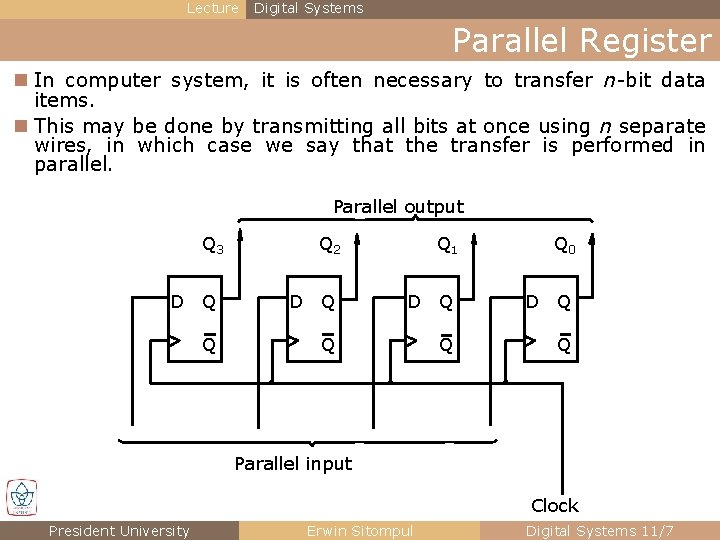

Lecture Digital Systems Parallel Register n In computer system, it is often necessary to transfer n-bit data items. n This may be done by transmitting all bits at once using n separate wires, in which case we say that the transfer is performed in parallel. Parallel output Q 3 D Q Q Q 2 D Q Q 1 D Q Q 0 D Q Q Parallel input Clock President University Erwin Sitompul Digital Systems 11/7

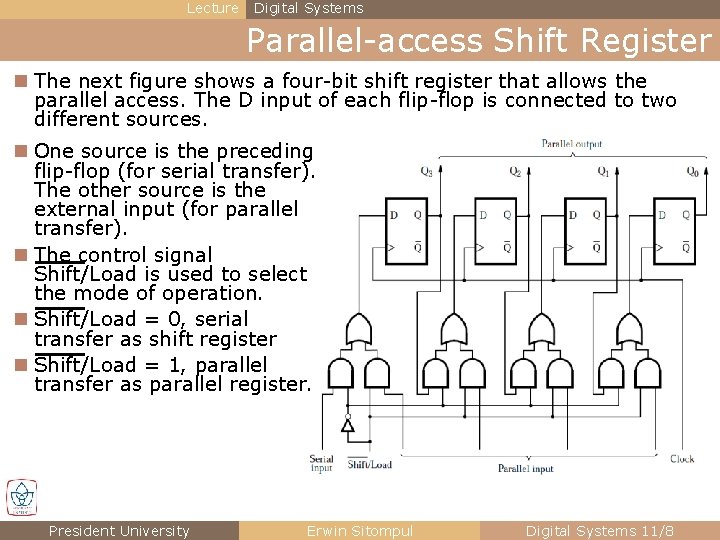

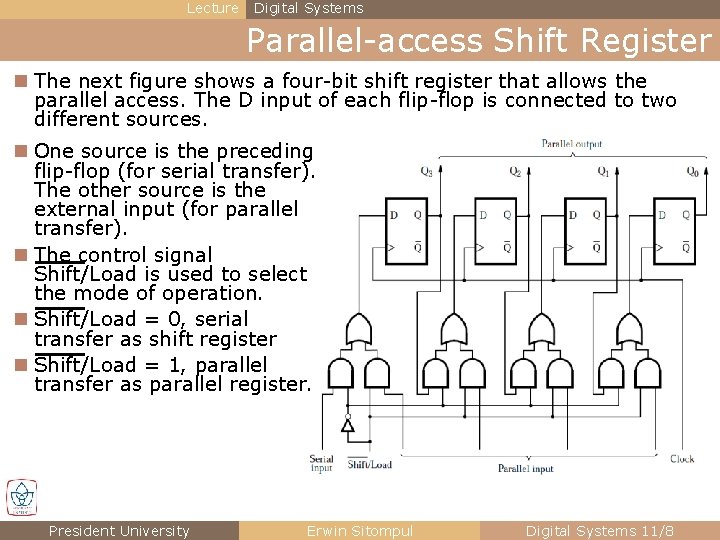

Lecture Digital Systems Parallel-access Shift Register n The next figure shows a four-bit shift register that allows the parallel access. The D input of each flip-flop is connected to two different sources. n One source is the preceding flip-flop (for serial transfer). The other source is the external input (for parallel transfer). n The control signal Shift/Load is used to select the mode of operation. n Shift/Load = 0, serial transfer as shift register n Shift/Load = 1, parallel transfer as parallel register. President University Erwin Sitompul Digital Systems 11/8

Lecture Digital Systems Section 15 Binary Numbers: Multiplication and Division President University Erwin Sitompul Digital Systems 11/9

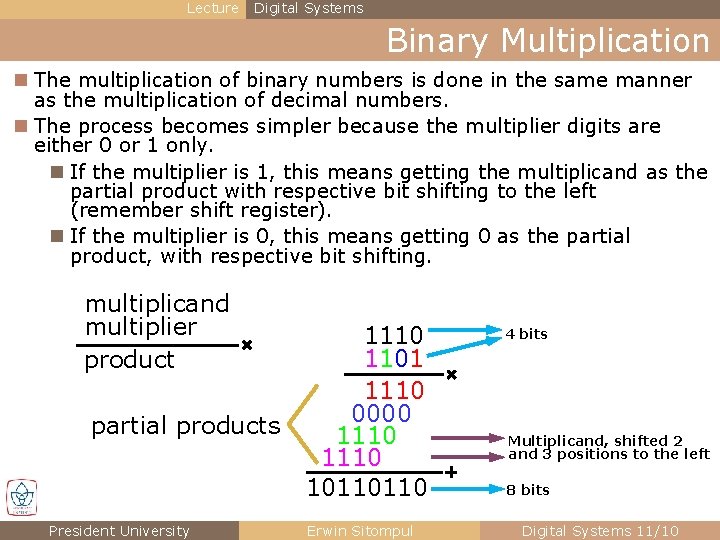

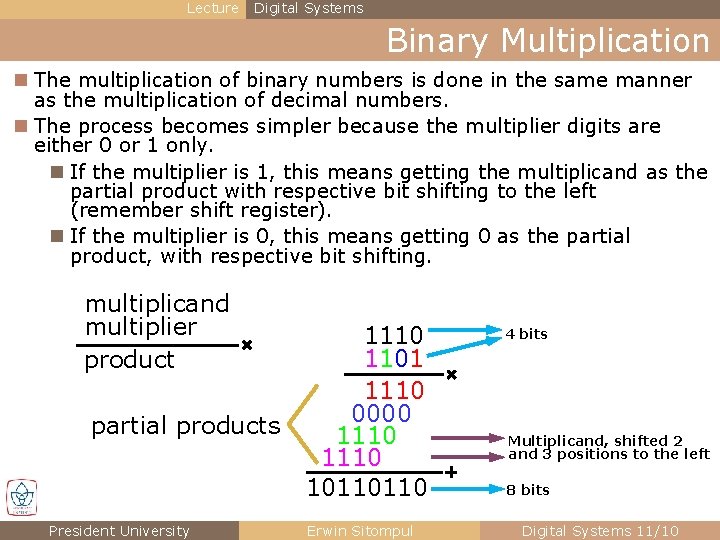

Lecture Digital Systems Binary Multiplication n The multiplication of binary numbers is done in the same manner as the multiplication of decimal numbers. n The process becomes simpler because the multiplier digits are either 0 or 1 only. n If the multiplier is 1, this means getting the multiplicand as the partial product with respective bit shifting to the left (remember shift register). n If the multiplier is 0, this means getting 0 as the partial product, with respective bit shifting. multiplicand multiplier product partial products President University 1110 1101 1110 0000 1110 10110110 Erwin Sitompul 4 bits Multiplicand, shifted 2 and 3 positions to the left 8 bits Digital Systems 11/10

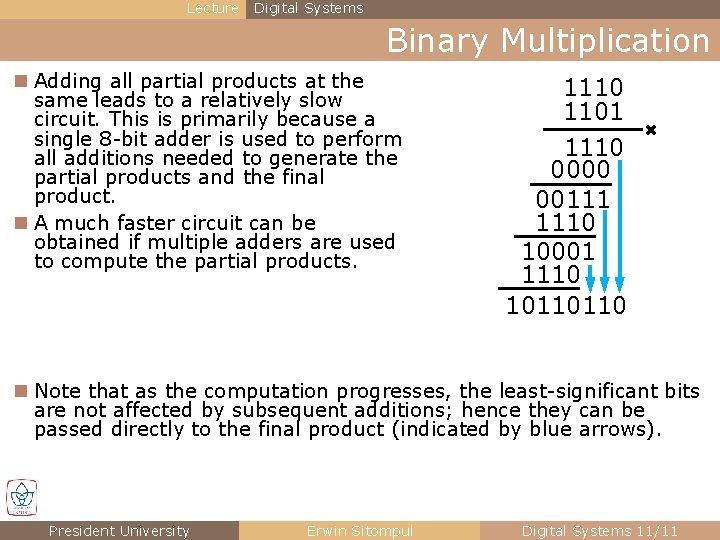

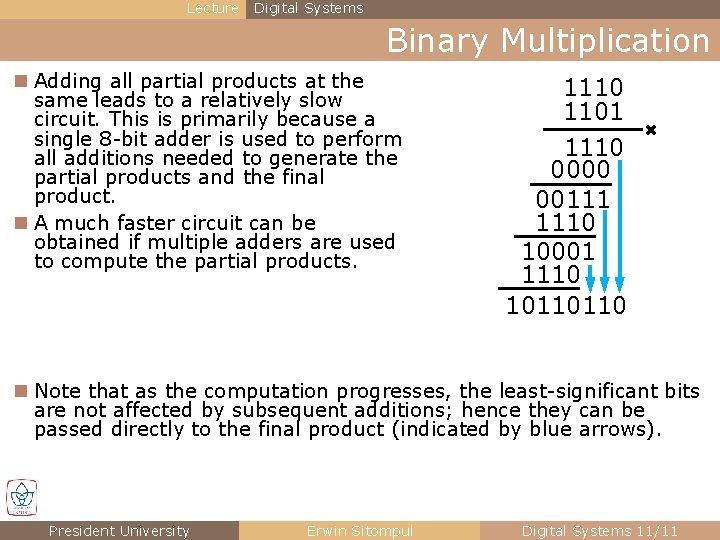

Lecture Digital Systems Binary Multiplication n Adding all partial products at the same leads to a relatively slow circuit. This is primarily because a single 8 -bit adder is used to perform all additions needed to generate the partial products and the final product. n A much faster circuit can be obtained if multiple adders are used to compute the partial products. 1110 1101 1110 0000 00111 1110 10001 1110 10110110 n Note that as the computation progresses, the least-significant bits are not affected by subsequent additions; hence they can be passed directly to the final product (indicated by blue arrows). President University Erwin Sitompul Digital Systems 11/11

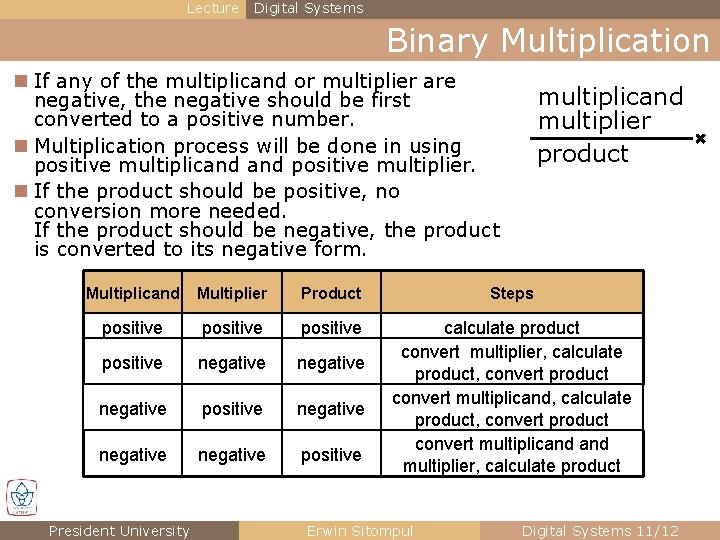

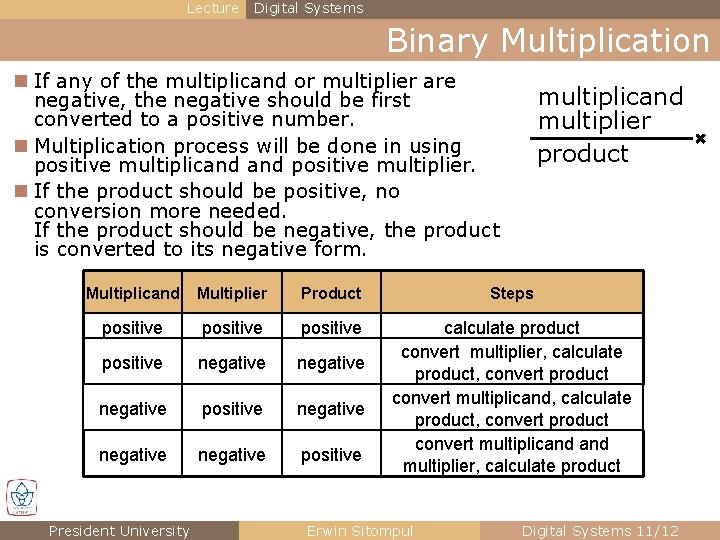

Lecture Digital Systems Binary Multiplication n If any of the multiplicand or multiplier are negative, the negative should be first converted to a positive number. n Multiplication process will be done in using positive multiplicand positive multiplier. n If the product should be positive, no conversion more needed. If the product should be negative, the product is converted to its negative form. multiplicand multiplier product Multiplicand Multiplier Product Steps positive negative negative positive calculate product convert multiplier, calculate product, convert product convert multiplicand and multiplier, calculate product President University Erwin Sitompul Digital Systems 11/12

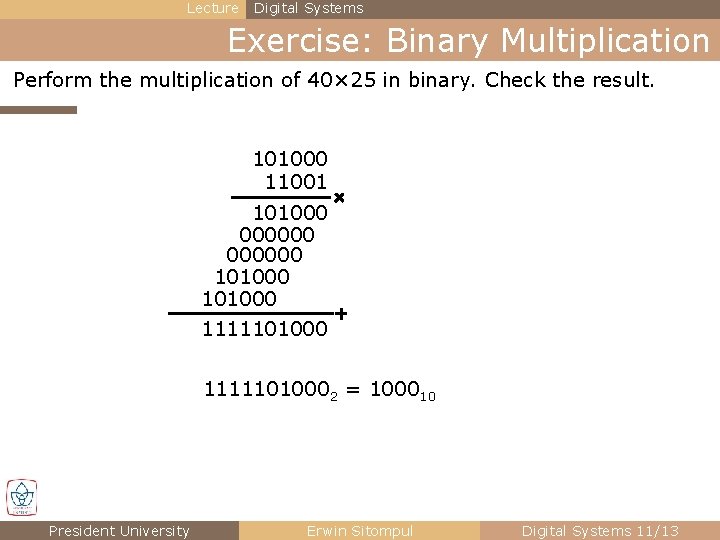

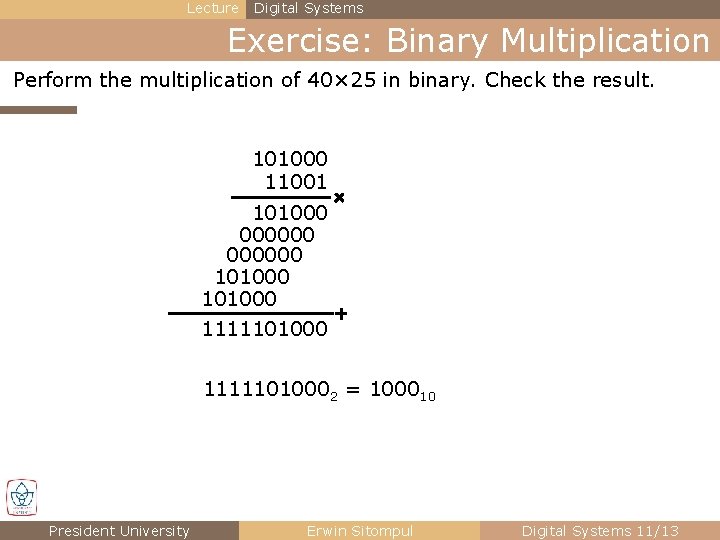

Lecture Digital Systems Exercise: Binary Multiplication Perform the multiplication of 40× 25 in binary. Check the result. 101000 11001 101000 00000000 1010000000 11111010002 = 100010 President University Erwin Sitompul Digital Systems 11/13

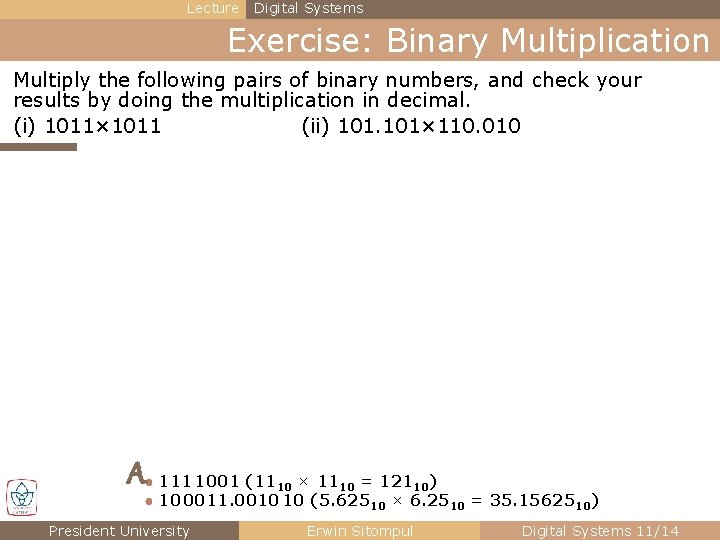

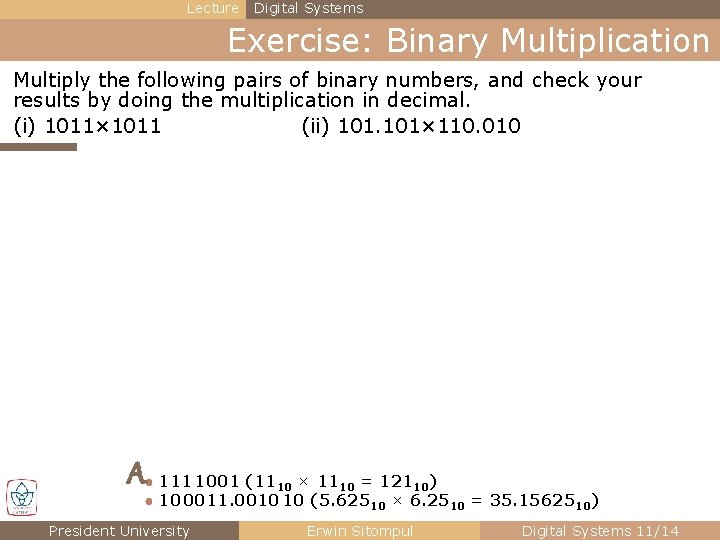

Lecture Digital Systems Exercise: Binary Multiplication Multiply the following pairs of binary numbers, and check your results by doing the multiplication in decimal. (i) 1011× 1011 (ii) 101× 110. 010 A● 111 1001 (11 × 1110 = 12110) ● 10 0011. 0010 10 (5. 62510 × 6. 2510 = 35. 1562510) President University 10 Erwin Sitompul Digital Systems 11/14

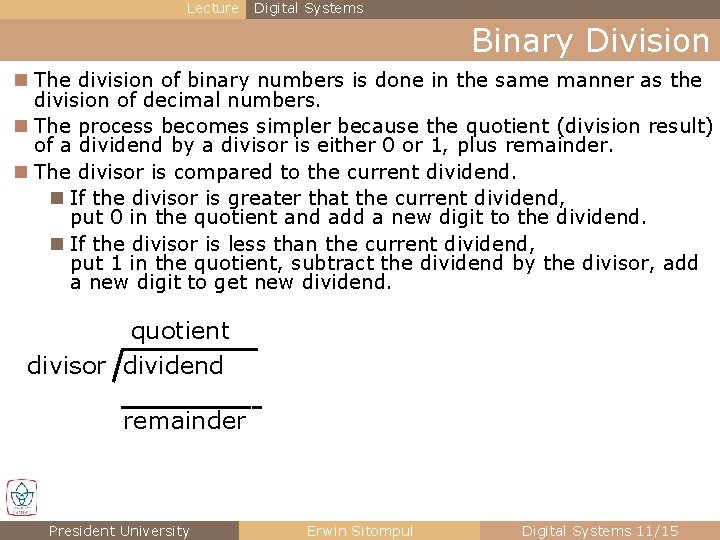

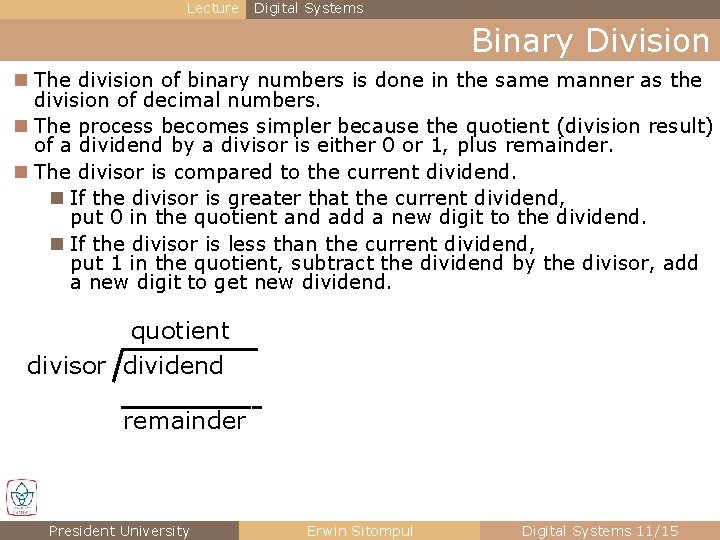

Lecture Digital Systems Binary Division n The division of binary numbers is done in the same manner as the division of decimal numbers. n The process becomes simpler because the quotient (division result) of a dividend by a divisor is either 0 or 1, plus remainder. n The divisor is compared to the current dividend. n If the divisor is greater that the current dividend, put 0 in the quotient and add a new digit to the dividend. n If the divisor is less than the current dividend, put 1 in the quotient, subtract the dividend by the divisor, add a new digit to get new dividend. quotient divisor dividend remainder President University Erwin Sitompul Digital Systems 11/15

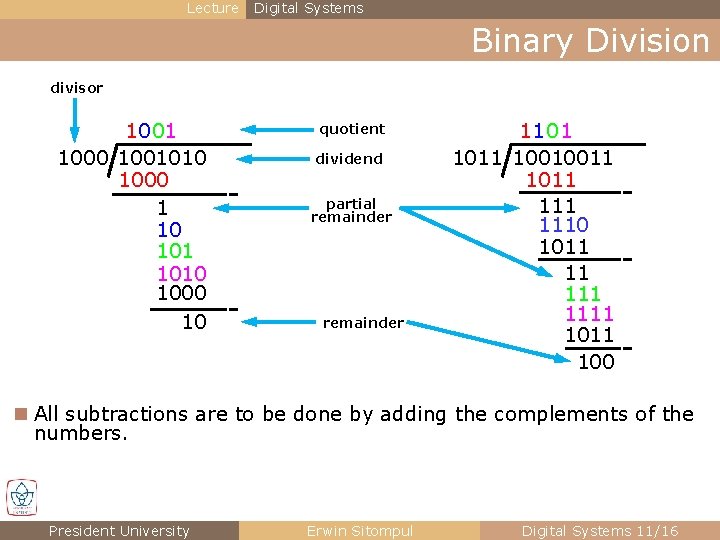

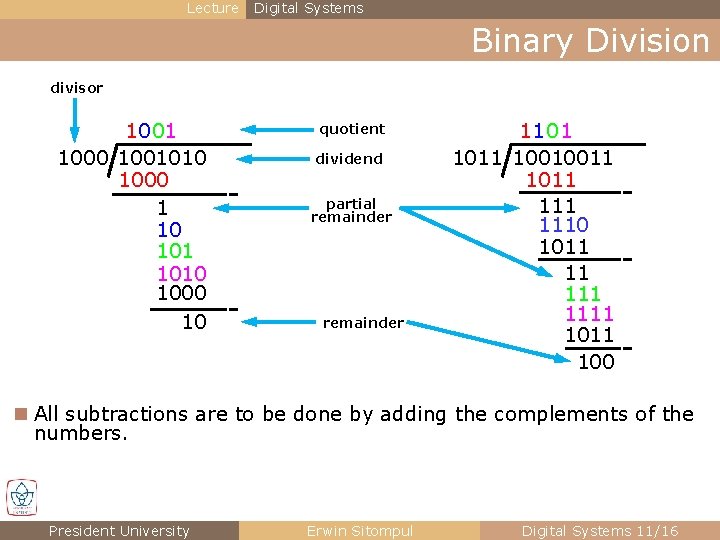

Lecture Digital Systems Binary Division divisor 10 01 1000 1001010 1000 1010 1000 10 quotient dividend partial remainder 110 1 1011 10010011 111 1110 1011 1101 11110 1111 100 n All subtractions are to be done by adding the complements of the numbers. President University Erwin Sitompul Digital Systems 11/16

Lecture Digital Systems Exercise: Binary Division Divide 01100100 by 00110010. A● 10 President University Erwin Sitompul Digital Systems 11/17

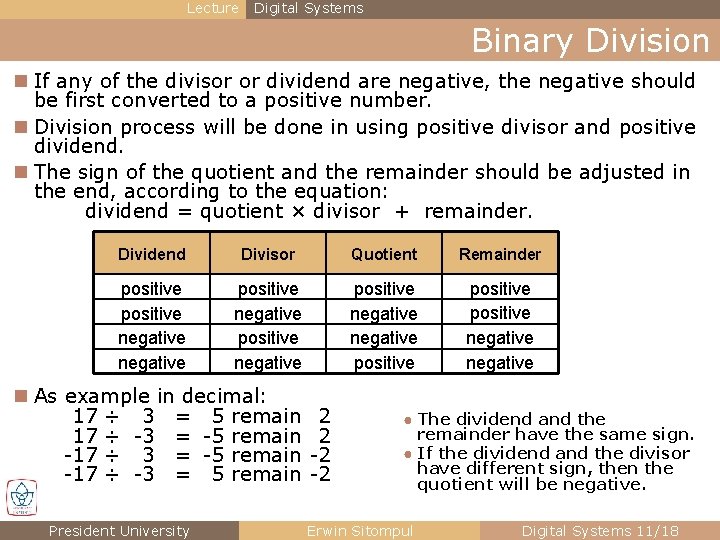

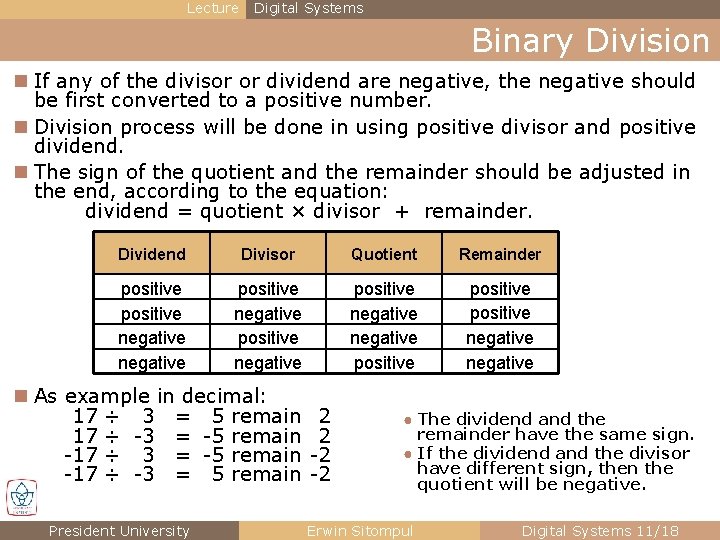

Lecture Digital Systems Binary Division n If any of the divisor or dividend are negative, the negative should be first converted to a positive number. n Division process will be done in using positive divisor and positive dividend. n The sign of the quotient and the remainder should be adjusted in the end, according to the equation: dividend = quotient × divisor + remainder. Dividend Divisor Quotient Remainder positive negative positive negative positive negative n As example in decimal: 17 ÷ 3 = 5 remain 17 ÷ -3 = -5 remain -17 ÷ -3 = 5 remain President University 2 2 -2 -2 ● The dividend and the remainder have the same sign. ● If the dividend and the divisor have different sign, then the quotient will be negative. Erwin Sitompul Digital Systems 11/18

Lecture Digital Systems Exercise: Binary Division Perform the following divisions. Check your results by doing the division in decimal. (i) 1100 ÷ 100 (ii) 10110. 1101 ÷ 1. 1 A● 11 (12 ÷ 410 = 310) ● 1111. 0011 0101 01 (22. 812510 ÷ 1. 510 = 15. 20833310) President University 10 Erwin Sitompul Digital Systems 11/19

Lecture Digital Systems Section 16 Multiplexers President University Erwin Sitompul Digital Systems 11/20

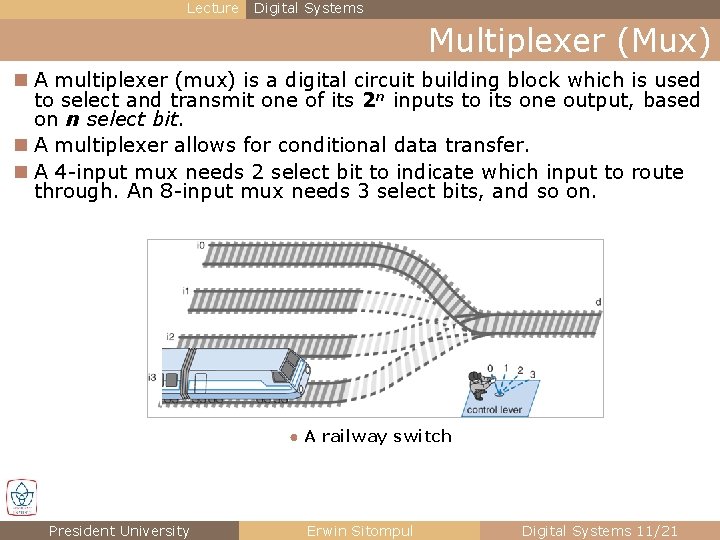

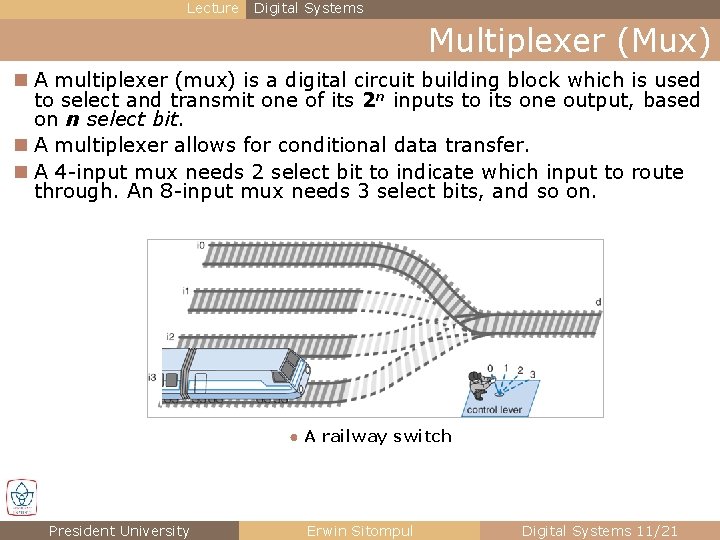

Lecture Digital Systems Multiplexer (Mux) n A multiplexer (mux) is a digital circuit building block which is used to select and transmit one of its 2 n inputs to its one output, based on n select bit. n A multiplexer allows for conditional data transfer. n A 4 -input mux needs 2 select bit to indicate which input to route through. An 8 -input mux needs 3 select bits, and so on. ● A railway switch President University Erwin Sitompul Digital Systems 11/21

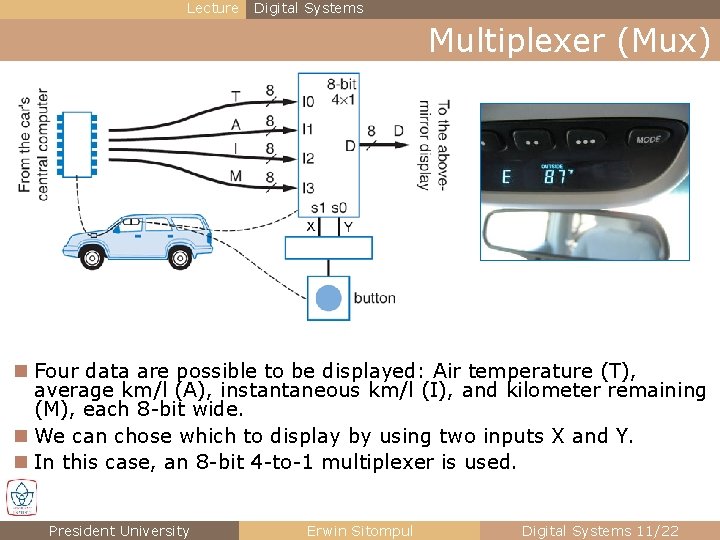

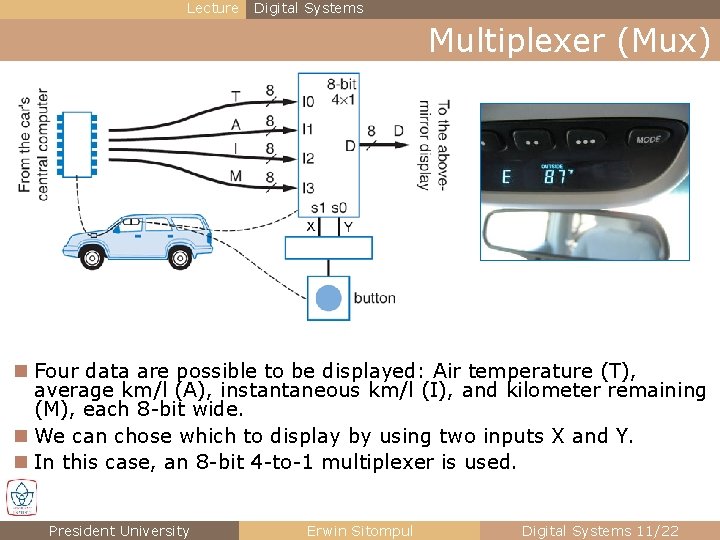

Lecture Digital Systems Multiplexer (Mux) n Four data are possible to be displayed: Air temperature (T), average km/l (A), instantaneous km/l (I), and kilometer remaining (M), each 8 -bit wide. n We can chose which to display by using two inputs X and Y. n In this case, an 8 -bit 4 -to-1 multiplexer is used. President University Erwin Sitompul Digital Systems 11/22

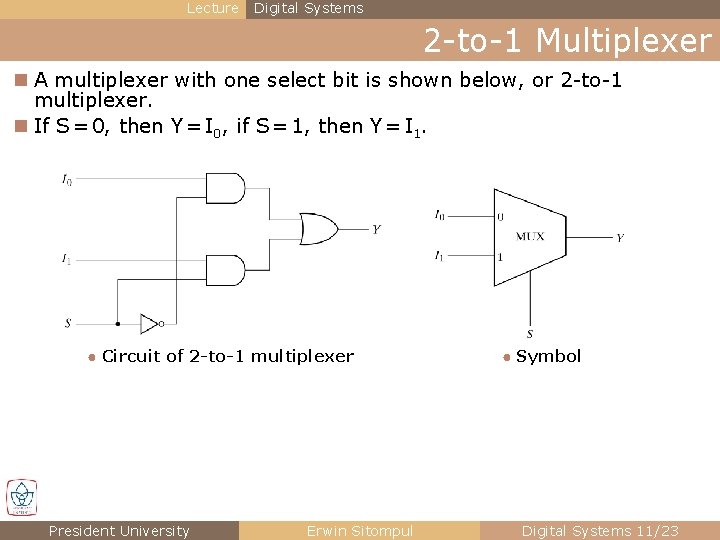

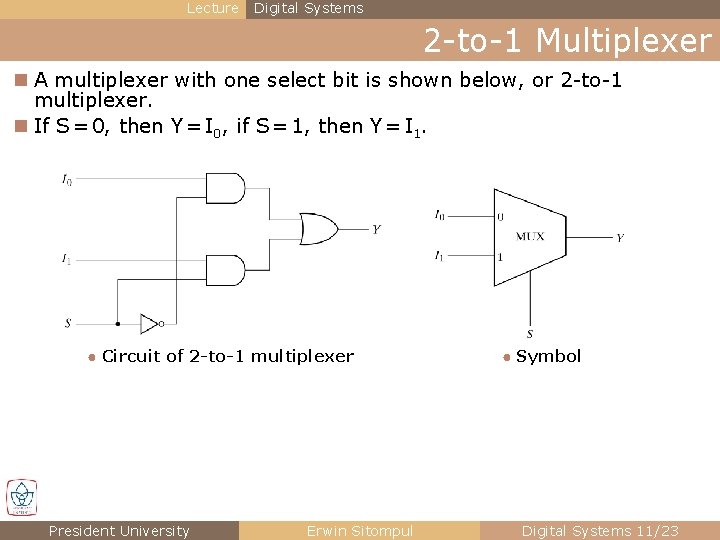

Lecture Digital Systems 2 -to-1 Multiplexer n A multiplexer with one select bit is shown below, or 2 -to-1 multiplexer. n If S = 0, then Y = I 0, if S = 1, then Y = I 1. ● Circuit of 2 -to-1 multiplexer President University Erwin Sitompul ● Symbol Digital Systems 11/23

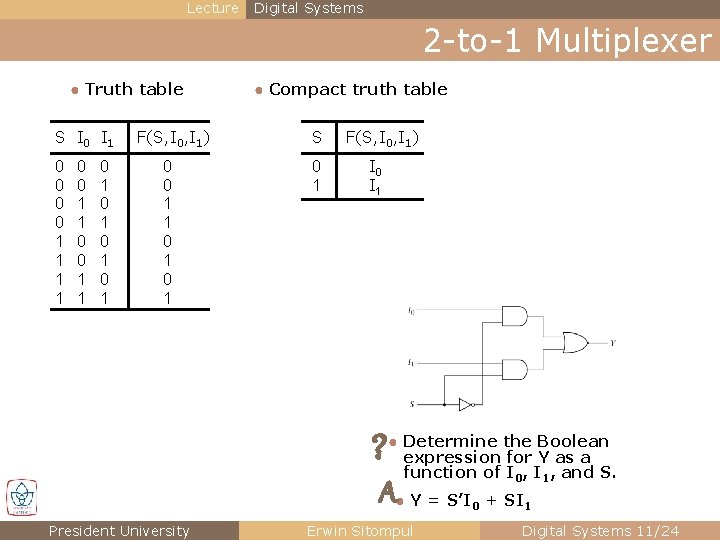

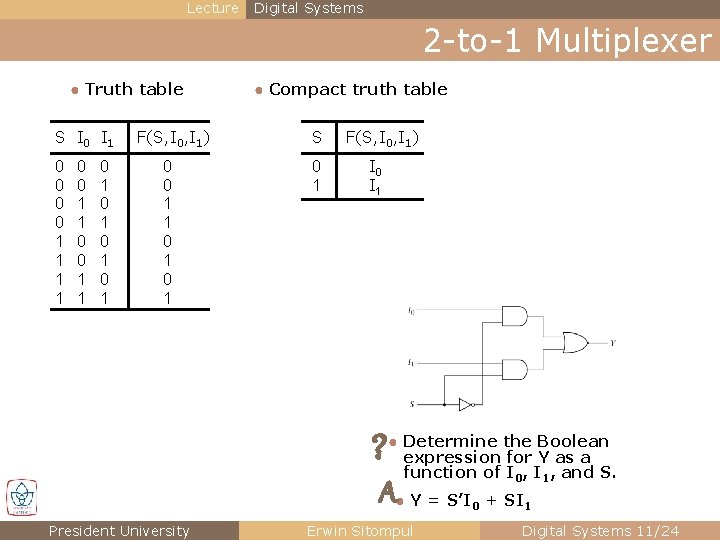

Lecture Digital Systems 2 -to-1 Multiplexer ● Truth table S I 0 I 1 0 0 1 1 0 1 0 1 F(S, I 0, I 1) 0 0 1 1 0 1 ● Compact truth table S 0 1 F(S, I 0, I 1) I 0 I 1 ? ● Determine the Boolean expression for Y as a function of I 0, I 1, and S. A● Y = S’I President University Erwin Sitompul 0 + SI 1 Digital Systems 11/24

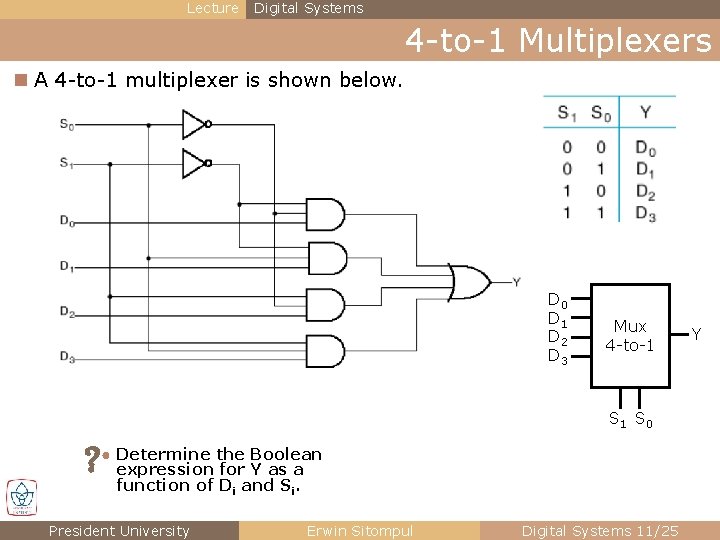

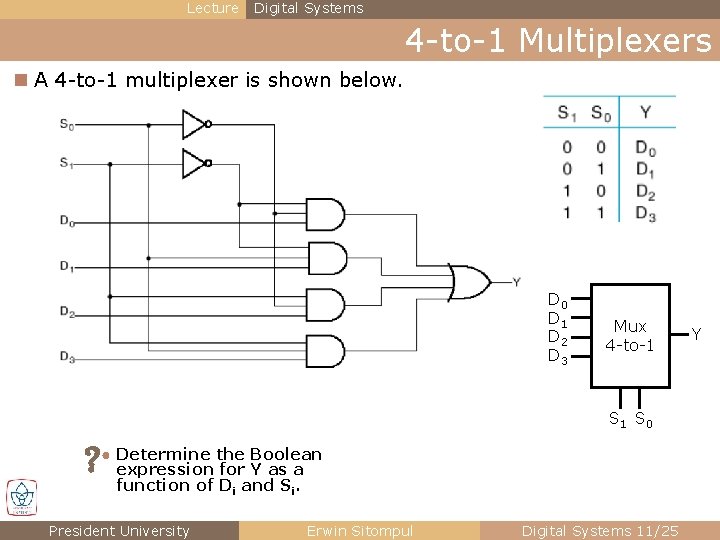

Lecture Digital Systems 4 -to-1 Multiplexers n A 4 -to-1 multiplexer is shown below. D 0 D 1 D 2 D 3 Mux 4 -to-1 S 0 ? ● Determine the Boolean expression for Y as a function of Di and Si. President University Erwin Sitompul Digital Systems 11/25 Y

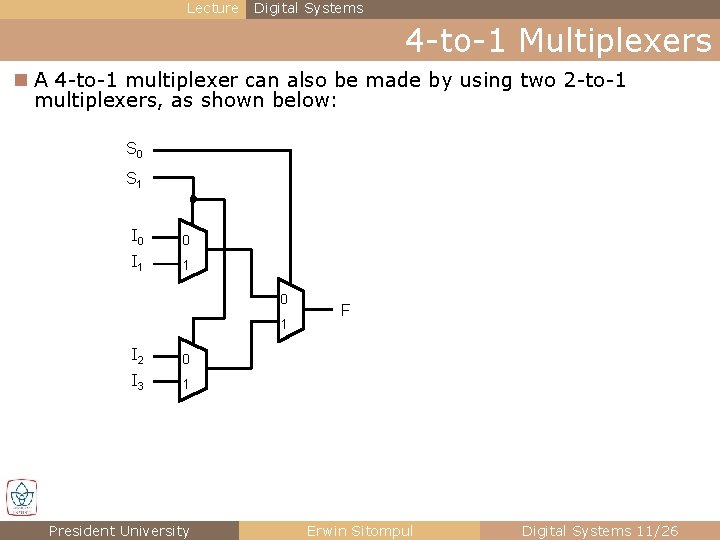

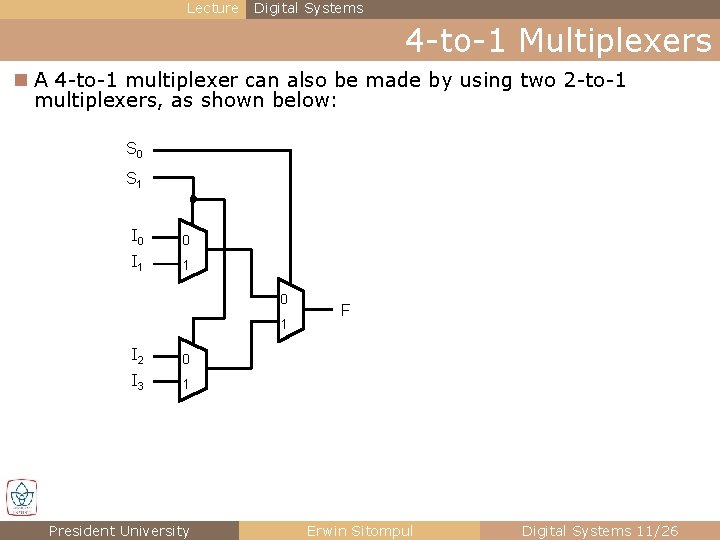

Lecture Digital Systems 4 -to-1 Multiplexers n A 4 -to-1 multiplexer can also be made by using two 2 -to-1 multiplexers, as shown below: S 0 S 1 I 0 0 I 1 1 0 1 I 2 0 I 3 1 President University F Erwin Sitompul Digital Systems 11/26

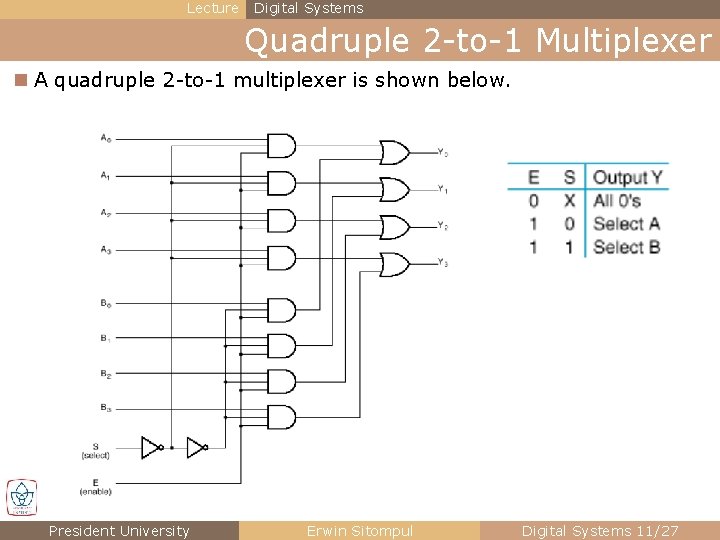

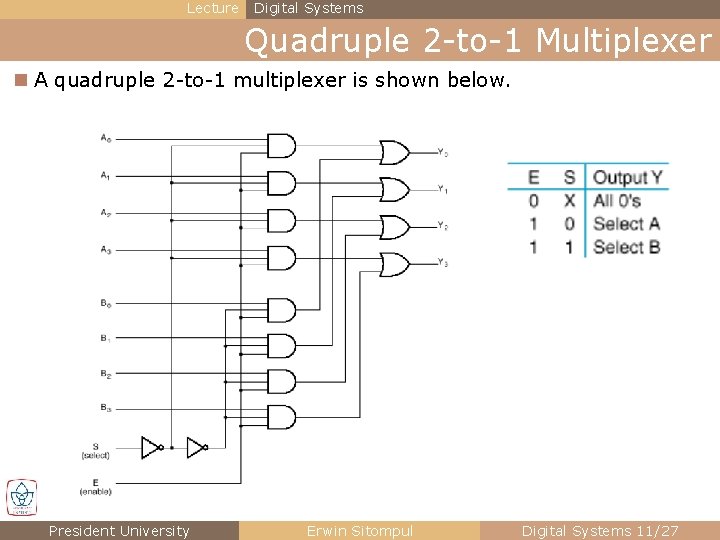

Lecture Digital Systems Quadruple 2 -to-1 Multiplexer n A quadruple 2 -to-1 multiplexer is shown below. President University Erwin Sitompul Digital Systems 11/27

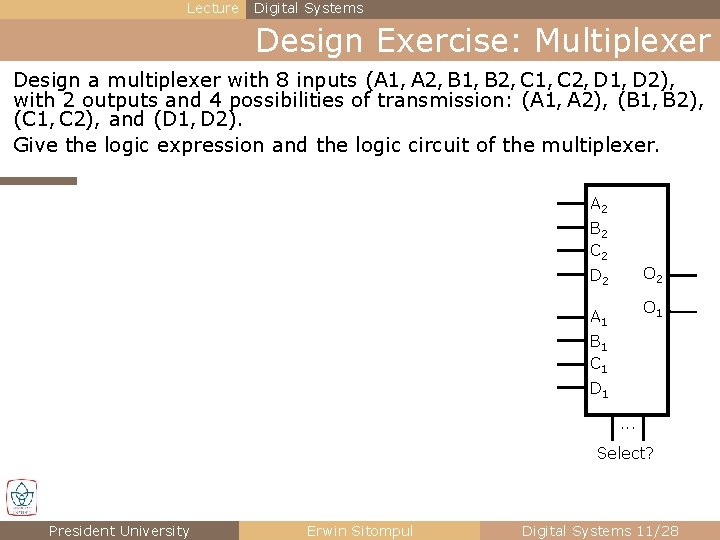

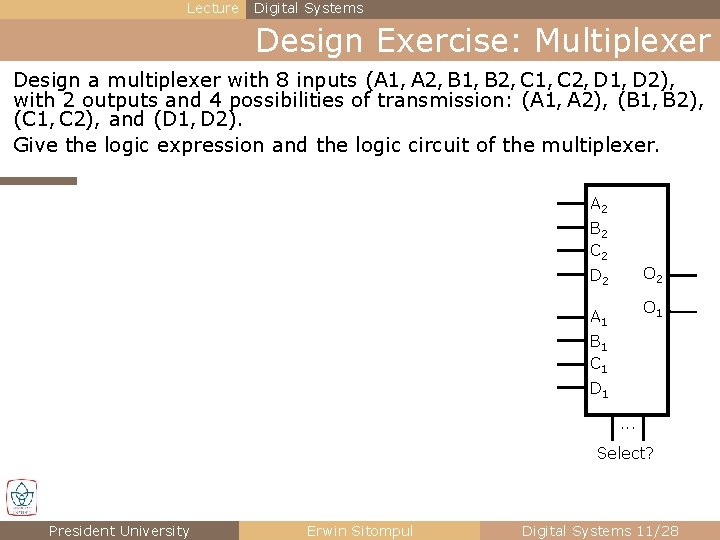

Lecture Digital Systems Design Exercise: Multiplexer Design a multiplexer with 8 inputs (A 1, A 2, B 1, B 2, C 1, C 2, D 1, D 2), with 2 outputs and 4 possibilities of transmission: (A 1, A 2), (B 1, B 2), (C 1, C 2), and (D 1, D 2). Give the logic expression and the logic circuit of the multiplexer. A 2 B 2 C 2 O 2 D 2 O 1 A 1 B 1 C 1 D 1. . . Select? President University Erwin Sitompul Digital Systems 11/28

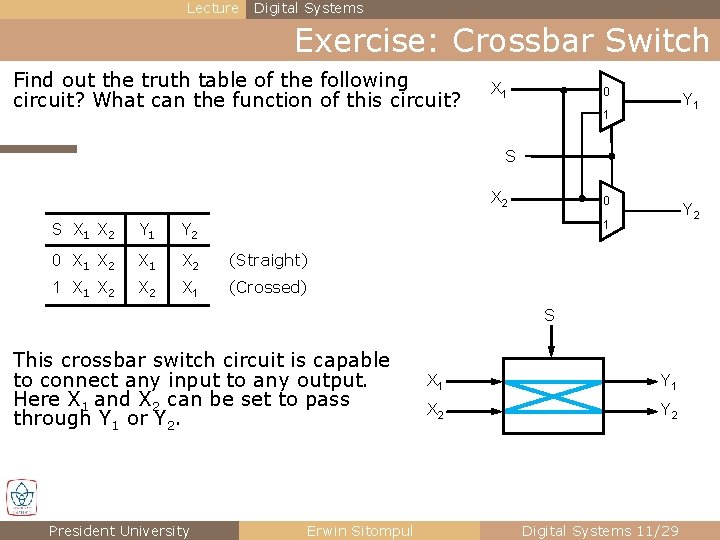

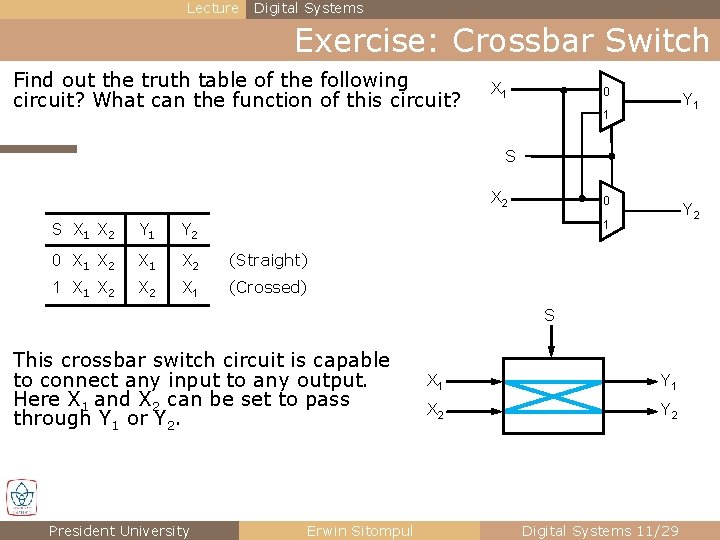

Lecture Digital Systems Exercise: Crossbar Switch Find out the truth table of the following circuit? What can the function of this circuit? X 1 0 Y 1 1 S X 2 0 Y 2 1 S X 1 X 2 Y 1 Y 2 0 X 1 X 2 (Straight) 1 X 2 X 1 (Crossed) S This crossbar switch circuit is capable to connect any input to any output. Here X 1 and X 2 can be set to pass through Y 1 or Y 2. President University Erwin Sitompul X 1 Y 1 X 2 Y 2 Digital Systems 11/29

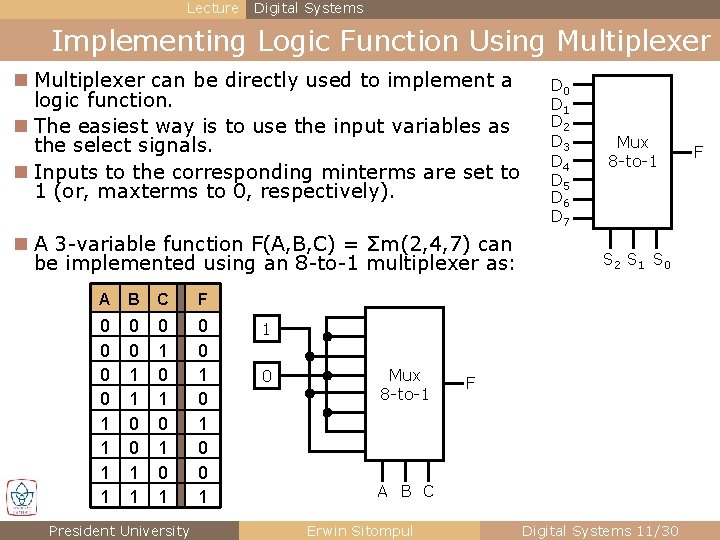

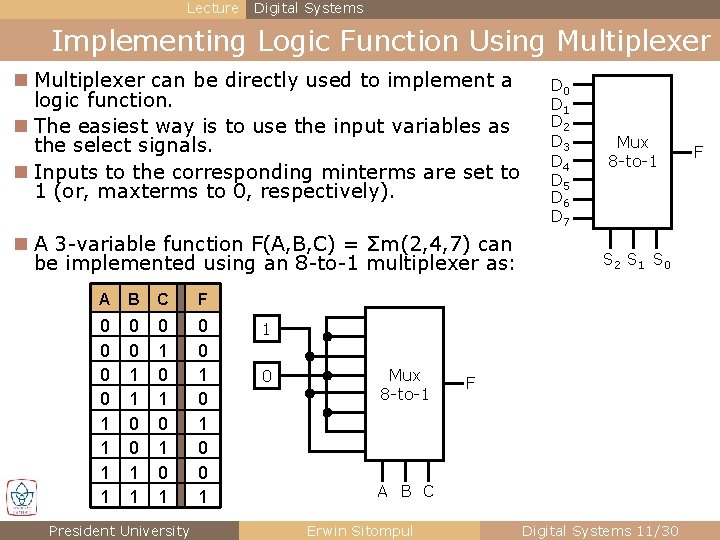

Lecture Digital Systems Implementing Logic Function Using Multiplexer n Multiplexer can be directly used to implement a logic function. n The easiest way is to use the input variables as the select signals. n Inputs to the corresponding minterms are set to 1 (or, maxterms to 0, respectively). n A 3 -variable function F(A, B, C) = Σm(2, 4, 7) can be implemented using an 8 -to-1 multiplexer as: A B C F 0 0 1 1 0 1 0 1 0 0 1 President University D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 Mux 8 -to-1 S 2 S 1 S 0 1 0 Mux 8 -to-1 F A B C Erwin Sitompul Digital Systems 11/30 F

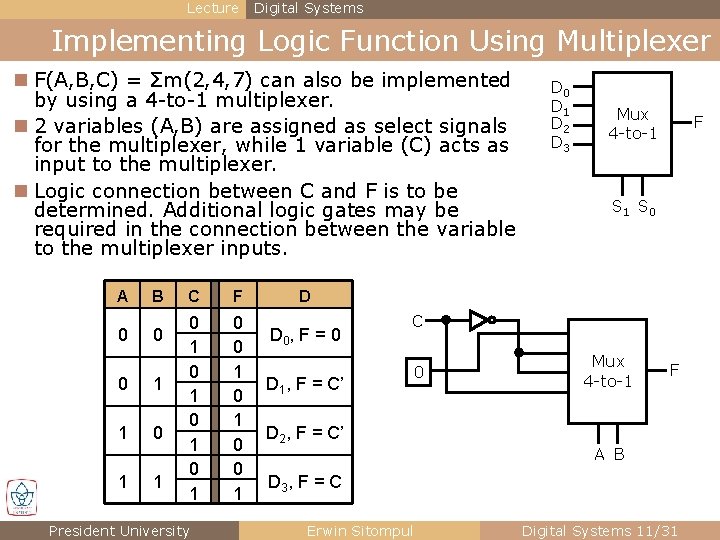

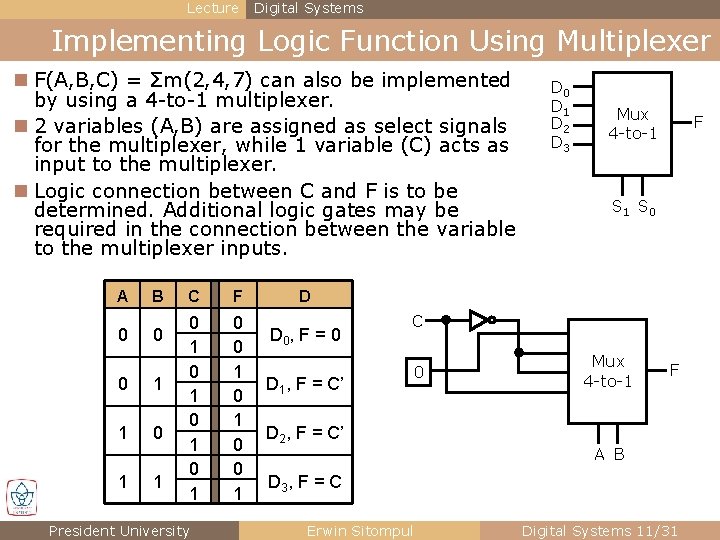

Lecture Digital Systems Implementing Logic Function Using Multiplexer n F(A, B, C) = Σm(2, 4, 7) can also be implemented by using a 4 -to-1 multiplexer. n 2 variables (A, B) are assigned as select signals for the multiplexer, while 1 variable (C) acts as input to the multiplexer. n Logic connection between C and F is to be determined. Additional logic gates may be required in the connection between the variable to the multiplexer inputs. A 0 B 0 0 1 1 C F 0 1 0 1 0 0 1 President University D 0 D 1 D 2 D 3 Mux 4 -to-1 F S 1 S 0 D D 0 , F = 0 D 1, F = C’ C 0 D 2, F = C’ Mux 4 -to-1 F A B D 3 , F = C Erwin Sitompul Digital Systems 11/31

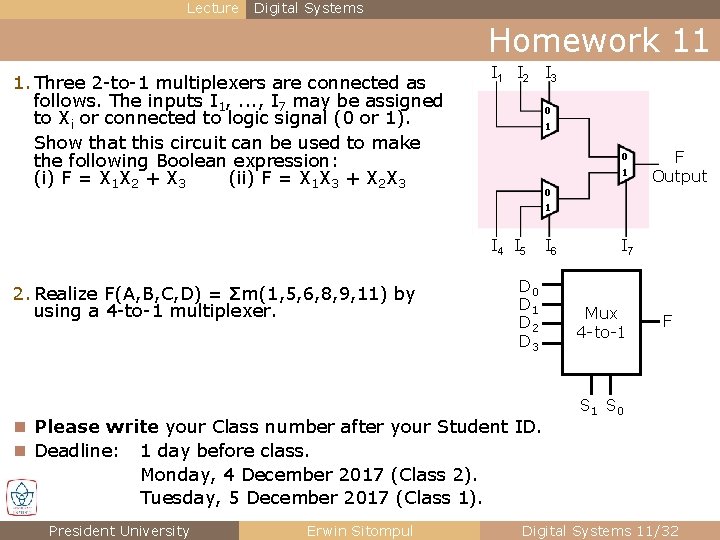

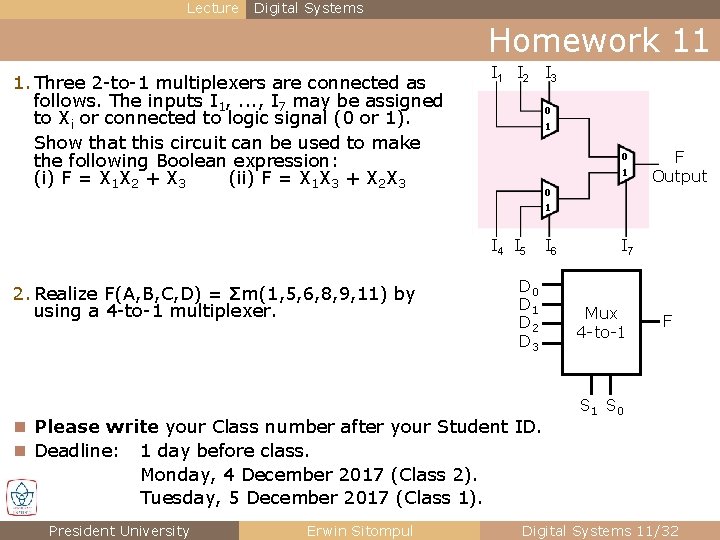

Lecture Digital Systems Homework 11 1. Three 2 -to-1 multiplexers are connected as follows. The inputs I 1, . . . , I 7 may be assigned to Xi or connected to logic signal (0 or 1). Show that this circuit can be used to make the following Boolean expression: (i) F = X 1 X 2 + X 3 (ii) F = X 1 X 3 + X 2 X 3 I 1 I 2 I 3 0 1 0 F Output 1 I 4 I 5 2. Realize F(A, B, C, D) = Σm(1, 5, 6, 8, 9, 11) by using a 4 -to-1 multiplexer. D 0 D 1 D 2 D 3 n Please write your Class number after your Student ID. n Deadline: 1 day before class. Monday, 4 December 2017 (Class 2). Tuesday, 5 December 2017 (Class 1). President University Erwin Sitompul I 6 I 7 Mux 4 -to-1 F S 1 S 0 Digital Systems 11/32