Digital Systems Lecture 9 Dr Ing Erwin Sitompul

- Slides: 33

Digital Systems Lecture 9 Dr. -Ing. Erwin Sitompul President University http: //zitompul. wordpress. com 2 0 1 7 President University Erwin Sitompul Digital Systems 9/1

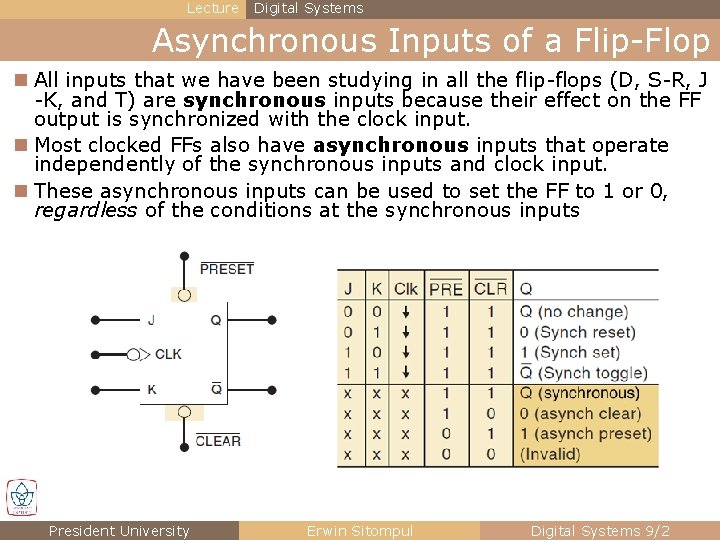

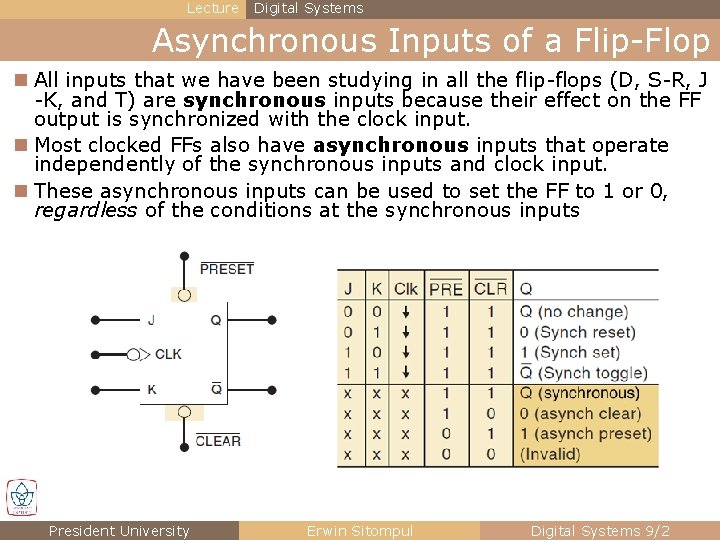

Lecture Digital Systems Asynchronous Inputs of a Flip-Flop n All inputs that we have been studying in all the flip-flops (D, S-R, J -K, and T) are synchronous inputs because their effect on the FF output is synchronized with the clock input. n Most clocked FFs also have asynchronous inputs that operate independently of the synchronous inputs and clock input. n These asynchronous inputs can be used to set the FF to 1 or 0, regardless of the conditions at the synchronous inputs President University Erwin Sitompul Digital Systems 9/2

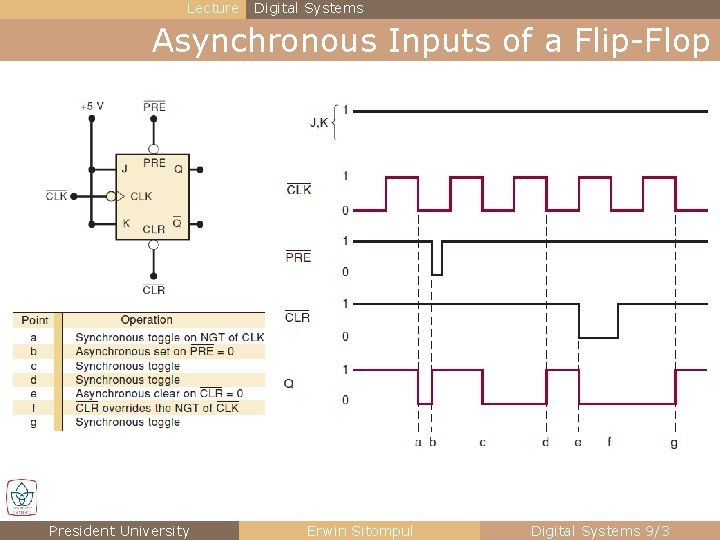

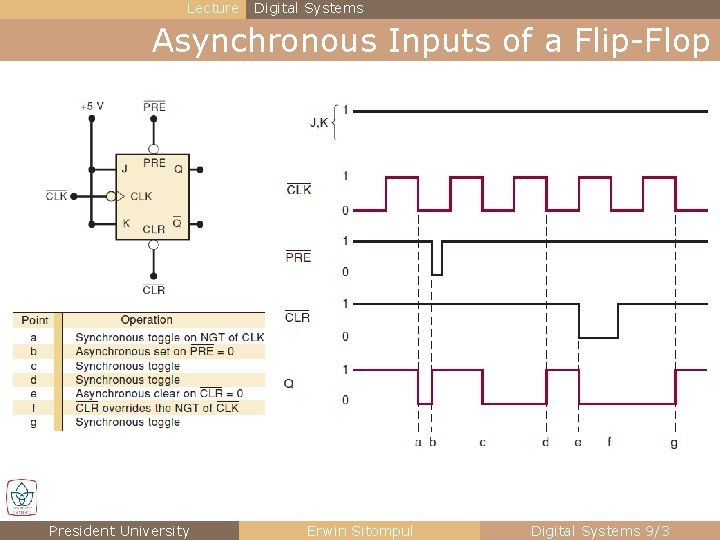

Lecture Digital Systems Asynchronous Inputs of a Flip-Flop President University Erwin Sitompul Digital Systems 9/3

Lecture Digital Systems Summary Flip-flops n Flip-flops are powerful storage elements. They are constructed from gates and latches. n D flip-flop is the simplest and the most widely used type. n Multiple flip-flops allow for data storage. They are the basis of computer memory. n Furthermore, combination of sequential logic and combinatorial logic build computation circuit. President University Erwin Sitompul Digital Systems 9/4

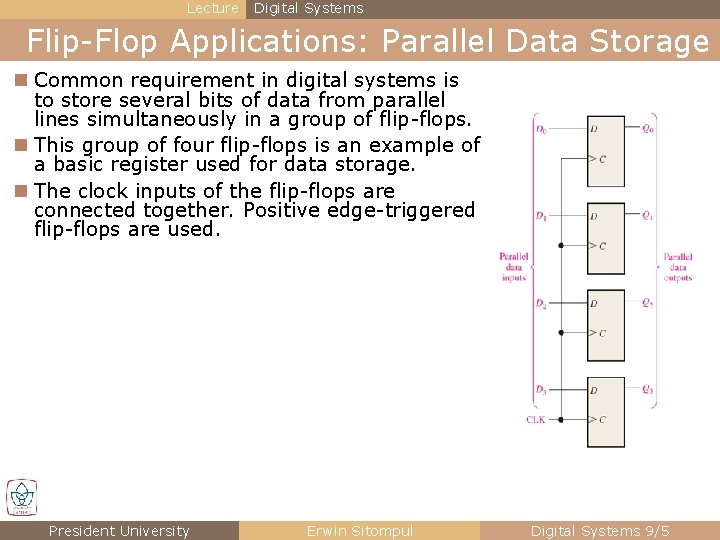

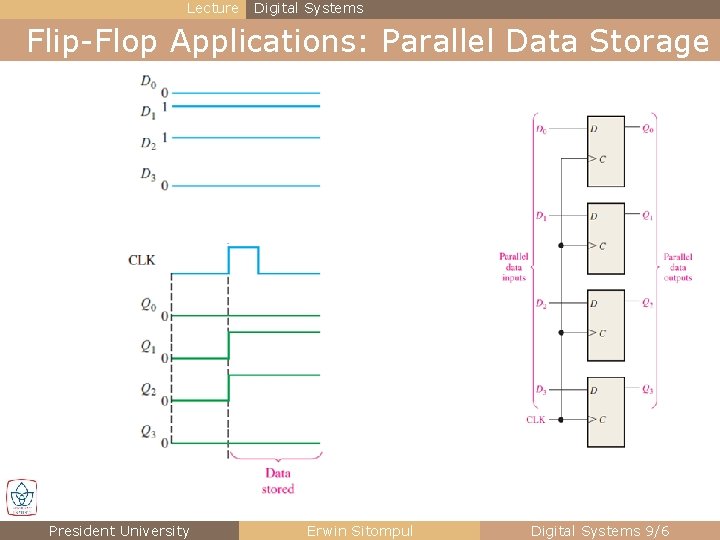

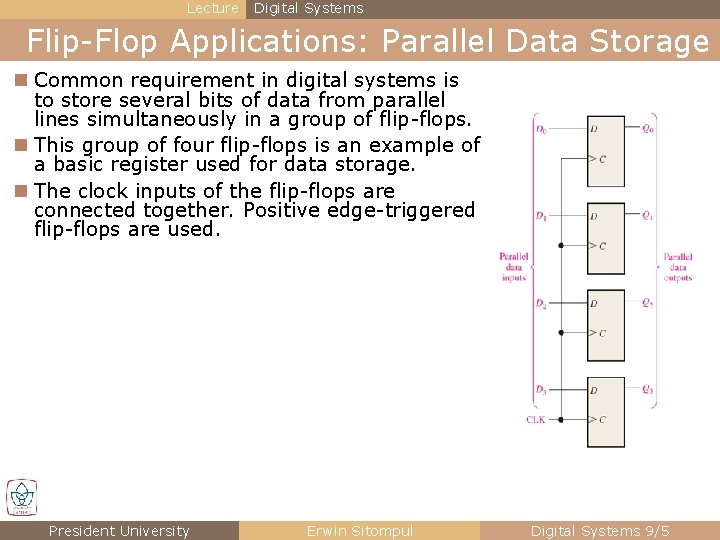

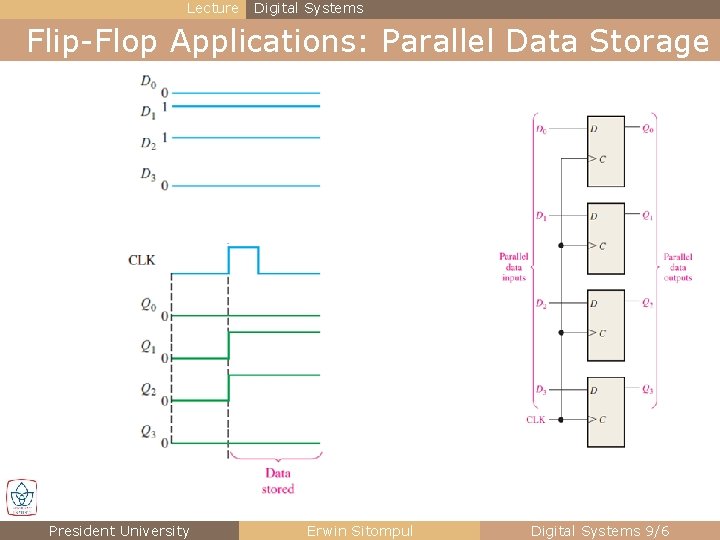

Lecture Digital Systems Flip-Flop Applications: Parallel Data Storage n Common requirement in digital systems is to store several bits of data from parallel lines simultaneously in a group of flip-flops. n This group of four flip-flops is an example of a basic register used for data storage. n The clock inputs of the flip-flops are connected together. Positive edge-triggered flip-flops are used. President University Erwin Sitompul Digital Systems 9/5

Lecture Digital Systems Flip-Flop Applications: Parallel Data Storage President University Erwin Sitompul Digital Systems 9/6

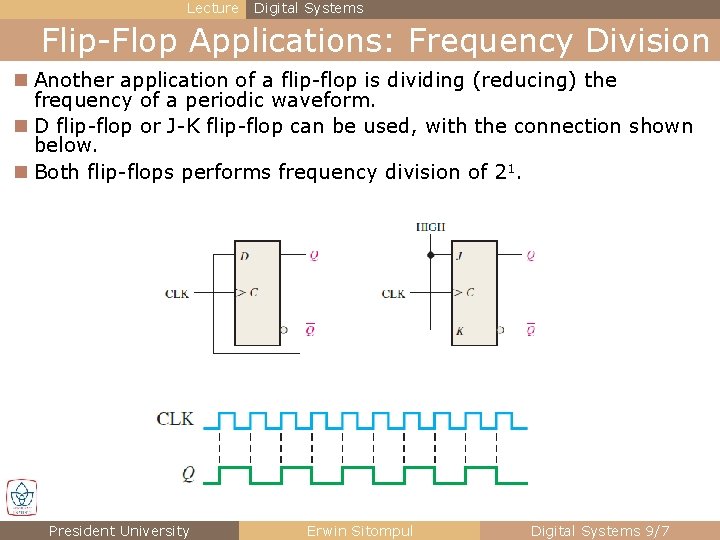

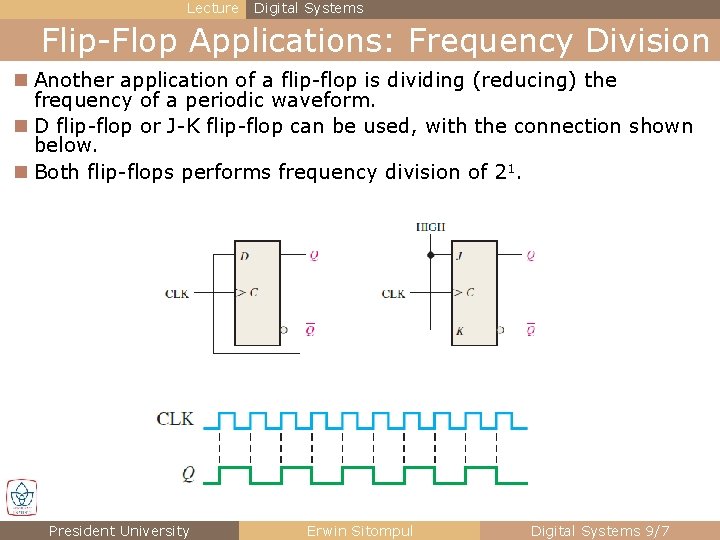

Lecture Digital Systems Flip-Flop Applications: Frequency Division n Another application of a flip-flop is dividing (reducing) the frequency of a periodic waveform. n D flip-flop or J-K flip-flop can be used, with the connection shown below. n Both flip-flops performs frequency division of 21. President University Erwin Sitompul Digital Systems 9/7

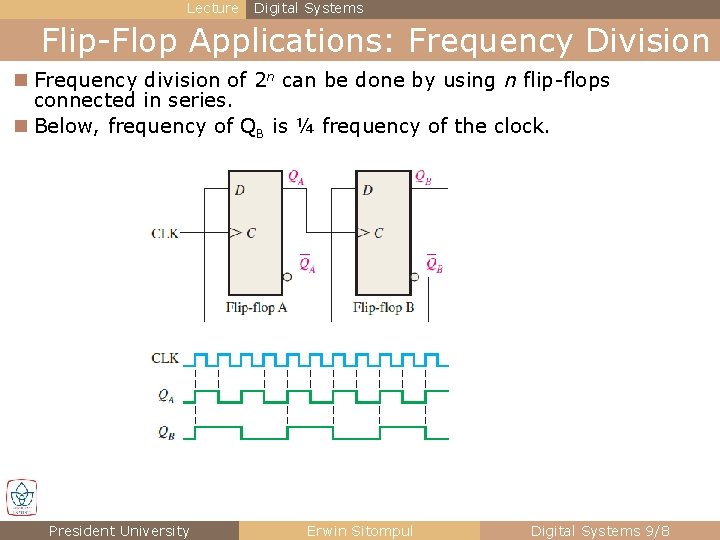

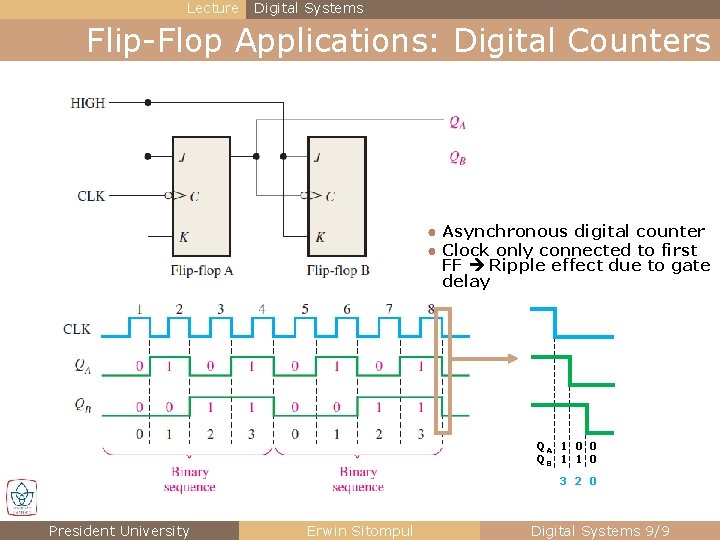

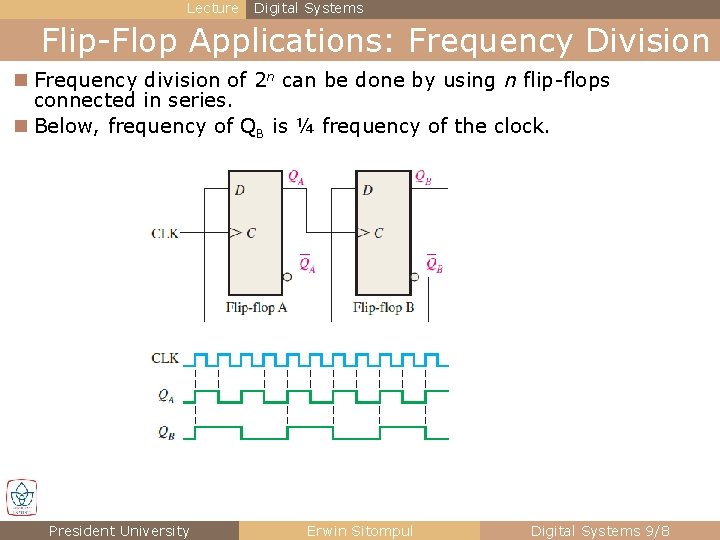

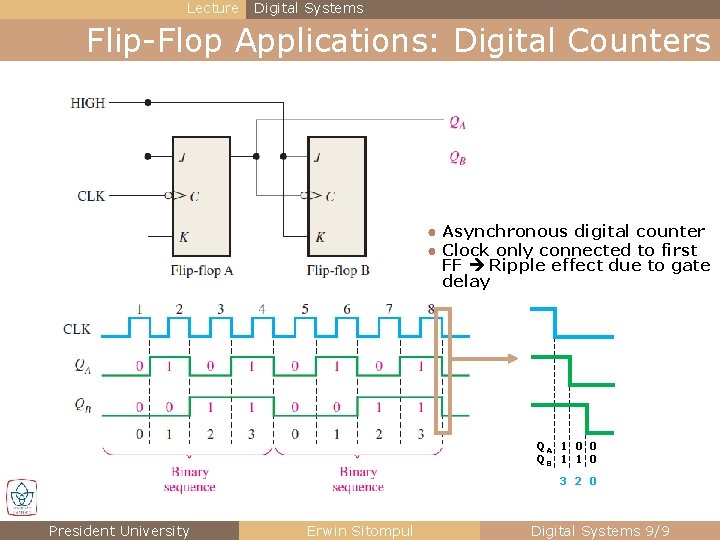

Lecture Digital Systems Flip-Flop Applications: Frequency Division n Frequency division of 2 n can be done by using n flip-flops connected in series. n Below, frequency of QB is ¼ frequency of the clock. President University Erwin Sitompul Digital Systems 9/8

Lecture Digital Systems Flip-Flop Applications: Digital Counters ● Asynchronous digital counter ● Clock only connected to first FF Ripple effect due to gate delay QA 1 0 0 QB 1 1 0 3 2 0 President University Erwin Sitompul Digital Systems 9/9

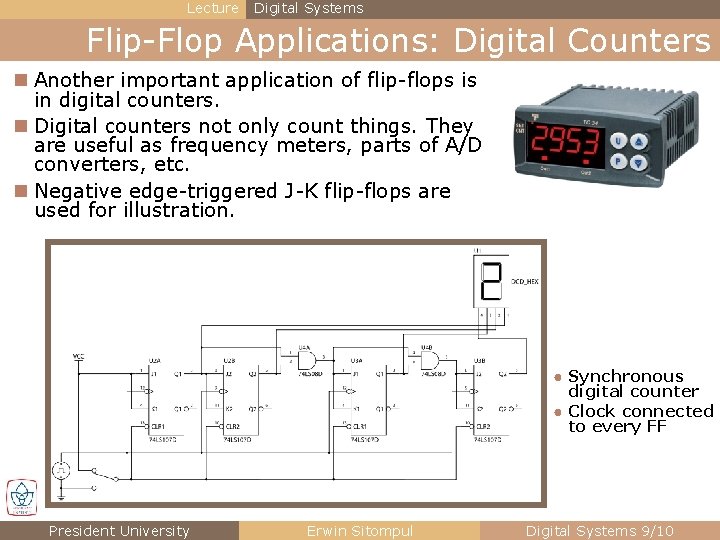

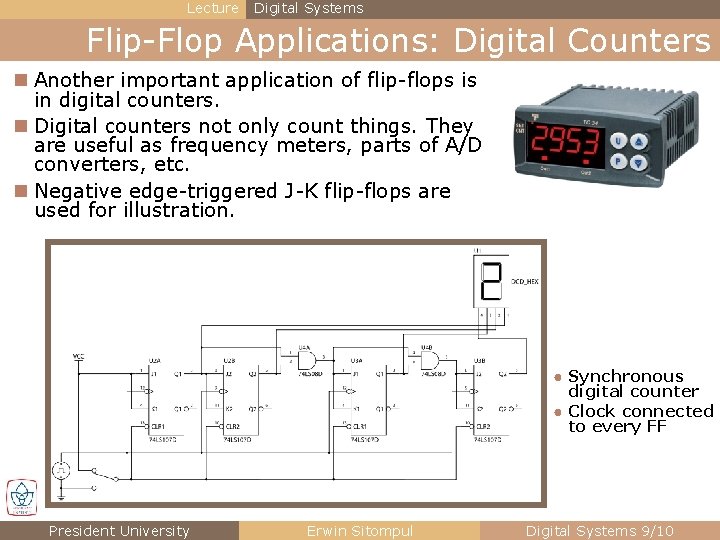

Lecture Digital Systems Flip-Flop Applications: Digital Counters n Another important application of flip-flops is in digital counters. n Digital counters not only count things. They are useful as frequency meters, parts of A/D converters, etc. n Negative edge-triggered J-K flip-flops are used for illustration. ● Synchronous digital counter ● Clock connected to every FF President University Erwin Sitompul Digital Systems 9/10

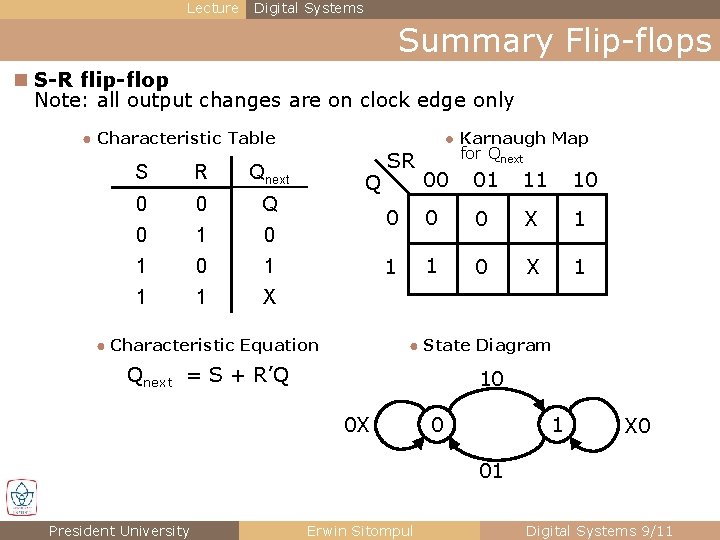

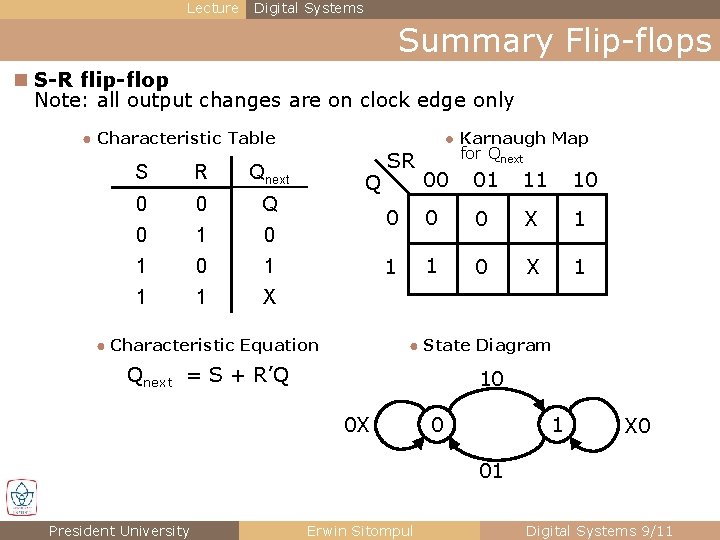

Lecture Digital Systems Summary Flip-flops n S-R flip-flop Note: all output changes are on clock edge only ● Karnaugh Map for Qnext ● Characteristic Table S R Qnext 0 0 Q 0 1 0 1 1 1 X Q ● Characteristic Equation SR 00 01 11 10 0 X 1 1 1 0 X 1 ● State Diagram Qnext = S + R’Q 10 0 X 0 1 X 0 01 President University Erwin Sitompul Digital Systems 9/11

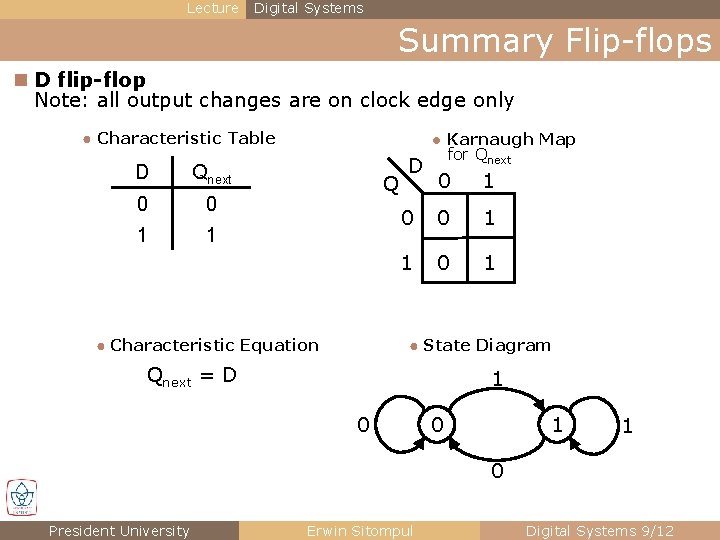

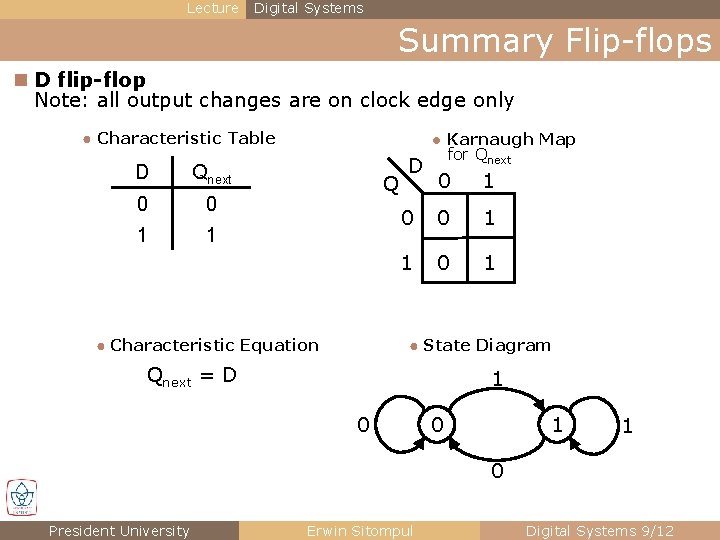

Lecture Digital Systems Summary Flip-flops n D flip-flop Note: all output changes are on clock edge only ● Characteristic Table D Qnext 0 0 1 1 Q ● Characteristic Equation D ● Karnaugh Map for Qnext 0 1 0 0 1 1 0 1 ● State Diagram Qnext = D 1 0 0 1 1 0 President University Erwin Sitompul Digital Systems 9/12

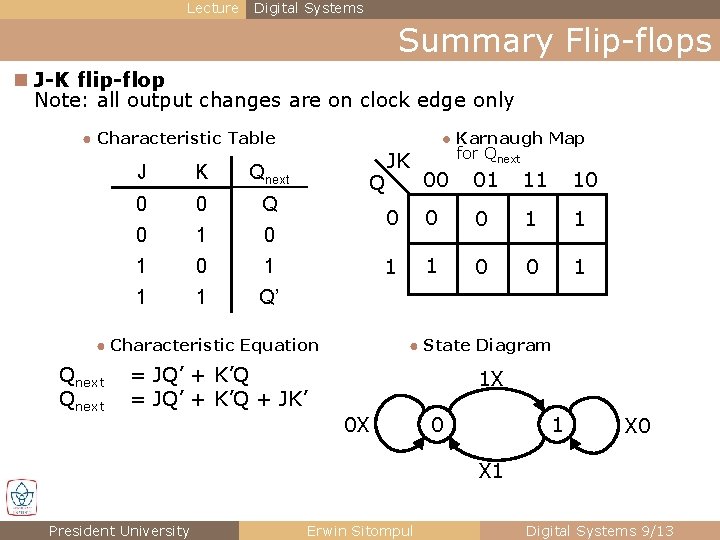

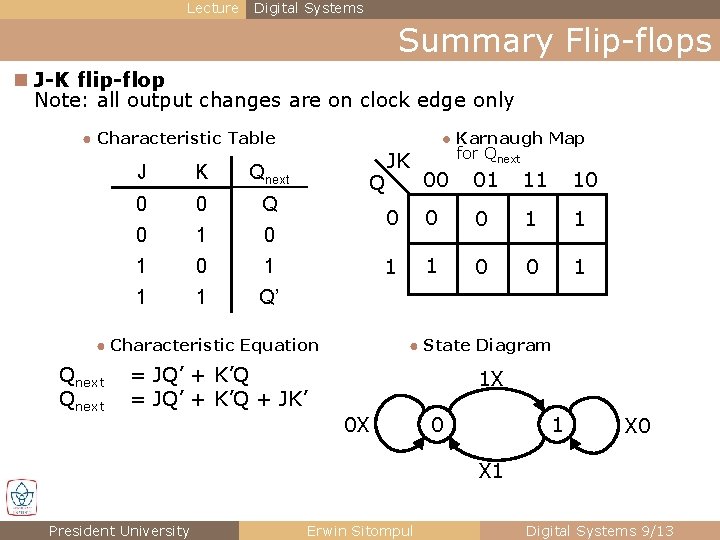

Lecture Digital Systems Summary Flip-flops n J-K flip-flop Note: all output changes are on clock edge only ● Karnaugh Map for Qnext ● Characteristic Table J K Qnext 0 0 Q 0 1 0 1 1 1 Q’ Qnext 00 01 11 10 0 1 1 0 0 1 Q ● Characteristic Equation JK ● State Diagram = JQ’ + K’Q + JK’ 1 X 0 X 0 1 X 0 X 1 President University Erwin Sitompul Digital Systems 9/13

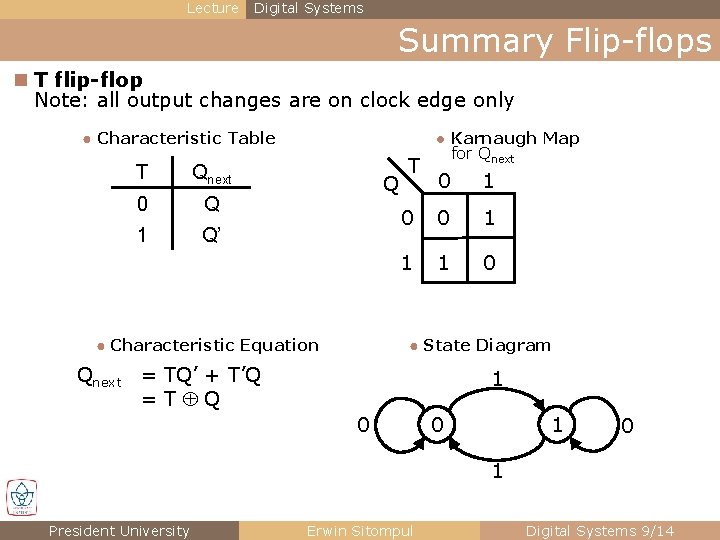

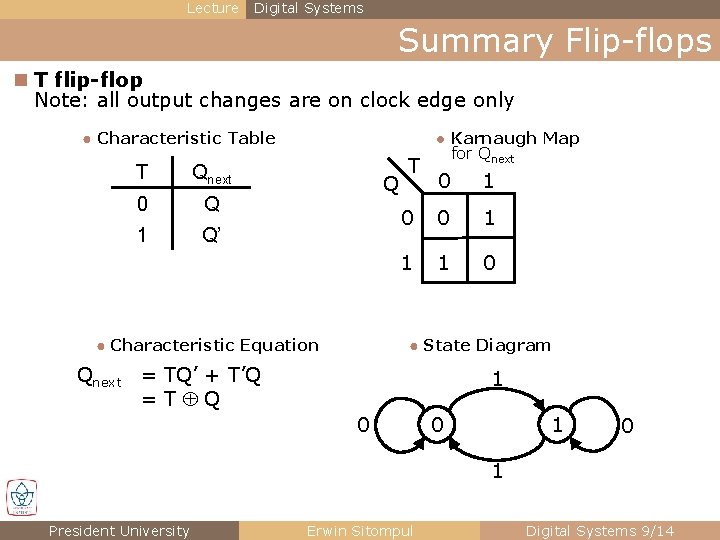

Lecture Digital Systems Summary Flip-flops n T flip-flop Note: all output changes are on clock edge only ● Characteristic Table T Qnext 0 Q 1 Q’ Q ● Characteristic Equation T ● Karnaugh Map for Qnext 0 1 0 0 1 1 1 0 ● State Diagram Qnext = TQ’ + T’Q = T Q 1 0 0 1 President University Erwin Sitompul Digital Systems 9/14

Digital Systems Section 11 Sequential Circuits: Finite State Machine President University Erwin Sitompul Digital Systems 9/15

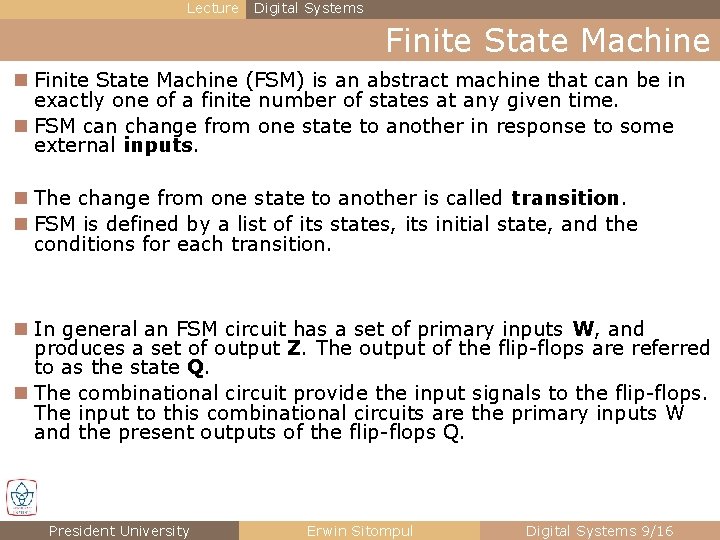

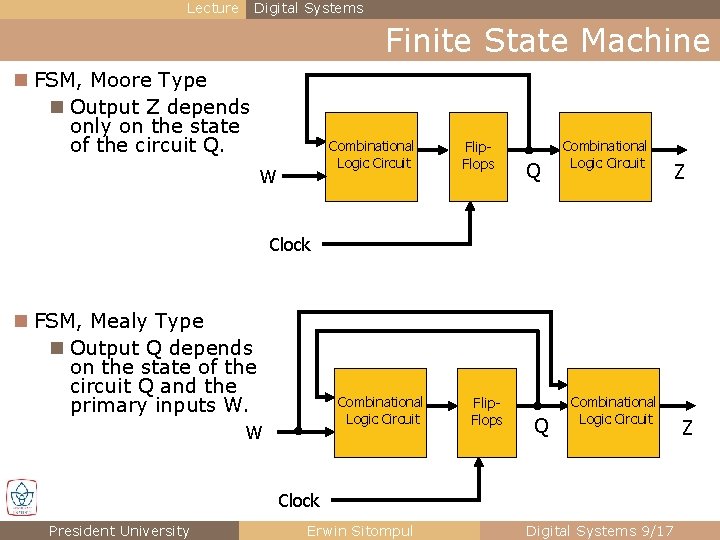

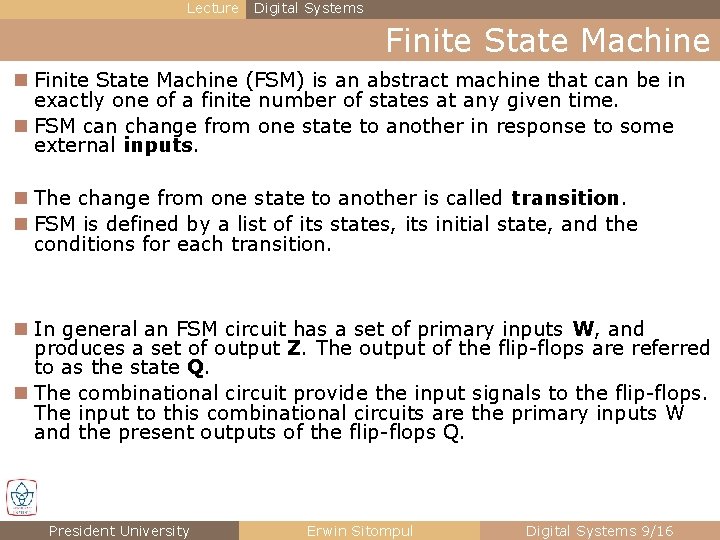

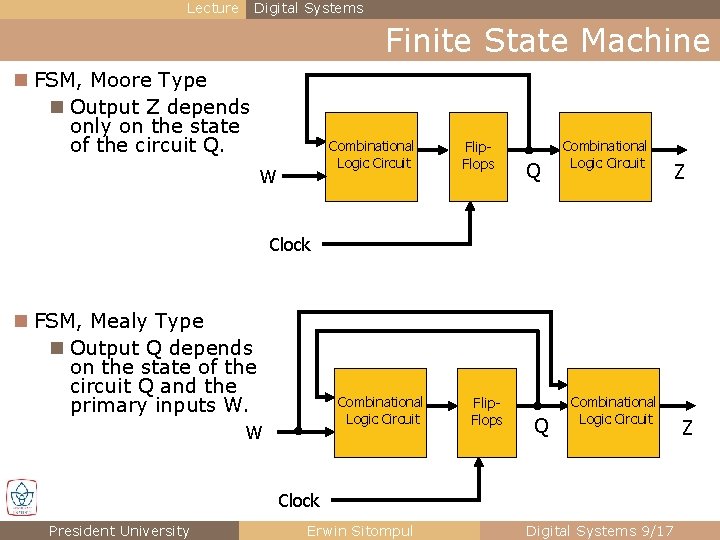

Lecture Digital Systems Finite State Machine n Finite State Machine (FSM) is an abstract machine that can be in exactly one of a finite number of states at any given time. n FSM can change from one state to another in response to some external inputs. n The change from one state to another is called transition. n FSM is defined by a list of its states, its initial state, and the conditions for each transition. n In general an FSM circuit has a set of primary inputs W, and produces a set of output Z. The output of the flip-flops are referred to as the state Q. n The combinational circuit provide the input signals to the flip-flops. The input to this combinational circuits are the primary inputs W and the present outputs of the flip-flops Q. President University Erwin Sitompul Digital Systems 9/16

Lecture Digital Systems Finite State Machine n FSM, Moore Type n Output Z depends only on the state of the circuit Q. Combinational Logic Circuit W Flip. Flops Q Combinational Logic Circuit Z Clock n FSM, Mealy Type n Output Q depends on the state of the circuit Q and the primary inputs W. Combinational Logic Circuit W Flip. Flops Q Combinational Logic Circuit Clock President University Erwin Sitompul Digital Systems 9/17 Z

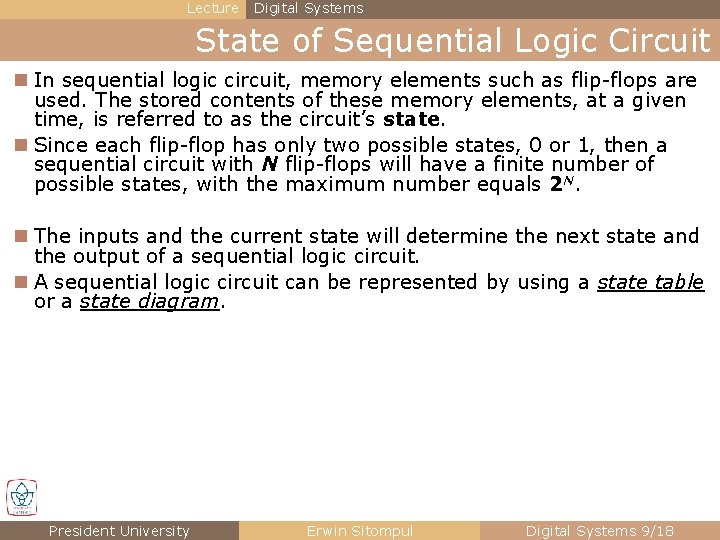

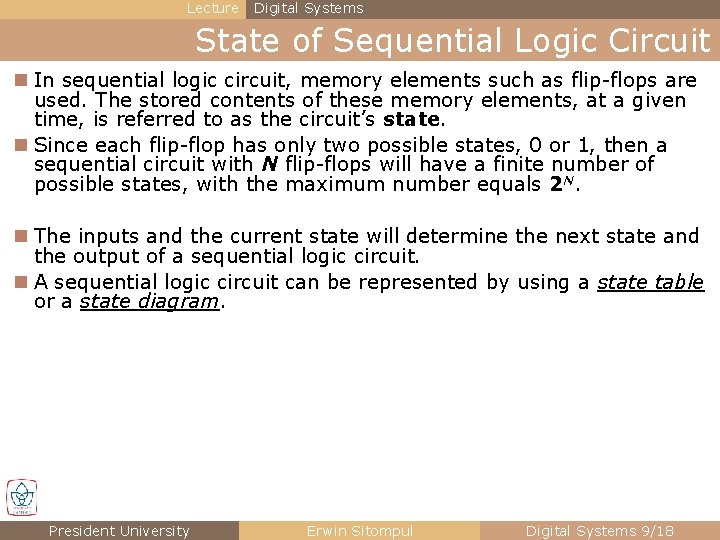

Lecture Digital Systems State of Sequential Logic Circuit n In sequential logic circuit, memory elements such as flip-flops are used. The stored contents of these memory elements, at a given time, is referred to as the circuit’s state. n Since each flip-flop has only two possible states, 0 or 1, then a sequential circuit with N flip-flops will have a finite number of possible states, with the maximum number equals 2 N. n The inputs and the current state will determine the next state and the output of a sequential logic circuit. n A sequential logic circuit can be represented by using a state table or a state diagram. President University Erwin Sitompul Digital Systems 9/18

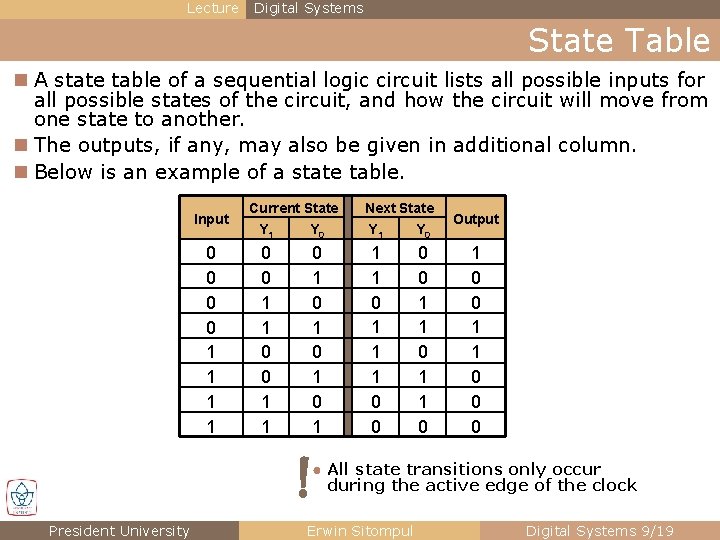

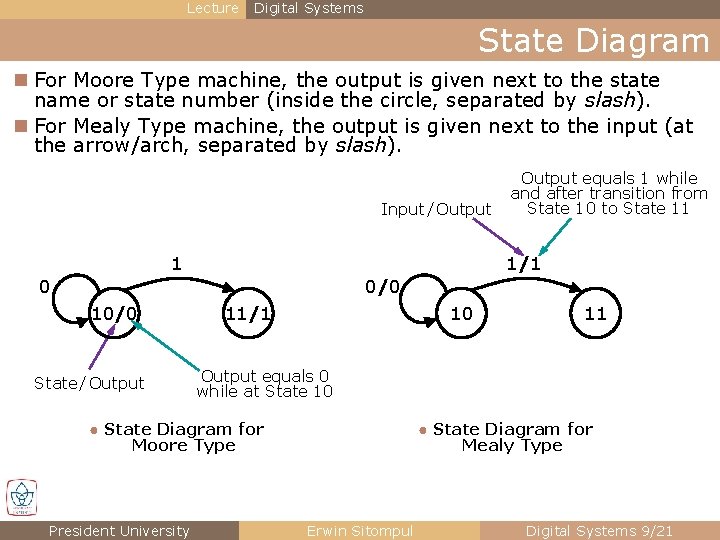

Lecture Digital Systems State Table n A state table of a sequential logic circuit lists all possible inputs for all possible states of the circuit, and how the circuit will move from one state to another. n The outputs, if any, may also be given in additional column. n Below is an example of a state table. Input 0 0 1 1 Current State Y 1 Y 0 0 0 1 1 0 1 0 1 1 1 0 0 1 1 0 ! President University Next State Output 1 0 0 1 1 0 0 0 ● All state transitions only occur during the active edge of the clock Erwin Sitompul Digital Systems 9/19

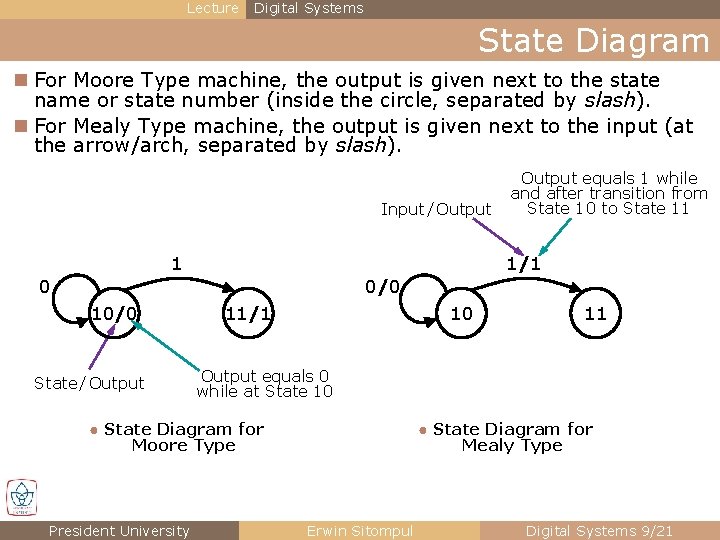

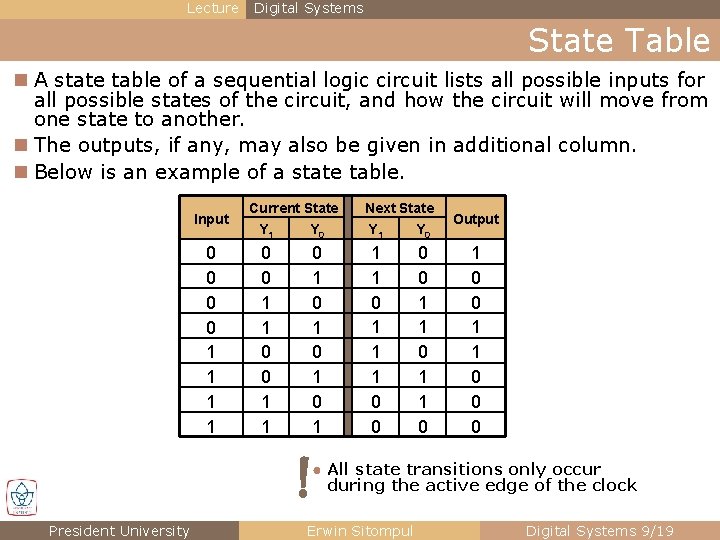

Lecture Digital Systems State Diagram n In a state diagram, a state is represented by a circle, and the transition between the states is represented by arrow/arc. n Every state is given name (S 0, S 1, . . . , S 23, etc. ) or number (00, 01, . . . , 101, etc. ) inside the circle. n Every transition is given the corresponding input at the arrow/arc. Possible inputs while at State 10 Transition to State 11 for input equals 1 1 0 10 11 Transition back to State 10 for input equals 0 State 11 ● A state diagram without output President University Erwin Sitompul Digital Systems 9/20

Lecture Digital Systems State Diagram n For Moore Type machine, the output is given next to the state name or state number (inside the circle, separated by slash). n For Mealy Type machine, the output is given next to the input (at the arrow/arch, separated by slash). Input / Output 1 Output equals 1 while and after transition from State 10 to State 11 1/1 0 0/0 10/0 State / Output 11/1 10 Output equals 0 while at State 10 ● State Diagram for Moore Type President University 11 ● State Diagram for Mealy Type Erwin Sitompul Digital Systems 9/21

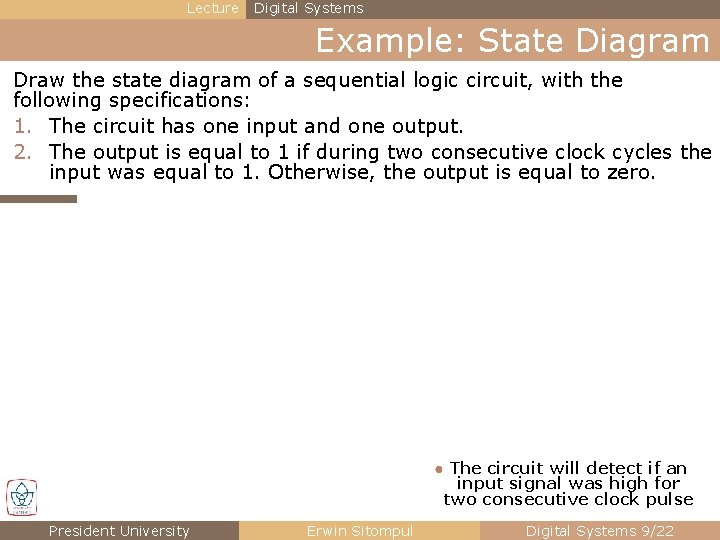

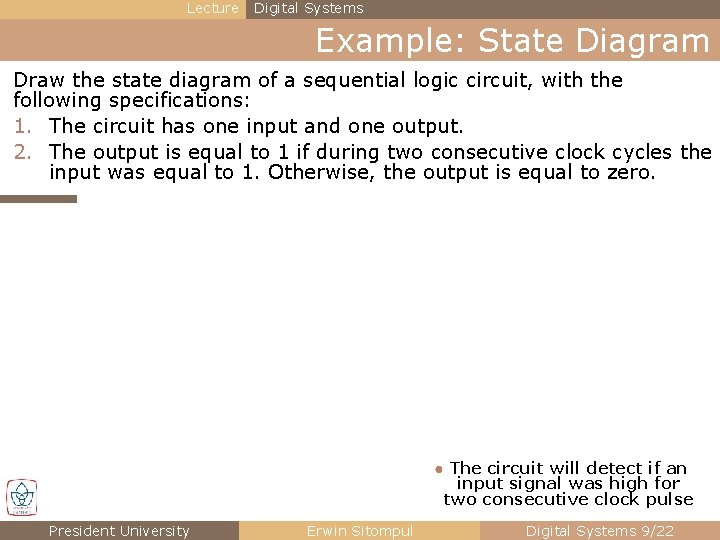

Lecture Digital Systems Example: State Diagram Draw the state diagram of a sequential logic circuit, with the following specifications: 1. The circuit has one input and one output. 2. The output is equal to 1 if during two consecutive clock cycles the input was equal to 1. Otherwise, the output is equal to zero. ● The circuit will detect if an input signal was high for two consecutive clock pulse President University Erwin Sitompul Digital Systems 9/22

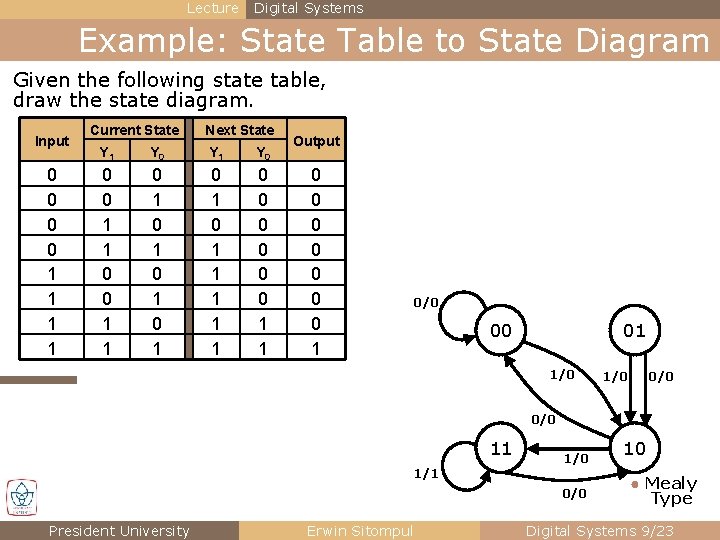

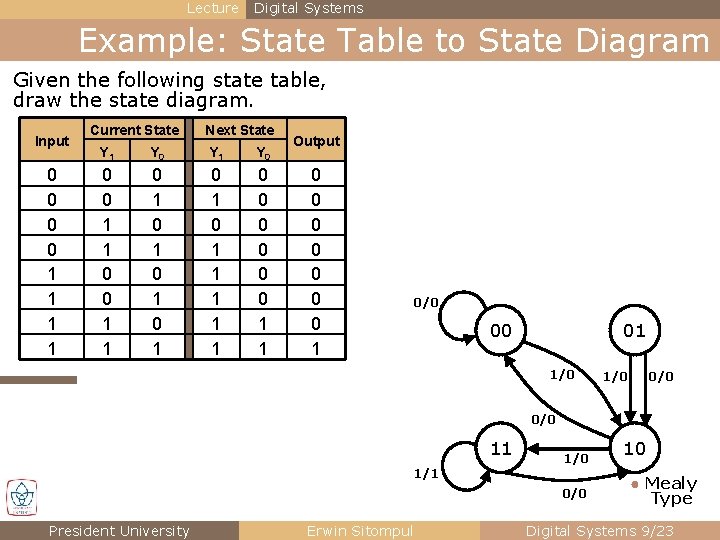

Lecture Digital Systems Example: State Table to State Diagram Given the following state table, draw the state diagram. Input 0 0 1 1 Current State Next State Y 1 Y 0 0 0 1 1 0 1 0 1 0 1 1 1 0 0 0 1 1 Output 0 0 0 0 1 0/0 00 01 1/0 0/0 11 1/0 1/1 0/0 President University Erwin Sitompul 10 ● Mealy Type Digital Systems 9/23

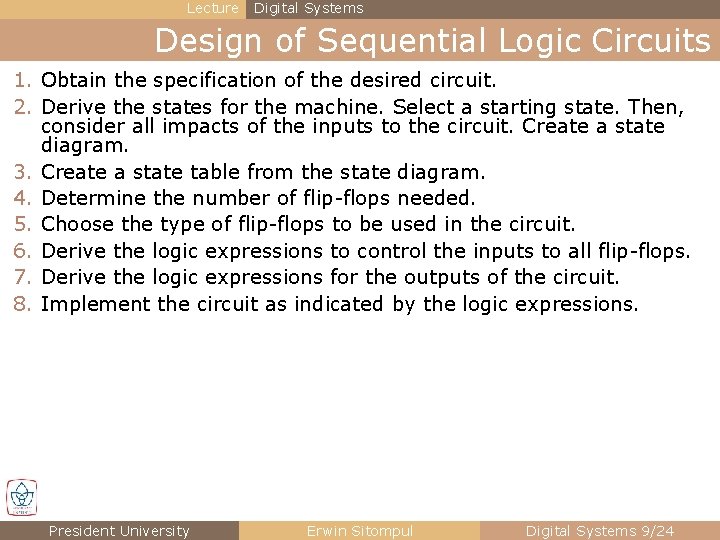

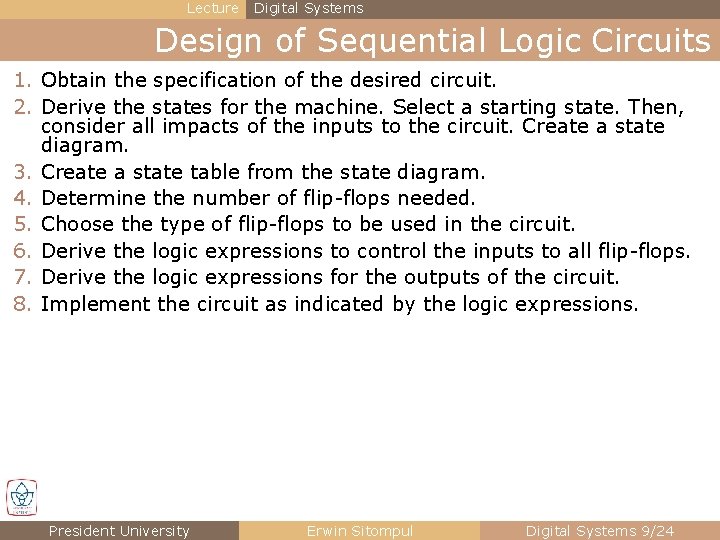

Lecture Digital Systems Design of Sequential Logic Circuits 1. Obtain the specification of the desired circuit. 2. Derive the states for the machine. Select a starting state. Then, consider all impacts of the inputs to the circuit. Create a state diagram. 3. Create a state table from the state diagram. 4. Determine the number of flip-flops needed. 5. Choose the type of flip-flops to be used in the circuit. 6. Derive the logic expressions to control the inputs to all flip-flops. 7. Derive the logic expressions for the outputs of the circuit. 8. Implement the circuit as indicated by the logic expressions. President University Erwin Sitompul Digital Systems 9/24

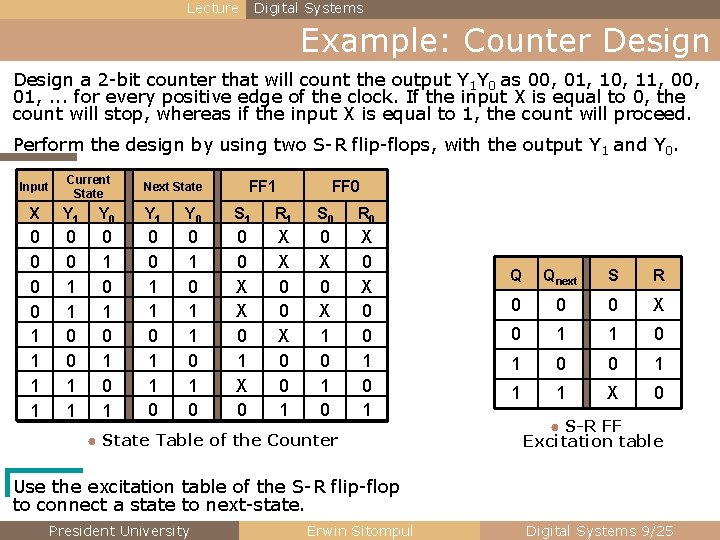

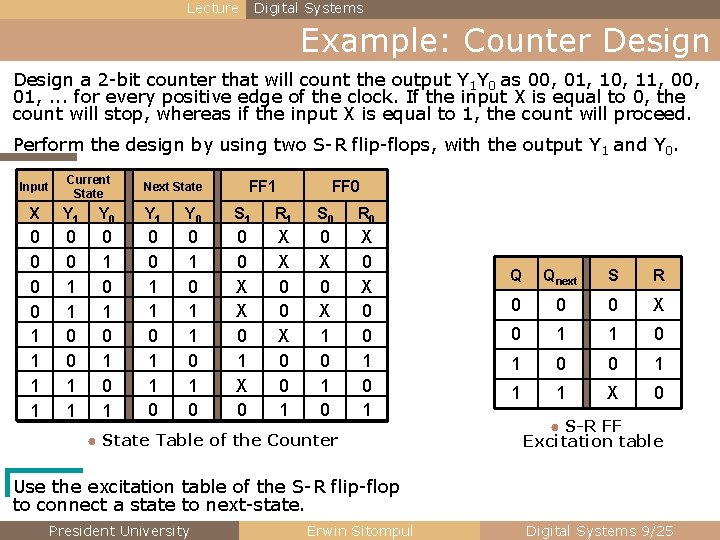

Lecture Digital Systems Example: Counter Design a 2 -bit counter that will count the output Y 1 Y 0 as 00, 01, 10, 11, 00, 01, . . . for every positive edge of the clock. If the input X is equal to 0, the count will stop, whereas if the input X is equal to 1, the count will proceed. Perform the design by using two S-R flip-flops, with the output Y 1 and Y 0. Input Current State FF 1 Next State FF 0 X Y 1 Y 0 S 1 R 1 S 0 R 0 0 0 1 1 0 1 0 1 0 0 1 1 0 0 ? 0 X X 0 1 X 0 X ? X 0 0 1 0 X 1 0 ? X 0 0 1 ? ● State Table of the Counter Q Qnext S R 0 0 0 X 0 1 1 0 0 1 1 1 X 0 ● S-R FF Excitation table Use the excitation table of the S-R flip-flop to connect a state to next-state. President University Erwin Sitompul Digital Systems 9/25

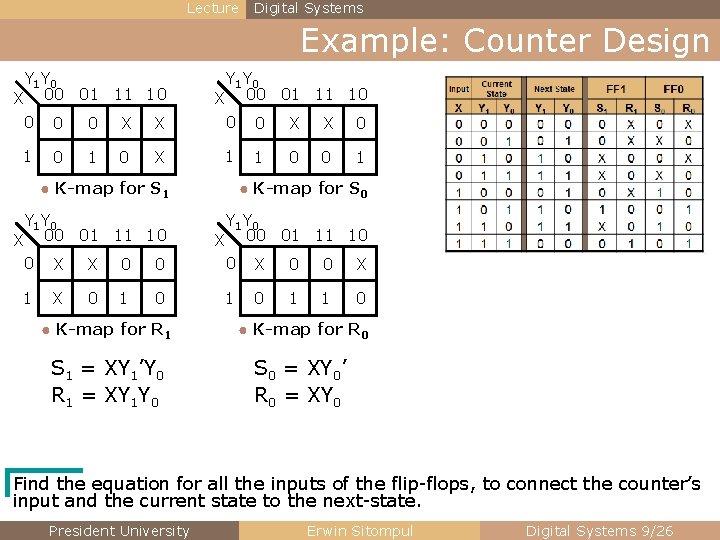

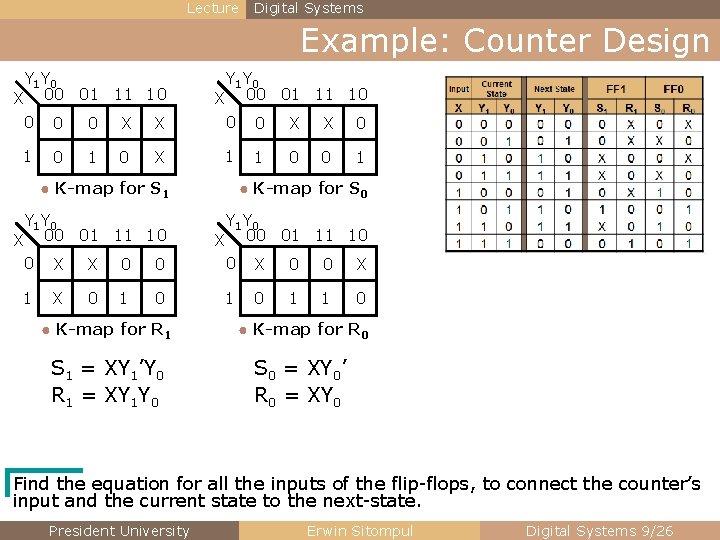

Lecture Digital Systems Example: Counter Design Y 1 Y 0 X 00 01 11 10 0 X X 1 0 X Y 1 Y 0 X 00 01 11 10 0 0 X X 0 1 1 0 0 1 ● K-map for S 0 Y 1 Y 0 X 00 01 11 10 0 X X 0 0 Y 1 Y 0 X 00 01 11 10 0 X 1 X 0 1 0 1 1 0 ● K-map for R 1 ● K-map for R 0 S 1 = XY 1’Y 0 R 1 = XY 1 Y 0 S 0 = XY 0’ R 0 = XY 0 Find the equation for all the inputs of the flip-flops, to connect the counter’s input and the current state to the next-state. President University Erwin Sitompul Digital Systems 9/26

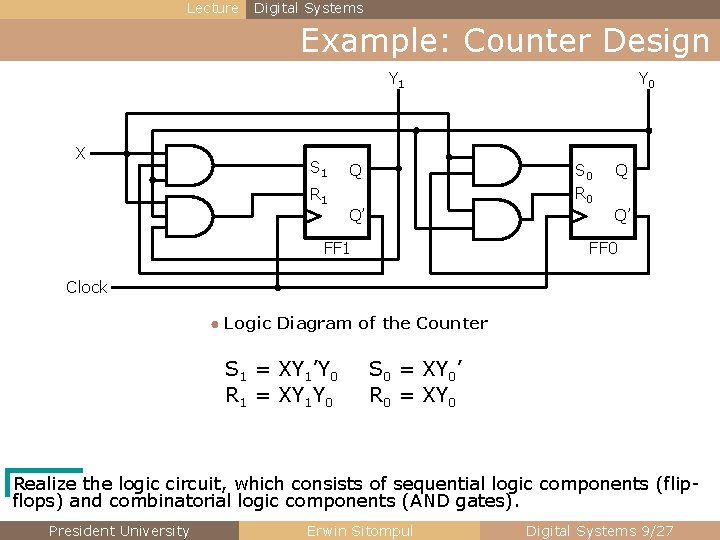

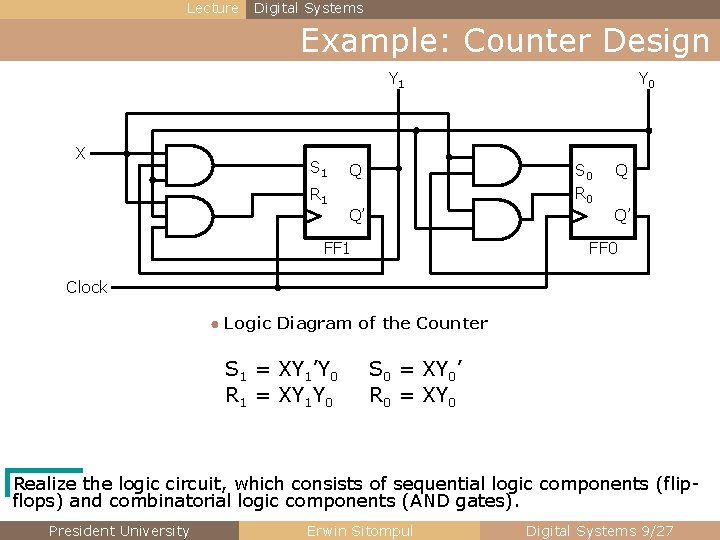

Lecture Digital Systems Example: Counter Design Y 1 X S 1 R 1 Y 0 S 0 R 0 Q Q’ FF 1 Q Q’ FF 0 Clock ● Logic Diagram of the Counter S 1 = XY 1’Y 0 R 1 = XY 1 Y 0 S 0 = XY 0’ R 0 = XY 0 Realize the logic circuit, which consists of sequential logic components (flipflops) and combinatorial logic components (AND gates). President University Erwin Sitompul Digital Systems 9/27

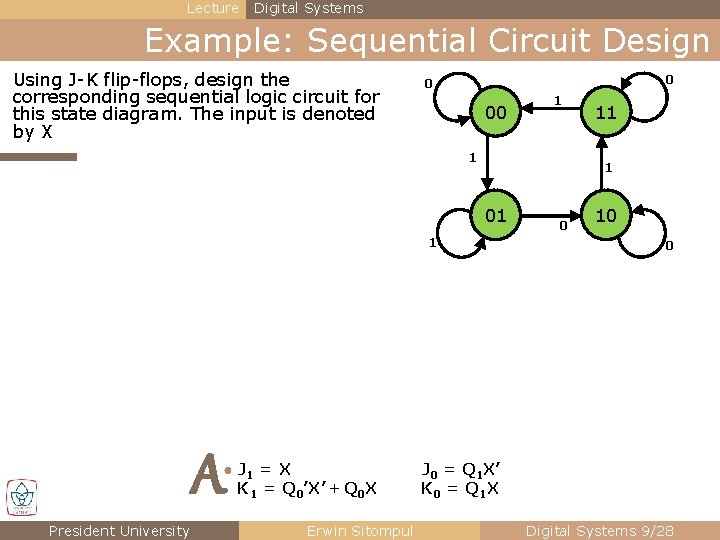

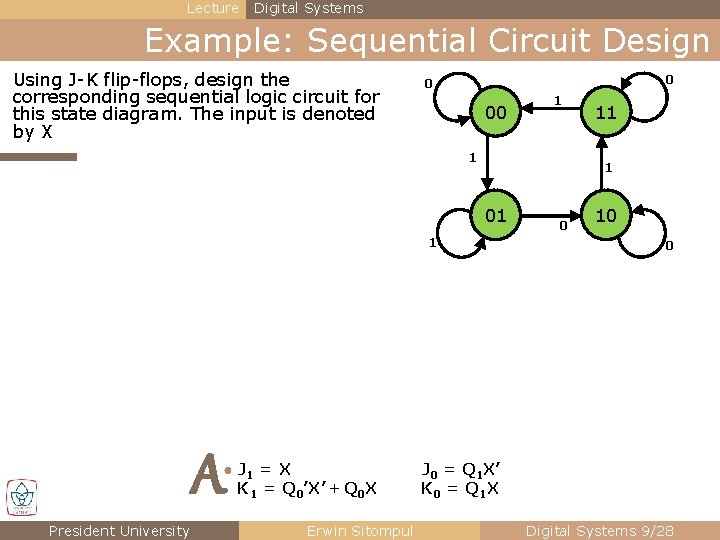

Lecture Digital Systems Example: Sequential Circuit Design Using J-K flip-flops, design the corresponding sequential logic circuit for this state diagram. The input is denoted by X 0 0 00 1 1 1 01 1 A ● J 1 = X K 1 = Q 0’X’ + Q 0 X President University Erwin Sitompul 11 0 10 0 J 0 = Q 1 X’ K 0 = Q 1 X Digital Systems 9/28

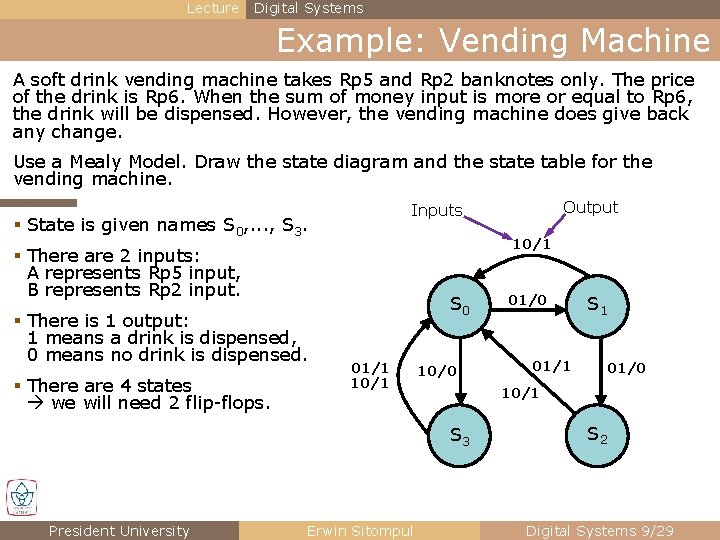

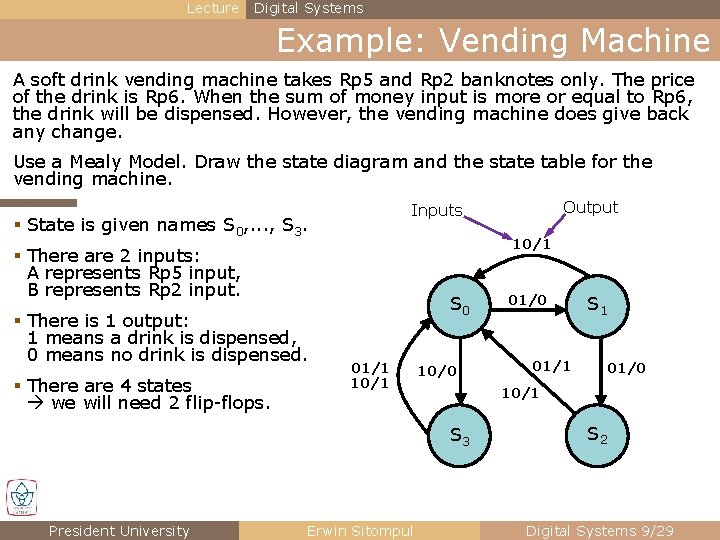

Lecture Digital Systems Example: Vending Machine A soft drink vending machine takes Rp 5 and Rp 2 banknotes only. The price of the drink is Rp 6. When the sum of money input is more or equal to Rp 6, the drink will be dispensed. However, the vending machine does give back any change. Use a Mealy Model. Draw the state diagram and the state table for the vending machine. § State is given names S 0, . . . , S 3. 10/1 § There are 2 inputs: A represents Rp 5 input, B represents Rp 2 input. § There is 1 output: 1 means a drink is dispensed, 0 means no drink is dispensed. § There are 4 states we will need 2 flip-flops. S 0 01/1 10/0 Erwin Sitompul 01/0 01/1 S 1 01/0 10/1 S 3 President University Output Inputs S 2 Digital Systems 9/29

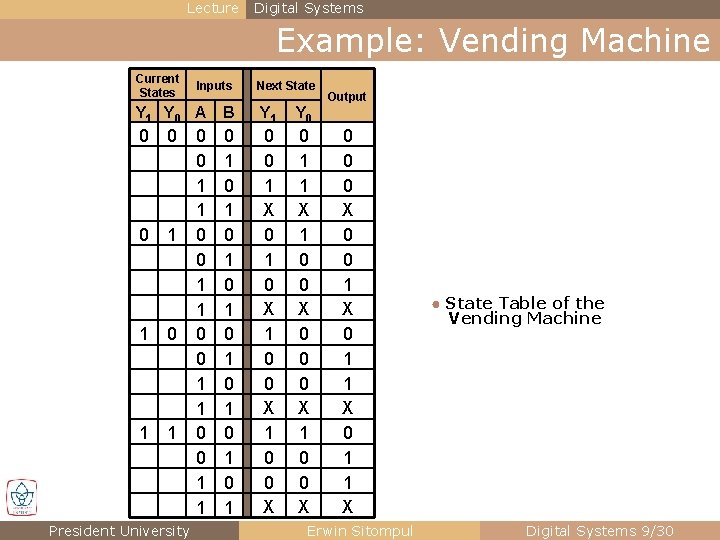

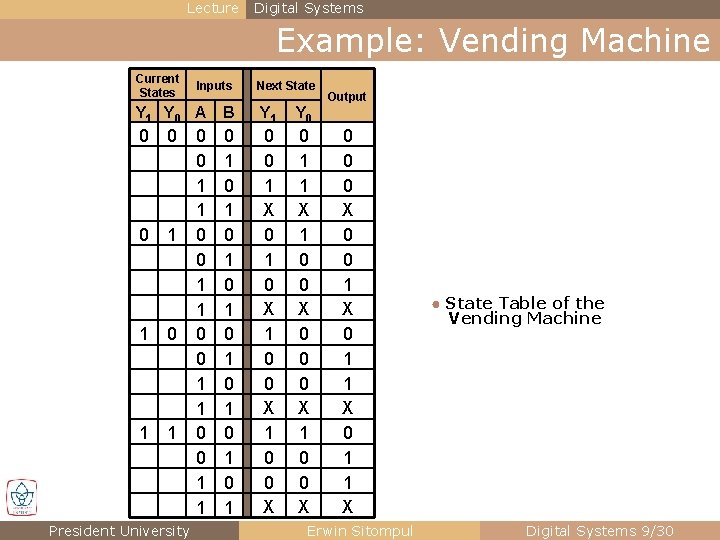

Lecture Digital Systems Example: Vending Machine Current States Inputs Next State Y 1 Y 0 A B Y 1 Y 0 0 1 0 1 0 1 0 0 1 X 0 1 0 X 1 0 0 X 0 1 1 X 1 0 0 X 0 0 0 X 1 0 1 1 President University 0 0 1 1 Output 0 0 0 X 0 0 1 X 0 1 1 X Erwin Sitompul ● State Table of the Vending Machine Digital Systems 9/30

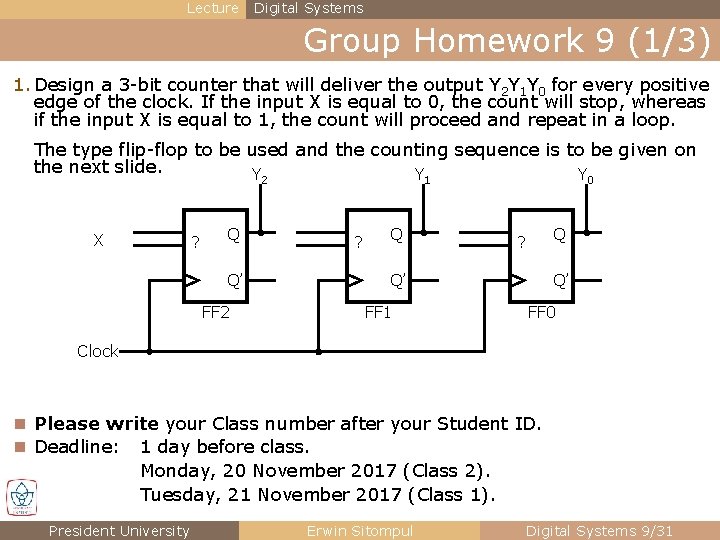

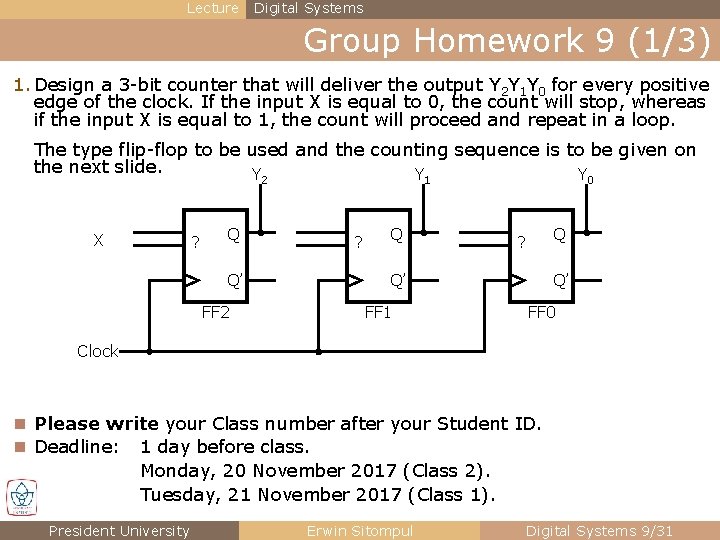

Lecture Digital Systems Group Homework 9 (1/3) 1. Design a 3 -bit counter that will deliver the output Y 2 Y 1 Y 0 for every positive edge of the clock. If the input X is equal to 0, the count will stop, whereas if the input X is equal to 1, the count will proceed and repeat in a loop. The type flip-flop to be used and the counting sequence is to be given on the next slide. Y 2 Y 1 Y 0 X ? Q Q’ FF 2 ? Q Q ? Q’ FF 1 Q’ FF 0 Clock n Please write your Class number after your Student ID. n Deadline: 1 day before class. Monday, 20 November 2017 (Class 2). Tuesday, 21 November 2017 (Class 1). President University Erwin Sitompul Digital Systems 9/31

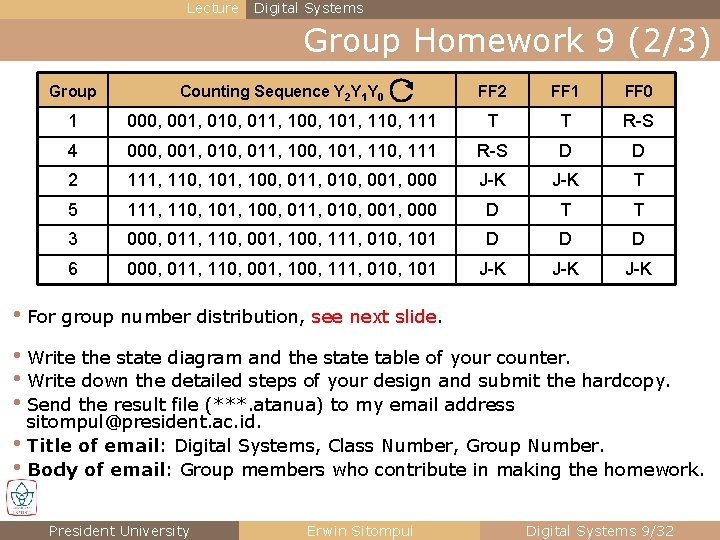

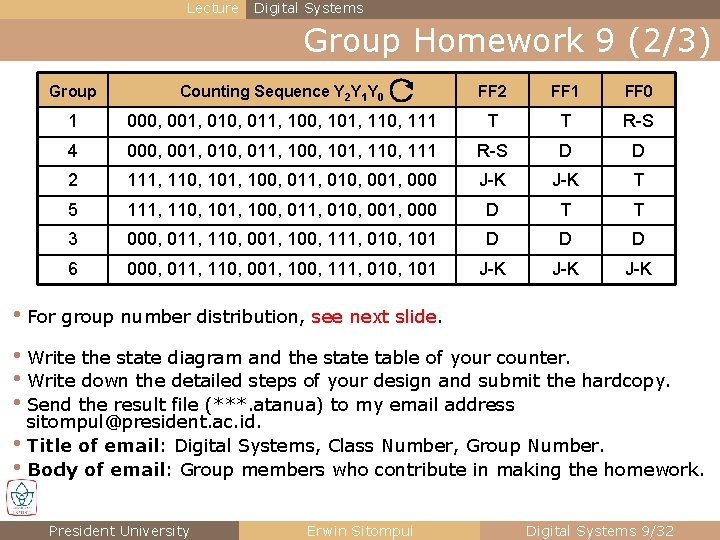

Lecture Digital Systems Group Homework 9 (2/3) Group Counting Sequence Y 2 Y 1 Y 0 FF 2 FF 1 FF 0 1 000, 001, 010, 011, 100, 101, 110, 111 T T R-S 4 000, 001, 010, 011, 100, 101, 110, 111 R-S D D 2 111, 110, 101, 100, 011, 010, 001, 000 J-K T 5 111, 110, 101, 100, 011, 010, 001, 000 D T T 3 000, 011, 110, 001, 100, 111, 010, 101 D D D 6 000, 011, 110, 001, 100, 111, 010, 101 J-K J-K • For group number distribution, see next slide. • Write the state diagram and the state table of your counter. • Write down the detailed steps of your design and submit the hardcopy. • Send the result file (***. atanua) to my email address sitompul@president. ac. id. • Title of email: Digital Systems, Class Number, Group Number. • Body of email: Group members who contribute in making the homework. President University Erwin Sitompul Digital Systems 9/32

Lecture Digital Systems Group Homework 9 (3/3) President University Erwin Sitompul Digital Systems 9/33