Digital Systems Lecture 12 Dr Ing Erwin Sitompul

- Slides: 23

Digital Systems Lecture 12 Dr. -Ing. Erwin Sitompul President University http: //zitompul. wordpress. com 2 0 1 7 President University Erwin Sitompul Digital Systems 12/1

Lecture Digital Systems Section 17 Decoders and Encoders President University Erwin Sitompul Digital Systems 12/2

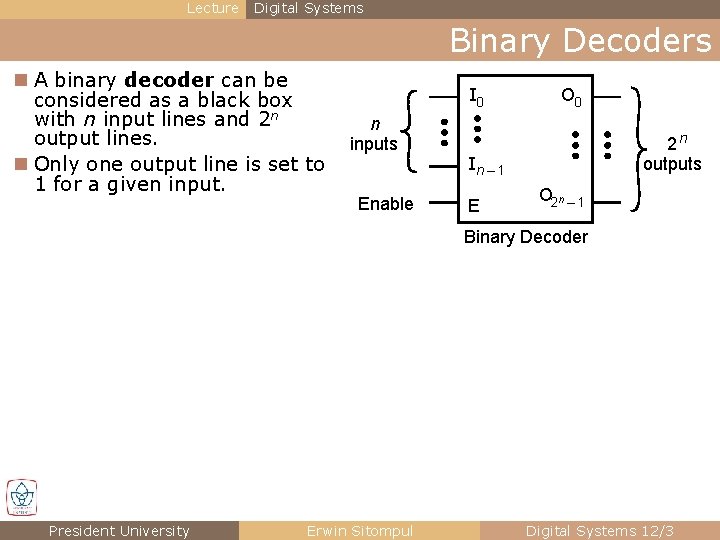

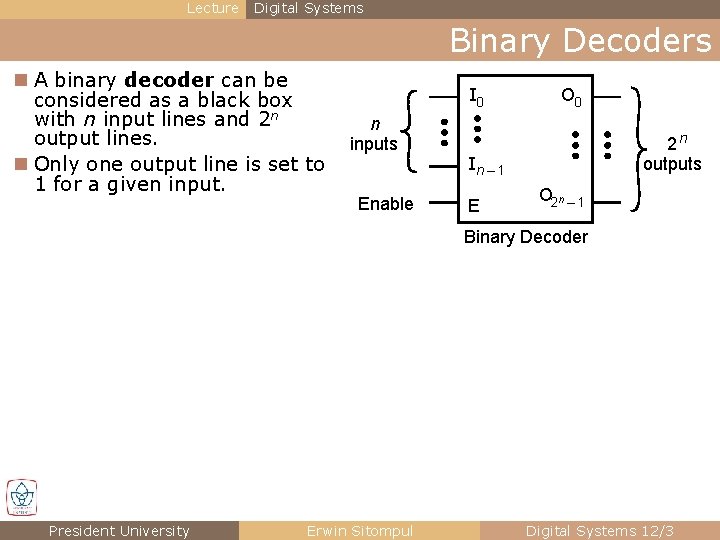

Lecture Digital Systems Binary Decoders n A binary decoder can be considered as a black box with n input lines and 2 n output lines. n Only one output line is set to 1 for a given input. I 0 n inputs Enable O 0 2 n outputs In – 1 E O 2 n – 1 Binary Decoder President University Erwin Sitompul Digital Systems 12/3

Lecture Digital Systems Binary Decoders n Binary decoders convert an n-bit input to a single output. It uses its n-bit input to determine which of the 2 n outputs will be uniquely activated. n Binary decoders can be developed using AND or OR Gates. n Later on, binary decoders can be implemented in logic circuits. n The outputs of a decoder are minterms. That is why decoders are sometimes called as minterm generators. n We can easily use a decoder to implement any sum of minterms expression. n Note: A minterm is a Boolean expression resulting in 1 only for the output of a single row (in a truth table) or a single cell (in a Karnaugh map), and 0 s for all other row or cells, respectively. President University Erwin Sitompul Digital Systems 12/4

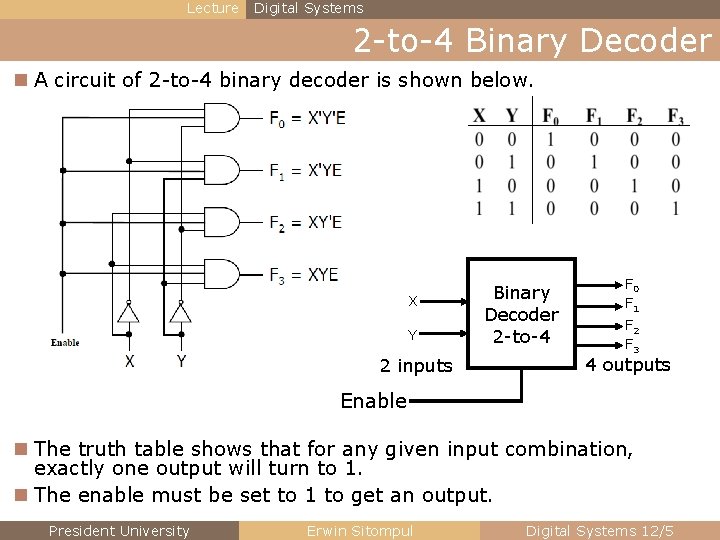

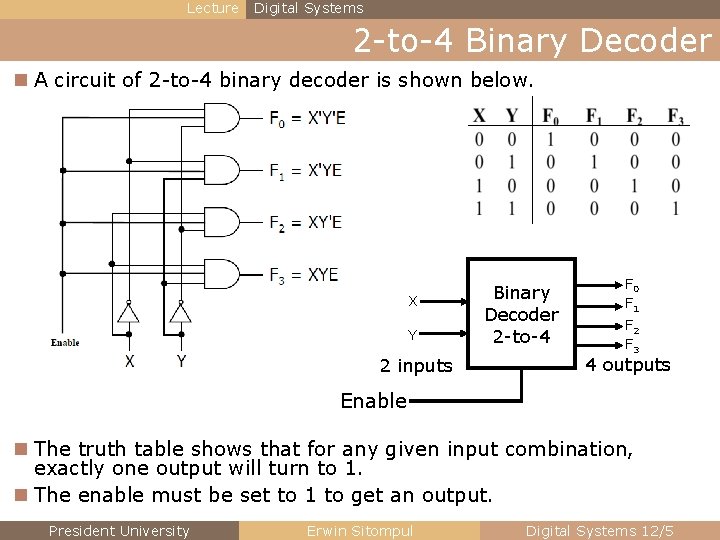

Lecture Digital Systems 2 -to-4 Binary Decoder n A circuit of 2 -to-4 binary decoder is shown below. X Y 2 inputs Binary Decoder 2 -to-4 F 0 F 1 F 2 F 3 4 outputs Enable n The truth table shows that for any given input combination, exactly one output will turn to 1. n The enable must be set to 1 to get an output. President University Erwin Sitompul Digital Systems 12/5

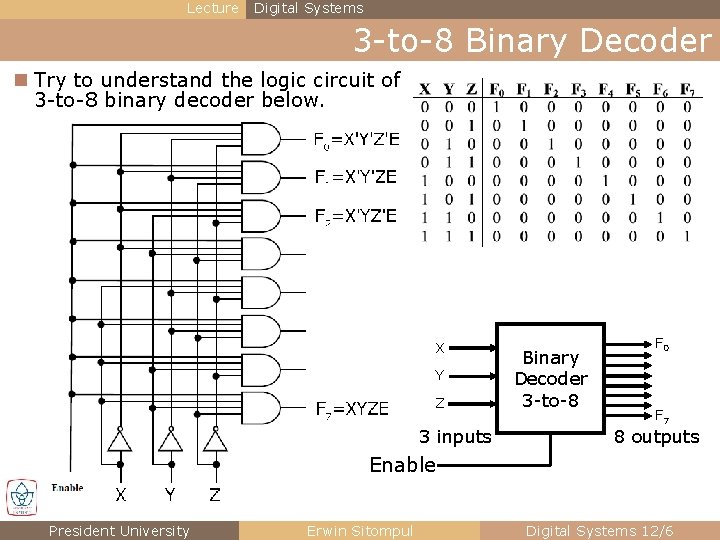

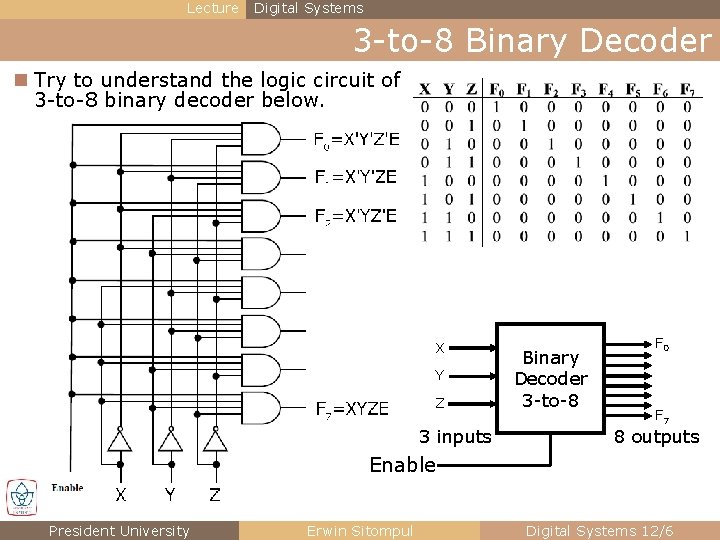

Lecture Digital Systems 3 -to-8 Binary Decoder n Try to understand the logic circuit of 3 -to-8 binary decoder below. X Y Z 3 inputs Binary Decoder 3 -to-8 F 0 F 7 8 outputs Enable President University Erwin Sitompul Digital Systems 12/6

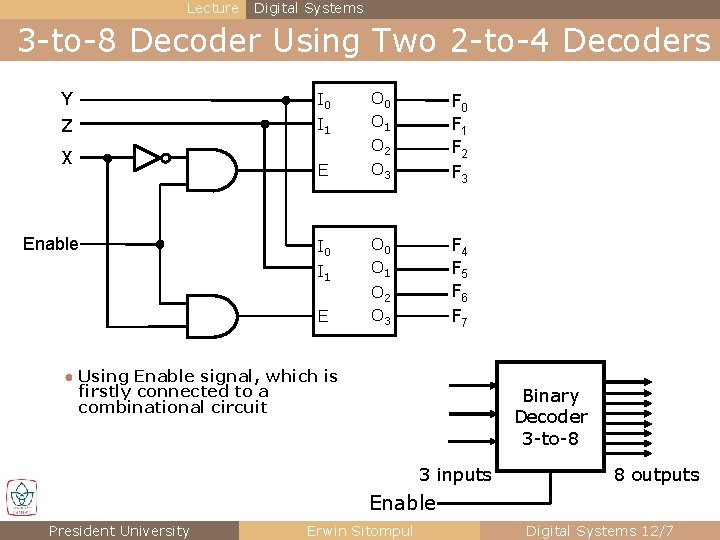

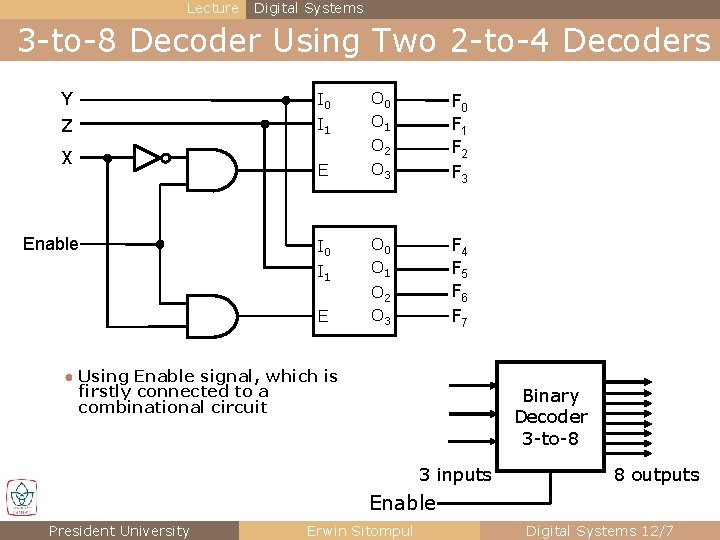

Lecture Digital Systems 3 -to-8 Decoder Using Two 2 -to-4 Decoders Y I 0 Z I 1 X Enable E I 0 I 1 E O 0 O 1 F 0 F 1 F 2 F 3 O 2 O 3 F 4 F 5 F 6 F 7 O 0 O 1 O 2 O 3 ● Using Enable signal, which is firstly connected to a combinational circuit Binary Decoder 3 -to-8 3 inputs 8 outputs Enable President University Erwin Sitompul Digital Systems 12/7

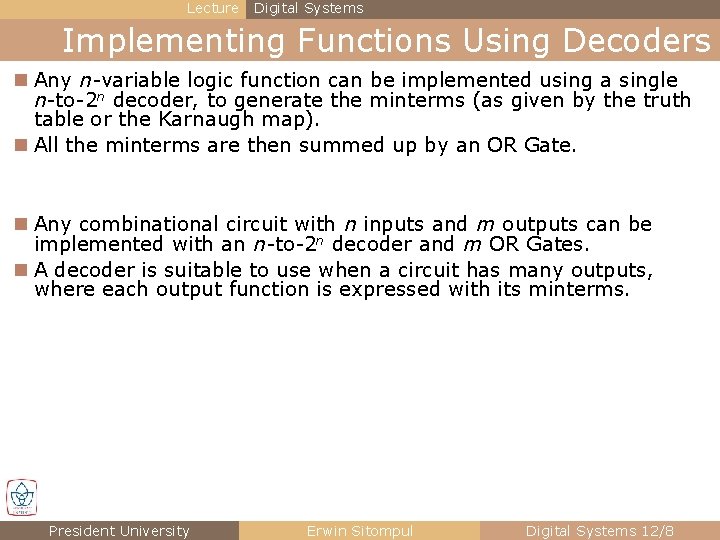

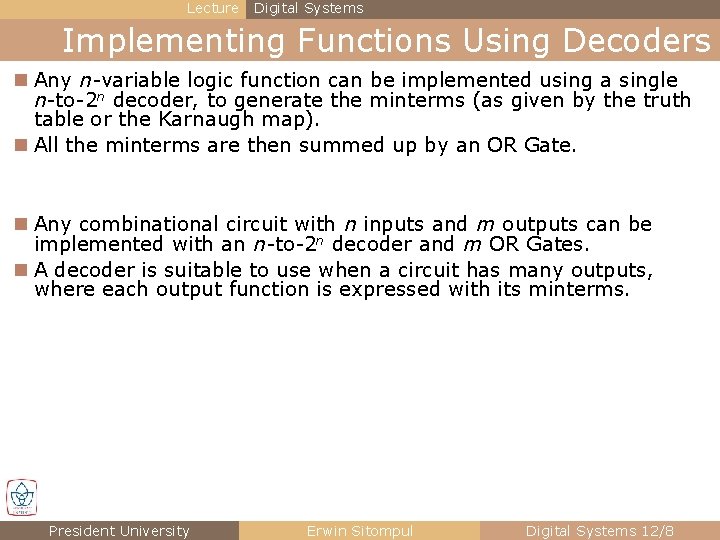

Lecture Digital Systems Implementing Functions Using Decoders n Any n-variable logic function can be implemented using a single n-to-2 n decoder, to generate the minterms (as given by the truth table or the Karnaugh map). n All the minterms are then summed up by an OR Gate. n Any combinational circuit with n inputs and m outputs can be implemented with an n-to-2 n decoder and m OR Gates. n A decoder is suitable to use when a circuit has many outputs, where each output function is expressed with its minterms. President University Erwin Sitompul Digital Systems 12/8

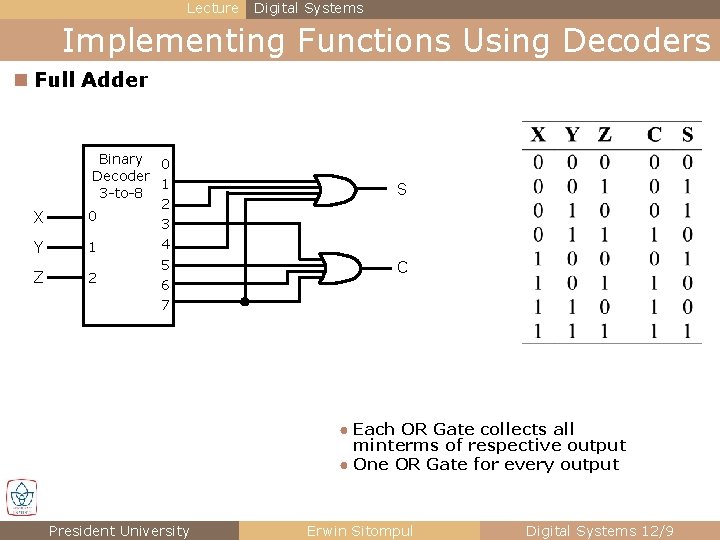

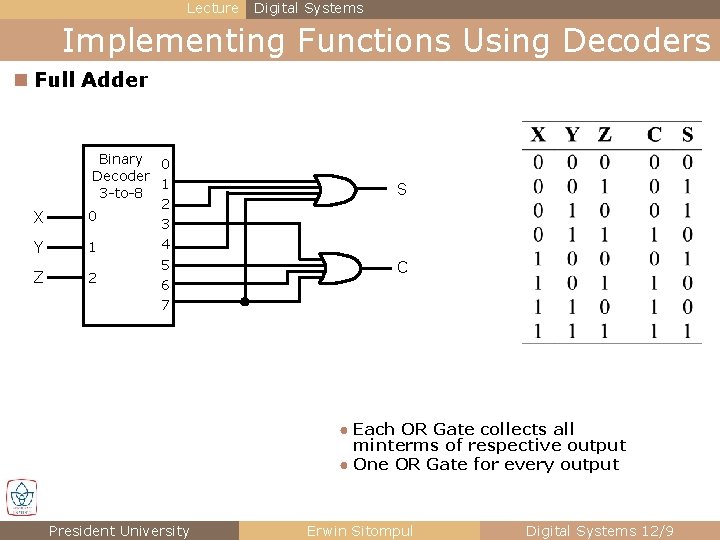

Lecture Digital Systems Implementing Functions Using Decoders n Full Adder X Y Z Binary 0 Decoder 1 3 -to-8 2 0 3 4 1 5 2 6 7 S C ● Each OR Gate collects all minterms of respective output ● One OR Gate for every output President University Erwin Sitompul Digital Systems 12/9

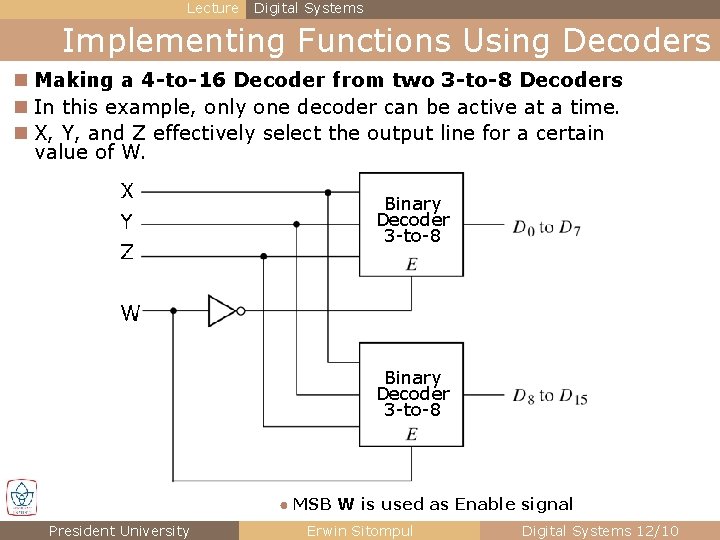

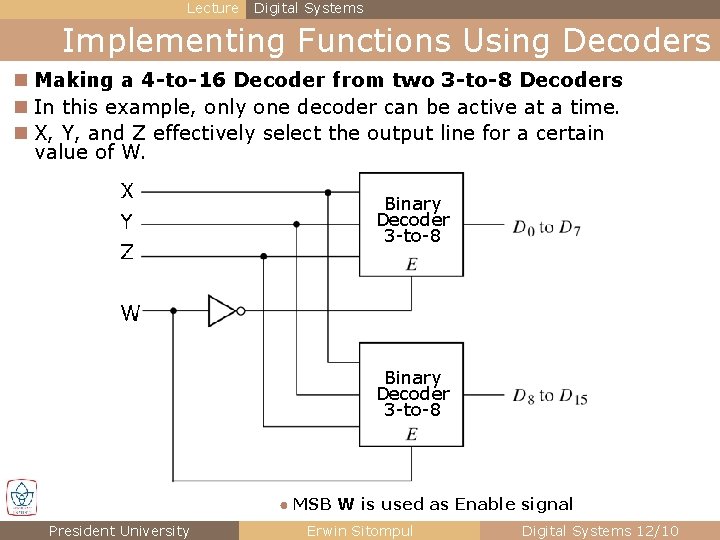

Lecture Digital Systems Implementing Functions Using Decoders n Making a 4 -to-16 Decoder from two 3 -to-8 Decoders n In this example, only one decoder can be active at a time. n X, Y, and Z effectively select the output line for a certain value of W. Binary Decoder 3 -to-8 ● MSB W is used as Enable signal President University Erwin Sitompul Digital Systems 12/10

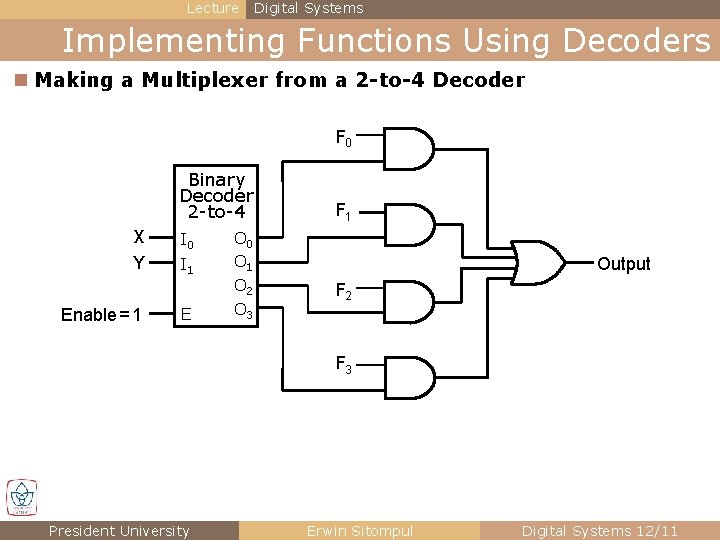

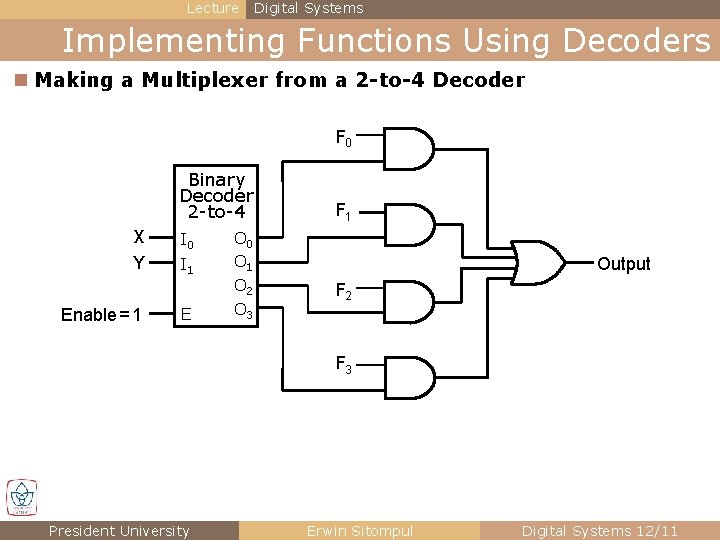

Lecture Digital Systems Implementing Functions Using Decoders n Making a Multiplexer from a 2 -to-4 Decoder F 0 Binary Decoder 2 -to-4 X Y Enable = 1 I 0 I 1 E F 1 O 0 O 1 O 2 O 3 Output F 2 F 3 President University Erwin Sitompul Digital Systems 12/11

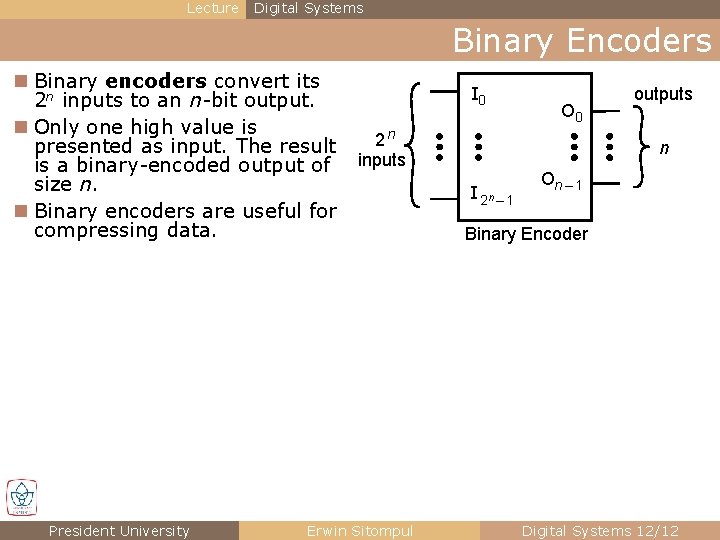

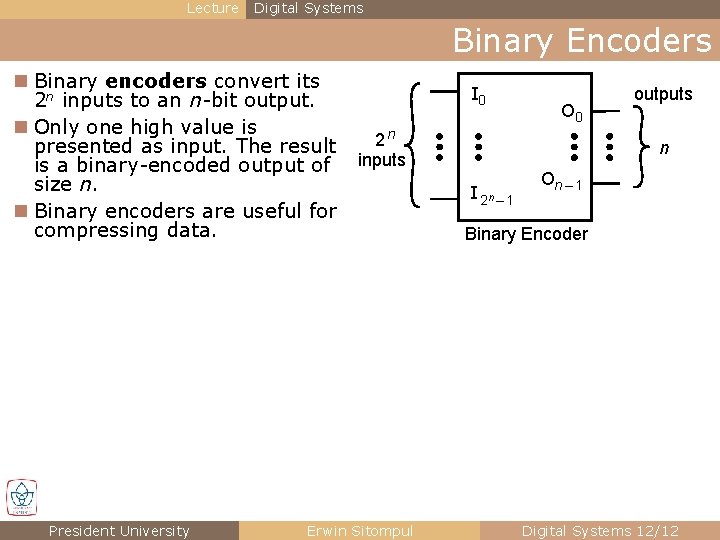

Lecture Digital Systems Binary Encoders n Binary encoders convert its 2 n inputs to an n-bit output. n Only one high value is presented as input. The result is a binary-encoded output of size n. n Binary encoders are useful for compressing data. President University I 0 2 n inputs Erwin Sitompul O 0 outputs n I 2 n – 1 On – 1 Binary Encoder Digital Systems 12/12

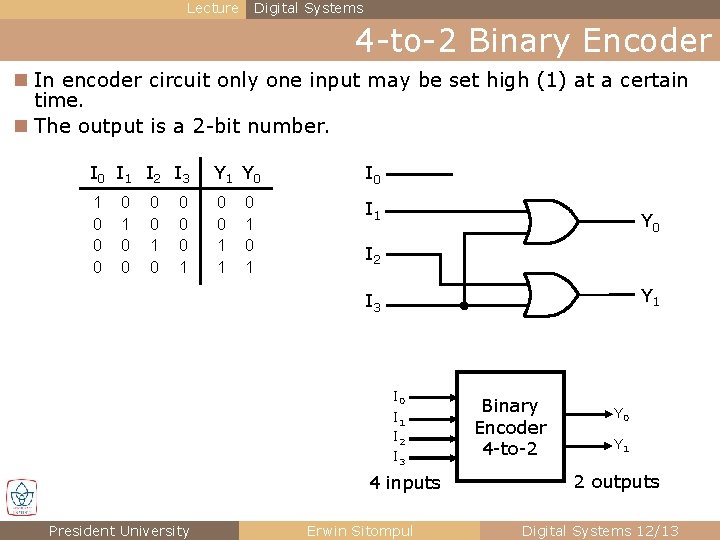

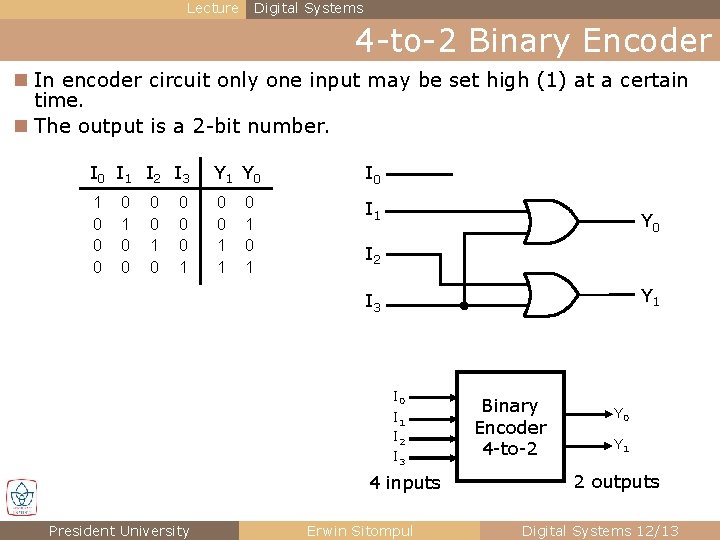

Lecture Digital Systems 4 -to-2 Binary Encoder n In encoder circuit only one input may be set high (1) at a certain time. n The output is a 2 -bit number. I 0 I 1 I 2 I 3 Y 1 Y 0 I 0 1 0 0 0 1 1 I 1 0 0 0 0 1 0 1 0 1 Y 0 I 2 Y 1 I 3 I 0 I 1 I 2 I 3 4 inputs President University Erwin Sitompul Binary Encoder 4 -to-2 Y 0 Y 1 2 outputs Digital Systems 12/13

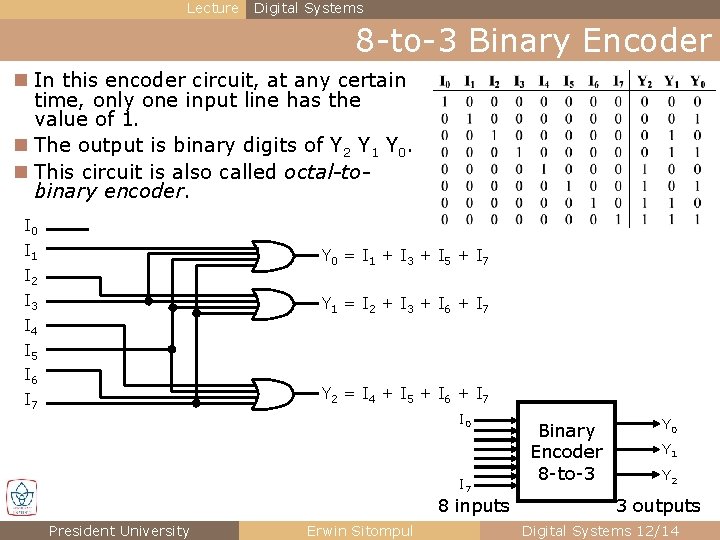

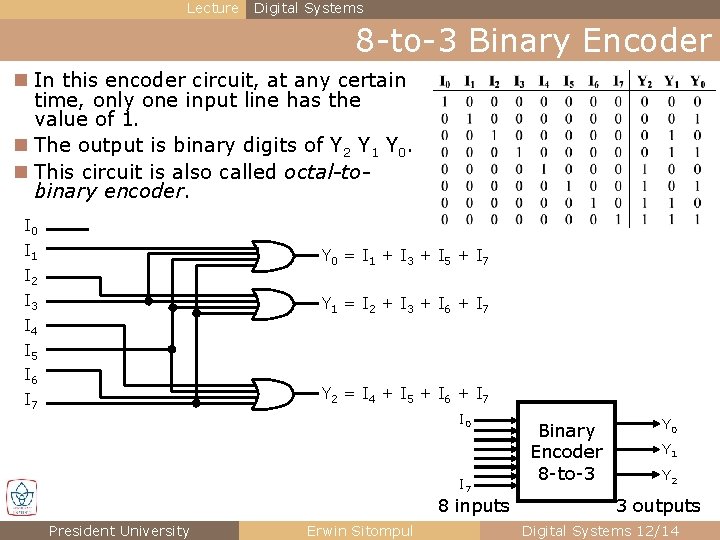

Lecture Digital Systems 8 -to-3 Binary Encoder n In this encoder circuit, at any certain time, only one input line has the value of 1. n The output is binary digits of Y 2 Y 1 Y 0. n This circuit is also called octal-tobinary encoder. I 0 I 1 Y 0 = I 1 + I 3 + I 5 + I 7 I 2 I 3 Y 1 = I 2 + I 3 + I 6 + I 7 I 4 I 5 I 6 Y 2 = I 4 + I 5 + I 6 + I 7 I 0 I 7 8 inputs President University Erwin Sitompul Binary Encoder 8 -to-3 Y 0 Y 1 Y 2 3 outputs Digital Systems 12/14

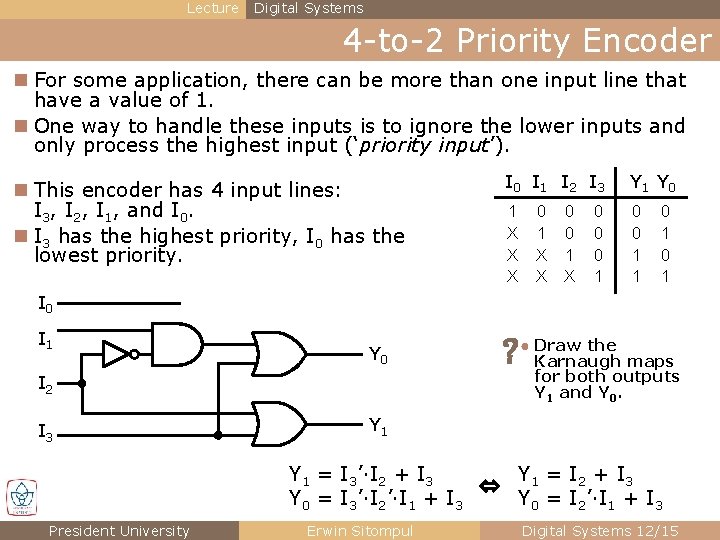

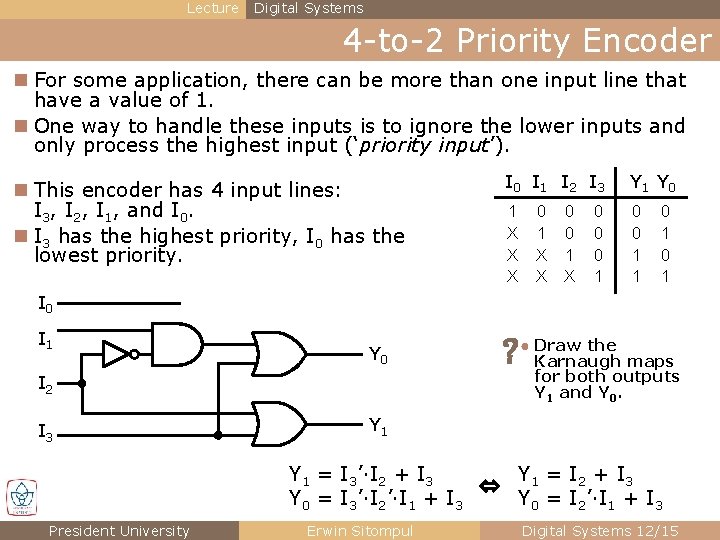

Lecture Digital Systems 4 -to-2 Priority Encoder n For some application, there can be more than one input line that have a value of 1. n One way to handle these inputs is to ignore the lower inputs and only process the highest input (‘priority input’). n This encoder has 4 input lines: I 3, I 2, I 1, and I 0. n I 3 has the highest priority, I 0 has the lowest priority. I 0 I 1 I 2 I 3 Y 1 Y 0 1 X X X 0 0 1 1 0 1 X X 0 0 1 X 0 0 0 1 0 1 I 0 I 1 Y 0 I 2 I 3 ● Draw the Karnaugh maps for both outputs Y 1 and Y 0. Y 1 = I 3’·I 2 + I 3 Y 0 = I 3’·I 2’·I 1 + I 3 President University ? Erwin Sitompul Y =I +I 3 ⇔ Y 1 = I 2’·I + I 3 0 2 1 Digital Systems 12/15

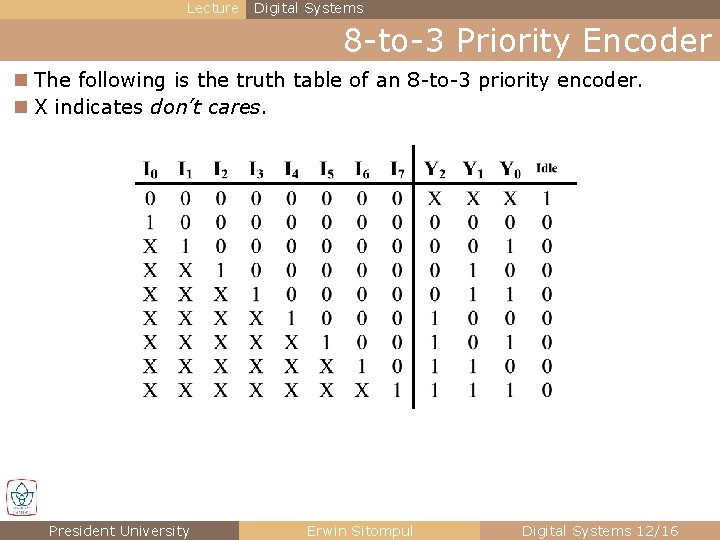

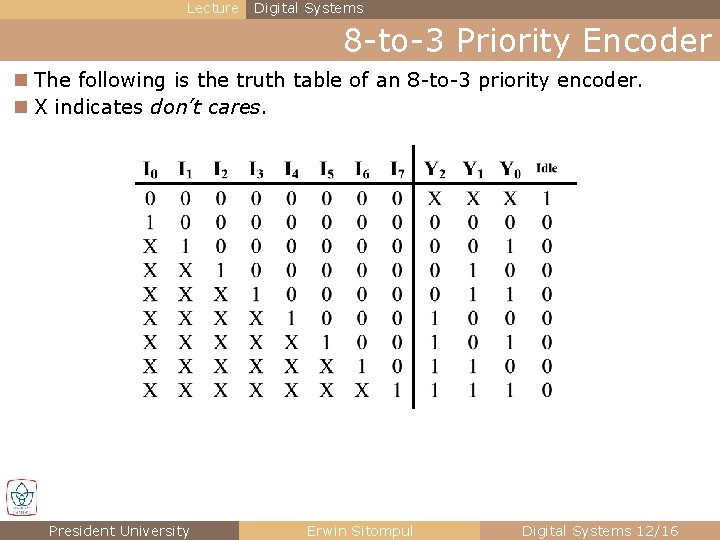

Lecture Digital Systems 8 -to-3 Priority Encoder n The following is the truth table of an 8 -to-3 priority encoder. n X indicates don’t cares. President University Erwin Sitompul Digital Systems 12/16

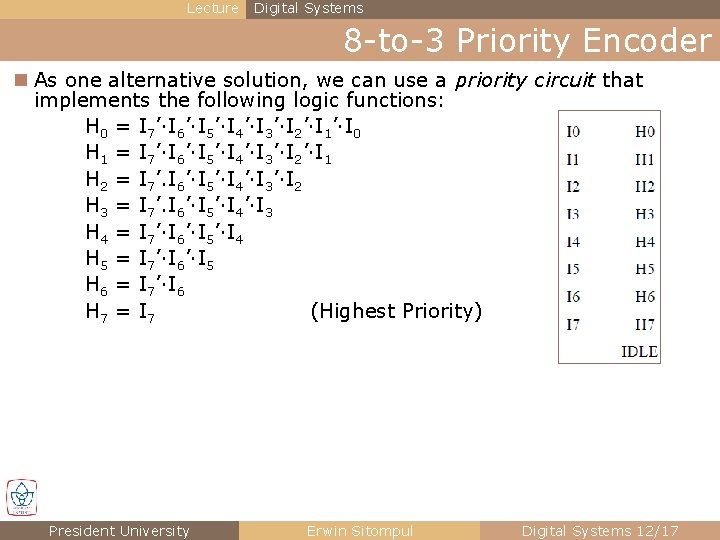

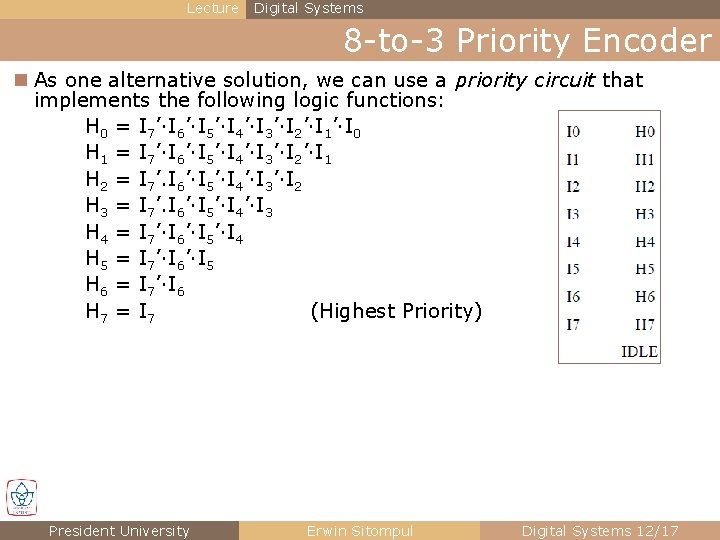

Lecture Digital Systems 8 -to-3 Priority Encoder n As one alternative solution, we can use a priority circuit that implements the following logic functions: H 0 = I 7’·I 6’·I 5’·I 4’·I 3’·I 2’·I 1’·I 0 H 1 = I 7’·I 6’·I 5’·I 4’·I 3’·I 2’·I 1 H 2 = I 7’. I 6’·I 5’·I 4’·I 3’·I 2 H 3 = I 7’. I 6’·I 5’·I 4’·I 3 H 4 = I 7’·I 6’·I 5’·I 4 H 5 = I 7’·I 6’·I 5 H 6 = I 7’·I 6 H 7 = I 7 (Highest Priority) President University Erwin Sitompul Digital Systems 12/17

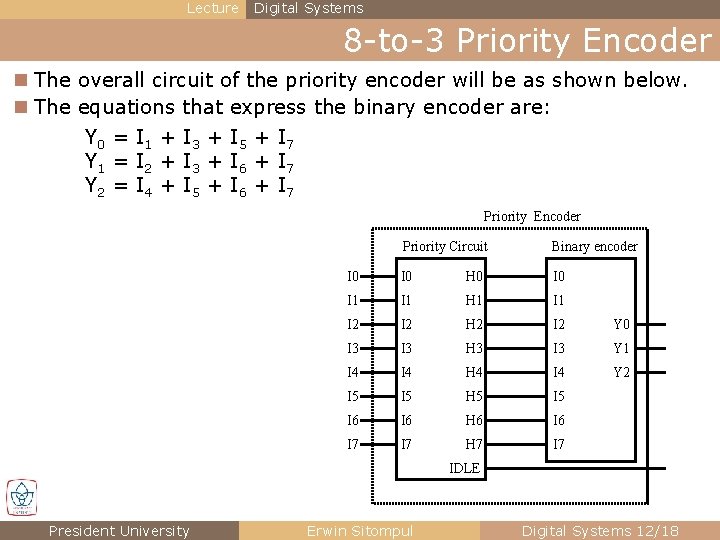

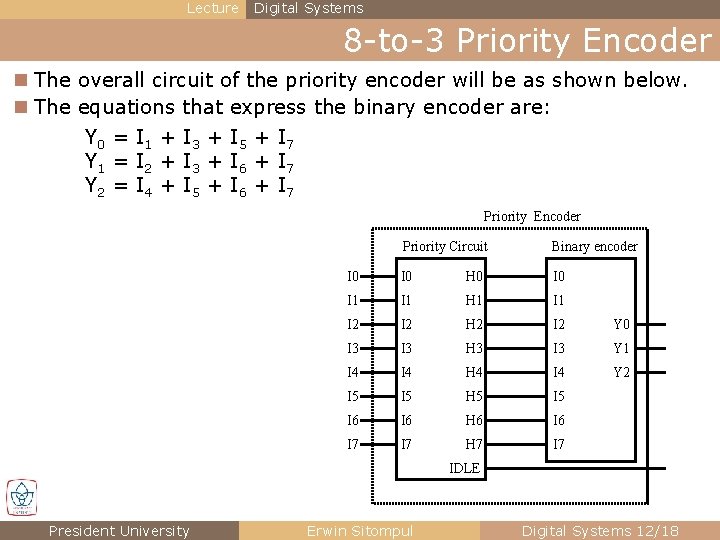

Lecture Digital Systems 8 -to-3 Priority Encoder n The overall circuit of the priority encoder will be as shown below. n The equations that express the binary encoder are: Y 0 = I 1 + I 3 + I 5 + I 7 Y 1 = I 2 + I 3 + I 6 + I 7 Y 2 = I 4 + I 5 + I 6 + I 7 Priority Encoder Priority Circuit Binary encoder I 0 H 0 I 1 I 1 H 1 I 2 I 2 H 2 I 2 Y 0 I 3 H 3 I 3 Y 1 I 4 H 4 I 4 Y 2 I 5 H 5 I 6 I 6 H 6 I 7 I 7 H 7 IDLE President University Erwin Sitompul Digital Systems 12/18

Lecture Digital Systems Design Exercise: 8 -to-3 Priority Encoder Design an 8 -to-3 priority encoder that will deliver only the lowest input and process it to becomes the output. President University Erwin Sitompul Digital Systems 12/19

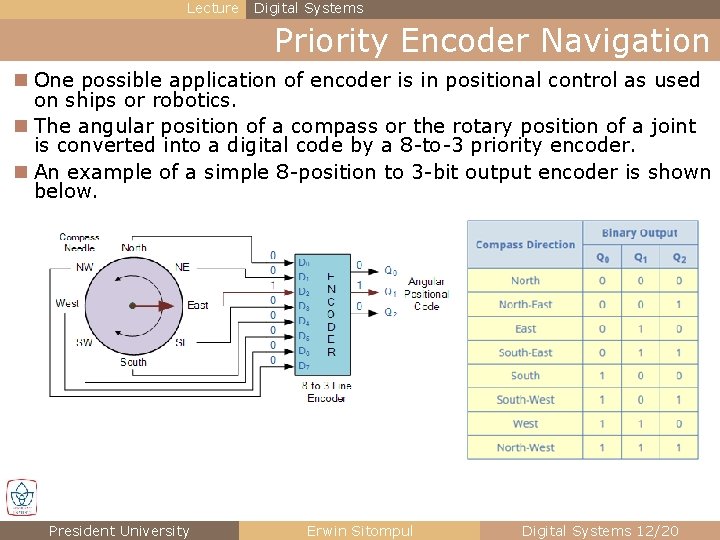

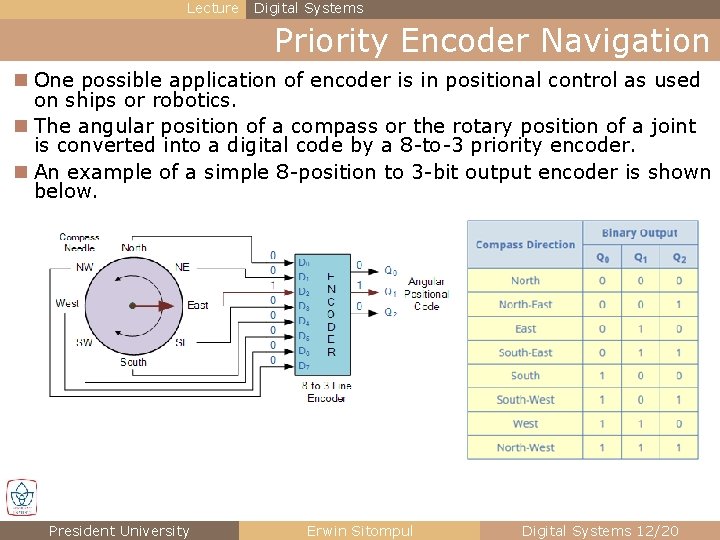

Lecture Digital Systems Priority Encoder Navigation n One possible application of encoder is in positional control as used on ships or robotics. n The angular position of a compass or the rotary position of a joint is converted into a digital code by a 8 -to-3 priority encoder. n An example of a simple 8 -position to 3 -bit output encoder is shown below. President University Erwin Sitompul Digital Systems 12/20

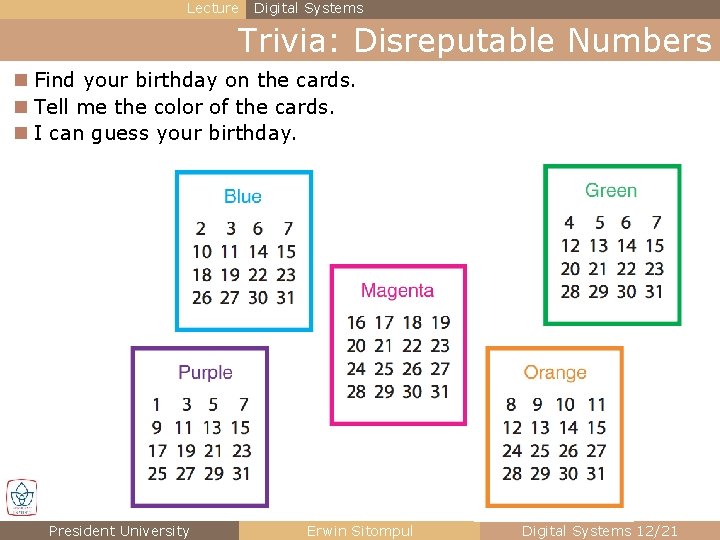

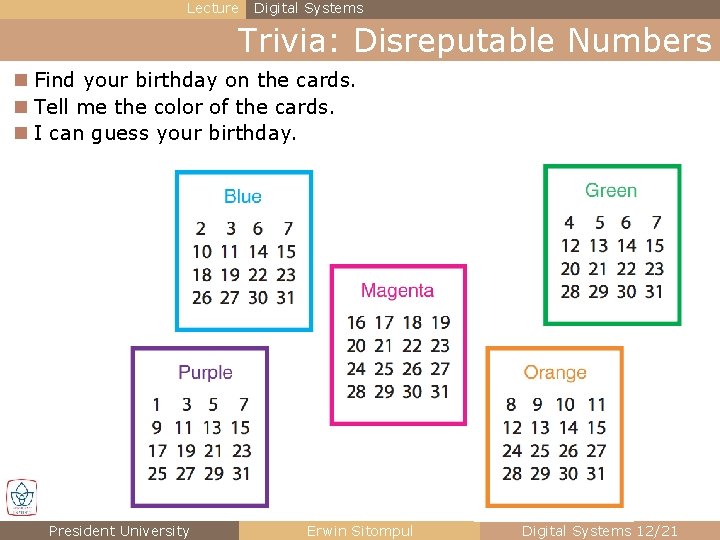

Lecture Digital Systems Trivia: Disreputable Numbers n Find your birthday on the cards. n Tell me the color of the cards. n I can guess your birthday. President University Erwin Sitompul Digital Systems 12/21

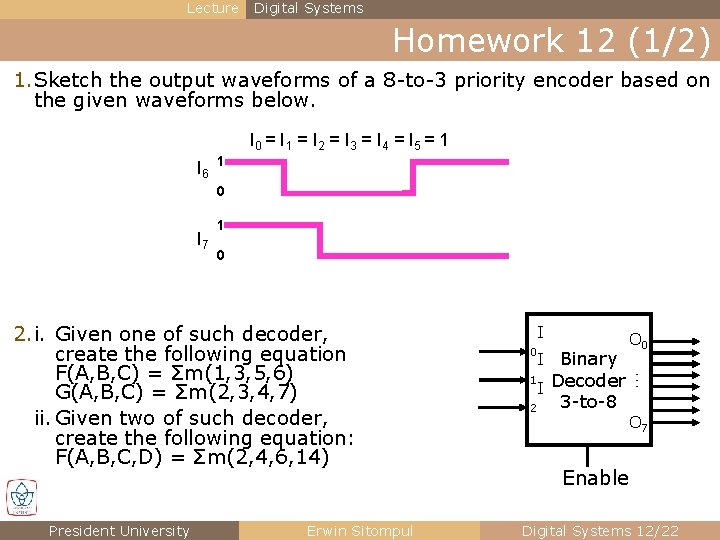

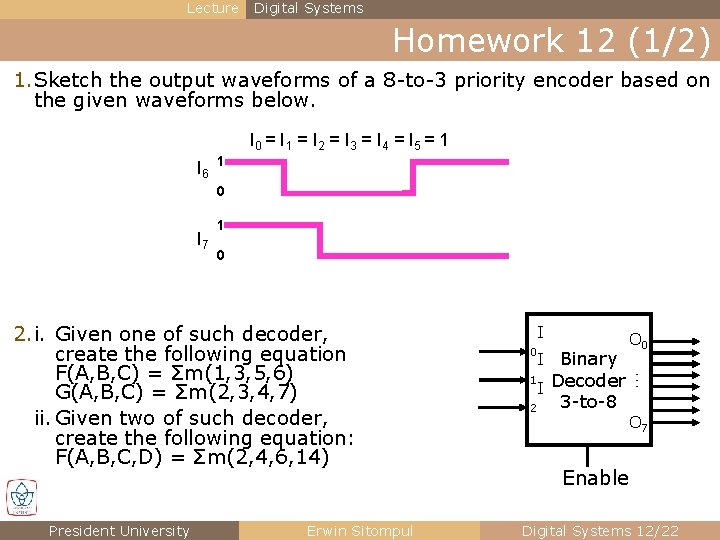

Lecture Digital Systems Homework 12 (1/2) 1. Sketch the output waveforms of a 8 -to-3 priority encoder based on the given waveforms below. I 0 = I 1 = I 2 = I 3 = I 4 = I 5 = 1 I 6 1 0 I 7 1 0 President University Erwin Sitompul I 0 Binary 1 Decoder I 3 -to-8 2 I O 0. . . 2. i. Given one of such decoder, create the following equation F(A, B, C) = Σm(1, 3, 5, 6) G(A, B, C) = Σm(2, 3, 4, 7) ii. Given two of such decoder, create the following equation: F(A, B, C, D) = Σm(2, 4, 6, 14) O 7 Enable Digital Systems 12/22

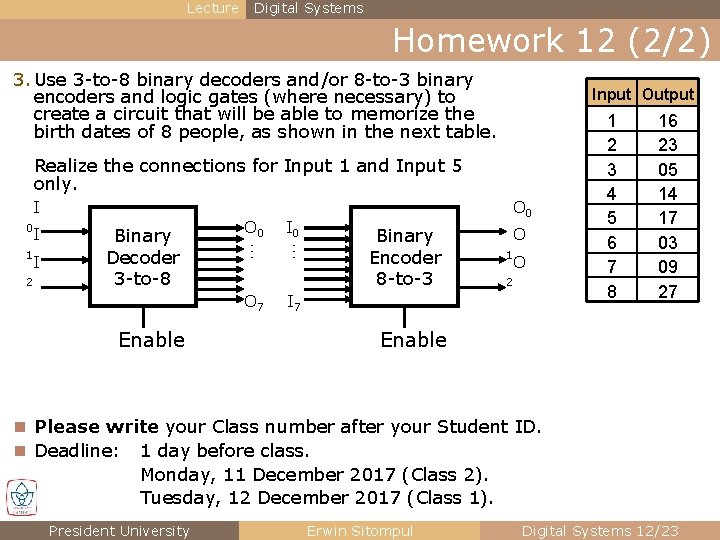

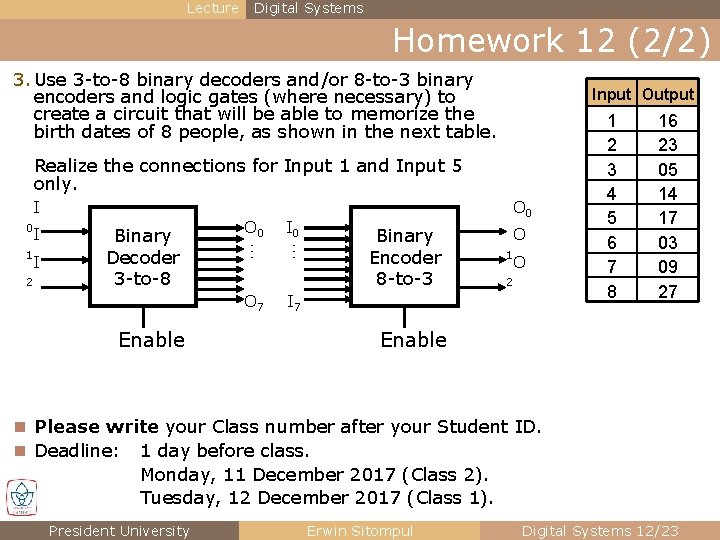

Lecture Digital Systems Homework 12 (2/2) 3. Use 3 -to-8 binary decoders and/or 8 -to-3 binary encoders and logic gates (where necessary) to create a circuit that will be able to memorize the birth dates of 8 people, as shown in the next table. Input Output Realize the connections for Input 1 and Input 5 only. I 1 I 2 Binary Decoder 3 -to-8 O 0 I 0. . . I . . . 0 O 7 Enable O 0 Binary Encoder 8 -to-3 O 1 O 2 I 7 1 2 3 4 5 6 7 8 16 23 05 14 17 03 09 27 Enable n Please write your Class number after your Student ID. n Deadline: 1 day before class. Monday, 11 December 2017 (Class 2). Tuesday, 12 December 2017 (Class 1). President University Erwin Sitompul Digital Systems 12/23