CSC Hardware Upgrade Status Mikhail Matveev Rice University

- Slides: 19

CSC Hardware Upgrade Status Mikhail Matveev Rice University Muon Phase II Upgrade Workshop CERN June 15, 2017

Outline ● DCFEBv 2 design modifications ● Comparator ASIC Update ● ALCT Upgrade ● Evaluation of new optical parts ● Low Voltage Distribution Board LVDB 5 Status ● HV Update ● Irradiation Tests in late 2016 – 2017 (TAMU, UCDavis, CHARM) June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 2

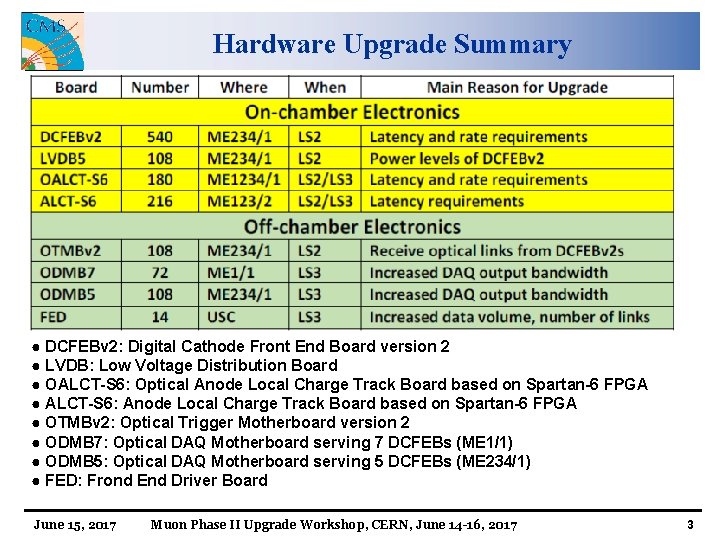

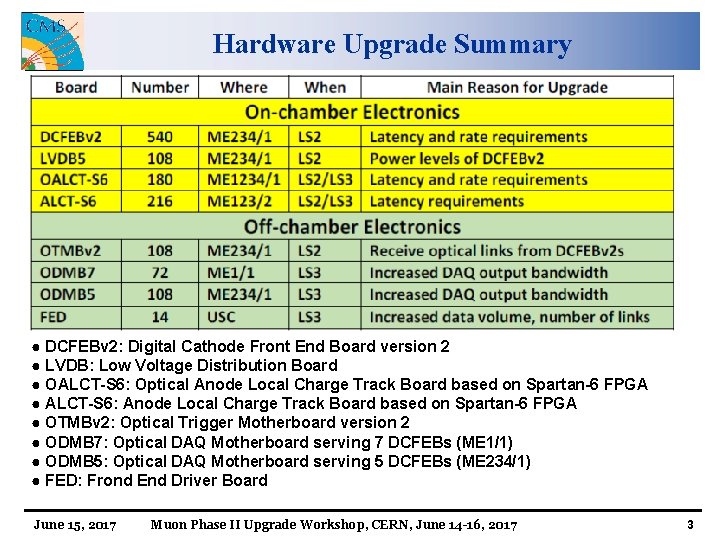

Hardware Upgrade Summary ● DCFEBv 2: Digital Cathode Front End Board version 2 ● LVDB: Low Voltage Distribution Board ● OALCT-S 6: Optical Anode Local Charge Track Board based on Spartan-6 FPGA ● ALCT-S 6: Anode Local Charge Track Board based on Spartan-6 FPGA ● OTMBv 2: Optical Trigger Motherboard version 2 ● ODMB 7: Optical DAQ Motherboard serving 7 DCFEBs (ME 1/1) ● ODMB 5: Optical DAQ Motherboard serving 5 DCFEBs (ME 234/1) ● FED: Frond End Driver Board June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 3

DCFEBv 2 Design Modifications ● Replace one Xilinx XCF 128 X PROM with two Xilinx XCF 32 P PROMs - both XCF 128 X and XCF 32 P are similar in terms of radiation tolerance, but XCF 128 X is obsolete and may not be available in required quantity in several months. XCF 08 P/16 P/32 P are still active. ● Add another PROM (XCF 08 P) to keep parameters ● Add a GBTx ASIC to implement PROM-less option for the FPGA ● Replace commercial optical transceivers with rad hard VTTx/VTRx ● Minor layout and placement improvements June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 4

PROM-less Option for DCFEBv 2 ● Recent radiation tests showed some Xilinx PROMs (both XCF 128 X and XCF 32 P) failed after 10 k. Rad ● PROM-less solution for DCFEBv 2 Virtex-6 FPGA would mitigate any radiation damage to PROMs ● Use radiation hard GBTx ASIC for downloading. Possible options: - Full duplex connection from FED to DCFEB - Full duplex connection from ODMB to DCFEB - Simplex connection from ODMB to DCFEB ● Utilize JTAG device with non-volatile I/O to select which programming option (PROM or GBTx) is active - DS 4550 is a candidate; under tests June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 5

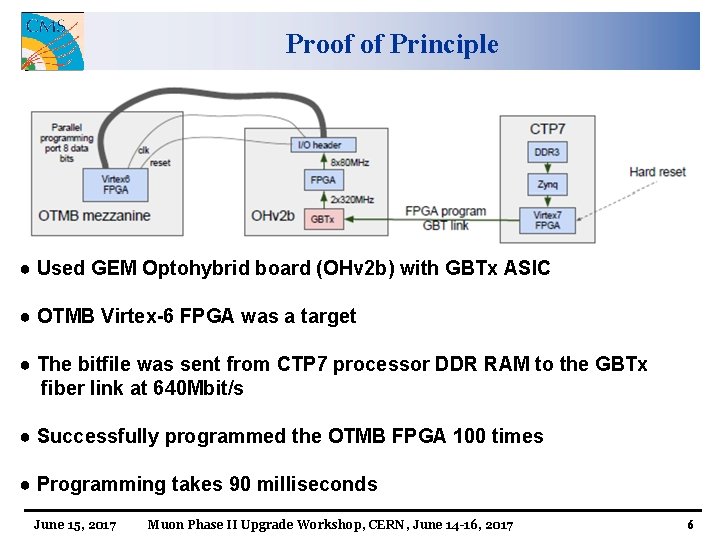

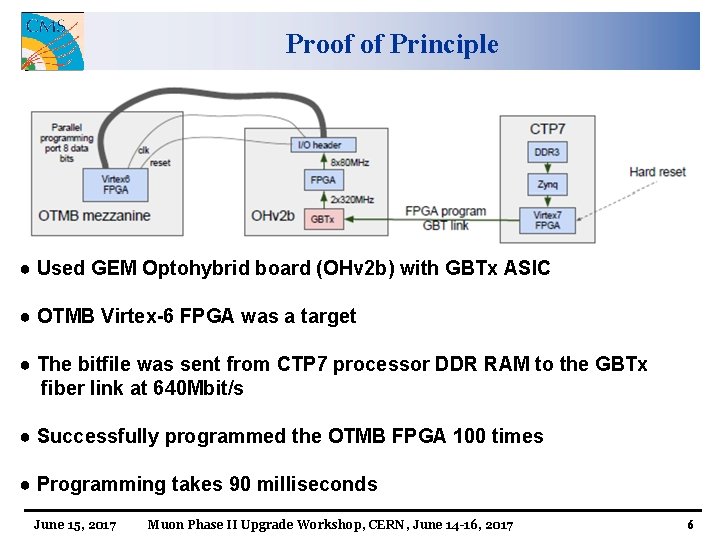

Proof of Principle ● Used GEM Optohybrid board (OHv 2 b) with GBTx ASIC ● OTMB Virtex-6 FPGA was a target ● The bitfile was sent from CTP 7 processor DDR RAM to the GBTx fiber link at 640 Mbit/s ● Successfully programmed the OTMB FPGA 100 times ● Programming takes 90 milliseconds June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 6

LCT Comparator ASIC ● CFEB/DCFEB triggering is based on comparator ASIC - Each ASIC comprises a network of 50 comparators and a digital part - Generates a serialized trigger output for 32 half-strips to TMB/OTMB - 6 ASICs per CFEB/DCFEB - designed and built in 1997 -2001 - we have a deficit of ~1000 ASICs for DCFEB upgrade ● New vendor: ON Semiconductor - order placed in late 2016, ~3000 ASICs - same package (TQFP 64) ● Engineering sample of 100 ASICs ready in spring 2017 - 96 received at UCLA in May (4 rejected during assembly) - 94 passed tests at UCLA (2 rejected) - 6 were OK after irradiation to 30 k. Rad at UCDavis cyclotron June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 7

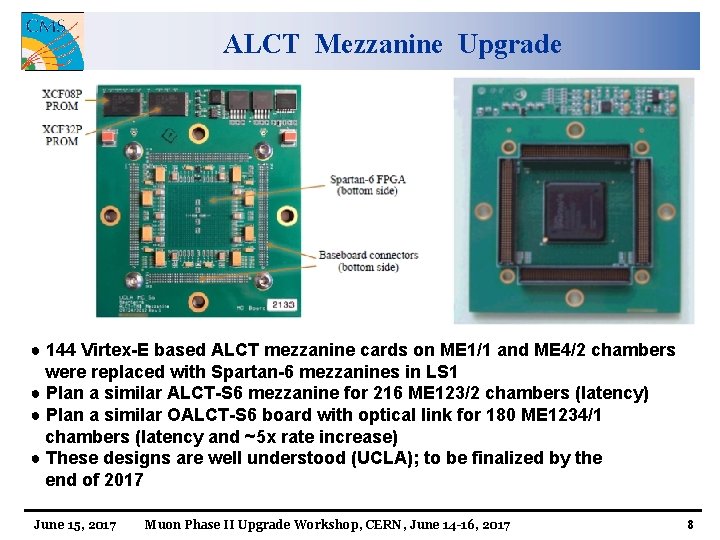

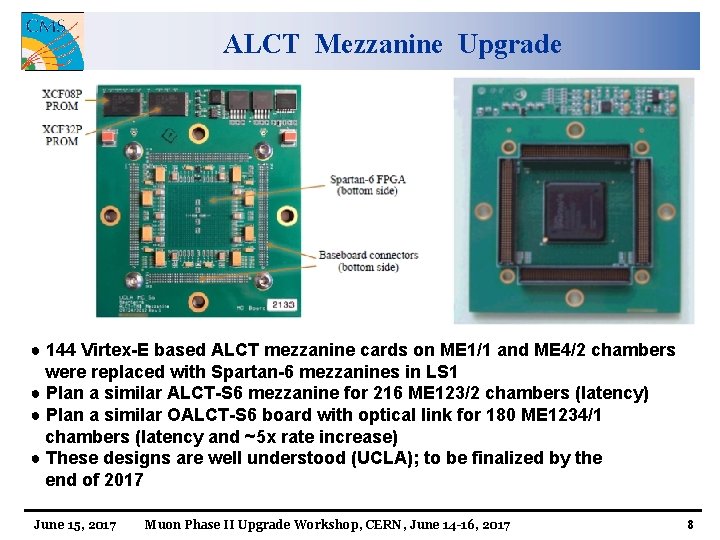

ALCT Mezzanine Upgrade ● 144 Virtex-E based ALCT mezzanine cards on ME 1/1 and ME 4/2 chambers were replaced with Spartan-6 mezzanines in LS 1 ● Plan a similar ALCT-S 6 mezzanine for 216 ME 123/2 chambers (latency) ● Plan a similar OALCT-S 6 board with optical link for 180 ME 1234/1 chambers (latency and ~5 x rate increase) ● These designs are well understood (UCLA); to be finalized by the end of 2017 June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 8

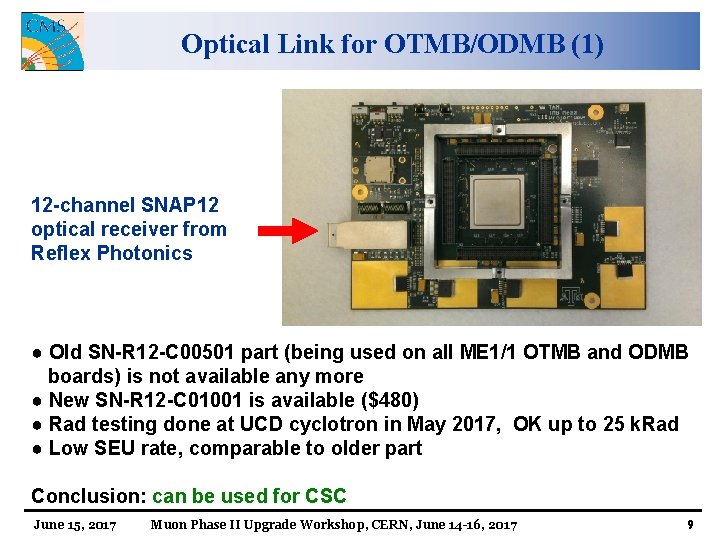

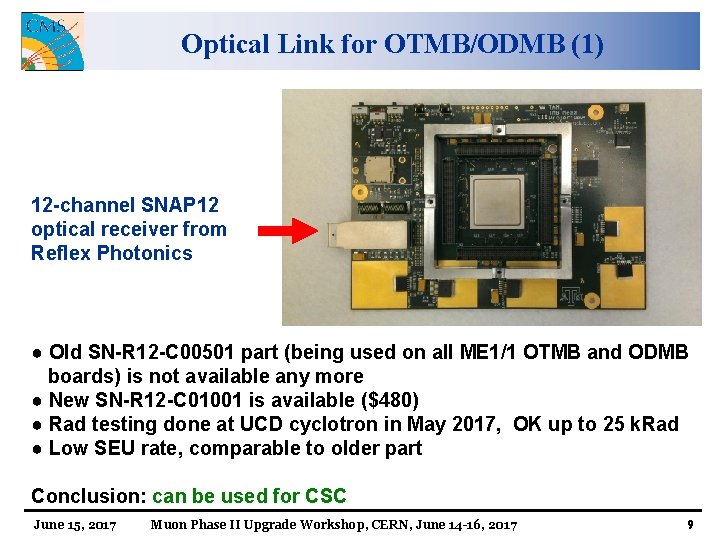

Optical Link for OTMB/ODMB (1) 12 -channel SNAP 12 optical receiver from Reflex Photonics ● Old SN-R 12 -C 00501 part (being used on all ME 1/1 OTMB and ODMB boards) is not available any more ● New SN-R 12 -C 01001 is available ($480) ● Rad testing done at UCD cyclotron in May 2017, OK up to 25 k. Rad ● Low SEU rate, comparable to older part Conclusion: can be used for CSC June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 9

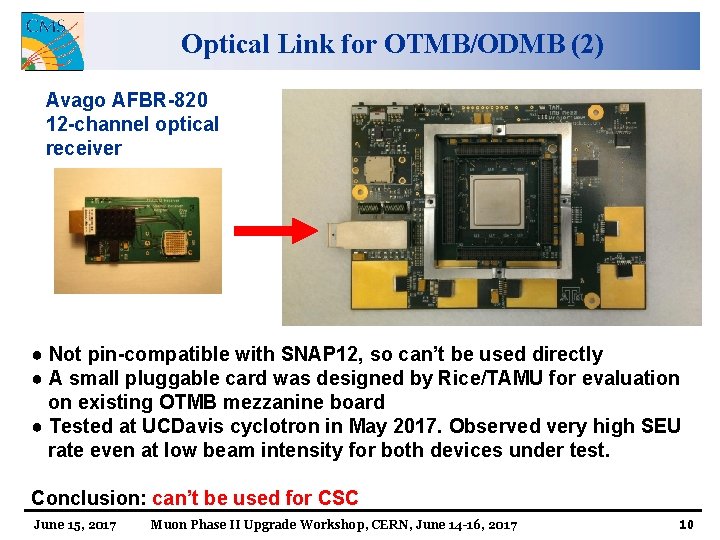

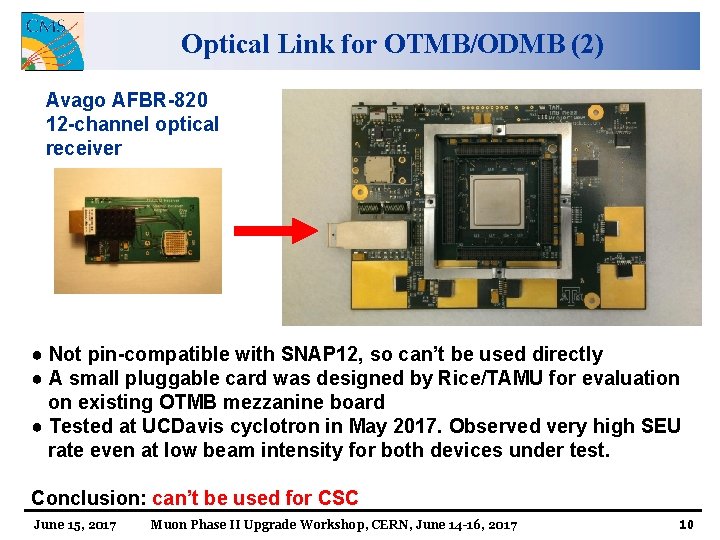

Optical Link for OTMB/ODMB (2) Avago AFBR-820 12 -channel optical receiver ● Not pin-compatible with SNAP 12, so can’t be used directly ● A small pluggable card was designed by Rice/TAMU for evaluation on existing OTMB mezzanine board ● Tested at UCDavis cyclotron in May 2017. Observed very high SEU rate even at low beam intensity for both devices under test. Conclusion: can’t be used for CSC June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 10

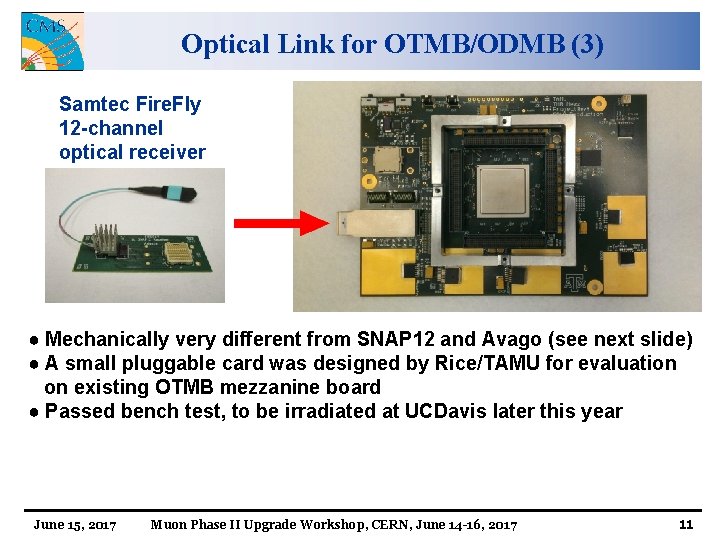

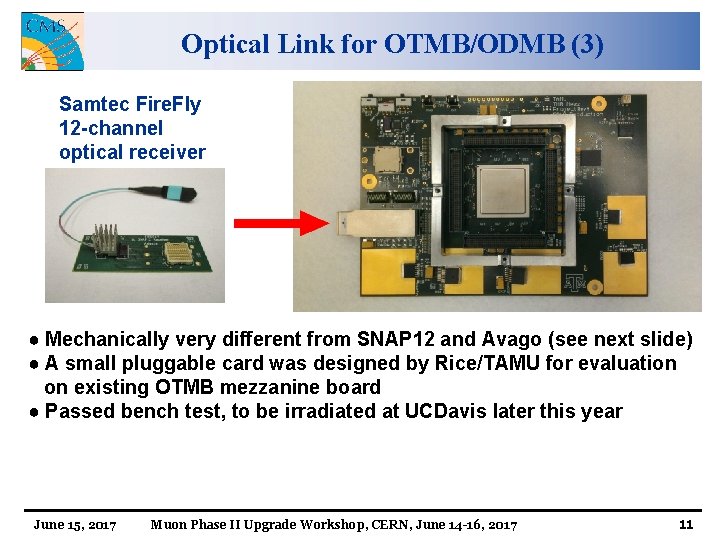

Optical Link for OTMB/ODMB (3) Samtec Fire. Fly 12 -channel optical receiver ● Mechanically very different from SNAP 12 and Avago (see next slide) ● A small pluggable card was designed by Rice/TAMU for evaluation on existing OTMB mezzanine board ● Passed bench test, to be irradiated at UCDavis later this year June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 11

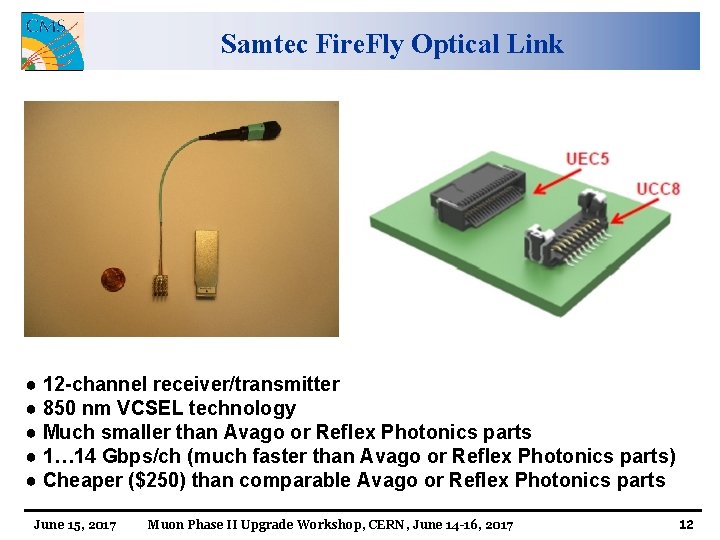

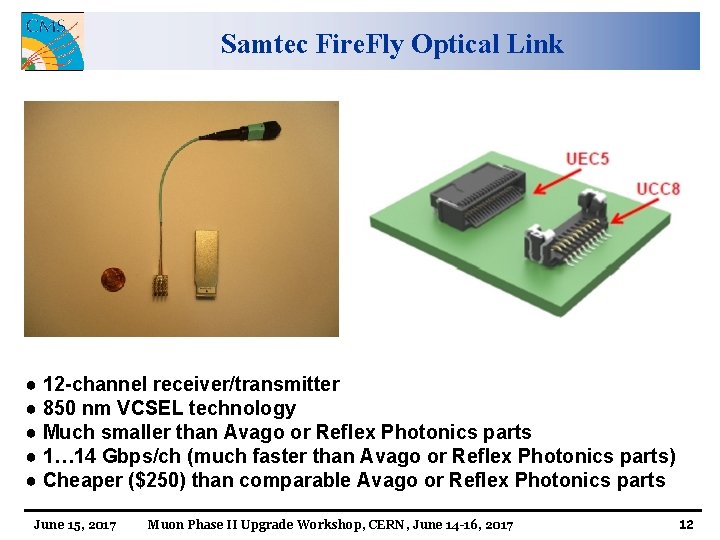

Samtec Fire. Fly Optical Link ● 12 -channel receiver/transmitter ● 850 nm VCSEL technology ● Much smaller than Avago or Reflex Photonics parts ● 1… 14 Gbps/ch (much faster than Avago or Reflex Photonics parts) ● Cheaper ($250) than comparable Avago or Reflex Photonics parts June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 12

LVDB 5 Board for ME 234/1 ● Will provide power to ALCT and 5 DCFEBv 2 on ME 234/1 chambers ● 120 boards total (108 + 12 spares) ● Design, fabrication and testing by JINR (Dubna) and INP (Minsk) ● Based on Sharp PQ 7 DV 10 voltage regulator ● Will use existing Low Voltage Monitoring Board (LVMB) ● Schematic design is done and prototypes are being built ● Two test stands will be assembled (production site and CERN) June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 13

HV Update ● Presently: CAEN system for ME 1/1 and UF/PNPI system for the rest of CSC ● Currents in the CSC scale linearly with the luminosity. The ME 2/1, ME 3/1, and ME 4/1 chambers are closest to the beam and draw the largest currents. Therefore, one expects a total current of about 700 µA in a pair of ME 2/1 chambers served by a single HV distribution board. The present limit of the HV distribution boards, set by the master HV boards, is 1. 5 m. A. This gives a safety factor of only two, which is uncomfortably small. Also need more reliable current measurements for ME 1/1. ● The plan is to have a common HV system for all CSCs. - 38 new 9 -channel Master boards - each channel will have its own HV power source 0… 4000 V, up to 2. 5 m. A. This gives a safety factor of 4. A prototype exists. June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 14

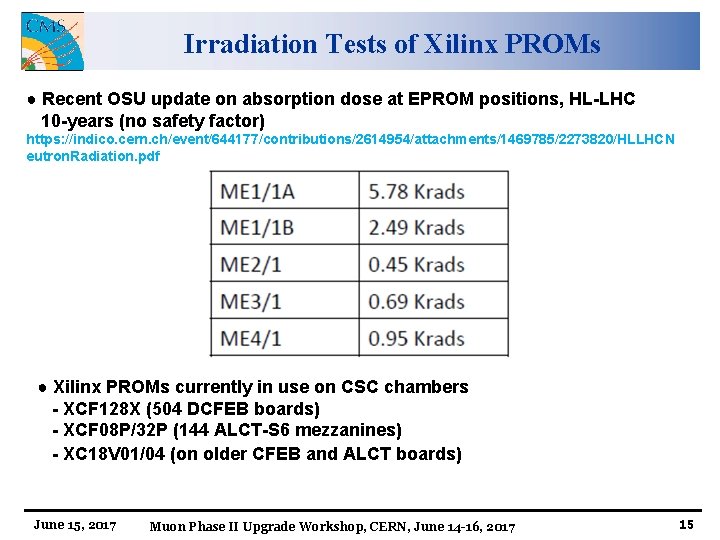

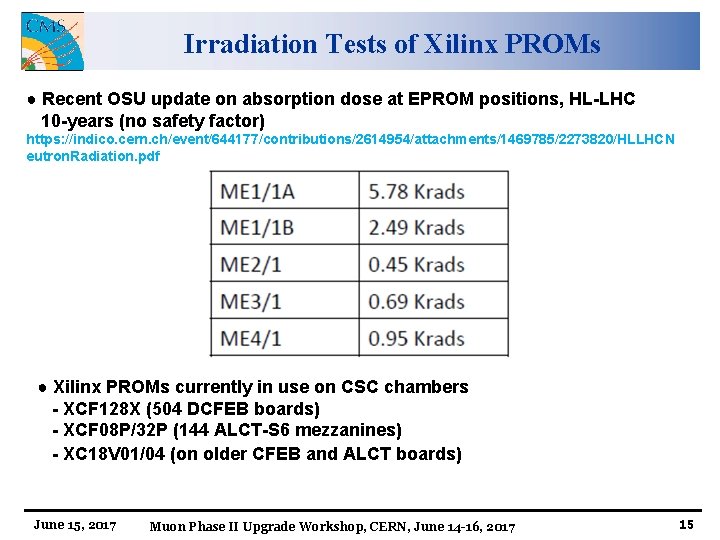

Irradiation Tests of Xilinx PROMs ● Recent OSU update on absorption dose at EPROM positions, HL-LHC 10 -years (no safety factor) https: //indico. cern. ch/event/644177/contributions/2614954/attachments/1469785/2273820/HLLHCN eutron. Radiation. pdf ● Xilinx PROMs currently in use on CSC chambers - XCF 128 X (504 DCFEB boards) - XCF 08 P/32 P (144 ALCT-S 6 mezzanines) - XC 18 V 01/04 (on older CFEB and ALCT boards) June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 15

Irradiation Tests of Xilinx XCF 32 P PROMs ● April 2013 at TAMU reactor: 1 device, OK after 30 k. Rad (but irradiated without power) ● November 2016 at CHARM: 1 of 2 devices failed after 35 k. Rad ● March 2017 at TAMU reactor: 4 devices, OK after 10 k. Rad, but all failed after 15 k. Rad ● May 2017 at UCDavis cyclotron: 2 devices; OK after 30 k. Rad Conclusion: Good up to 10 k. Rad. Tests finished. June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 16

Irradiation Tests of Xilinx XCF 128 X PROMs ● August 2011 at TAMU cyclotron: 1 device, OK after 3. 7 k. Rad ● November 2016 at CHARM: 2 devices, both failed after 35 k. Rad ● March 2017 at TAMU reactor: 2 devices, OK after 10 k. Rad, but both failed after 15 k. Rad ● May 2017 at UCDavis cyclotron: 2 devices; OK after 30 k. Rad Conclusion: Good up to 10 k. Rad. Tests finished. June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 17

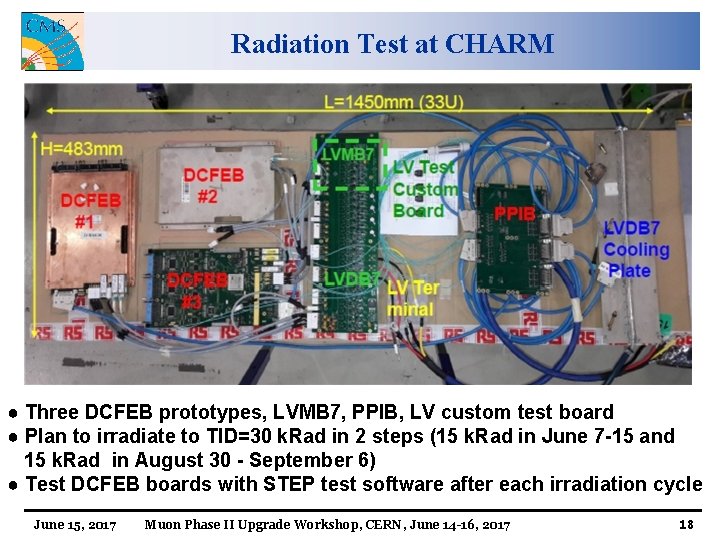

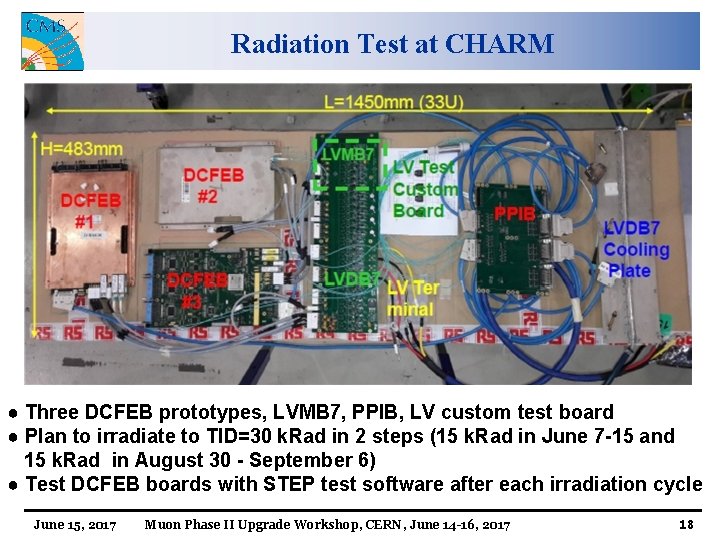

Radiation Test at CHARM ● Three DCFEB prototypes, LVMB 7, PPIB, LV custom test board ● Plan to irradiate to TID=30 k. Rad in 2 steps (15 k. Rad in June 7 -15 and 15 k. Rad in August 30 - September 6) ● Test DCFEB boards with STEP test software after each irradiation cycle June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 18

Conclusion and Near Future Plans ● Finalize the PROM-less implementation and other design modifications on DCFEBv 2 by October 2017 ● Very good yield of comparator ASICs, the order is in production ● Will use rad hard VTTX/VTRX optical parts for on-chamber upgrades. Evaluation of new optical parts for OTMBv 2/ODMB 5/7 is in progress. ● LVDB 5 prototype is being built ● Another round of irradiation tests at UCDavis cyclotron later in summer (Samtec Fire. Fly optical receiver, few more simple parts). Irradiation tests at CHARM ongoing, results not before October. June 15, 2017 Muon Phase II Upgrade Workshop, CERN, June 14 -16, 2017 19