CS 447 Computer Architecture Lecture 2 Computer Arithmetic

- Slides: 29

CS 447 – Computer Architecture Lecture 2 Computer Arithmetic (1) August 29, 2007 Karem Sakallah ksakalla@qatar. cmu. edu www. qatar. cmu. edu/~msakr/15447 -f 07/ Computer Architecture Fall 2007 ©

Chapter objectives In this lecture we will focus on the representation of numbers and techniques for implementing arithmetic operations. Processors typically support two types of arithmetic: integer, or fixed point, and floating point. For both cases, the lecture first examines the representation of numbers and then discusses arithmetic operations. Computer Architecture Fall 2007 ©

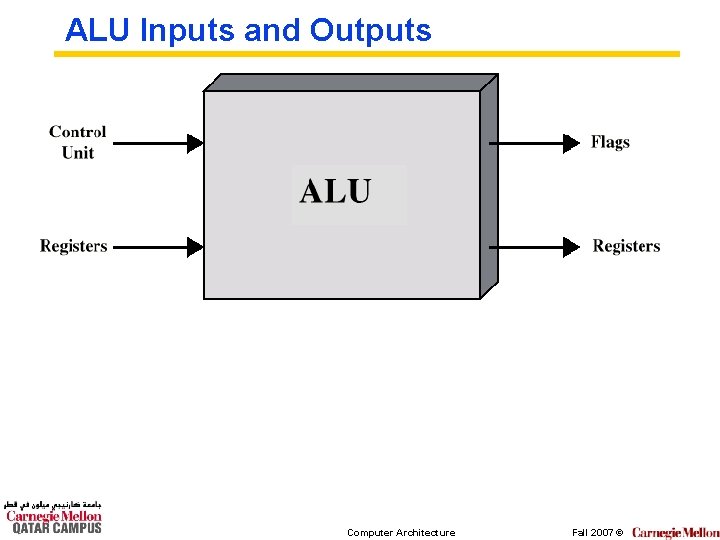

Arithmetic & Logic Unit ° Does the calculations ° Everything else in the computer is there to service this unit ° Handles integers ° May handle floating point (real) numbers ° May be separate (maths co-processor) Computer Architecture Fall 2007 ©

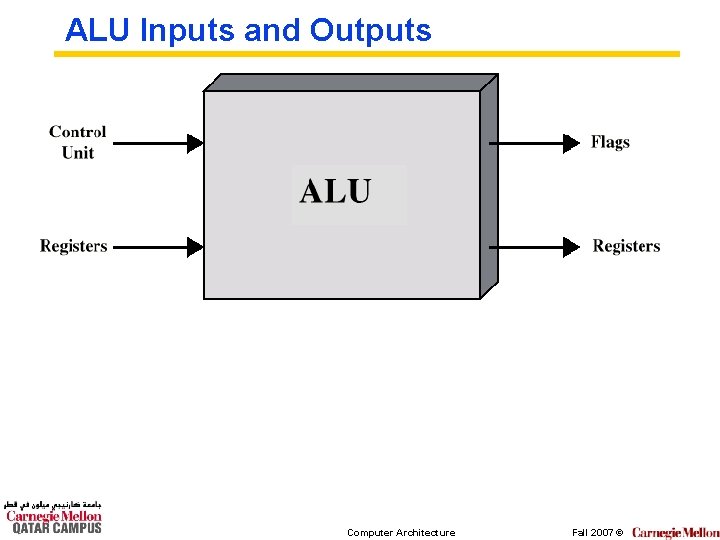

ALU Inputs and Outputs Computer Architecture Fall 2007 ©

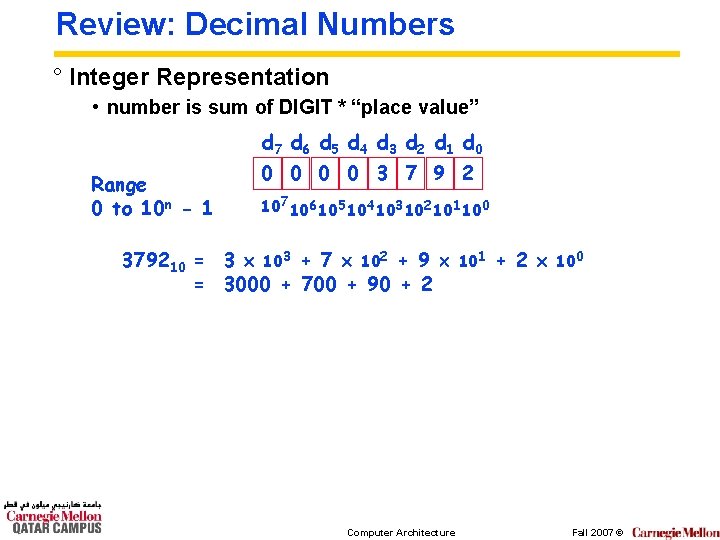

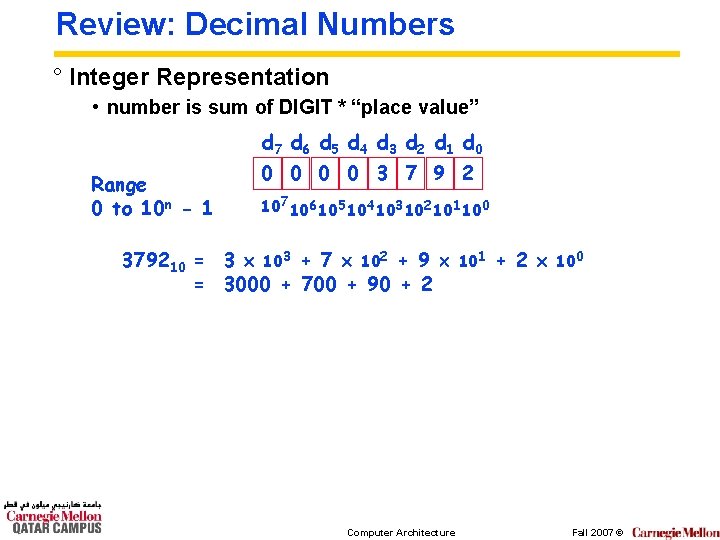

Review: Decimal Numbers ° Integer Representation • number is sum of DIGIT * “place value” d 7 d 6 d 5 d 4 d 3 d 2 d 1 d 0 Range 0 to 10 n - 1 0 0 3 7 9 2 107 106 105 104 103 102 101 100 379210 = 3 103 + 7 102 + 9 = 3000 + 700 + 90 + 2 Computer Architecture 101 + 2 100 Fall 2007 ©

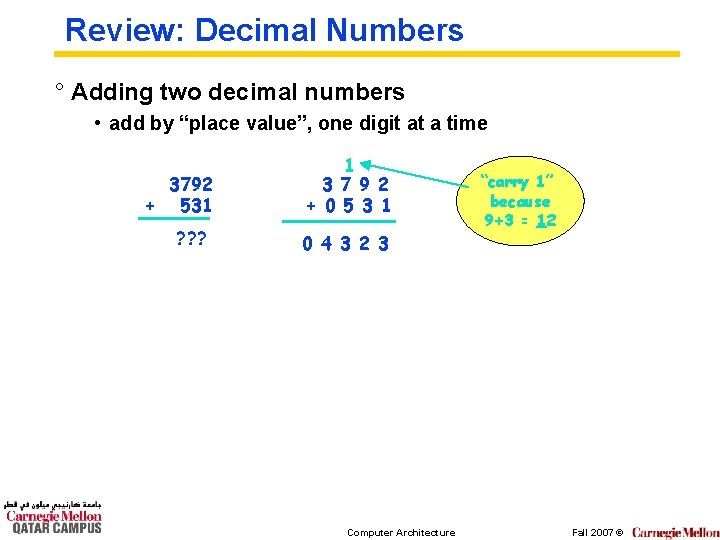

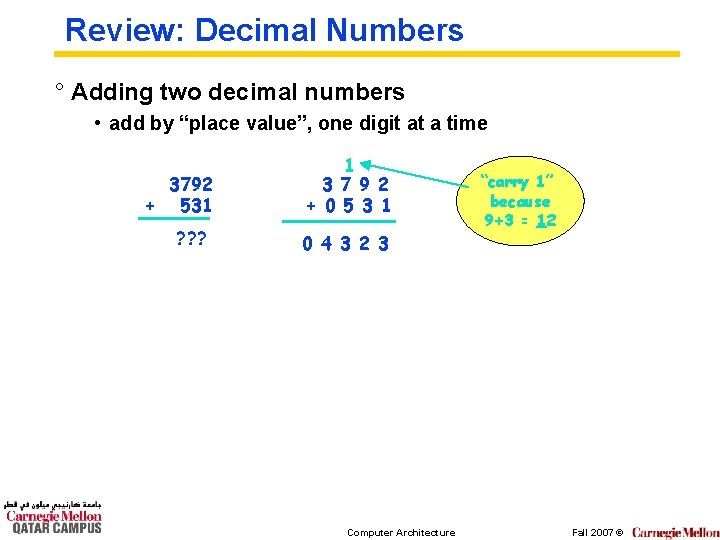

Review: Decimal Numbers ° Adding two decimal numbers • add by “place value”, one digit at a time 3792 + 531 ? ? ? 1 3 7 9 2 + 0 5 3 1 0 4 3 2 3 Computer Architecture “carry 1” because 9+3 = 12 Fall 2007 ©

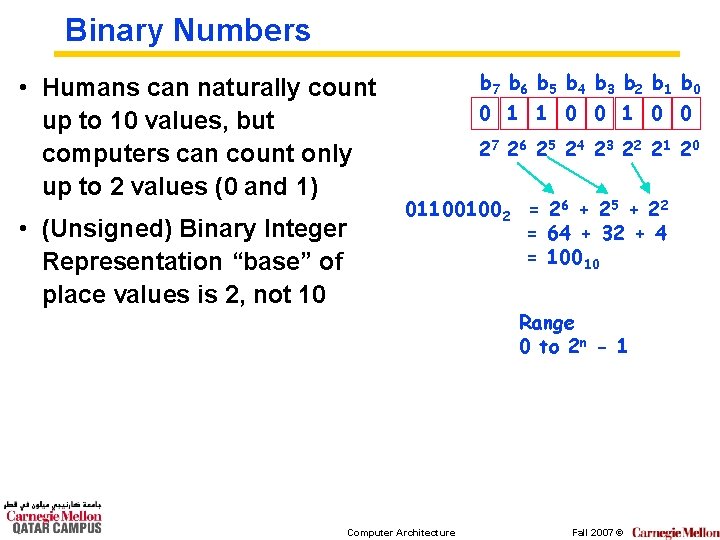

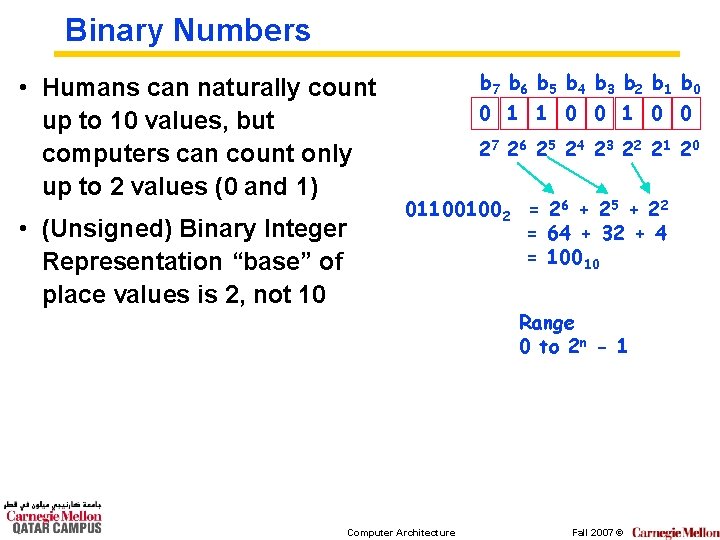

Binary Numbers • Humans can naturally count up to 10 values, but computers can count only up to 2 values (0 and 1) • (Unsigned) Binary Integer Representation “base” of place values is 2, not 10 b 7 b 6 b 5 b 4 b 3 b 2 b 1 b 0 0 1 1 0 0 27 26 25 24 23 22 21 20 011001002 = 26 + 25 + 22 = 64 + 32 + 4 = 10010 Computer Architecture Range 0 to 2 n - 1 Fall 2007 ©

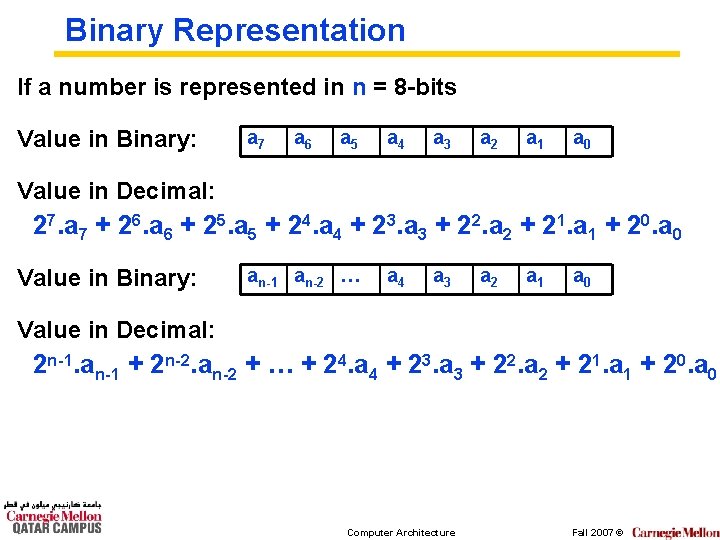

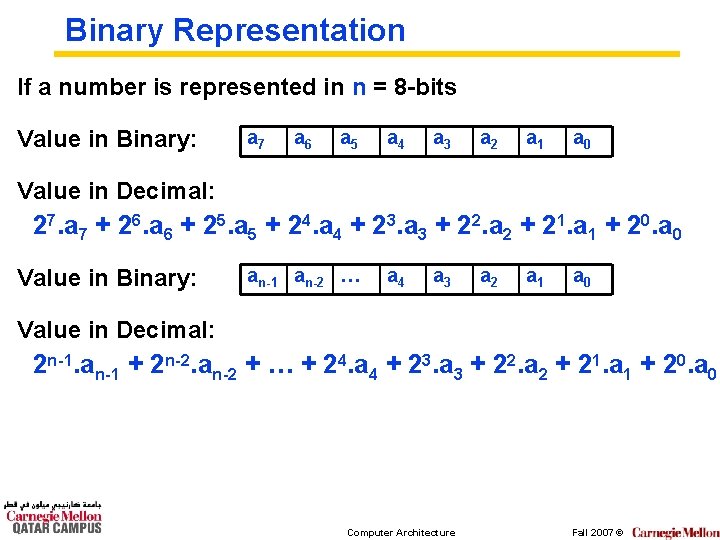

Binary Representation If a number is represented in n = 8 -bits Value in Binary: a 7 a 6 a 5 a 4 a 3 a 2 a 1 a 0 Value in Decimal: 27. a 7 + 26. a 6 + 25. a 5 + 24. a 4 + 23. a 3 + 22. a 2 + 21. a 1 + 20. a 0 Value in Binary: an-1 an-2 … a 4 a 3 a 2 a 1 a 0 Value in Decimal: 2 n-1. an-1 + 2 n-2. an-2 + … + 24. a 4 + 23. a 3 + 22. a 2 + 21. a 1 + 20. a 0 Computer Architecture Fall 2007 ©

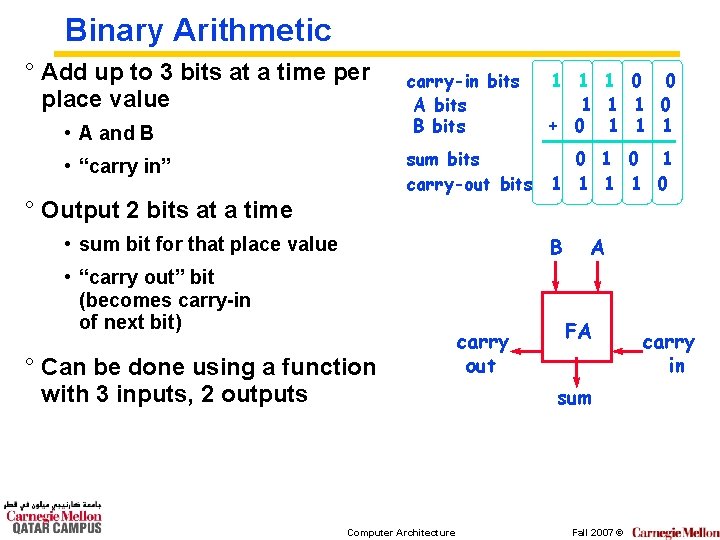

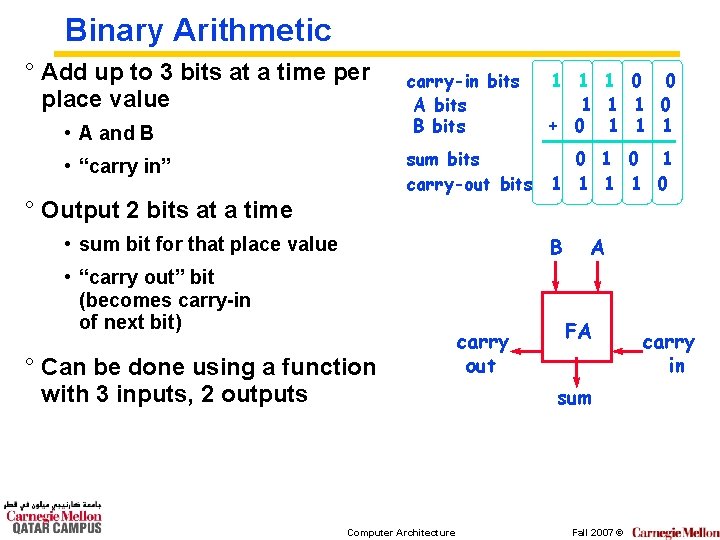

Binary Arithmetic ° Add up to 3 bits at a time per place value • A and B • “carry in” carry-in bits A bits B bits 1 1 1 0 0 1 1 1 0 + 0 1 1 1 sum bits carry-out bits 0 1 1 1 0 ° Output 2 bits at a time B • sum bit for that place value • “carry out” bit (becomes carry-in of next bit) ° Can be done using a function with 3 inputs, 2 outputs Computer Architecture carry out A FA sum Fall 2007 © carry in

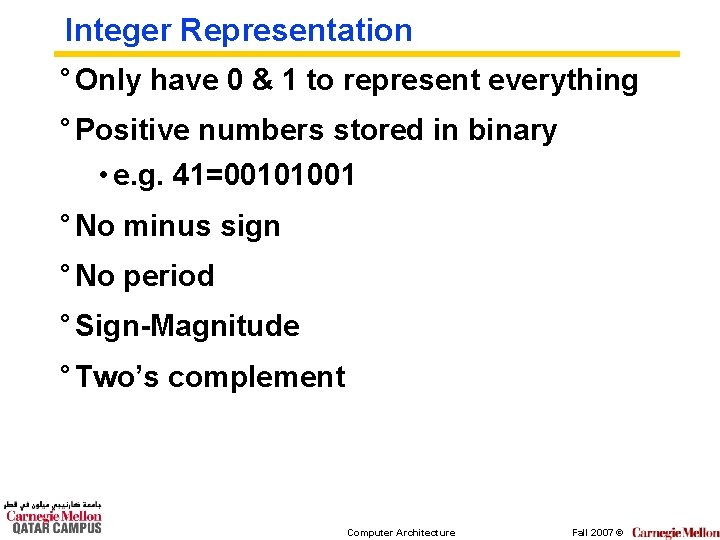

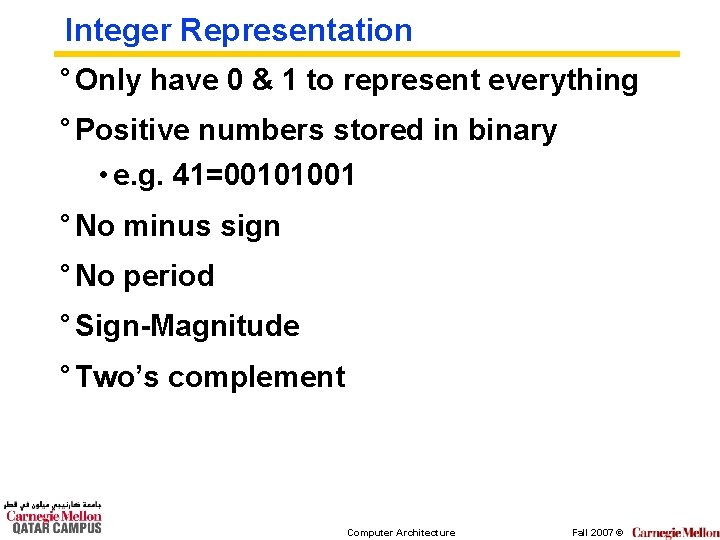

Integer Representation ° Only have 0 & 1 to represent everything ° Positive numbers stored in binary • e. g. 41=00101001 ° No minus sign ° No period ° Sign-Magnitude ° Two’s complement Computer Architecture Fall 2007 ©

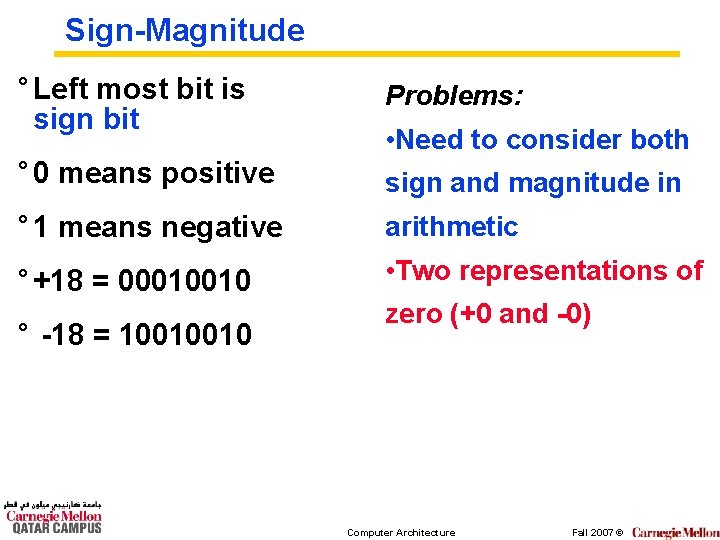

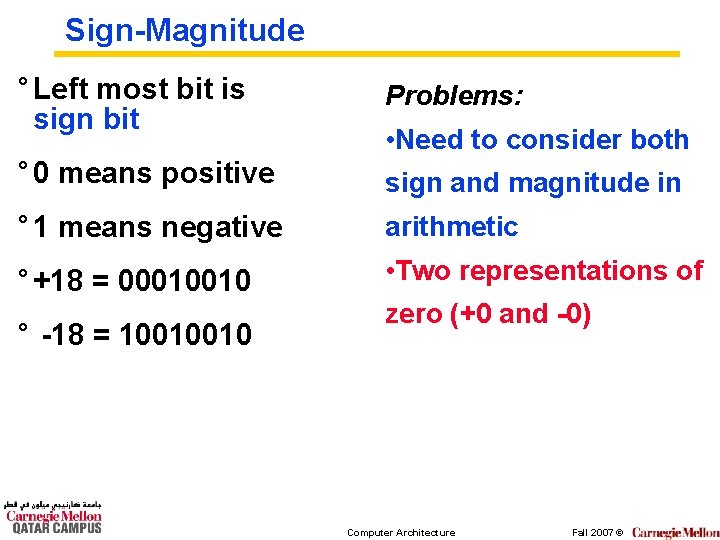

Sign-Magnitude ° Left most bit is sign bit Problems: ° 0 means positive sign and magnitude in ° 1 means negative arithmetic ° +18 = 00010010 • Two representations of ° -18 = 10010010 • Need to consider both zero (+0 and -0) Computer Architecture Fall 2007 ©

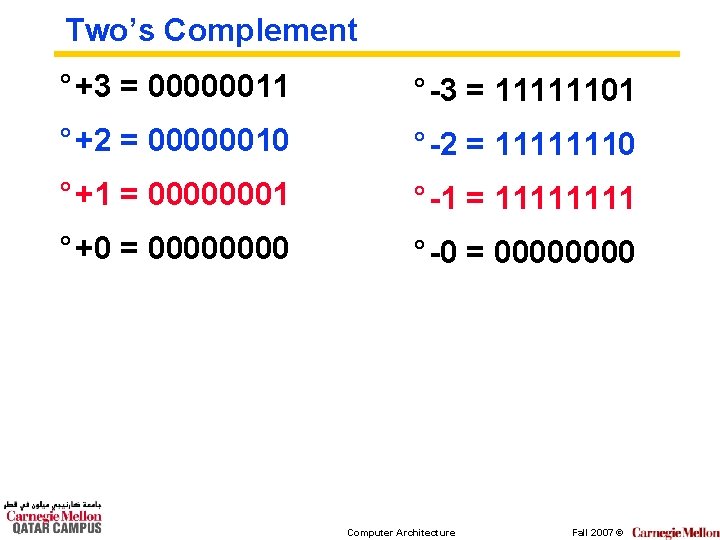

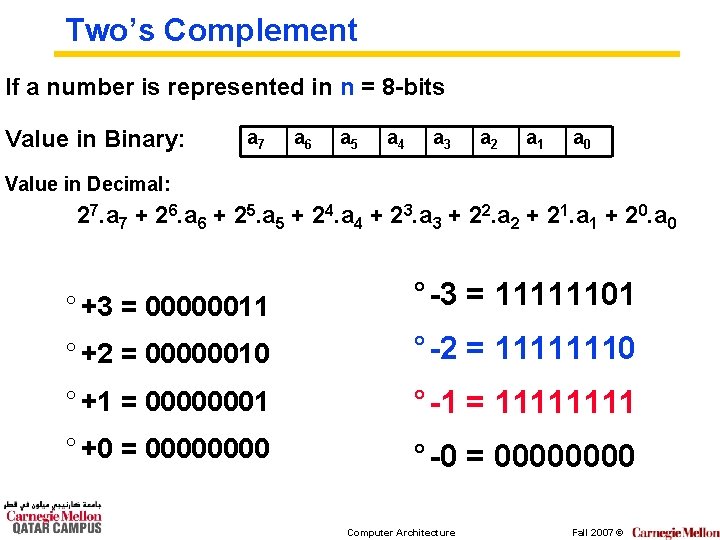

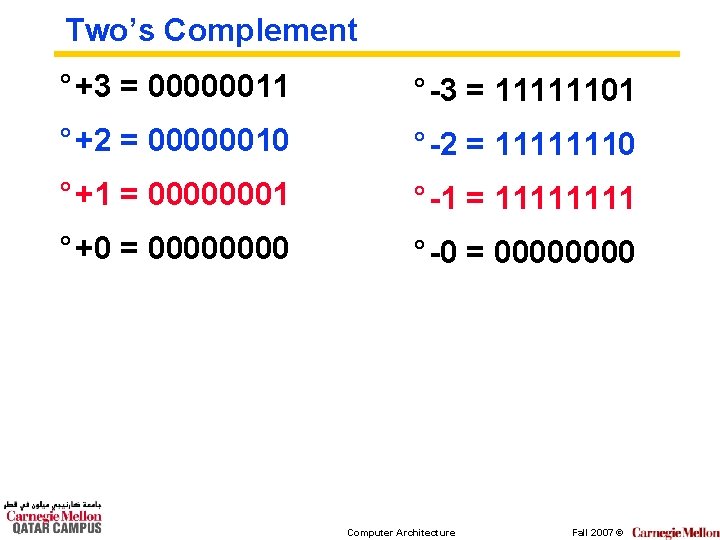

Two’s Complement ° +3 = 00000011 ° -3 = 11111101 ° +2 = 00000010 ° -2 = 11111110 ° +1 = 00000001 ° -1 = 1111 ° +0 = 0000 ° -0 = 0000 Computer Architecture Fall 2007 ©

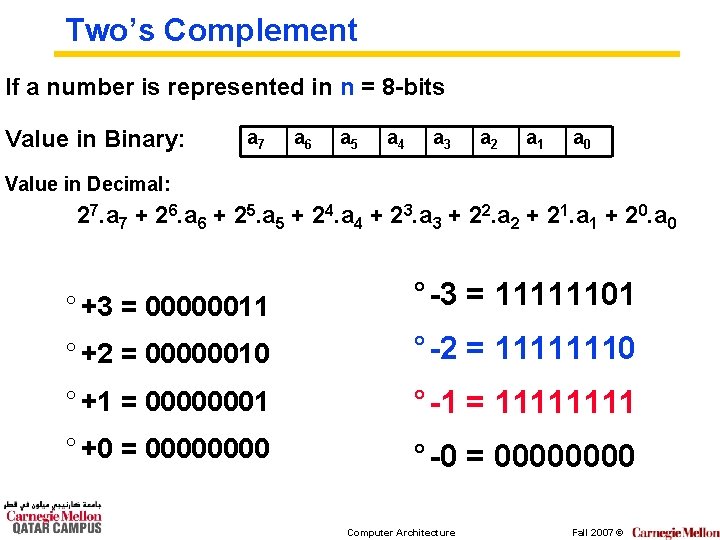

Two’s Complement If a number is represented in n = 8 -bits Value in Binary: a 7 a 6 a 5 a 4 a 3 a 2 a 1 a 0 Value in Decimal: 27. a 7 + 26. a 6 + 25. a 5 + 24. a 4 + 23. a 3 + 22. a 2 + 21. a 1 + 20. a 0 ° +3 = 00000011 ° -3 = 11111101 ° +2 = 00000010 ° -2 = 11111110 ° +1 = 00000001 ° -1 = 1111 ° +0 = 0000 ° -0 = 0000 Computer Architecture Fall 2007 ©

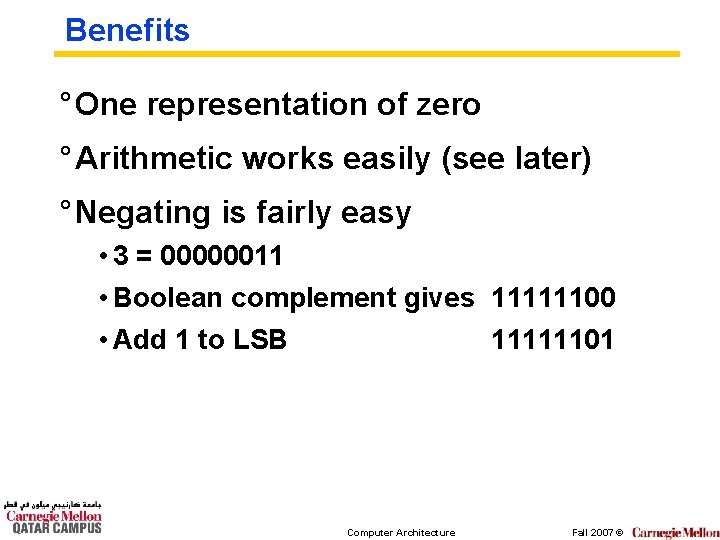

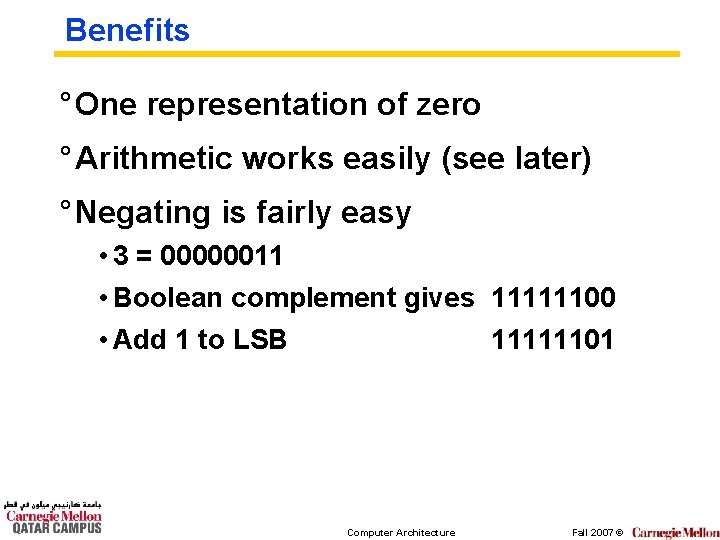

Benefits ° One representation of zero ° Arithmetic works easily (see later) ° Negating is fairly easy • 3 = 00000011 • Boolean complement gives 11111100 • Add 1 to LSB 11111101 Computer Architecture Fall 2007 ©

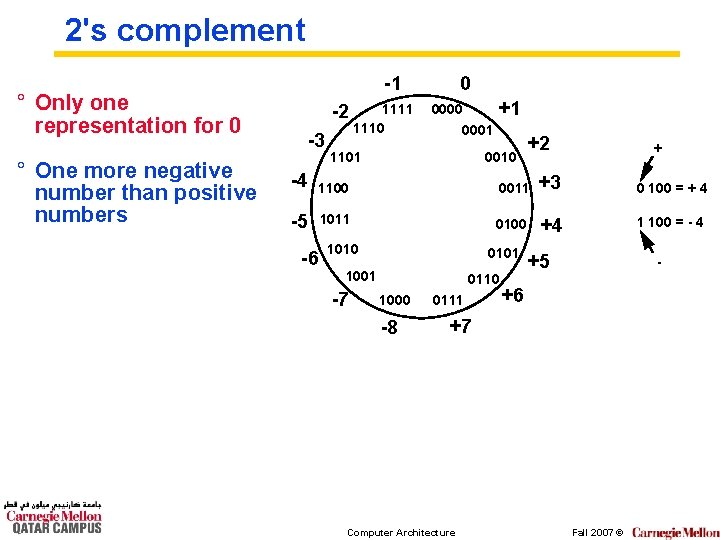

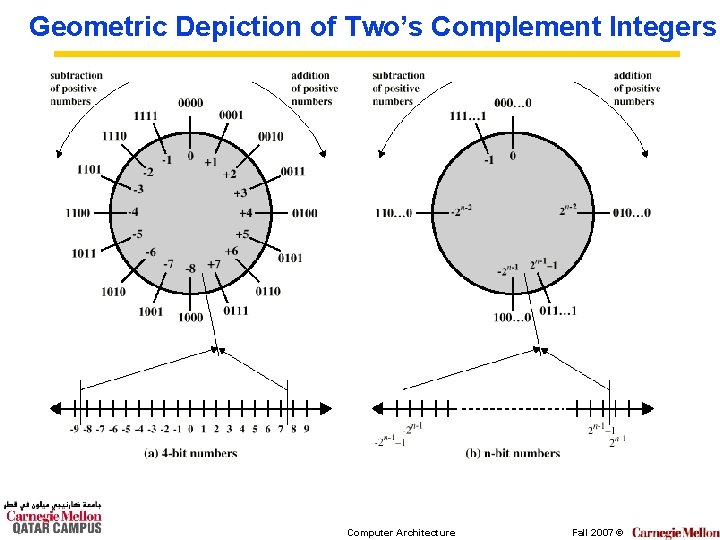

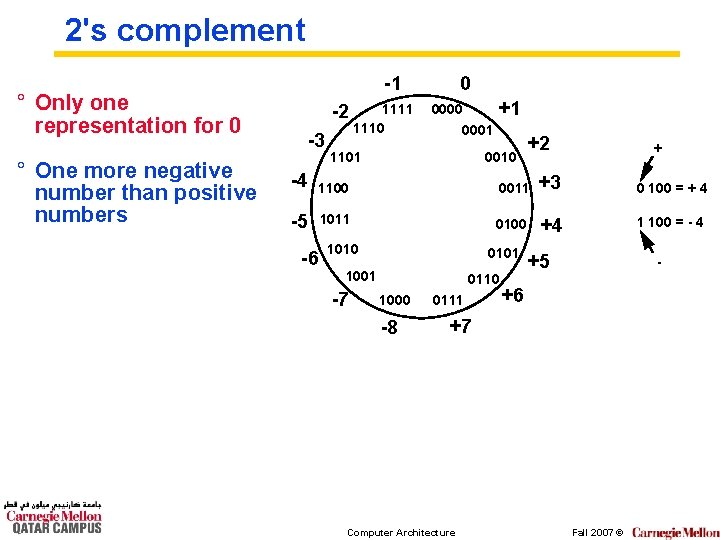

2's complement ° Only one representation for 0 ° One more negative number than positive numbers -1 -2 -3 1111 1110 0 0001 1101 +1 0010 +2 + -4 1100 0011 +3 0 100 = + 4 -5 1011 0100 +4 1 100 = - 4 -6 1010 0101 1001 -7 0110 1000 -8 0111 +5 - +6 +7 Computer Architecture Fall 2007 ©

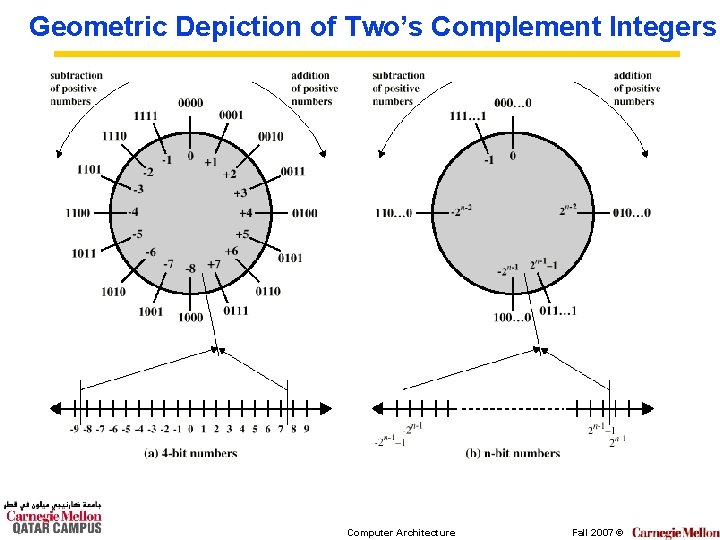

Geometric Depiction of Two’s Complement Integers Computer Architecture Fall 2007 ©

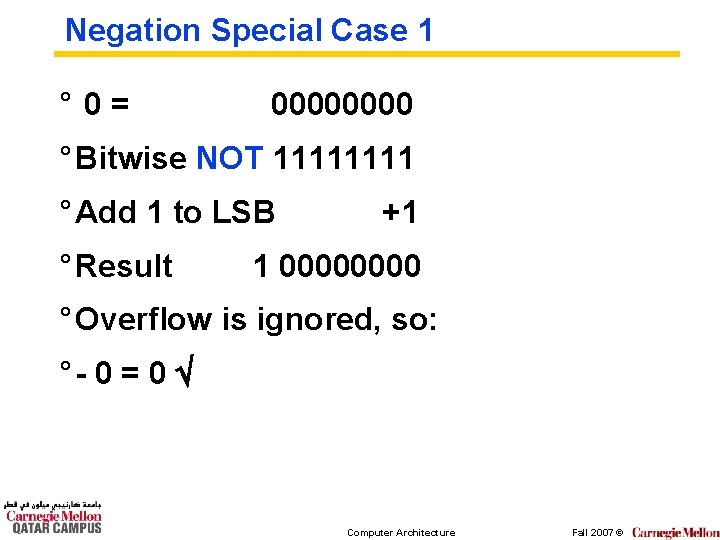

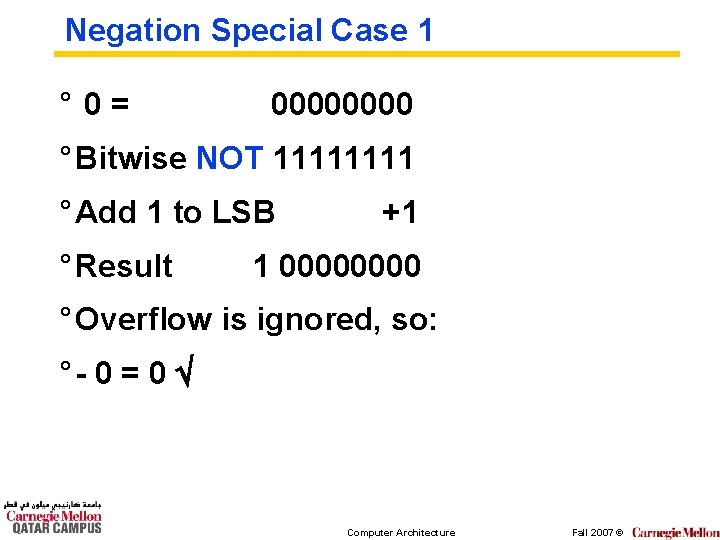

Negation Special Case 1 ° 0= 0000 ° Bitwise NOT 1111 ° Add 1 to LSB ° Result +1 1 0000 ° Overflow is ignored, so: °- 0 = 0 Computer Architecture Fall 2007 ©

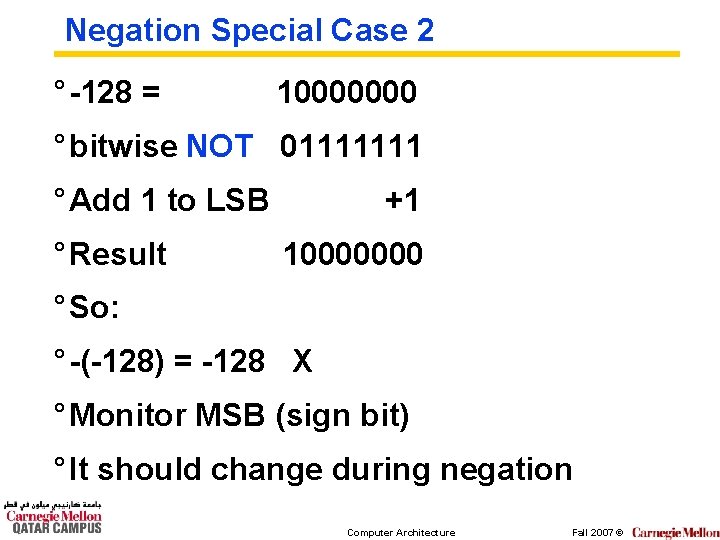

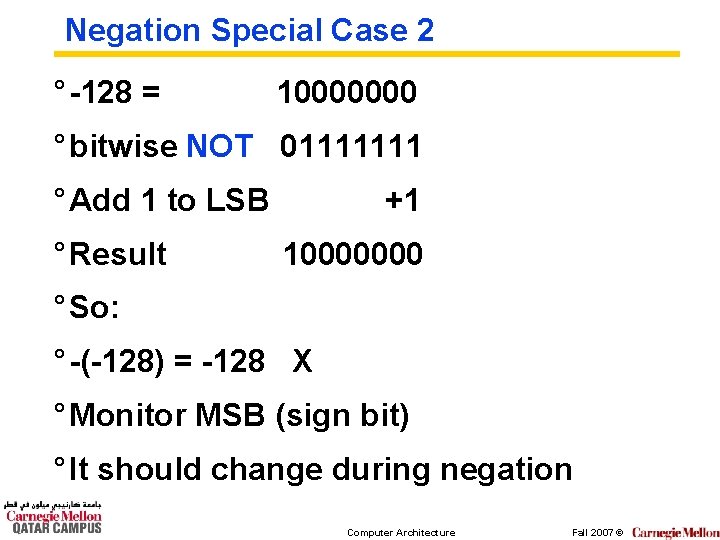

Negation Special Case 2 ° -128 = 10000000 ° bitwise NOT 01111111 ° Add 1 to LSB ° Result +1 10000000 ° So: ° -(-128) = -128 X ° Monitor MSB (sign bit) ° It should change during negation Computer Architecture Fall 2007 ©

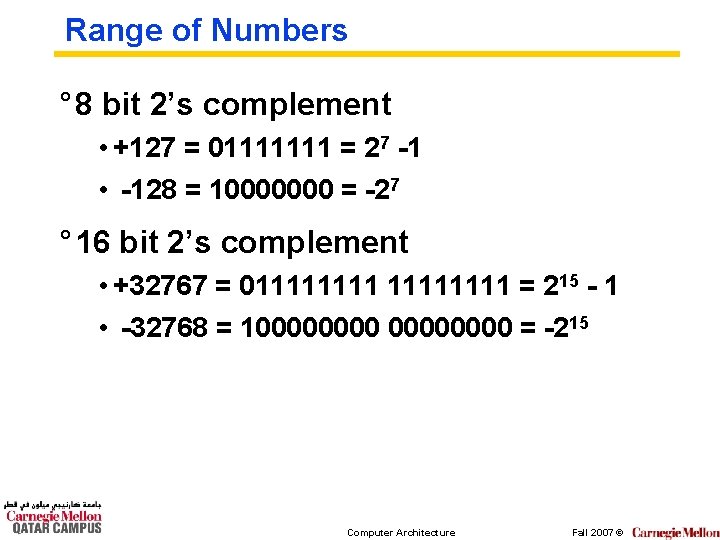

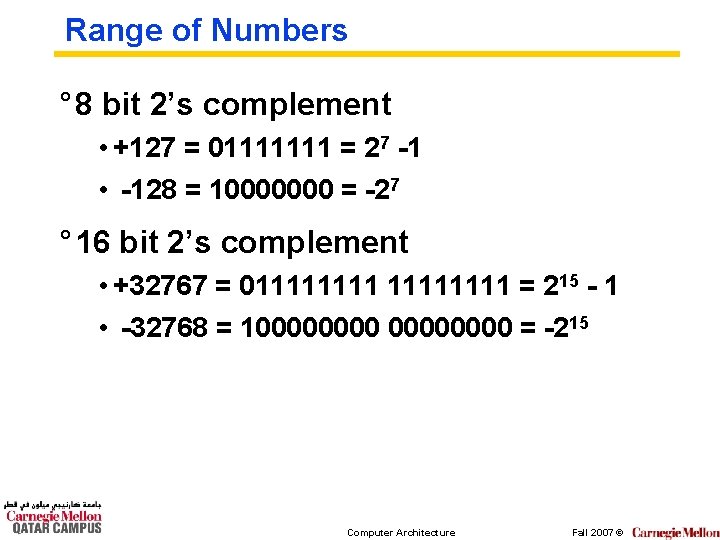

Range of Numbers ° 8 bit 2’s complement • +127 = 01111111 = 27 -1 • -128 = 10000000 = -27 ° 16 bit 2’s complement • +32767 = 011111111 = 215 - 1 • -32768 = 100000000 = -215 Computer Architecture Fall 2007 ©

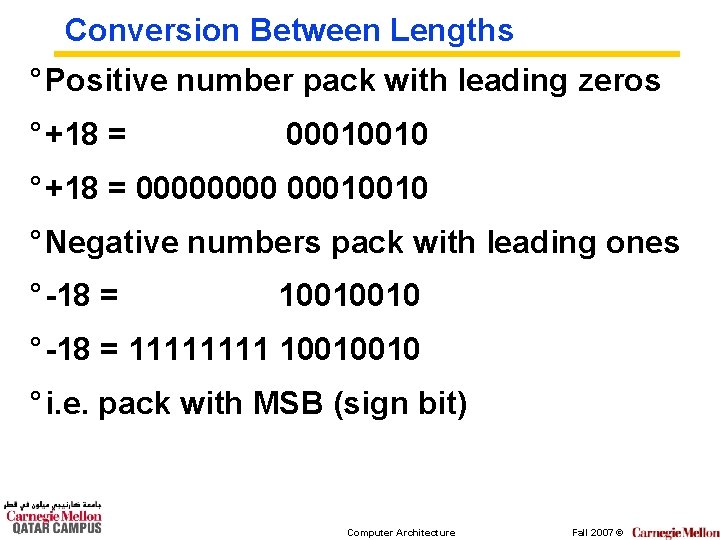

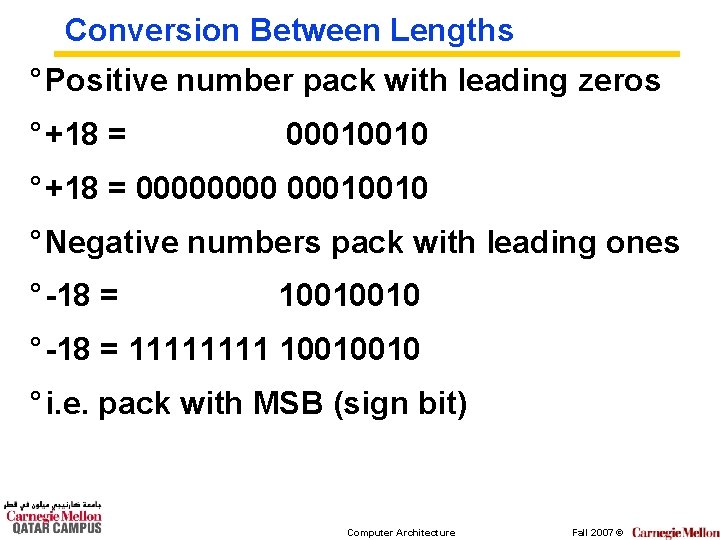

Conversion Between Lengths ° Positive number pack with leading zeros ° +18 = 00010010 ° +18 = 0000 00010010 ° Negative numbers pack with leading ones ° -18 = 10010010 ° -18 = 1111 10010010 ° i. e. pack with MSB (sign bit) Computer Architecture Fall 2007 ©

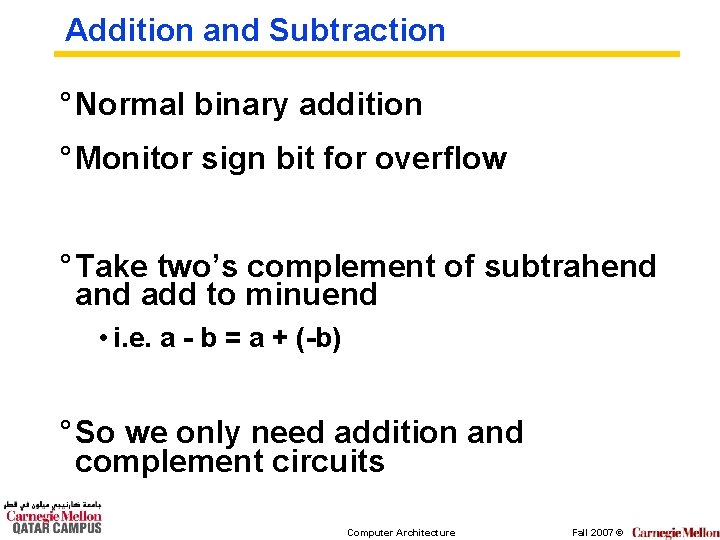

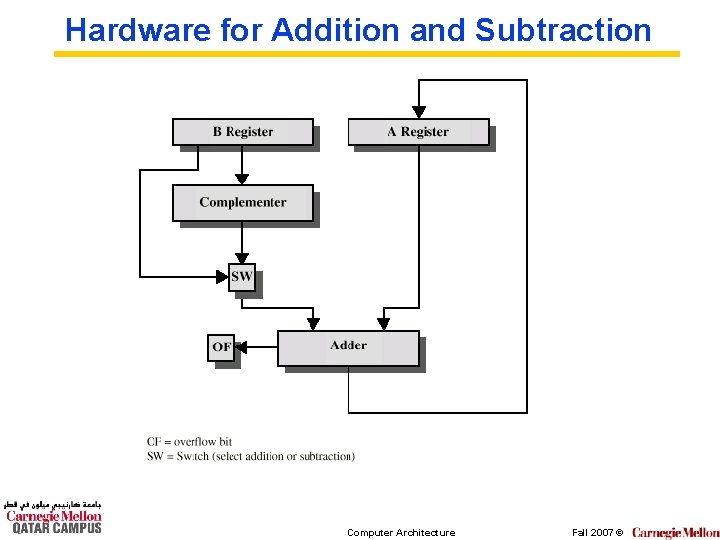

Addition and Subtraction ° Normal binary addition ° Monitor sign bit for overflow ° Take two’s complement of subtrahend add to minuend • i. e. a - b = a + (-b) ° So we only need addition and complement circuits Computer Architecture Fall 2007 ©

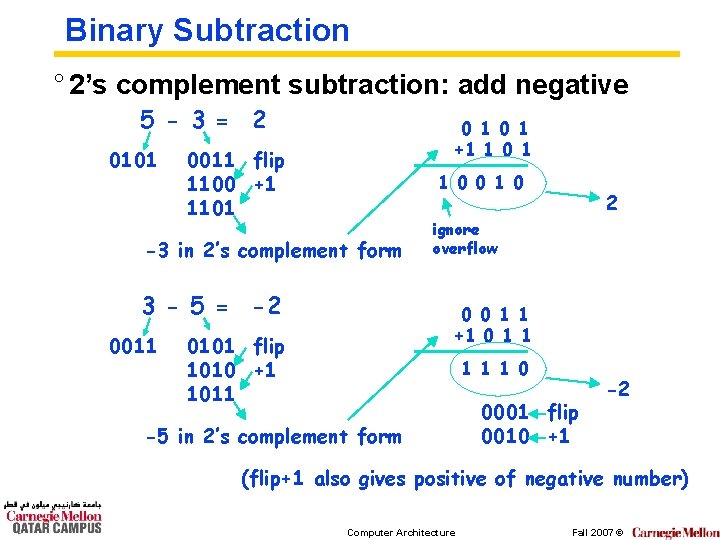

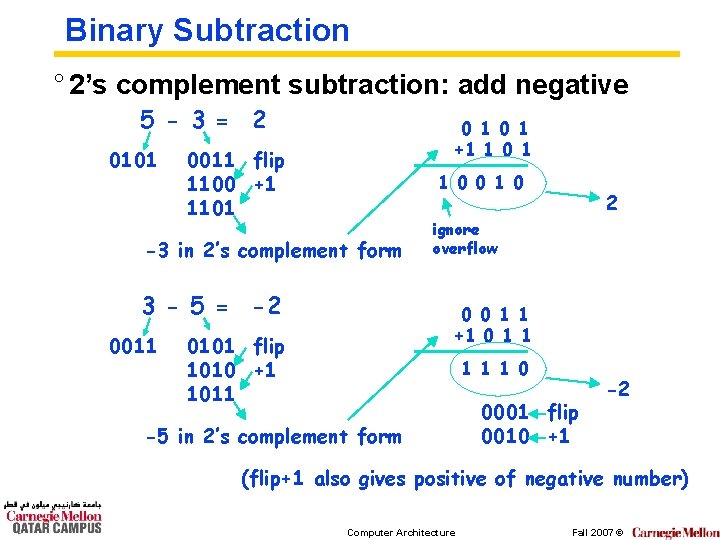

Binary Subtraction ° 2’s complement subtraction: add negative 5 - 3 = 2 0101 0 1 +1 1 0011 flip 1100 +1 1101 1 0 0 1 0 -3 in 2’s complement form 3 - 5 = -2 0011 2 ignore overflow 0 0 1 1 +1 0 1 1 0101 flip 1010 +1 1011 1 0 -5 in 2’s complement form 0001 flip 0010 +1 -2 (flip+1 also gives positive of negative number) Computer Architecture Fall 2007 ©

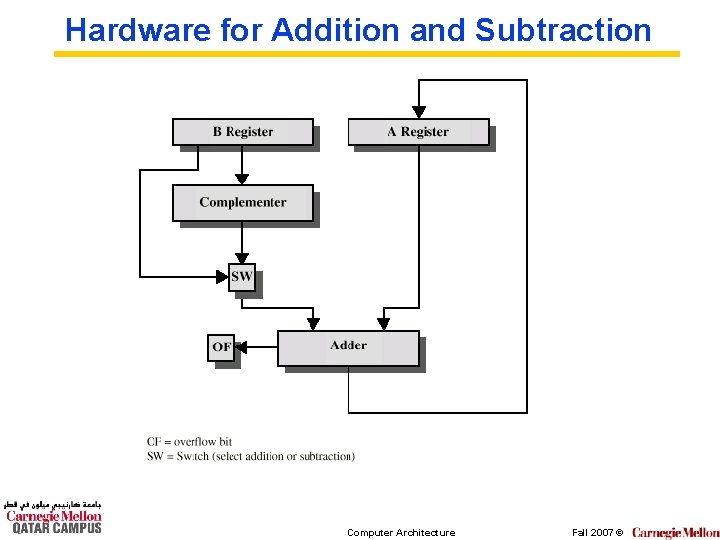

Hardware for Addition and Subtraction Computer Architecture Fall 2007 ©

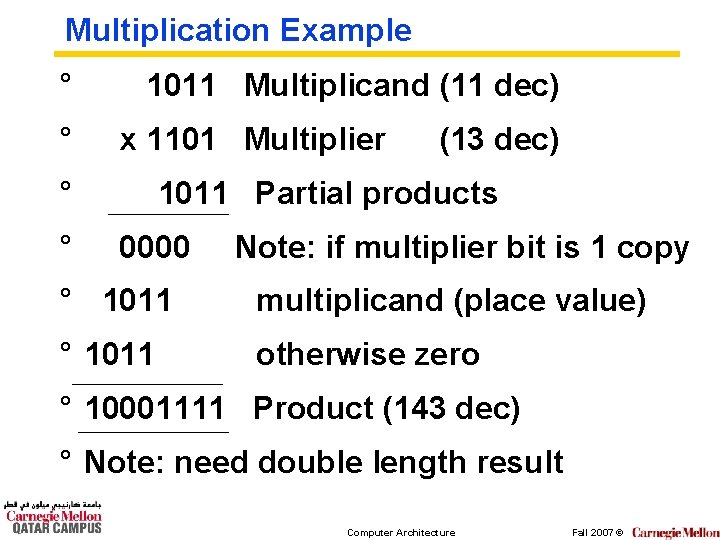

Multiplication ° Complex ° Work out partial product for each digit ° Take care with place value (column) ° Add partial products Computer Architecture Fall 2007 ©

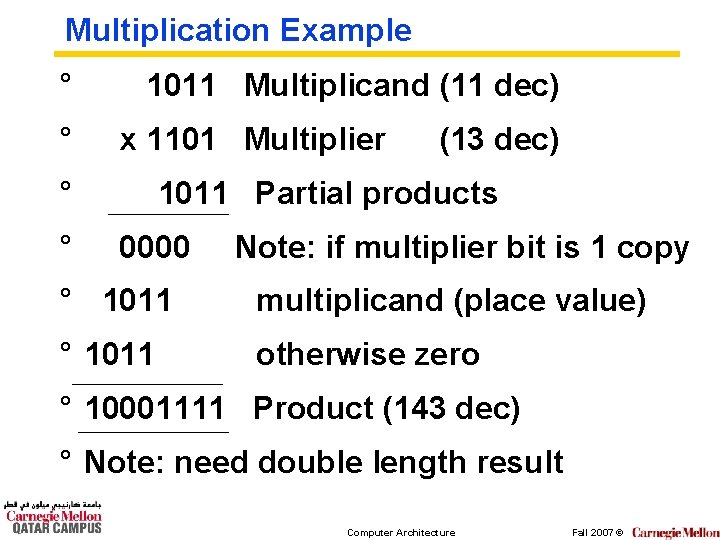

Multiplication Example ° ° 1011 Multiplicand (11 dec) x 1101 Multiplier ° ° (13 dec) 1011 Partial products 0000 Note: if multiplier bit is 1 copy ° 1011 multiplicand (place value) ° 1011 otherwise zero ° 10001111 Product (143 dec) ° Note: need double length result Computer Architecture Fall 2007 ©

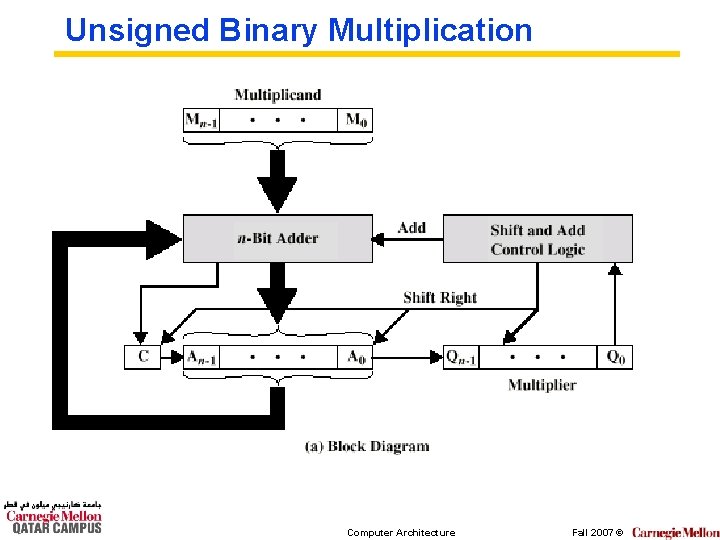

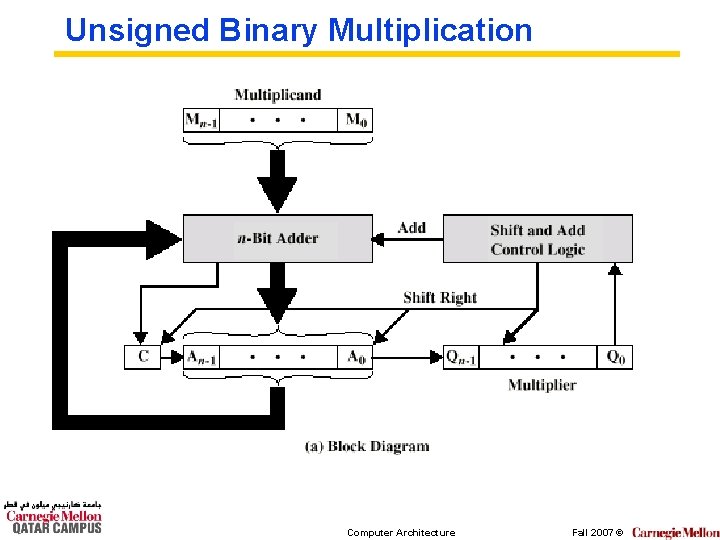

Unsigned Binary Multiplication Computer Architecture Fall 2007 ©

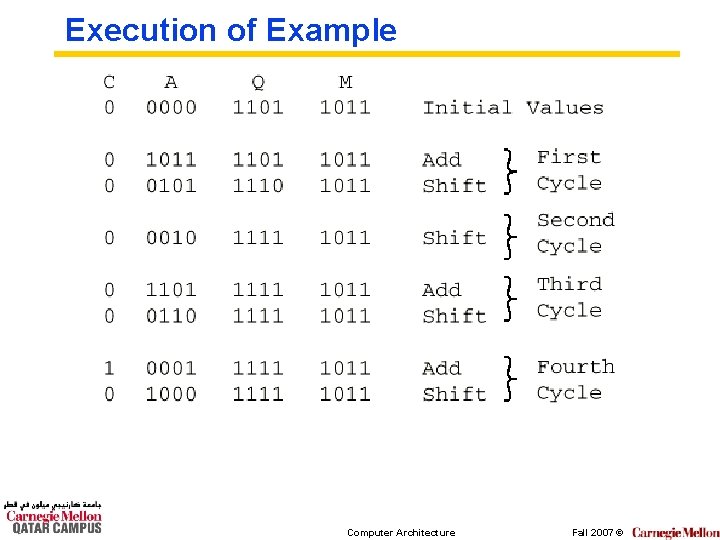

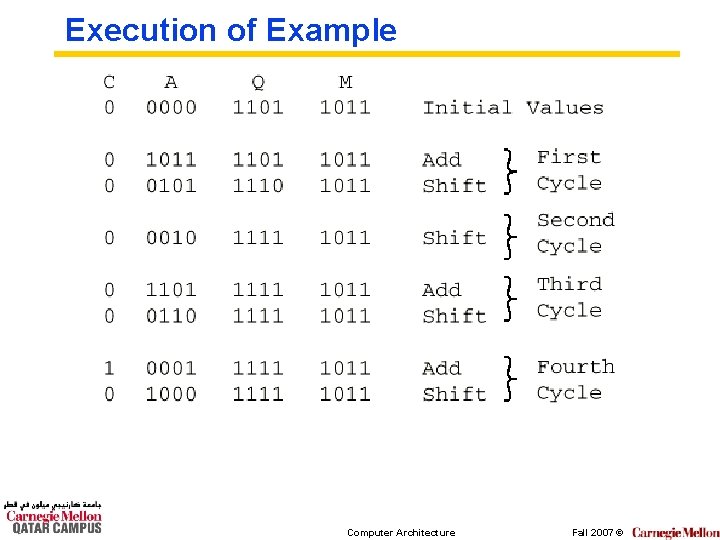

Execution of Example Computer Architecture Fall 2007 ©

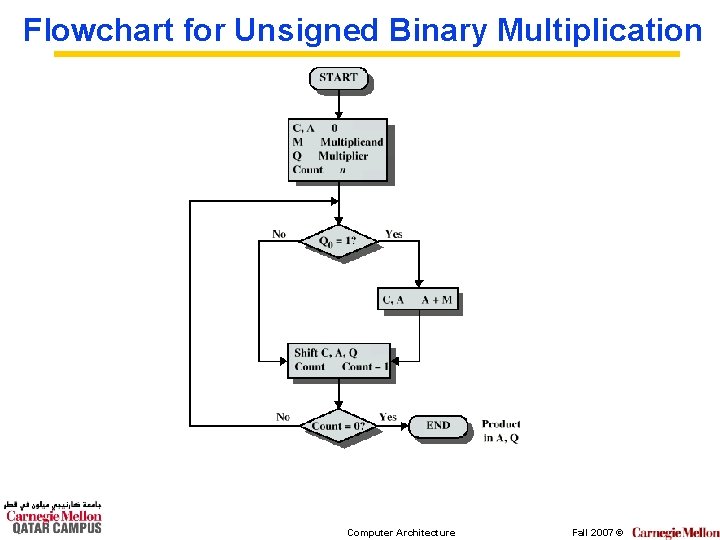

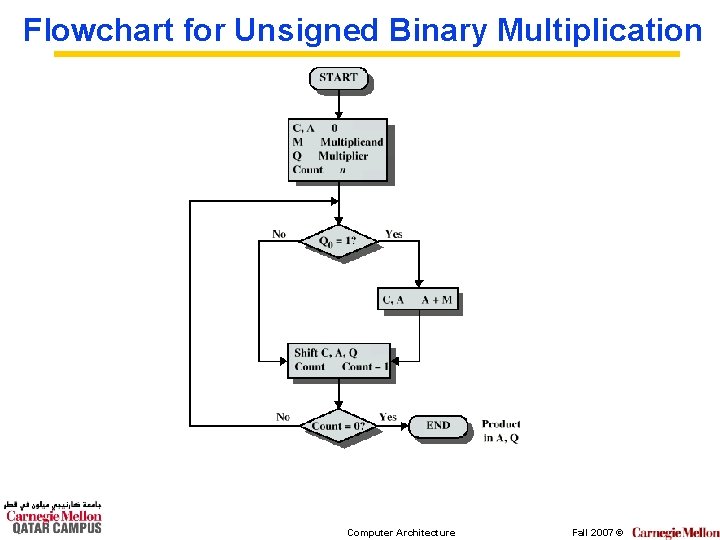

Flowchart for Unsigned Binary Multiplication Computer Architecture Fall 2007 ©

Multiplying Negative Numbers ° This does not work! ° Solution 1 • Convert to positive if required • Multiply as above • If signs were different, negate answer ° Solution 2 • Booth’s algorithm Computer Architecture Fall 2007 ©