Clock Noise in Sampled Data Systems Sampled Data

- Slides: 19

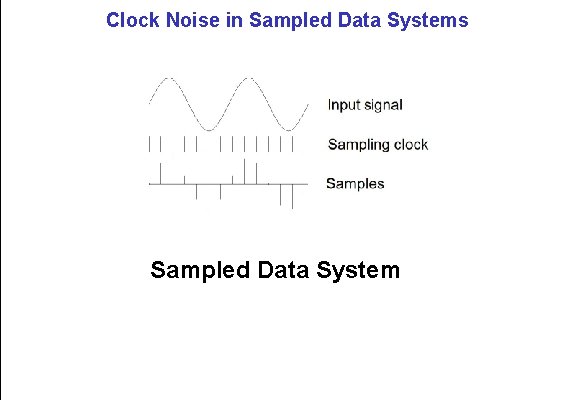

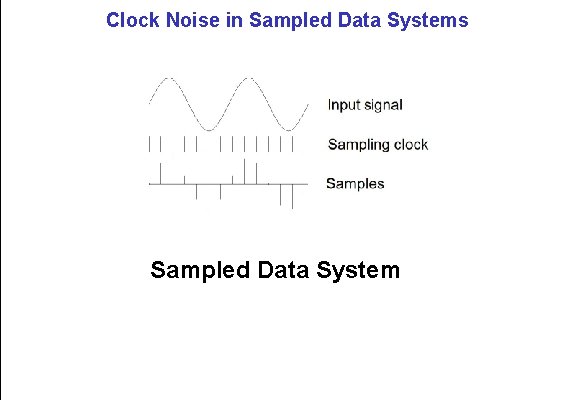

Clock Noise in Sampled Data Systems Sampled Data System

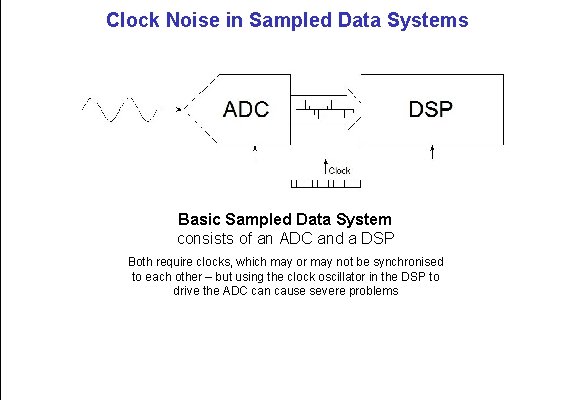

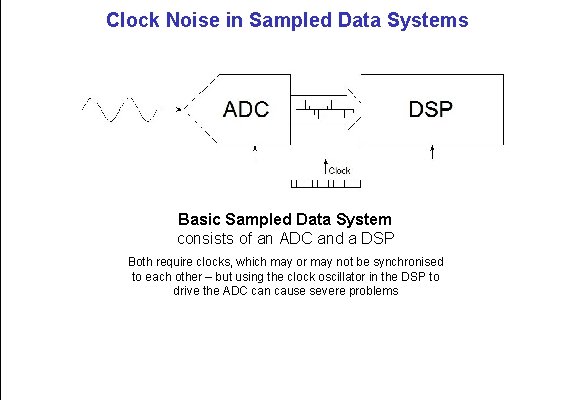

Clock Noise in Sampled Data Systems Basic Sampled Data System consists of an ADC and a DSP Both require clocks, which may or may not be synchronised to each other – but using the clock oscillator in the DSP to drive the ADC can cause severe problems

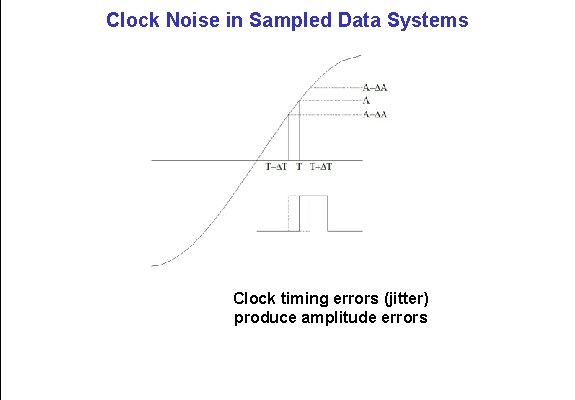

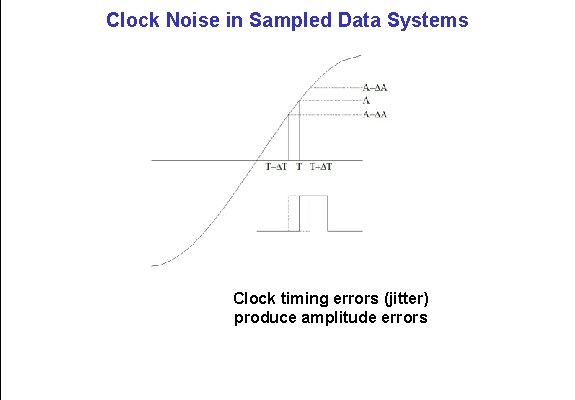

Clock Noise in Sampled Data Systems Clock timing errors (jitter) produce amplitude errors

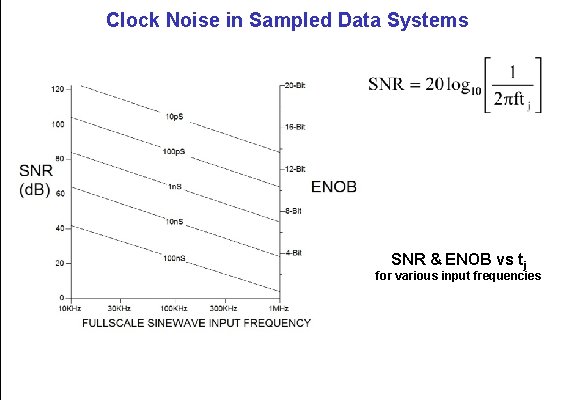

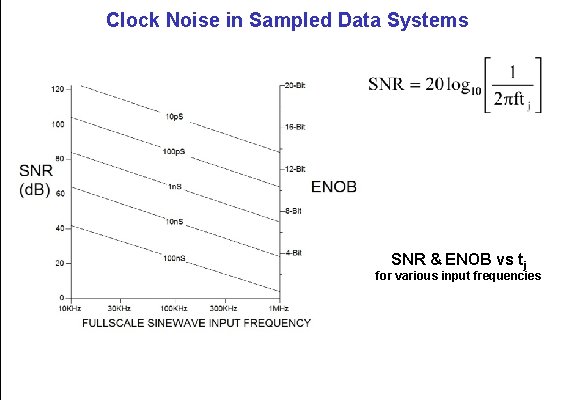

Clock Noise in Sampled Data Systems SNR & ENOB vs tj for various input frequencies

Clock Noise in Sampled Data Systems SOURCES OF JITTER Jitter in the converter and its SHA The sampling clock generator itself The signal route from the clock to the converter(s)

Clock Noise in Sampled Data Systems SOURCES OF JITTER Jitter in the converter and its SHA The sampling clock generator itself The signal route from the clock to the converter(s) Twenty years ago one of the most important specifications of a sample and hold circuit (SHA) was its jitter, today, although jitter is still as important as ever, the circuitry used in SHAs and converters has improved so much that circuit jitter is rarely a problem, although jitter due to power supply noise can still occur when decoupling is inadequate You should still check the data sheet carefully for this specification!

Clock Noise in Sampled Data Systems SOURCES OF JITTER Jitter in the converter and its SHA The sampling clock generator itself The signal route from the clock to the converter(s) There are two types of clock generator with poor phase noise: Oscillator circuits which are intrinsically noisy Low-noise oscillators which have been affected by interference

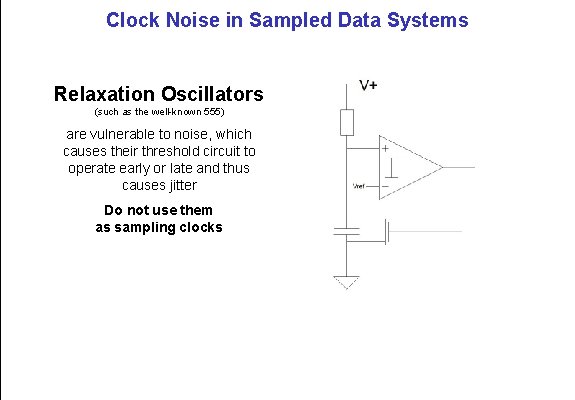

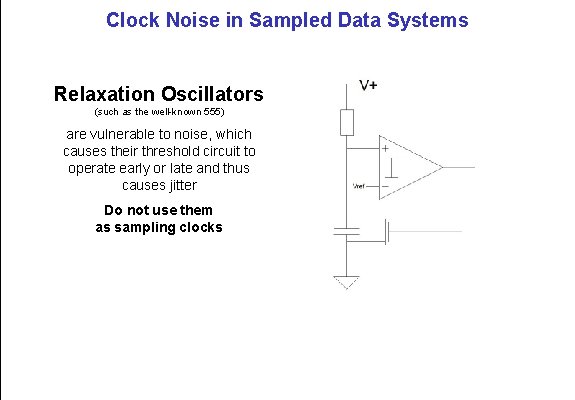

Clock Noise in Sampled Data Systems Relaxation Oscillators (such as the well-known 555) are vulnerable to noise, which causes their threshold circuit to operate early or late and thus causes jitter Do not use them as sampling clocks

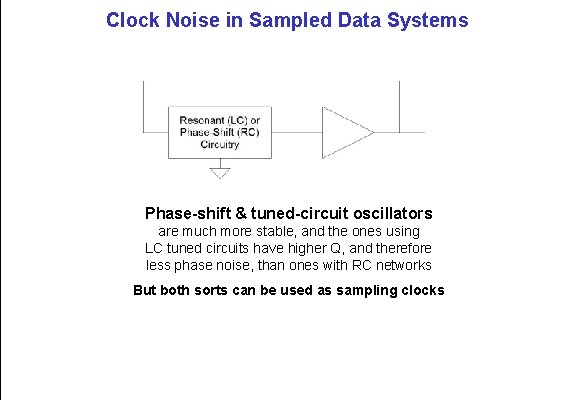

Clock Noise in Sampled Data Systems Phase-shift & tuned-circuit oscillators are much more stable, and the ones using LC tuned circuits have higher Q, and therefore less phase noise, than ones with RC networks But both sorts can be used as sampling clocks

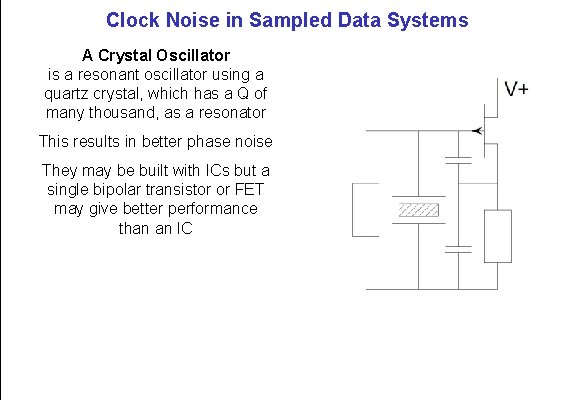

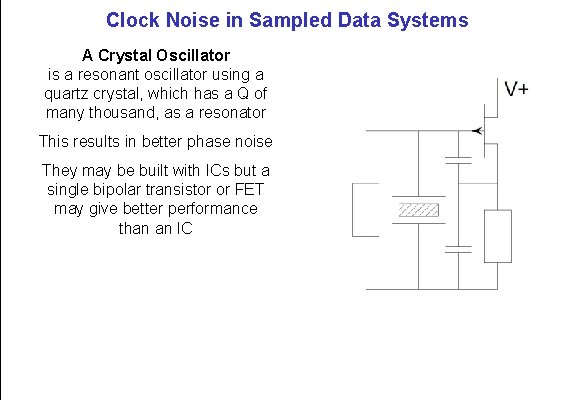

Clock Noise in Sampled Data Systems A Crystal Oscillator is a resonant oscillator using a quartz crystal, which has a Q of many thousand, as a resonator This results in better phase noise They may be built with ICs but a single bipolar transistor or FET may give better performance than an IC

Clock Noise in Sampled Data Systems A Crystal Oscillator built with logic gates is not nearly such a good oscillator as a purpose-built one Especially if other gates on the same chip are handling high-speed digital signals which are not synchronous with the oscillator – cross-talk in such a case can cause very bad phase noise

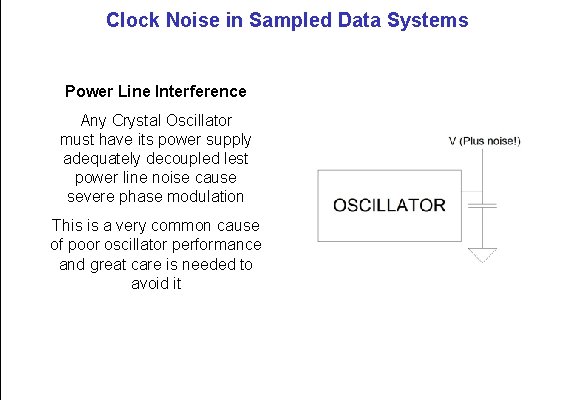

Clock Noise in Sampled Data Systems Power Line Interference Any Crystal Oscillator must have its power supply adequately decoupled lest power line noise cause severe phase modulation This is a very common cause of poor oscillator performance and great care is needed to avoid it

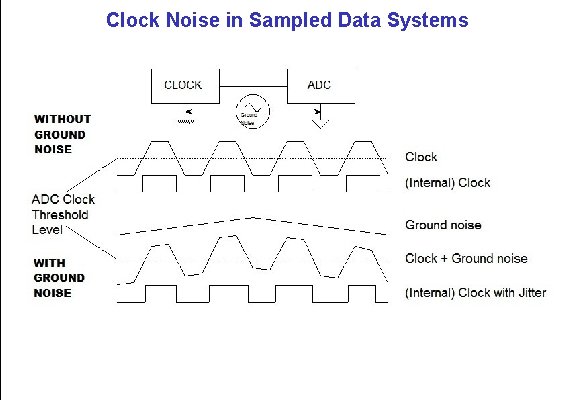

Clock Noise in Sampled Data Systems SOURCES OF JITTER Jitter in the converter and its SHA The sampling clock generator itself The signal route from the clock to the converter(s) As the sampling clock goes from the clock oscillator to the ADC/SHA it can be affected by two noise sources: Cross-talk from other digital lines Common-mode noise between analog and digital ground

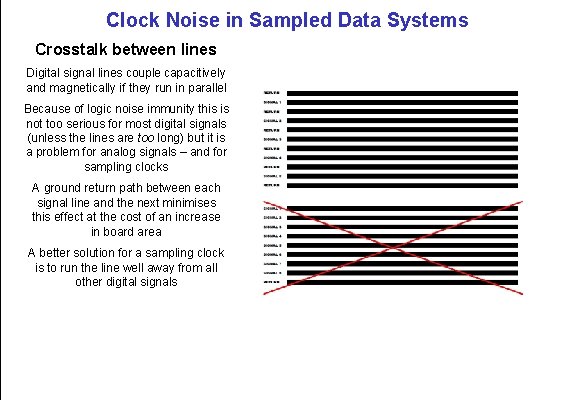

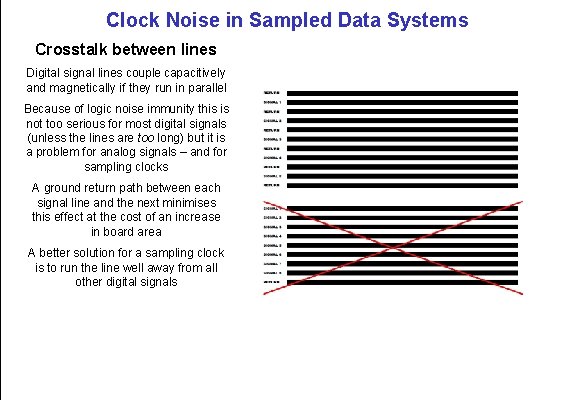

Clock Noise in Sampled Data Systems Crosstalk between lines Digital signal lines couple capacitively and magnetically if they run in parallel Because of logic noise immunity this is not too serious for most digital signals (unless the lines are too long) but it is a problem for analog signals – and for sampling clocks A ground return path between each signal line and the next minimises this effect at the cost of an increase in board area A better solution for a sampling clock is to run the line well away from all other digital signals

Clock Noise in Sampled Data Systems

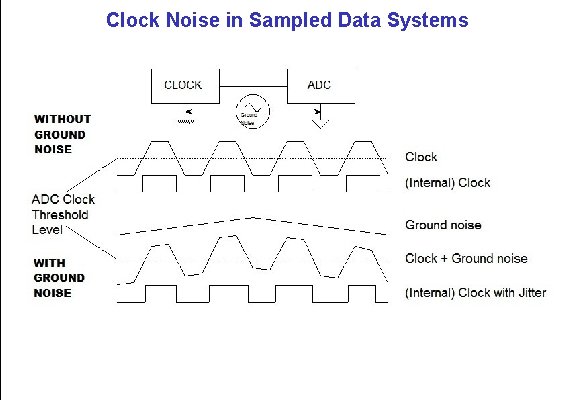

Clock Noise in Sampled Data Systems Ground Noise The best way to eliminate jitter caused by ground noise is to put the sampling clock on the system analog ground

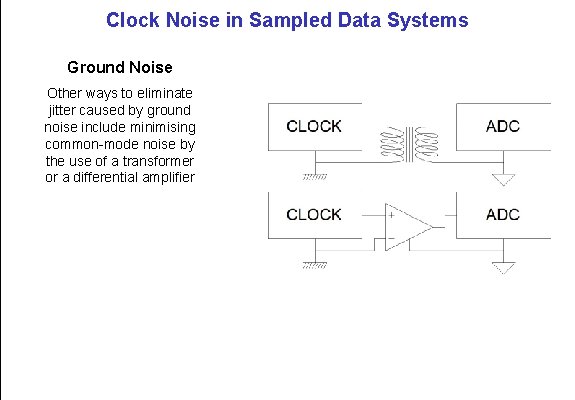

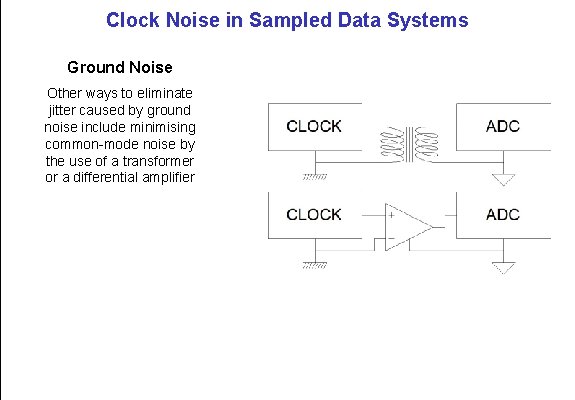

Clock Noise in Sampled Data Systems Ground Noise Other ways to eliminate jitter caused by ground noise include minimising common-mode noise by the use of a transformer or a differential amplifier

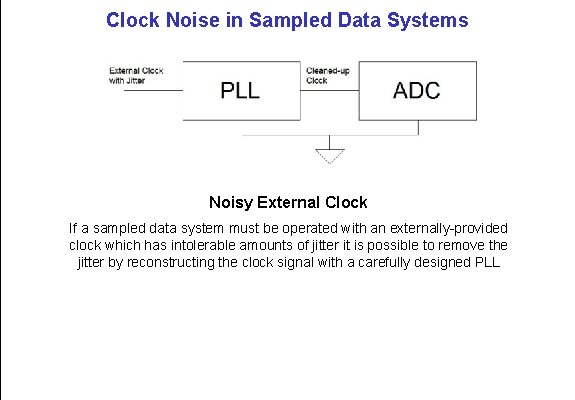

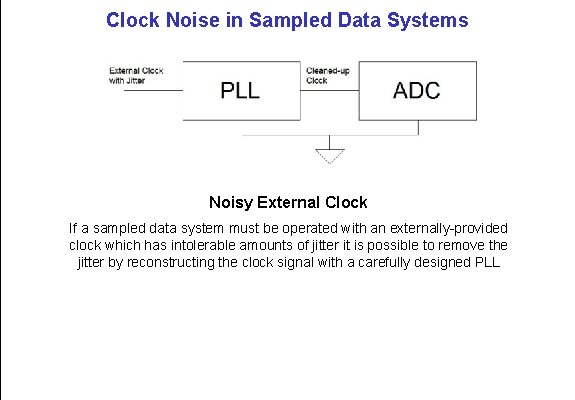

Clock Noise in Sampled Data Systems Noisy External Clock If a sampled data system must be operated with an externally-provided clock which has intolerable amounts of jitter it is possible to remove the jitter by reconstructing the clock signal with a carefully designed PLL

Clock Noise in Sampled Data Systems JITTER KILLS SAMPLED DATA SYSTEM PERFORMANCE BUT IT CAN BE AVOIDED OR CURED