PhaseLocked Loop PLL EE 174 SJSU Tan Nguyen

- Slides: 40

Phase-Locked Loop (PLL) EE 174 – SJSU Tan Nguyen 1

OBJECTIVES • Introduction to Phase-locked loop (PLL) • Historical Background • Basic PLL System • Phase Detector (PD) • Voltage Controlled Oscillator (VCO) • Loop Filter (LF) • PLL Applications 2

Introduction to Phase-locked Loop (PLL) • A Phase-Locked Loop (PLL) is a negative feedback system consists of a phase detector, a low pass filter and a voltage controlled oscillator (VCO) within its loop. Its purpose is to synchronize an output signal with a reference or input signal in frequency as well as in phase. • In the synchronized or “locked” state, the phase error between the oscillator’s output signal and the reference signal is zero, or it remains constant. • If a phase error builds up, a control mechanism acts on the oscillator to reduce the phase error to a minimum so that the phase of the output signal is actually locked to the phase of the reference signal. This is why it is called a PLL. • The majority of PLL applications fall into four main categories: • Frequency synthesis (Most widely used so PLL is also referred as frequency synthesizer). • Frequency (FM) and phase (PM) modulation and demodulation. • Data and carrier recovery. • Tracking filters. • Classification of PLLs: Analog or Linear PLL (LPLL), Digital PLL (DPLL) is Analog PLL with digital phase detector, All-Digital PLL (ADPLL) is a digital loop in two senses: all digital components and all digital (discrete-time) signals. 3

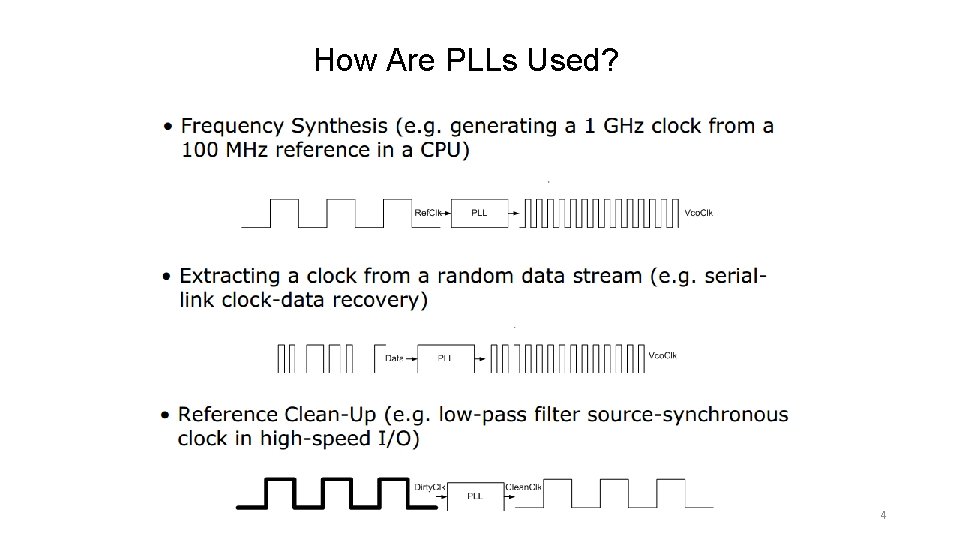

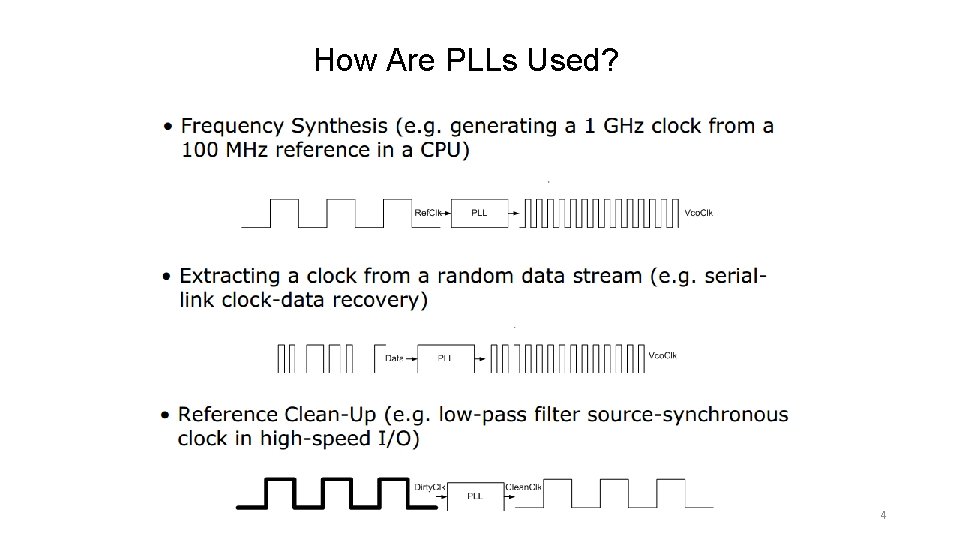

How Are PLLs Used? 4

Brief Phase-Locked Loop (PLL) History § 1932: Invention of “coherent communication” using vacuum tube, (de. Bellescize) § 1943: Horizontal and vertical sweep synchronization in television (Wendt and Faraday) § 1954: Color television (Richman) § 1965: PLL on integrated circuit § 1970: Classical digital PLL § 1972: All-digital PLL §PLLs today: in every cell phone, TV, radio, pager, computer, … §Clock and Data Recovery §Frequency Synthesis §Clock Generation §Clock-skew minimization §Duty-cycle enhancement 1. people. ee. duke. edu/~mbrooke/defense/Borte. ppt 5

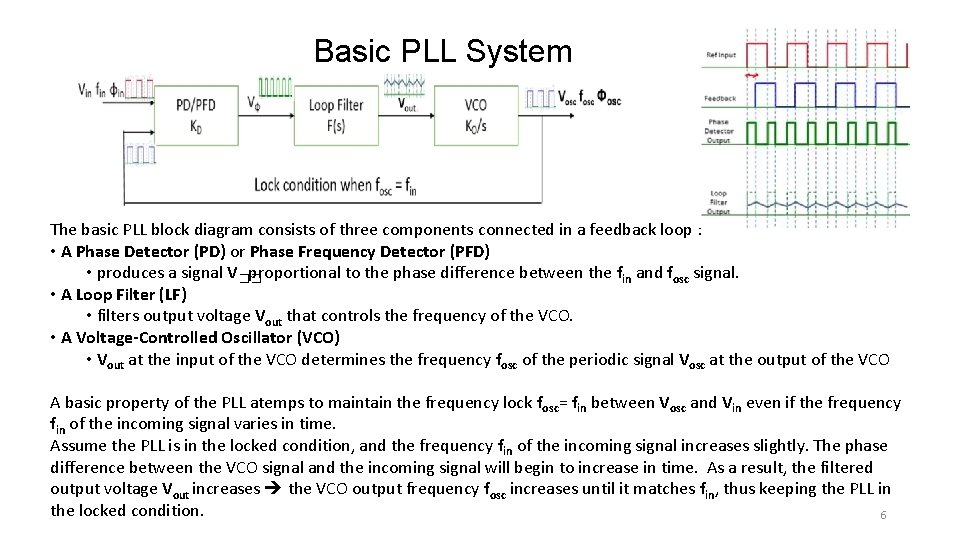

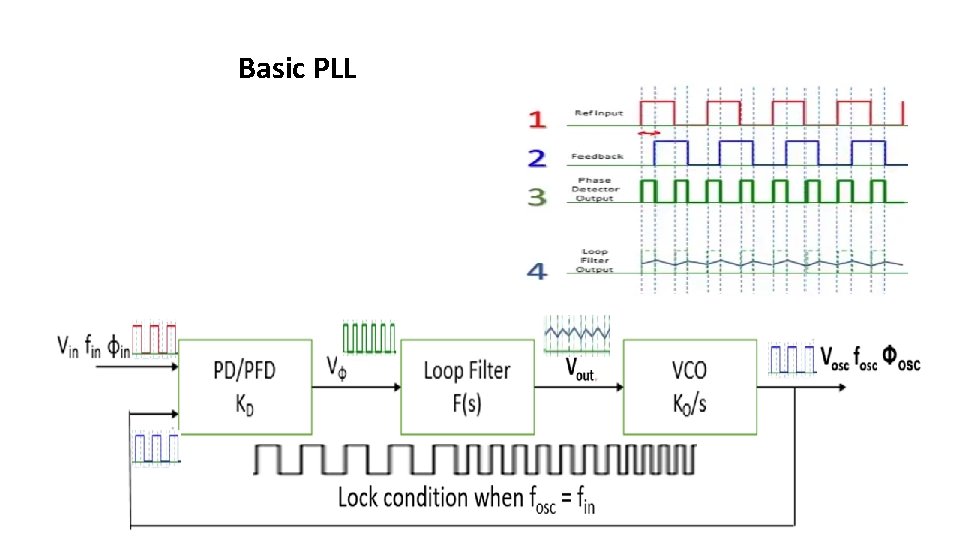

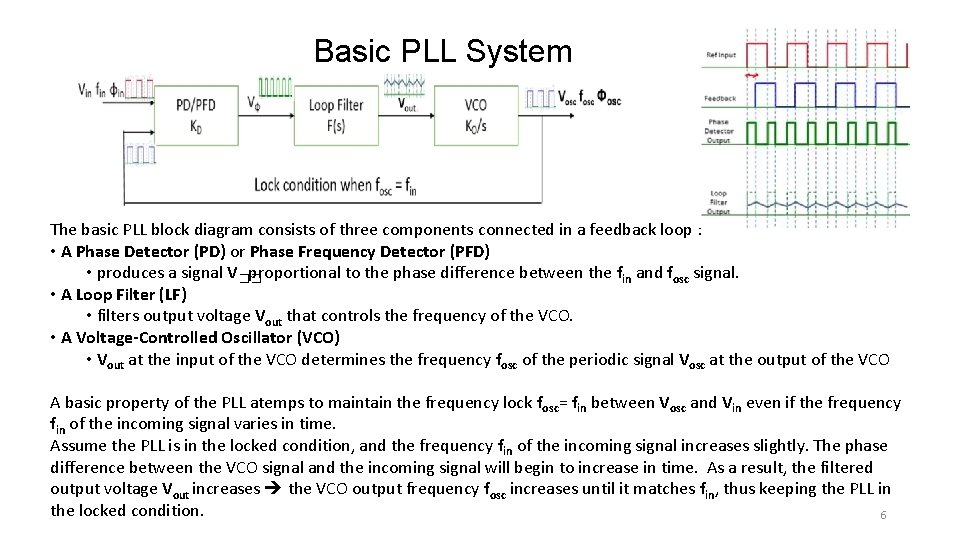

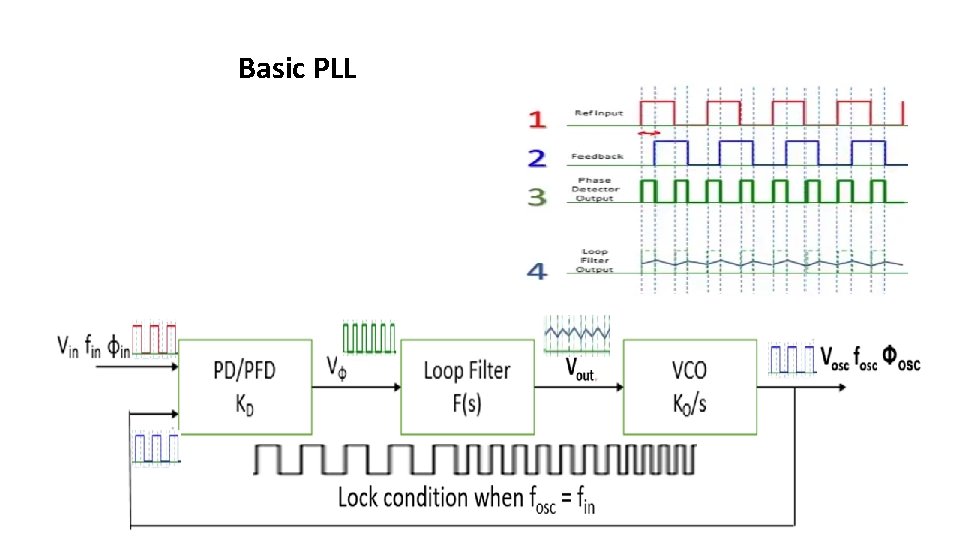

Basic PLL System The basic PLL block diagram consists of three components connected in a feedback loop : • A Phase Detector (PD) or Phase Frequency Detector (PFD) • produces a signal V�� proportional to the phase difference between the fin and fosc signal. • A Loop Filter (LF) • filters output voltage Vout that controls the frequency of the VCO. • A Voltage-Controlled Oscillator (VCO) • Vout at the input of the VCO determines the frequency fosc of the periodic signal Vosc at the output of the VCO A basic property of the PLL atemps to maintain the frequency lock fosc= fin between Vosc and Vin even if the frequency fin of the incoming signal varies in time. Assume the PLL is in the locked condition, and the frequency fin of the incoming signal increases slightly. The phase difference between the VCO signal and the incoming signal will begin to increase in time. As a result, the filtered output voltage Vout increases the VCO output frequency fosc increases until it matches fin, thus keeping the PLL in the locked condition. 6

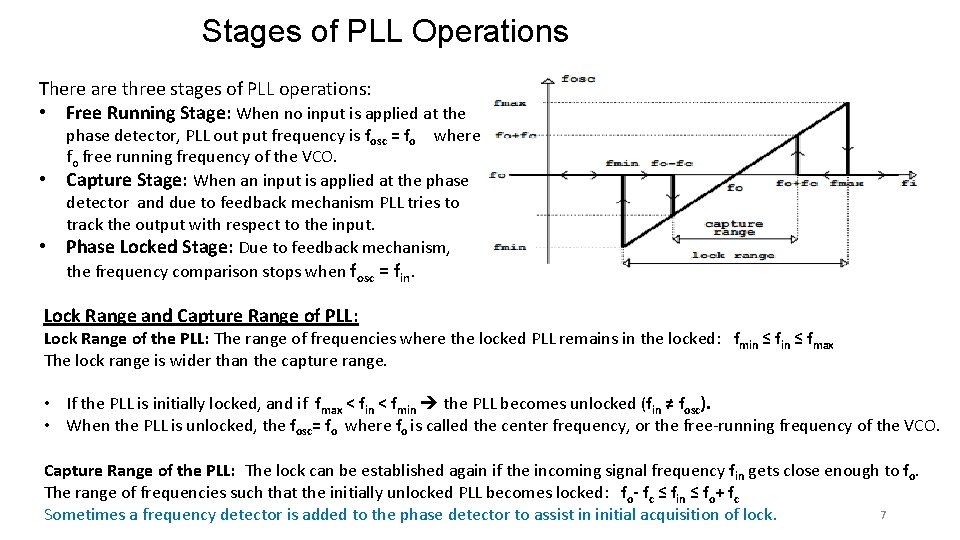

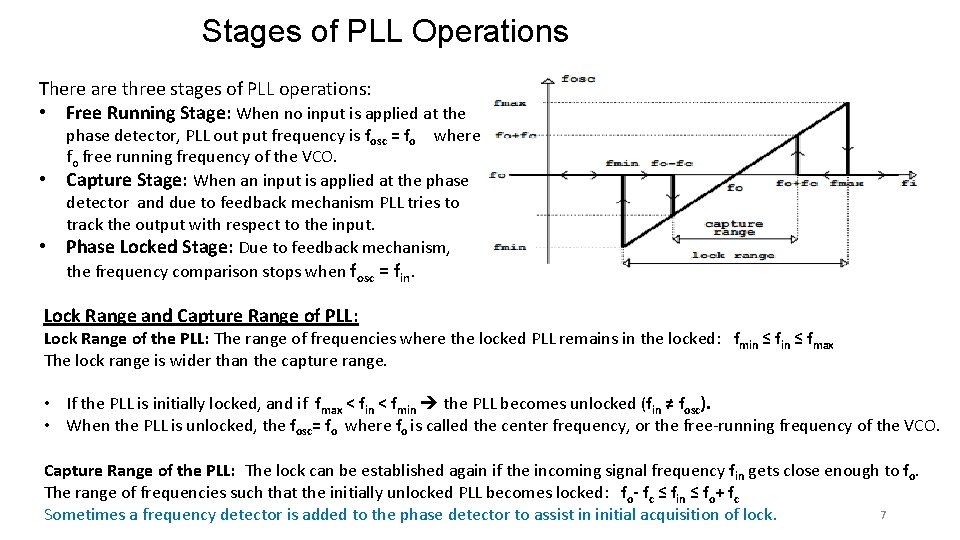

Stages of PLL Operations There are three stages of PLL operations: • Free Running Stage: When no input is applied at the • • phase detector, PLL out put frequency is fosc = fo where fo free running frequency of the VCO. Capture Stage: When an input is applied at the phase detector and due to feedback mechanism PLL tries to track the output with respect to the input. Phase Locked Stage: Due to feedback mechanism, the frequency comparison stops when fosc = fin. Lock Range and Capture Range of PLL: Lock Range of the PLL: The range of frequencies where the locked PLL remains in the locked: fmin ≤ fmax The lock range is wider than the capture range. • If the PLL is initially locked, and if fmax < fin < fmin the PLL becomes unlocked (fin ≠ fosc). • When the PLL is unlocked, the fosc= fo where fo is called the center frequency, or the free-running frequency of the VCO. Capture Range of the PLL: The lock can be established again if the incoming signal frequency fin gets close enough to fo. The range of frequencies such that the initially unlocked PLL becomes locked: fo- fc ≤ fin ≤ fo+ fc 7 Sometimes a frequency detector is added to the phase detector to assist in initial acquisition of lock.

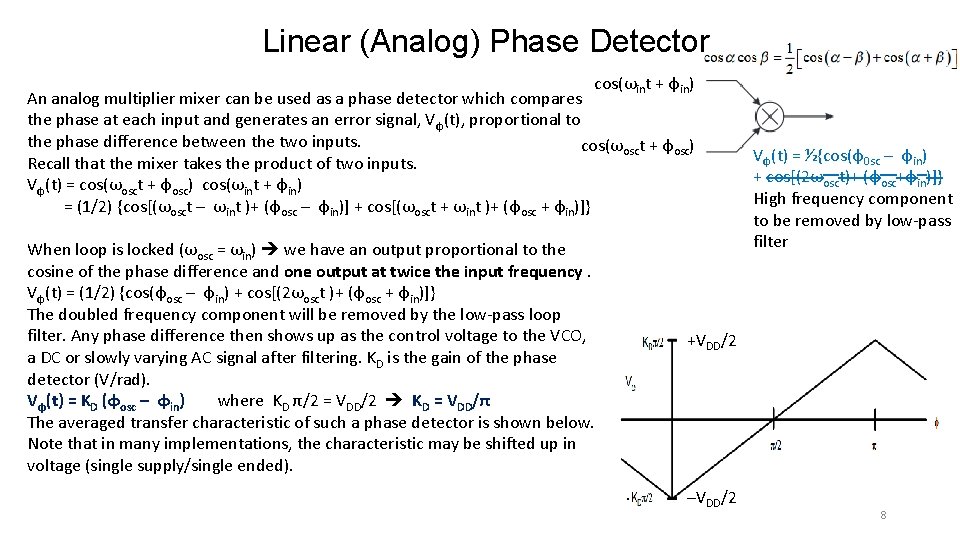

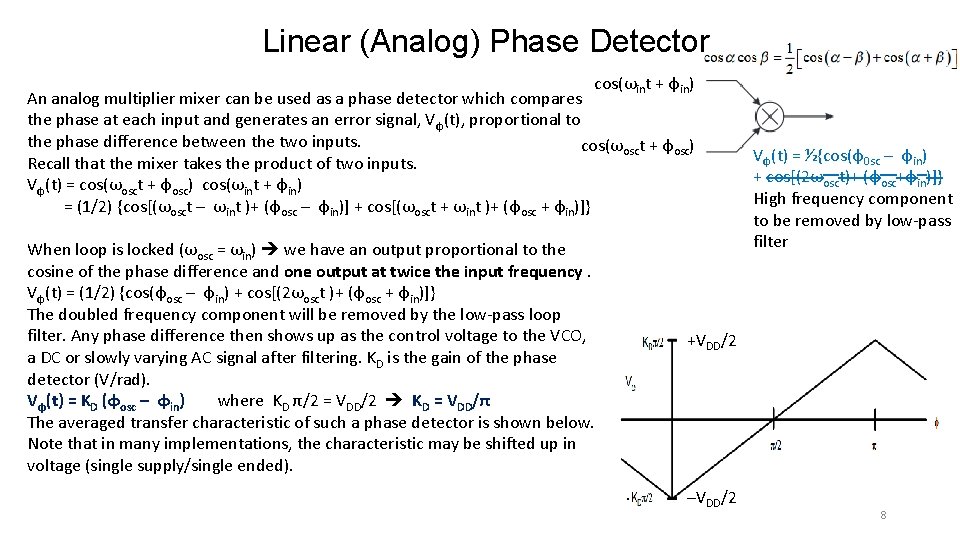

Linear (Analog) Phase Detector cos(ωint + φin) An analog multiplier mixer can be used as a phase detector which compares the phase at each input and generates an error signal, Vφ(t), proportional to the phase difference between the two inputs. cos(ωosct + φosc) Recall that the mixer takes the product of two inputs. Vφ(t) = cos(ωosct + φosc) cos(ωint + φin) = (1/2) {cos[(ωosct – ωint )+ (φosc – φin)] + cos[(ωosct + ωint )+ (φosc + φin)]} When loop is locked (ωosc = ωin) we have an output proportional to the cosine of the phase difference and one output at twice the input frequency. Vφ(t) = (1/2) {cos(φosc – φin) + cos[(2ωosct )+ (φosc + φin)]} The doubled frequency component will be removed by the low-pass loop filter. Any phase difference then shows up as the control voltage to the VCO, a DC or slowly varying AC signal after filtering. KD is the gain of the phase detector (V/rad). Vφ(t) = KD (φosc – φin) where KD π/2 = VDD/2 KD = VDD/π The averaged transfer characteristic of such a phase detector is shown below. Note that in many implementations, the characteristic may be shifted up in voltage (single supply/single ended). Vφ(t) = ½{cos(φ0 sc – φin) + cos[(2ωosct)+ (φosc+φin)]} High frequency component to be removed by low-pass filter +VDD/2 –VDD/2 8

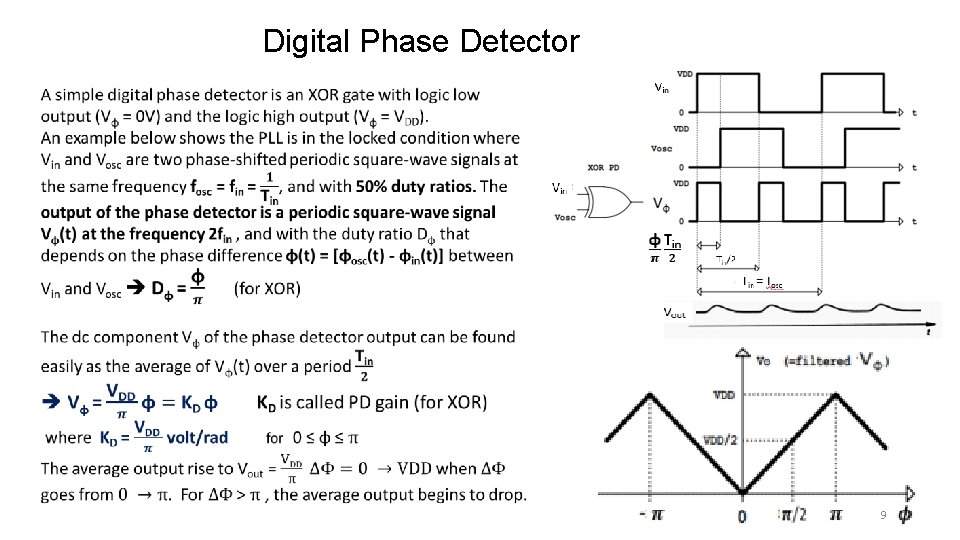

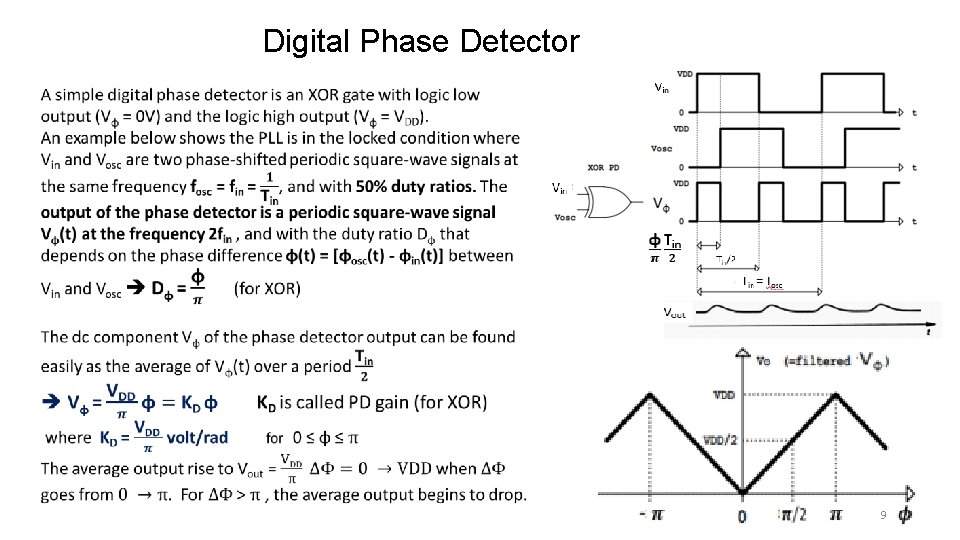

Digital Phase Detector 9

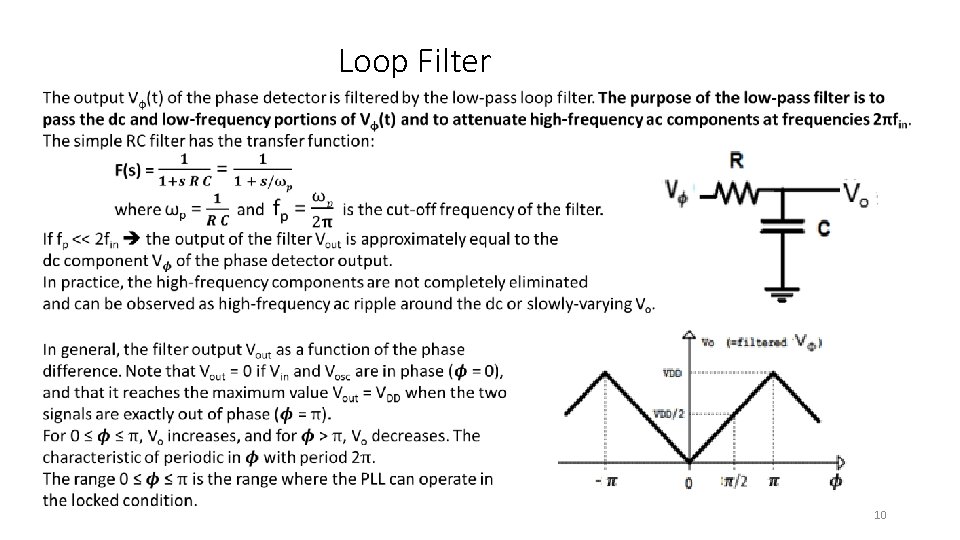

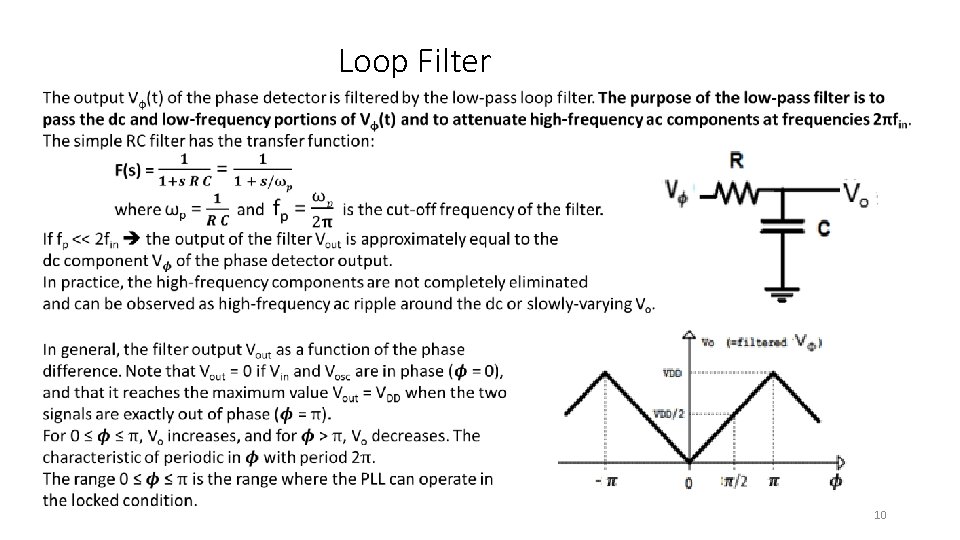

Loop Filter 10

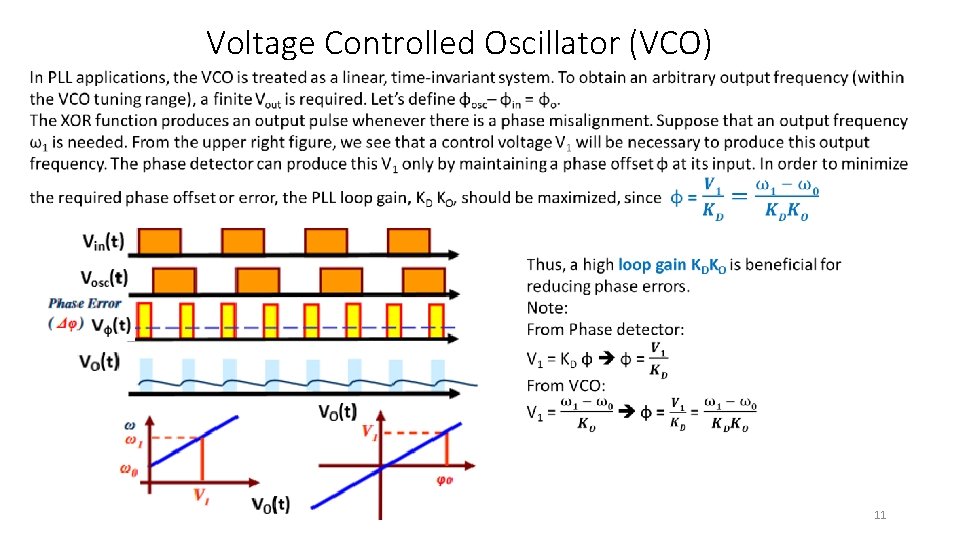

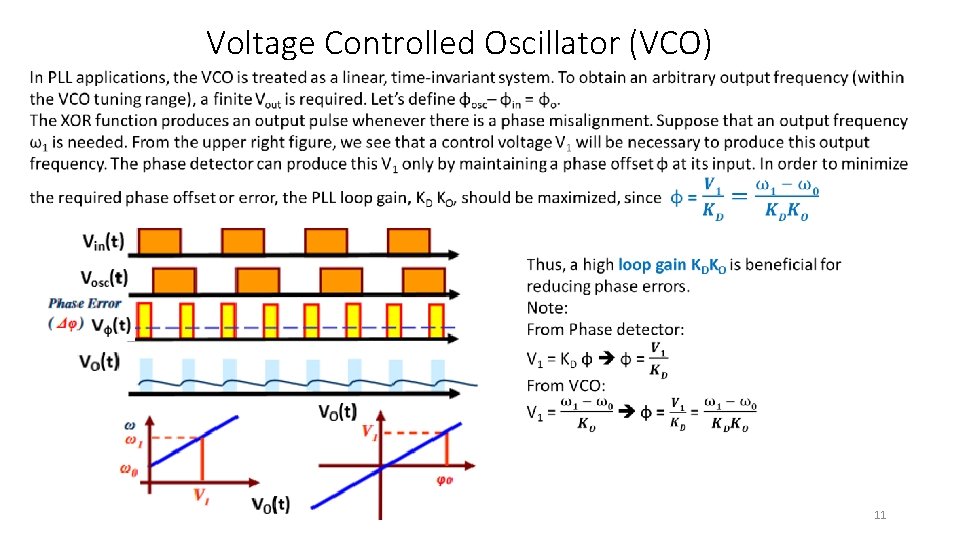

Voltage Controlled Oscillator (VCO) 11

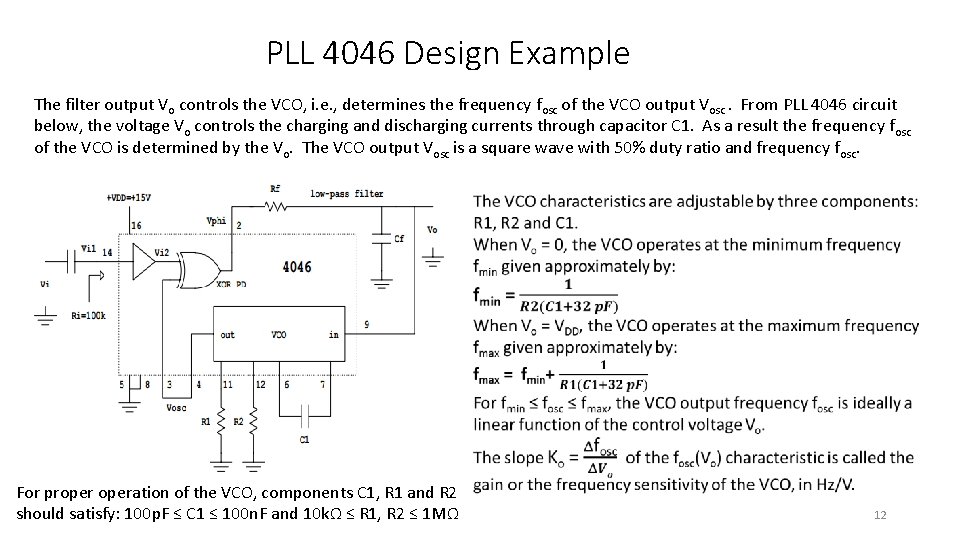

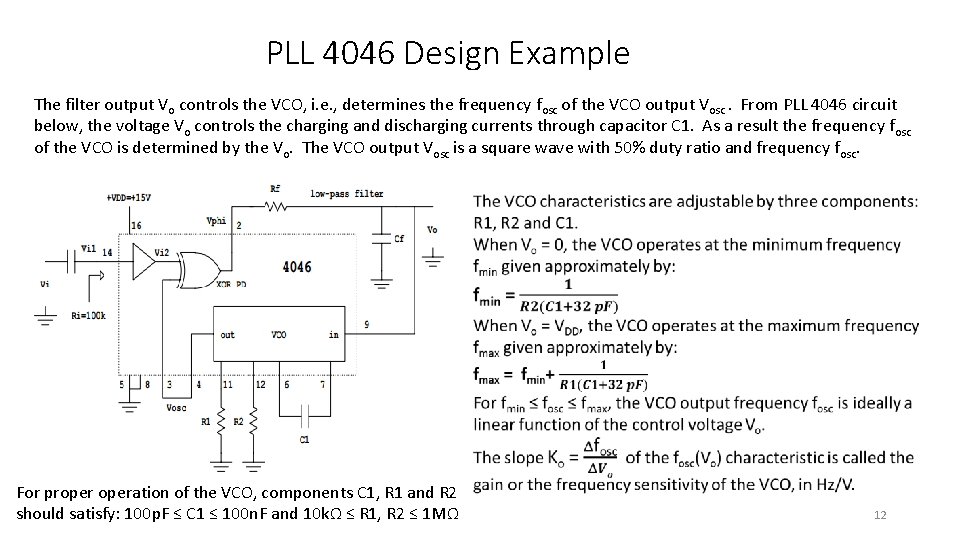

PLL 4046 Design Example The filter output Vo controls the VCO, i. e. , determines the frequency fosc of the VCO output Vosc. From PLL 4046 circuit below, the voltage Vo controls the charging and discharging currents through capacitor C 1. As a result the frequency f osc of the VCO is determined by the Vo. The VCO output Vosc is a square wave with 50% duty ratio and frequency fosc. For properation of the VCO, components C 1, R 1 and R 2 should satisfy: 100 p. F ≤ C 1 ≤ 100 n. F and 10 kΩ ≤ R 1, R 2 ≤ 1 MΩ 12

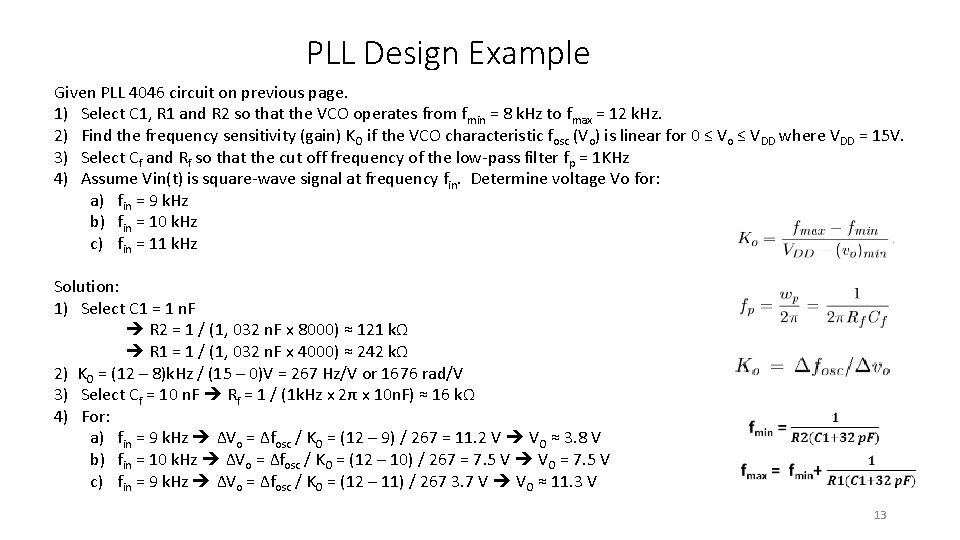

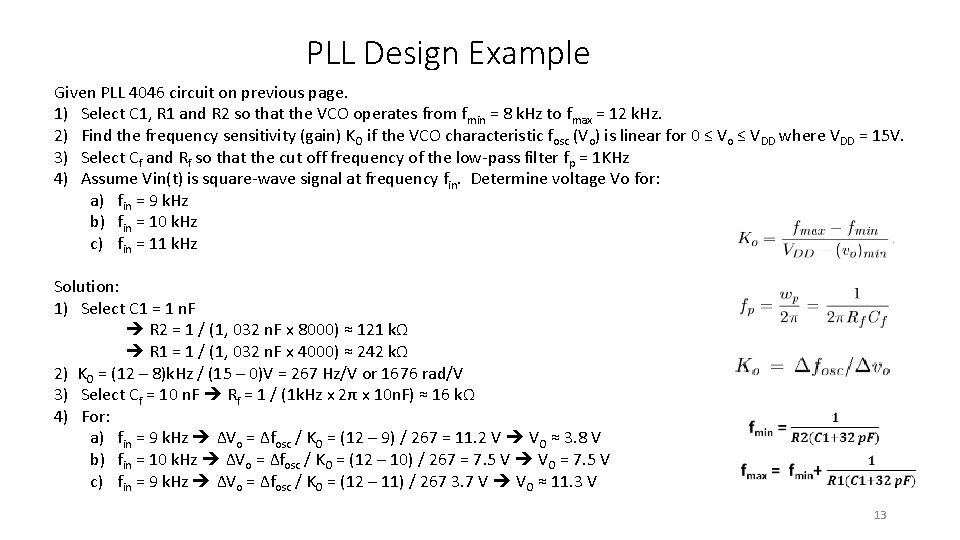

PLL Design Example Given PLL 4046 circuit on previous page. 1) Select C 1, R 1 and R 2 so that the VCO operates from fmin = 8 k. Hz to fmax = 12 k. Hz. 2) Find the frequency sensitivity (gain) KO if the VCO characteristic fosc (Vo) is linear for 0 ≤ Vo ≤ VDD where VDD = 15 V. 3) Select Cf and Rf so that the cut off frequency of the low-pass filter fp = 1 KHz 4) Assume Vin(t) is square-wave signal at frequency fin. Determine voltage Vo for: a) fin = 9 k. Hz b) fin = 10 k. Hz c) fin = 11 k. Hz Solution: 1) Select C 1 = 1 n. F R 2 = 1 / (1, 032 n. F x 8000) ≈ 121 kΩ R 1 = 1 / (1, 032 n. F x 4000) ≈ 242 kΩ 2) KO = (12 – 8)k. Hz / (15 – 0)V = 267 Hz/V or 1676 rad/V 3) Select Cf = 10 n. F Rf = 1 / (1 k. Hz x 2π x 10 n. F) ≈ 16 kΩ 4) For: a) fin = 9 k. Hz ΔVo = Δfosc / KO = (12 – 9) / 267 = 11. 2 V VO ≈ 3. 8 V b) fin = 10 k. Hz ΔVo = Δfosc / KO = (12 – 10) / 267 = 7. 5 V VO = 7. 5 V c) fin = 9 k. Hz ΔVo = Δfosc / KO = (12 – 11) / 267 3. 7 V VO ≈ 11. 3 V 13

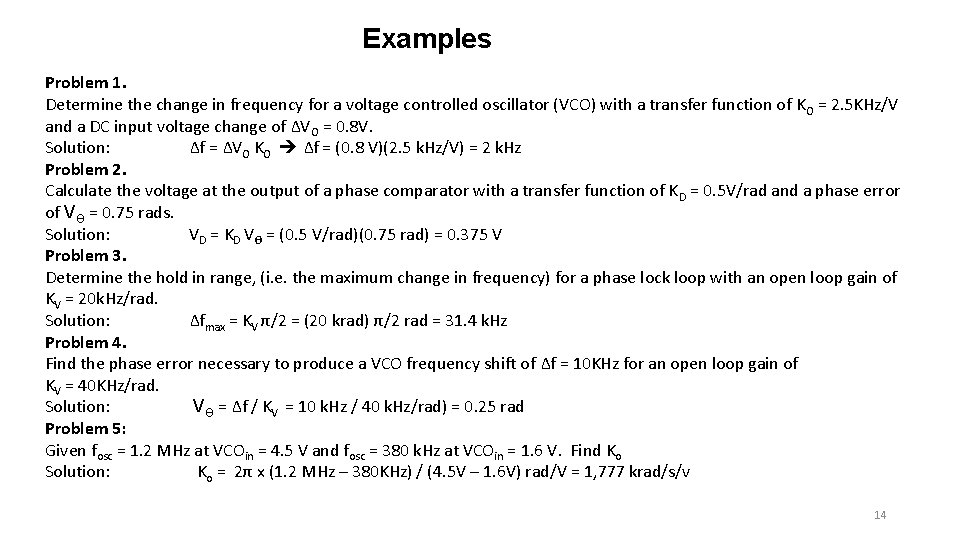

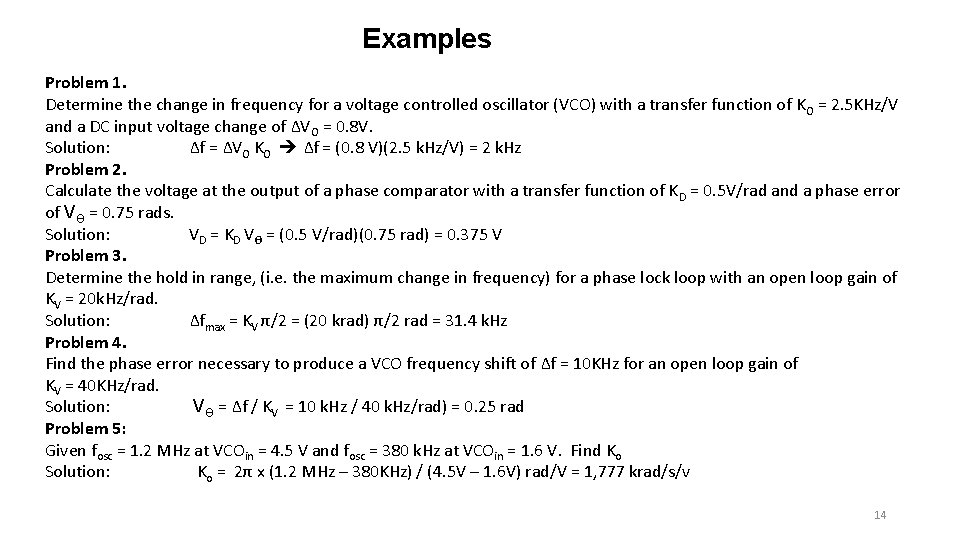

Examples Problem 1. Determine the change in frequency for a voltage controlled oscillator (VCO) with a transfer function of K O = 2. 5 KHz/V and a DC input voltage change of ΔVO = 0. 8 V. Solution: Δf = ΔVO KO Δf = (0. 8 V)(2. 5 k. Hz/V) = 2 k. Hz Problem 2. Calculate the voltage at the output of a phase comparator with a transfer function of K D = 0. 5 V/rad and a phase error of Vϴ = 0. 75 rads. Solution: VD = KD Vϴ = (0. 5 V/rad)(0. 75 rad) = 0. 375 V Problem 3. Determine the hold in range, (i. e. the maximum change in frequency) for a phase lock loop with an open loop gain of KV = 20 k. Hz/rad. Solution: Δfmax = KV π/2 = (20 krad) π/2 rad = 31. 4 k. Hz Problem 4. Find the phase error necessary to produce a VCO frequency shift of Δf = 10 KHz for an open loop gain of KV = 40 KHz/rad. Solution: Vϴ = Δf / KV = 10 k. Hz / 40 k. Hz/rad) = 0. 25 rad Problem 5: Given fosc = 1. 2 MHz at VCOin = 4. 5 V and fosc = 380 k. Hz at VCOin = 1. 6 V. Find Ko Solution: Ko = 2π x (1. 2 MHz – 380 KHz) / (4. 5 V – 1. 6 V) rad/V = 1, 777 krad/s/v 14

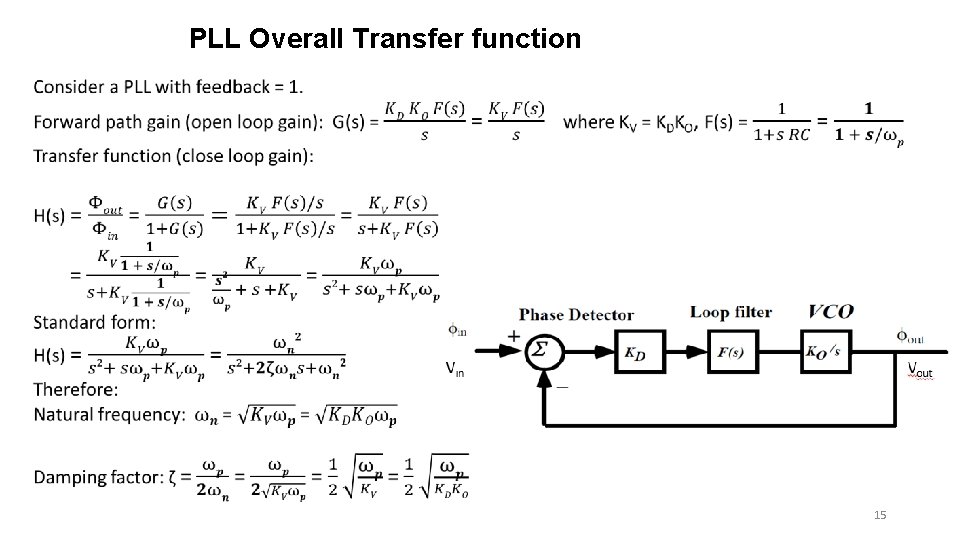

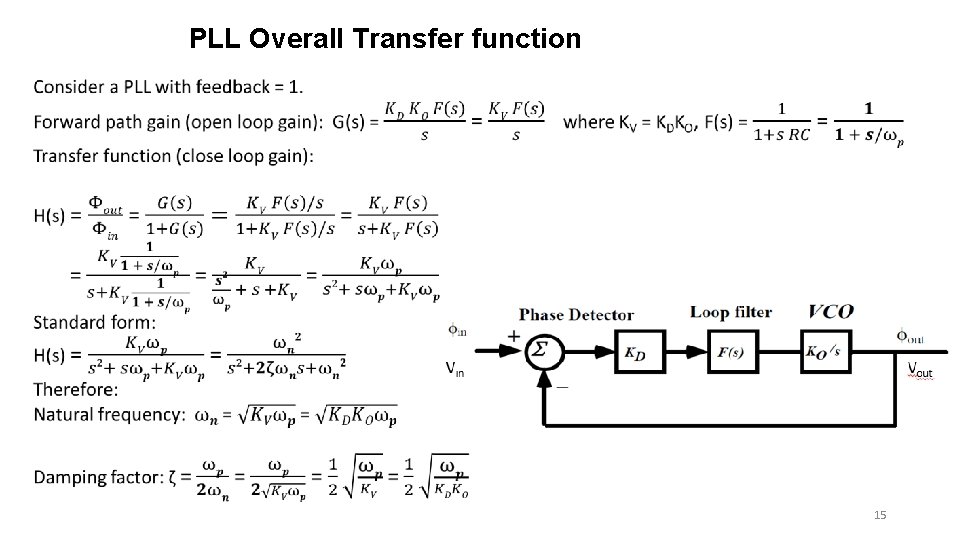

PLL Overall Transfer function 15

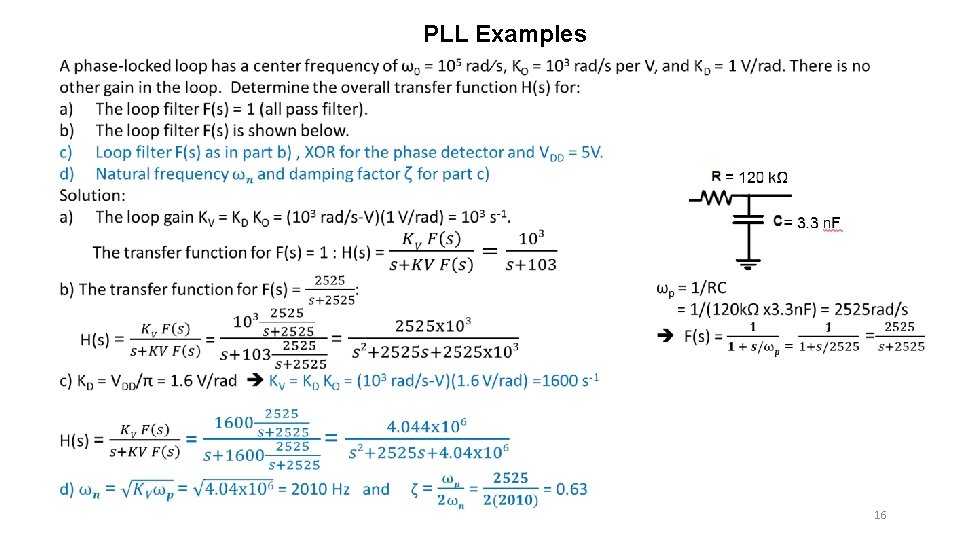

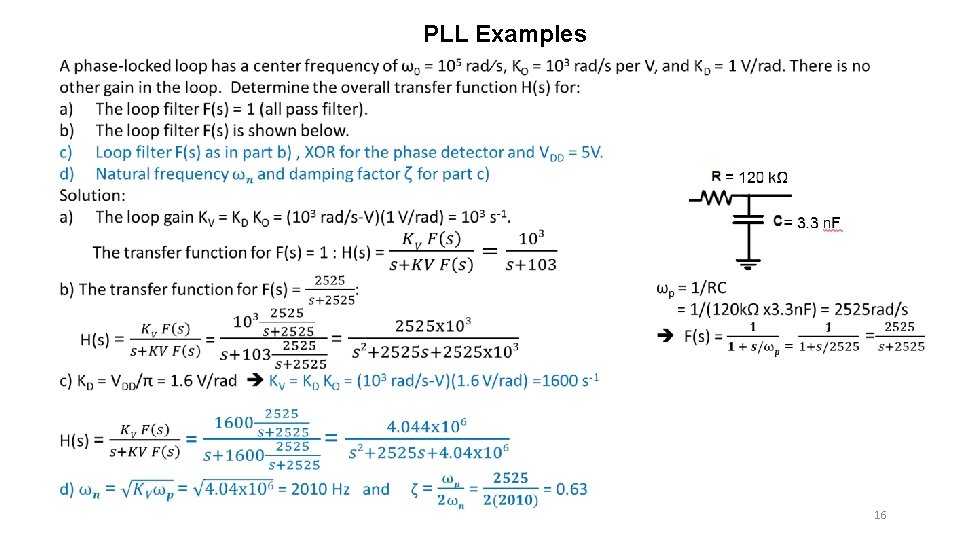

PLL Examples 16

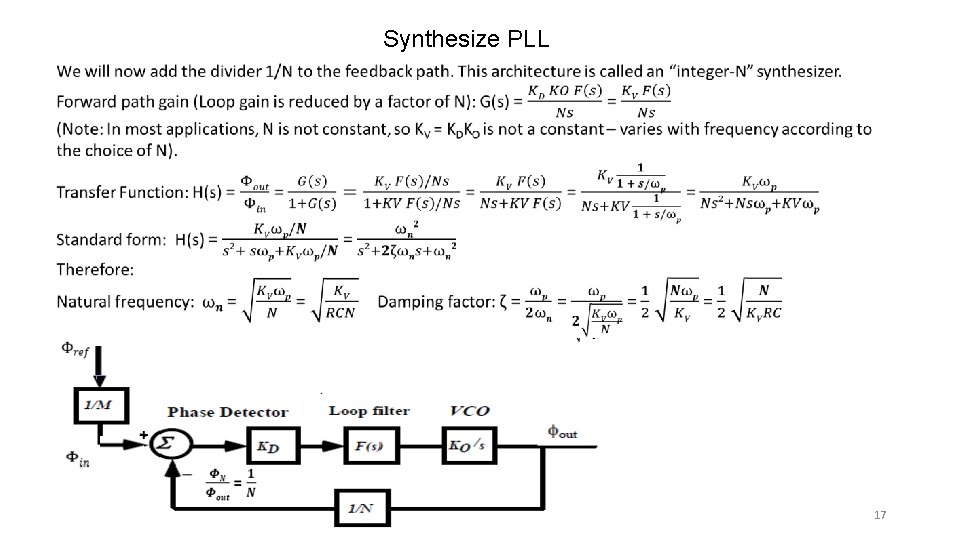

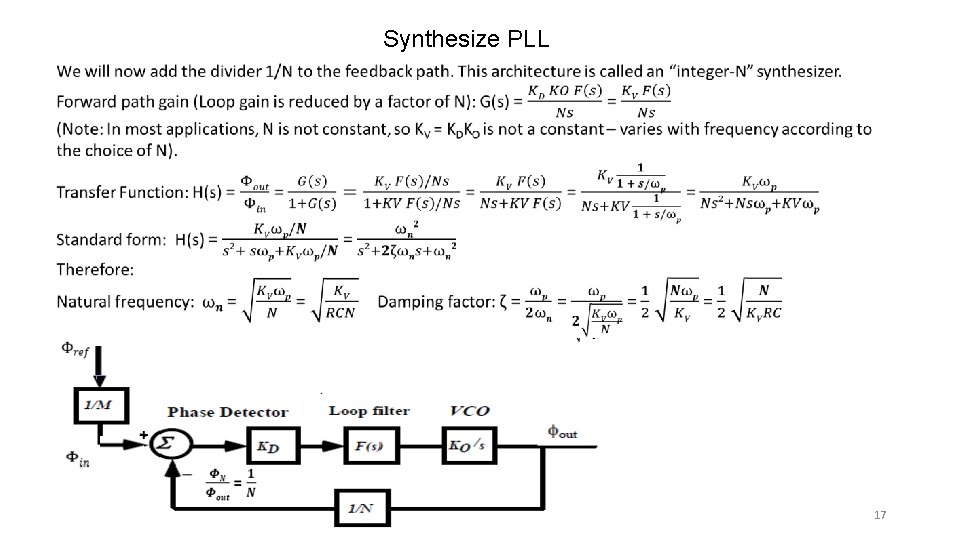

Synthesize PLL 17

Phase Lock Loop Applications EE 174 – SJSU Tan Nguyen

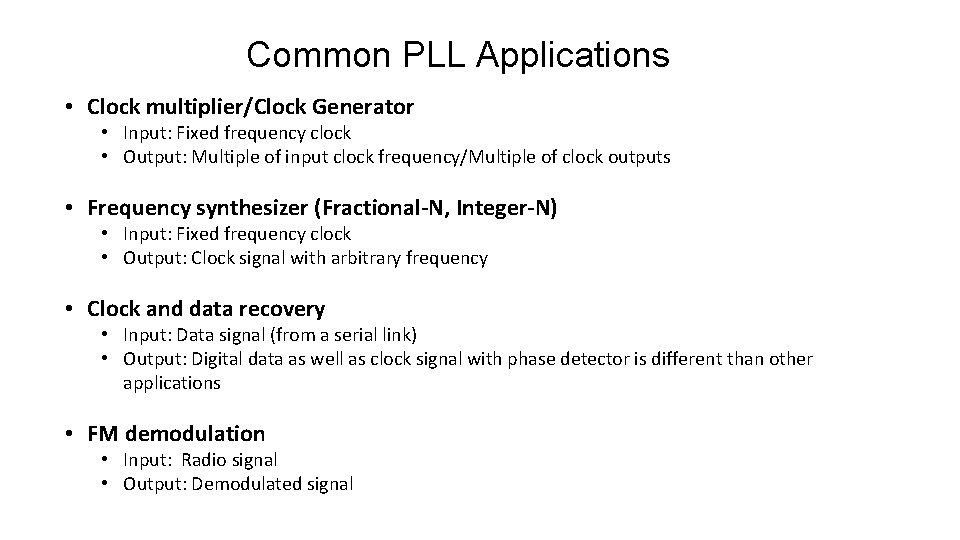

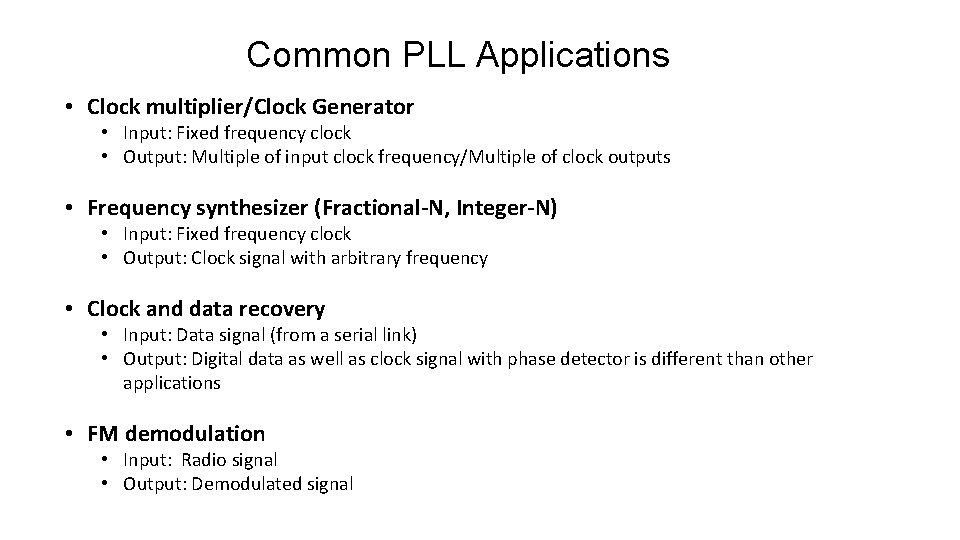

Common PLL Applications • Clock multiplier/Clock Generator • Input: Fixed frequency clock • Output: Multiple of input clock frequency/Multiple of clock outputs • Frequency synthesizer (Fractional-N, Integer-N) • Input: Fixed frequency clock • Output: Clock signal with arbitrary frequency • Clock and data recovery • Input: Data signal (from a serial link) • Output: Digital data as well as clock signal with phase detector is different than other applications • FM demodulation • Input: Radio signal • Output: Demodulated signal

Basic PLL

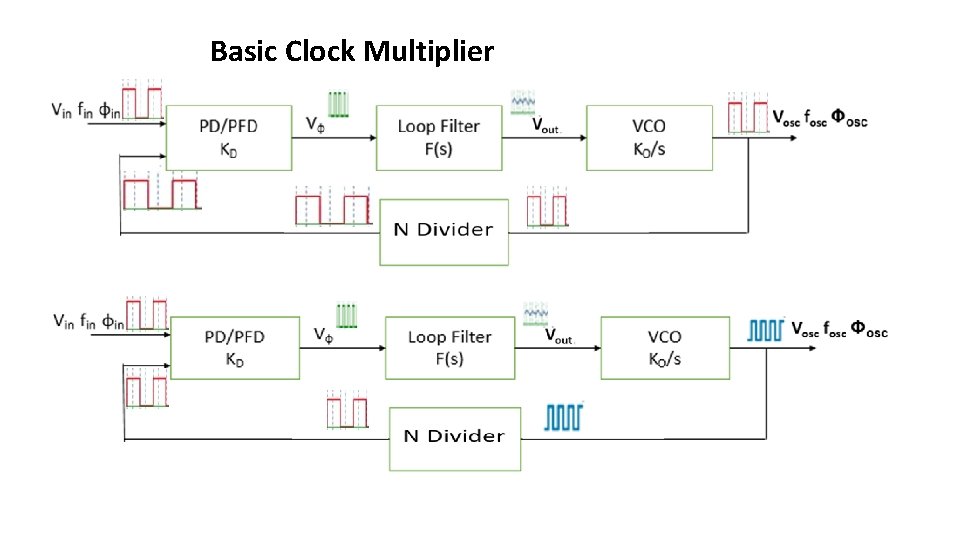

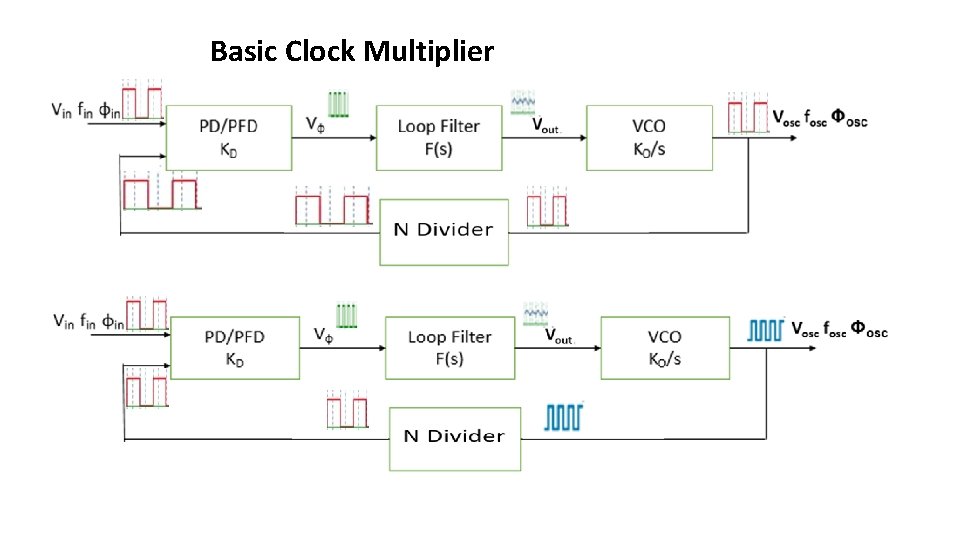

Basic Clock Multiplier

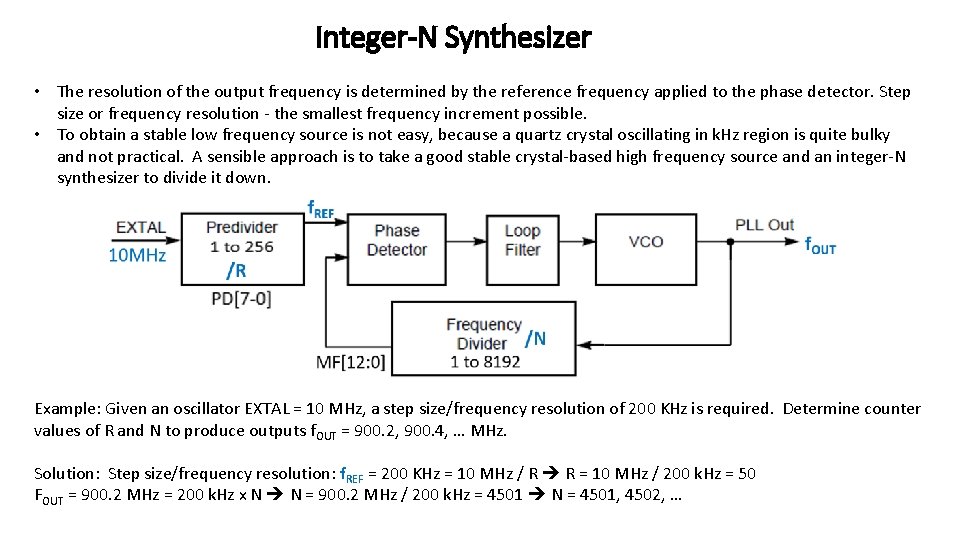

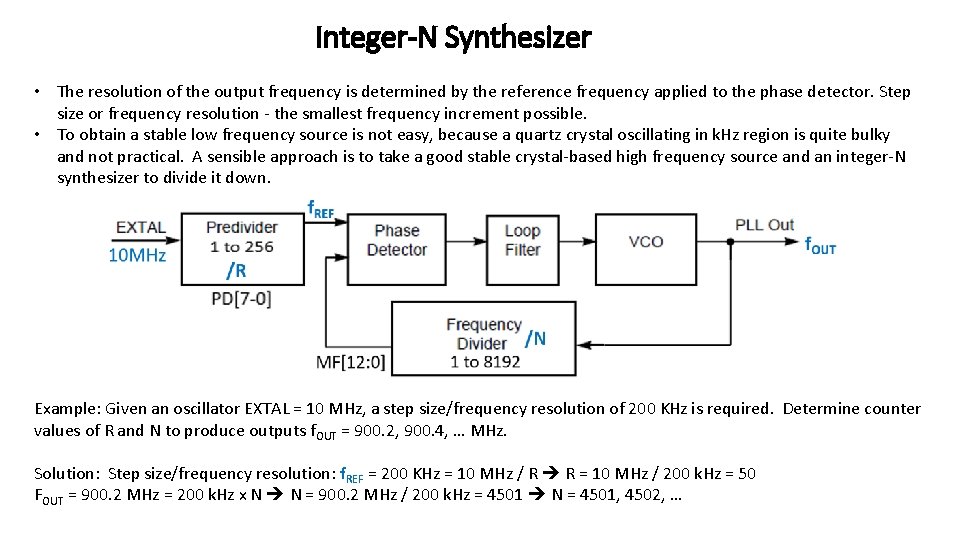

Integer-N Synthesizer • The resolution of the output frequency is determined by the reference frequency applied to the phase detector. Step size or frequency resolution - the smallest frequency increment possible. • To obtain a stable low frequency source is not easy, because a quartz crystal oscillating in k. Hz region is quite bulky and not practical. A sensible approach is to take a good stable crystal-based high frequency source and an integer-N synthesizer to divide it down. Example: Given an oscillator EXTAL = 10 MHz, a step size/frequency resolution of 200 KHz is required. Determine counter values of R and N to produce outputs f. OUT = 900. 2, 900. 4, … MHz. Solution: Step size/frequency resolution: f. REF = 200 KHz = 10 MHz / R R = 10 MHz / 200 k. Hz = 50 FOUT = 900. 2 MHz = 200 k. Hz x N N = 900. 2 MHz / 200 k. Hz = 4501 N = 4501, 4502, …

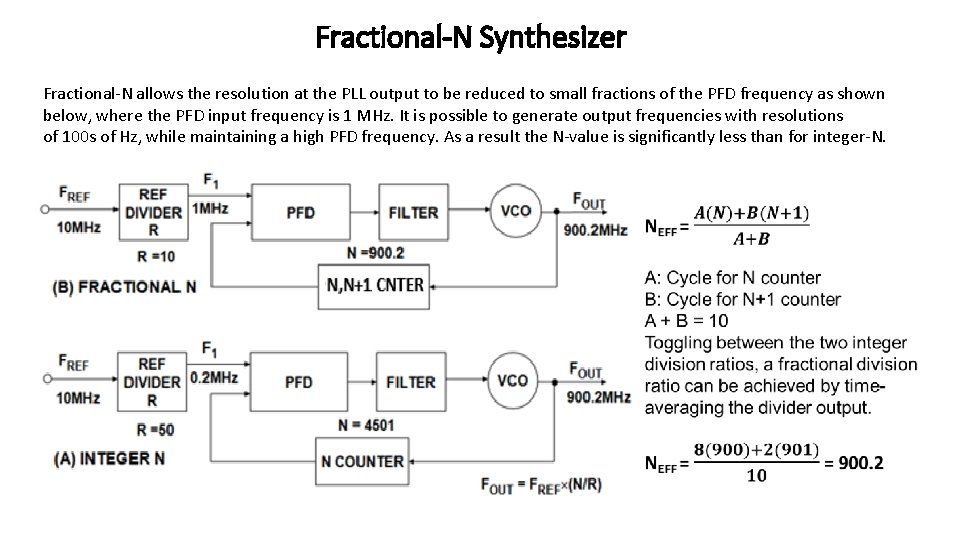

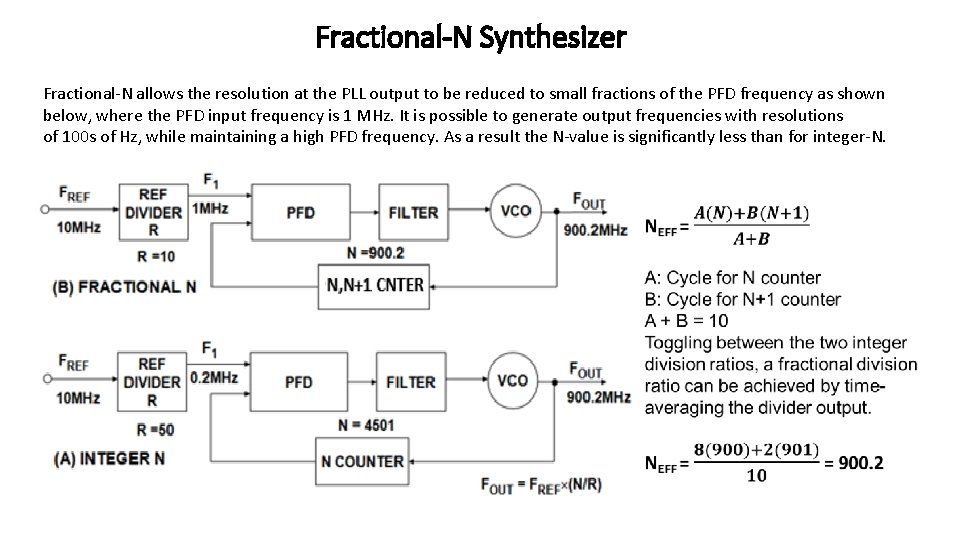

Fractional-N Synthesizer Fractional-N allows the resolution at the PLL output to be reduced to small fractions of the PFD frequency as shown below, where the PFD input frequency is 1 MHz. It is possible to generate output frequencies with resolutions of 100 s of Hz, while maintaining a high PFD frequency. As a result the N-value is significantly less than for integer-N.

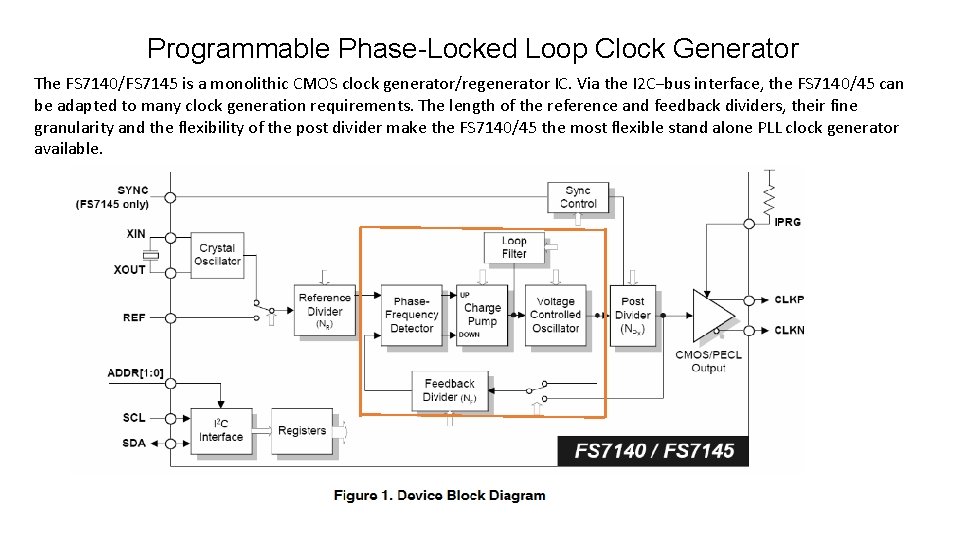

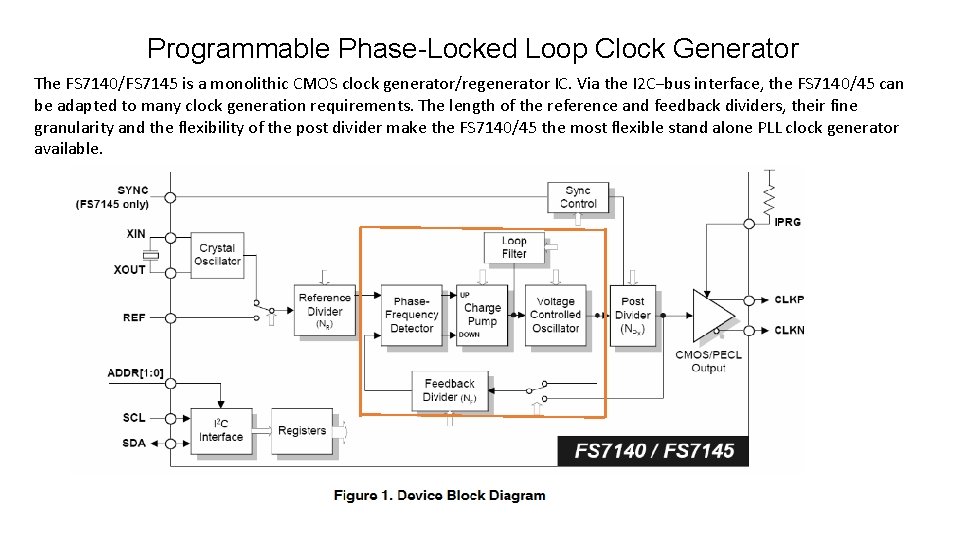

Programmable Phase-Locked Loop Clock Generator The FS 7140/FS 7145 is a monolithic CMOS clock generator/regenerator IC. Via the I 2 C−bus interface, the FS 7140/45 can be adapted to many clock generation requirements. The length of the reference and feedback dividers, their fine granularity and the flexibility of the post divider make the FS 7140/45 the most flexible stand alone PLL clock generator available.

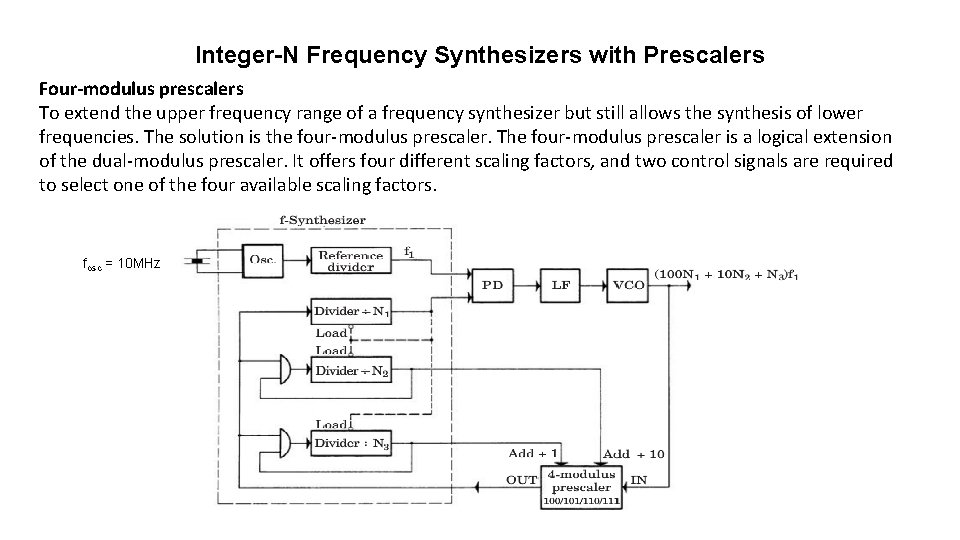

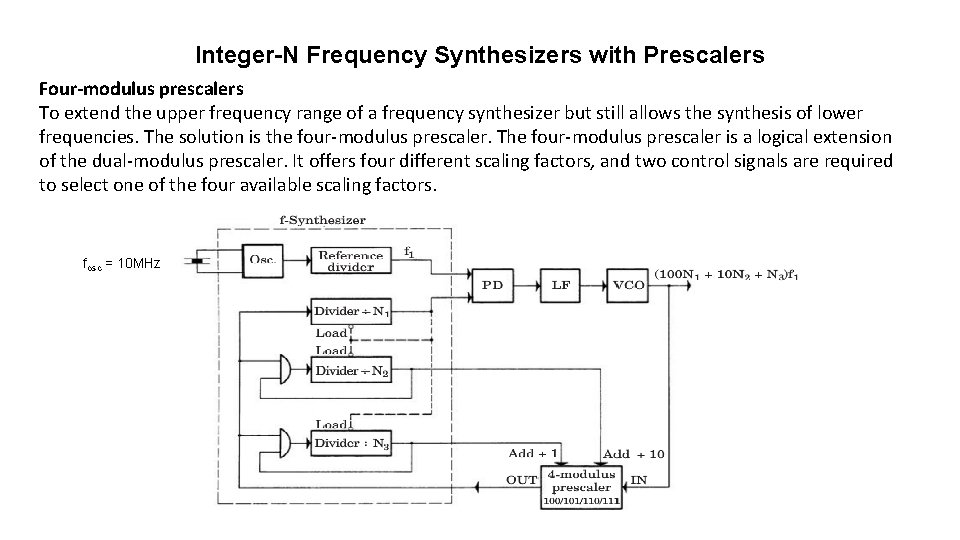

Integer-N Frequency Synthesizers with Prescalers Four-modulus prescalers To extend the upper frequency range of a frequency synthesizer but still allows the synthesis of lower frequencies. The solution is the four-modulus prescaler. The four-modulus prescaler is a logical extension of the dual-modulus prescaler. It offers four different scaling factors, and two control signals are required to select one of the four available scaling factors. fosc = 10 MHz

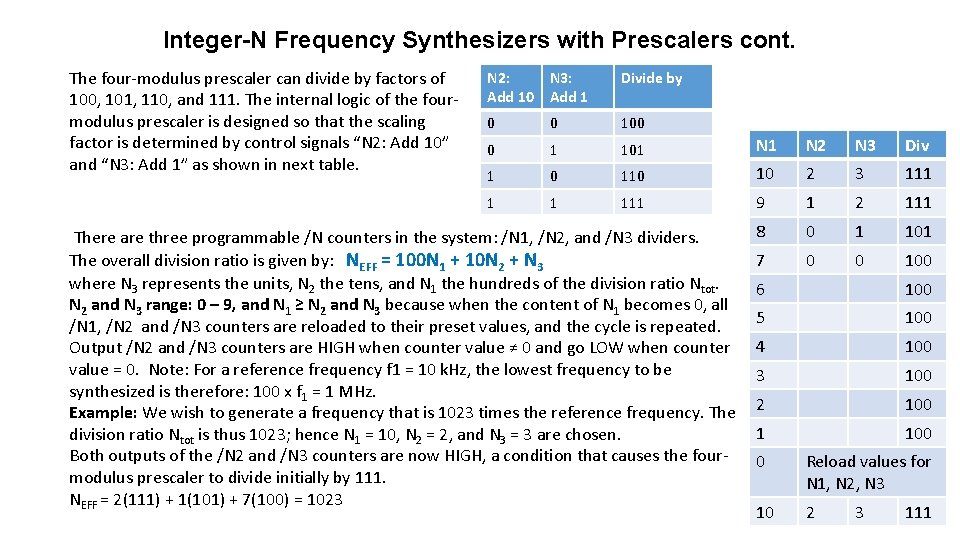

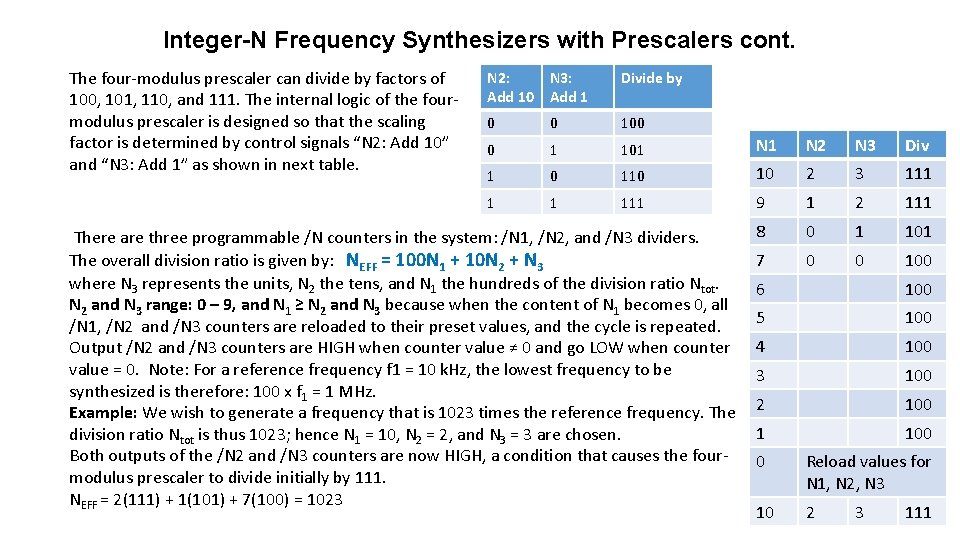

Integer-N Frequency Synthesizers with Prescalers cont. The four-modulus prescaler can divide by factors of 100, 101, 110, and 111. The internal logic of the fourmodulus prescaler is designed so that the scaling factor is determined by control signals “N 2: Add 10” and “N 3: Add 1” as shown in next table. N 2: N 3: Add 10 Add 1 Divide by 0 0 100 0 1 101 N 2 N 3 Div 1 0 110 10 2 3 111 1 1 111 9 1 2 111 8 0 1 101 7 0 0 100 There are three programmable /N counters in the system: /N 1, /N 2, and /N 3 dividers. The overall division ratio is given by: NEFF = 100 N 1 + 10 N 2 + N 3 where N 3 represents the units, N 2 the tens, and N 1 the hundreds of the division ratio Ntot. N 2 and N 3 range: 0 – 9, and N 1 ≥ N 2 and N 3 because when the content of N 1 becomes 0, all /N 1, /N 2 and /N 3 counters are reloaded to their preset values, and the cycle is repeated. Output /N 2 and /N 3 counters are HIGH when counter value ≠ 0 and go LOW when counter value = 0. Note: For a reference frequency f 1 = 10 k. Hz, the lowest frequency to be synthesized is therefore: 100 x f 1 = 1 MHz. Example: We wish to generate a frequency that is 1023 times the reference frequency. The division ratio Ntot is thus 1023; hence N 1 = 10, N 2 = 2, and N 3 = 3 are chosen. Both outputs of the /N 2 and /N 3 counters are now HIGH, a condition that causes the fourmodulus prescaler to divide initially by 111. NEFF = 2(111) + 1(101) + 7(100) = 1023 6 100 5 100 4 100 3 100 2 100 1 100 0 Reload values for N 1, N 2, N 3 10 2 3 111

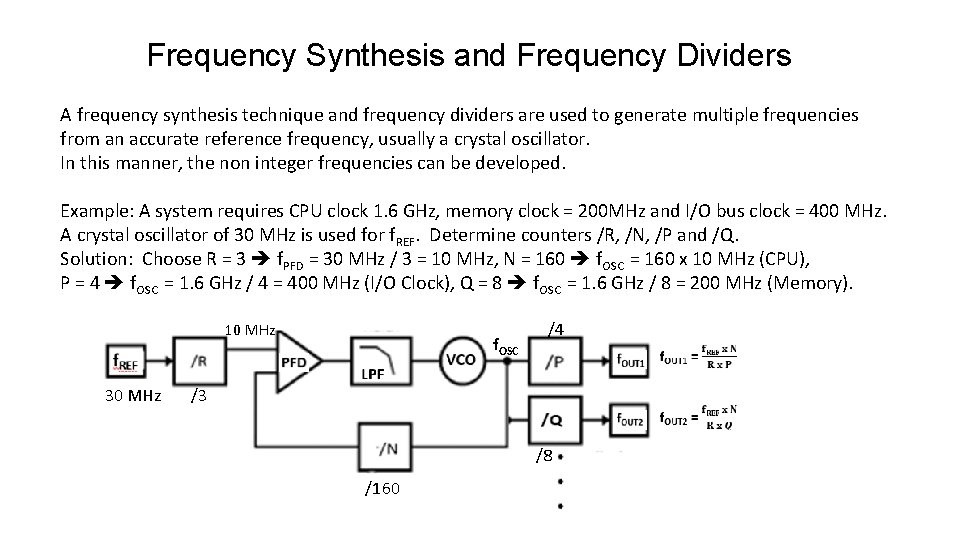

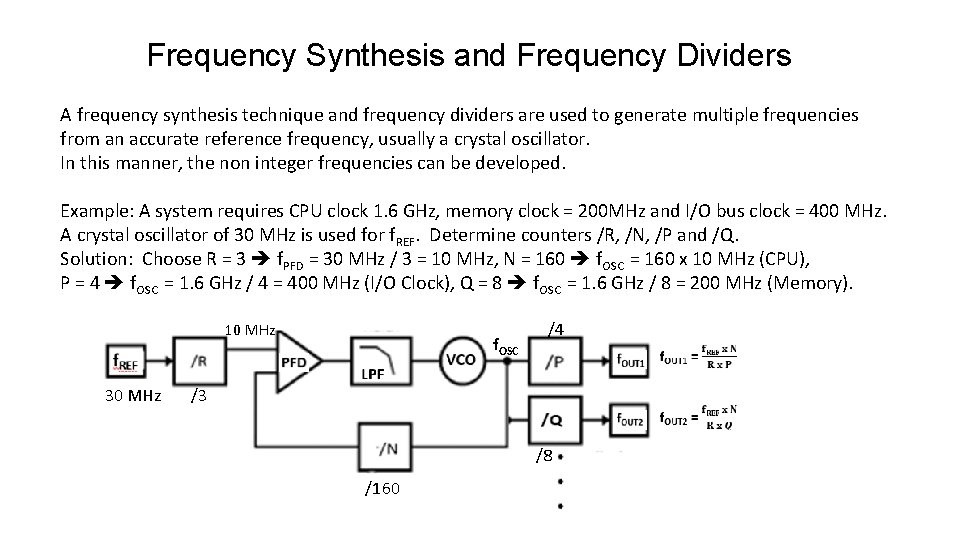

Frequency Synthesis and Frequency Dividers A frequency synthesis technique and frequency dividers are used to generate multiple frequencies from an accurate reference frequency, usually a crystal oscillator. In this manner, the non integer frequencies can be developed. Example: A system requires CPU clock 1. 6 GHz, memory clock = 200 MHz and I/O bus clock = 400 MHz. A crystal oscillator of 30 MHz is used for f. REF. Determine counters /R, /N, /P and /Q. Solution: Choose R = 3 f. PFD = 30 MHz / 3 = 10 MHz, N = 160 f. OSC = 160 x 10 MHz (CPU), P = 4 f. OSC = 1. 6 GHz / 4 = 400 MHz (I/O Clock), Q = 8 f. OSC = 1. 6 GHz / 8 = 200 MHz (Memory). 10 MHz 30 MHz f. OSC /4 /3 /8 /160

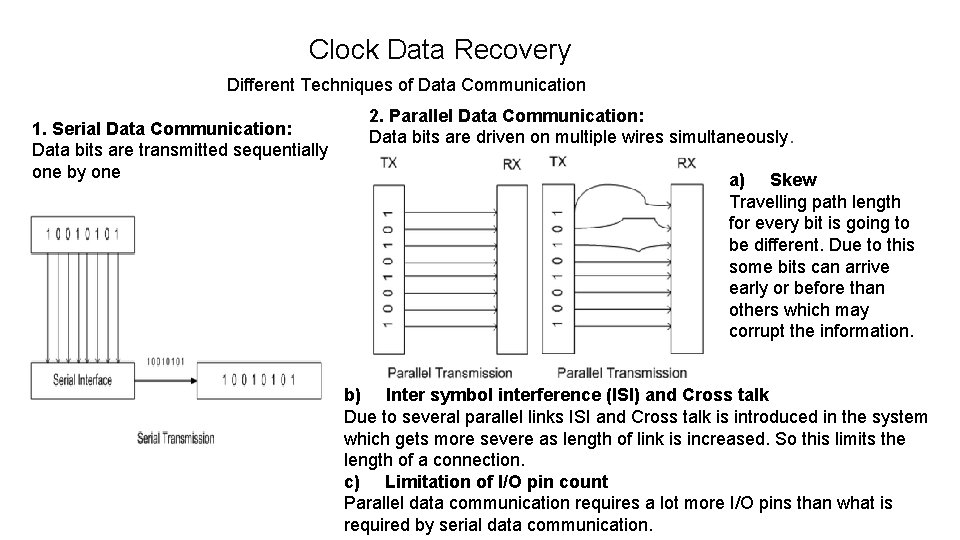

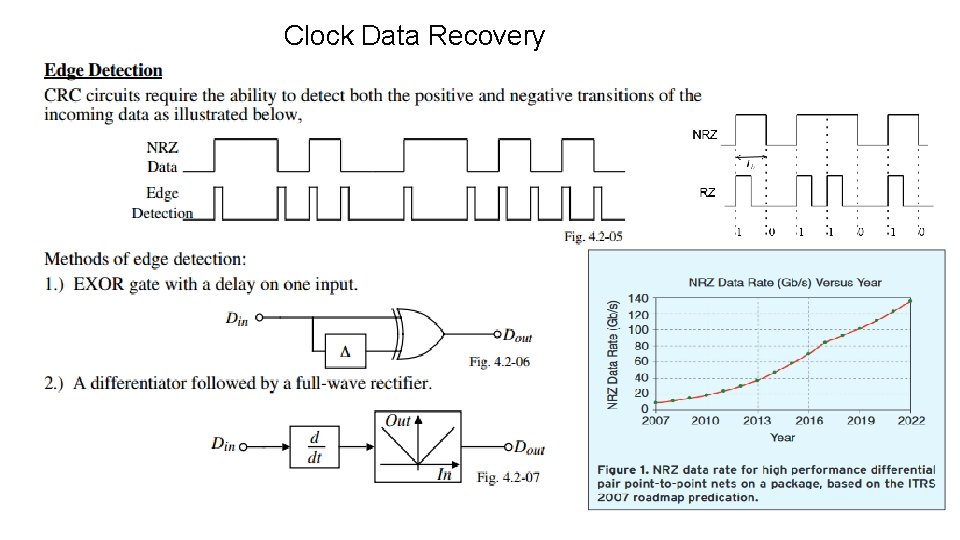

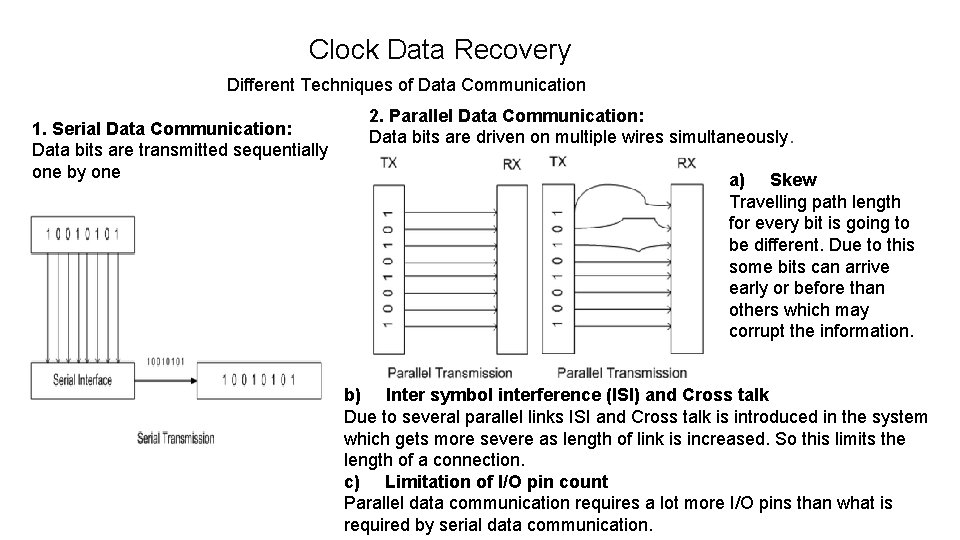

Clock Data Recovery Different Techniques of Data Communication 1. Serial Data Communication: Data bits are transmitted sequentially one by one 2. Parallel Data Communication: Data bits are driven on multiple wires simultaneously. a) Skew Travelling path length for every bit is going to be different. Due to this some bits can arrive early or before than others which may corrupt the information. b) Inter symbol interference (ISI) and Cross talk Due to several parallel links ISI and Cross talk is introduced in the system which gets more severe as length of link is increased. So this limits the length of a connection. c) Limitation of I/O pin count Parallel data communication requires a lot more I/O pins than what is required by serial data communication.

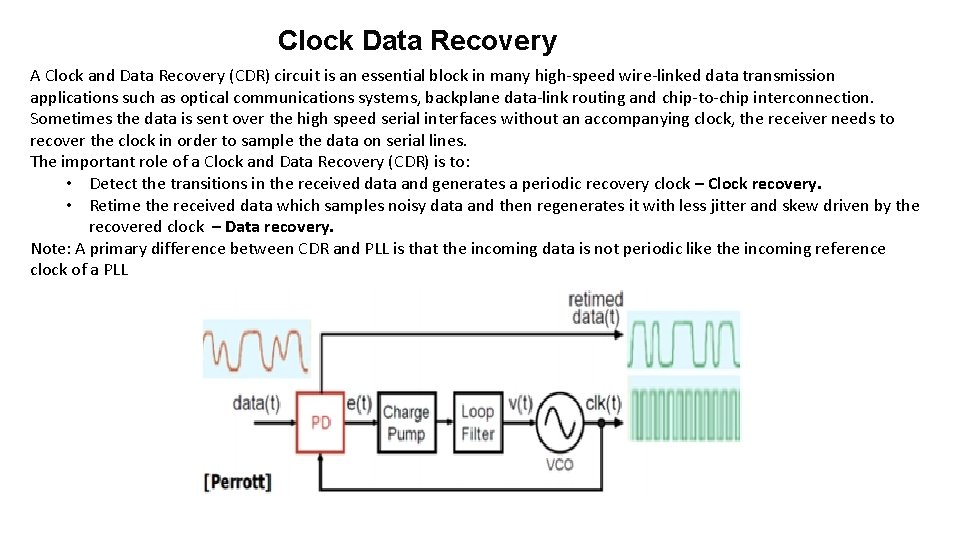

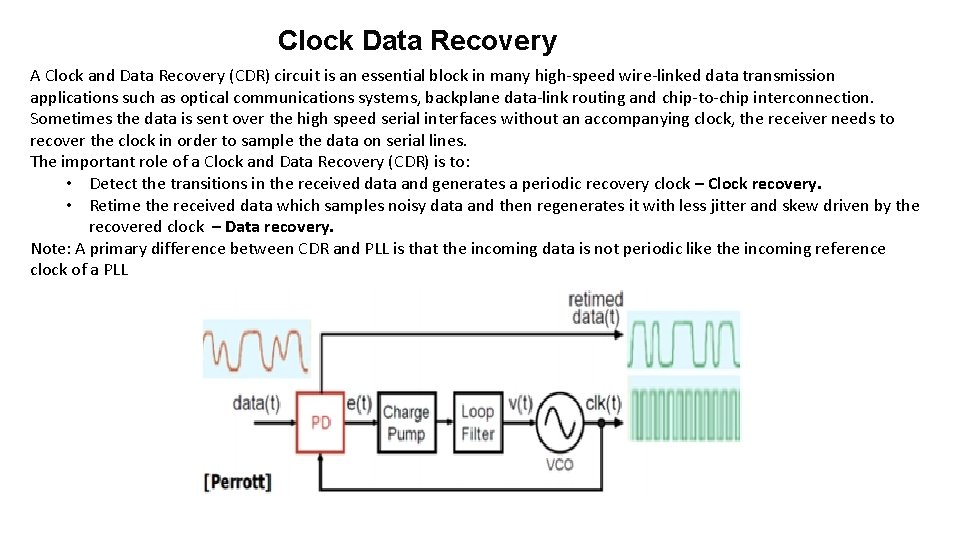

Clock Data Recovery A Clock and Data Recovery (CDR) circuit is an essential block in many high-speed wire-linked data transmission applications such as optical communications systems, backplane data-link routing and chip-to-chip interconnection. Sometimes the data is sent over the high speed serial interfaces without an accompanying clock, the receiver needs to recover the clock in order to sample the data on serial lines. The important role of a Clock and Data Recovery (CDR) is to: • Detect the transitions in the received data and generates a periodic recovery clock – Clock recovery. • Retime the received data which samples noisy data and then regenerates it with less jitter and skew driven by the recovered clock – Data recovery. Note: A primary difference between CDR and PLL is that the incoming data is not periodic like the incoming reference clock of a PLL

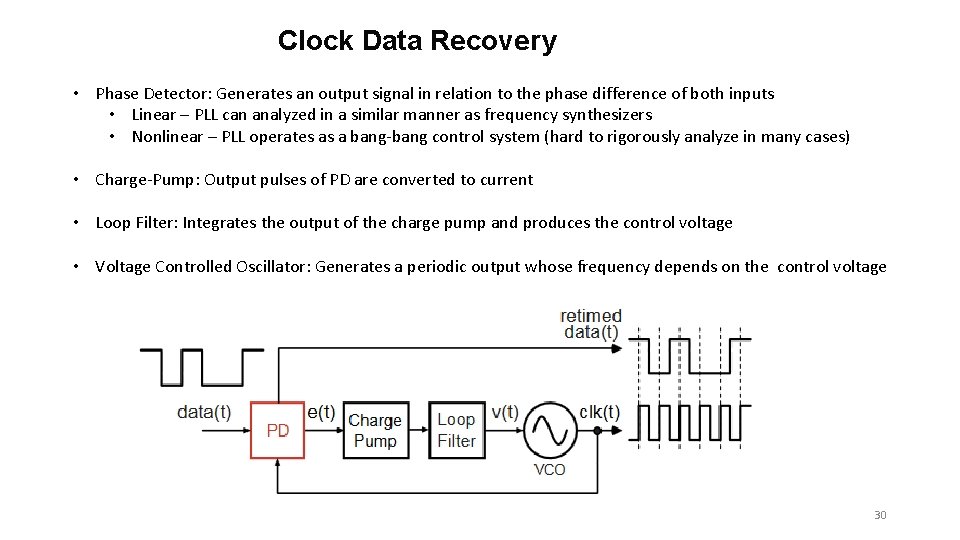

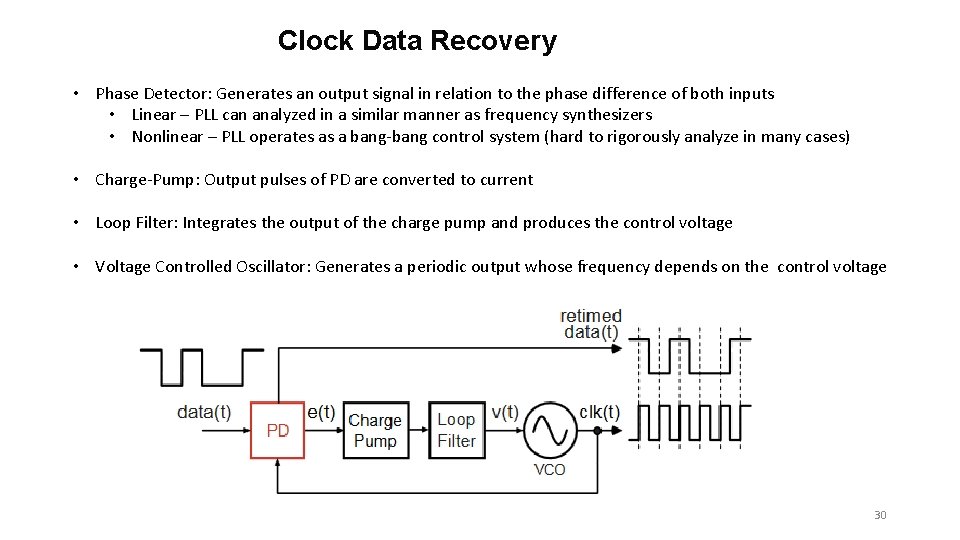

Clock Data Recovery • Phase Detector: Generates an output signal in relation to the phase difference of both inputs • Linear – PLL can analyzed in a similar manner as frequency synthesizers • Nonlinear – PLL operates as a bang-bang control system (hard to rigorously analyze in many cases) • Charge-Pump: Output pulses of PD are converted to current • Loop Filter: Integrates the output of the charge pump and produces the control voltage • Voltage Controlled Oscillator: Generates a periodic output whose frequency depends on the control voltage 30

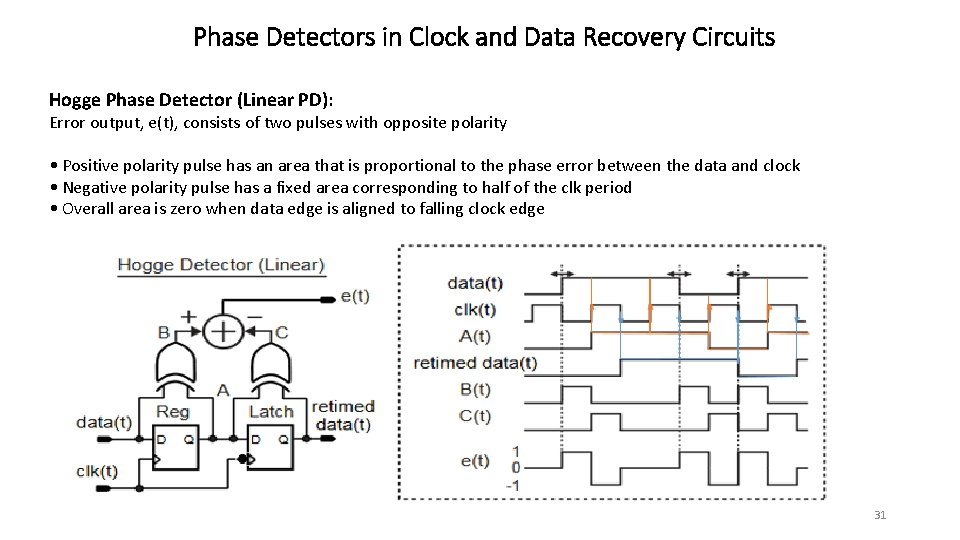

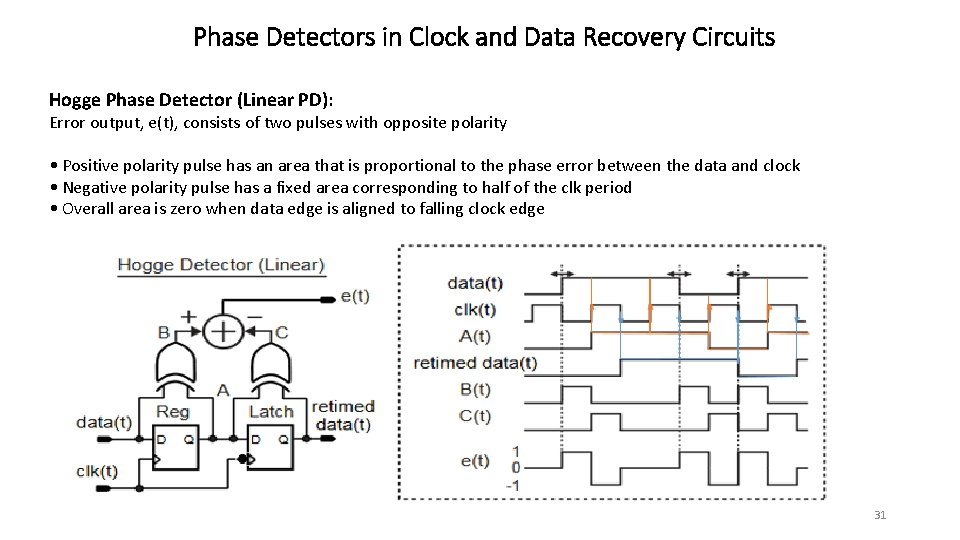

Phase Detectors in Clock and Data Recovery Circuits Hogge Phase Detector (Linear PD): Error output, e(t), consists of two pulses with opposite polarity • Positive polarity pulse has an area that is proportional to the phase error between the data and clock • Negative polarity pulse has a fixed area corresponding to half of the clk period • Overall area is zero when data edge is aligned to falling clock edge 31

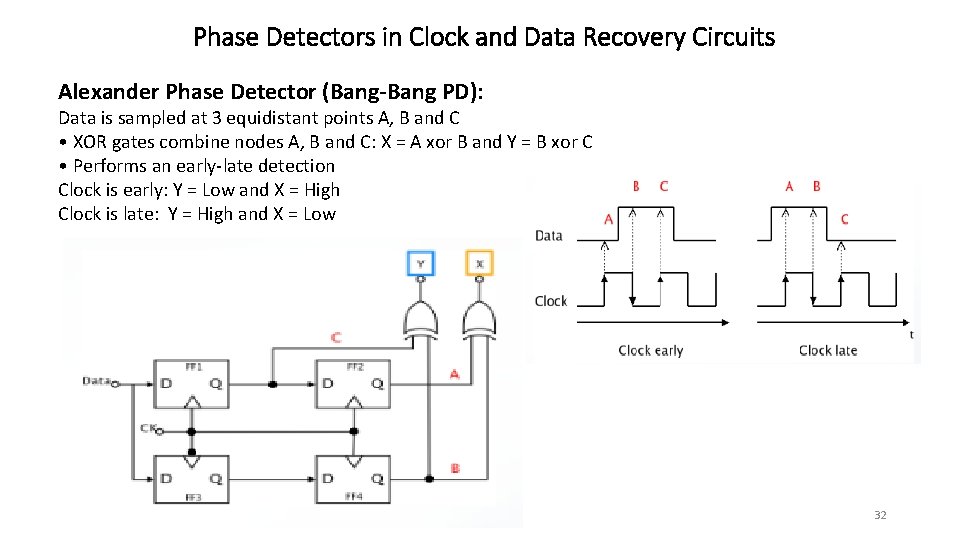

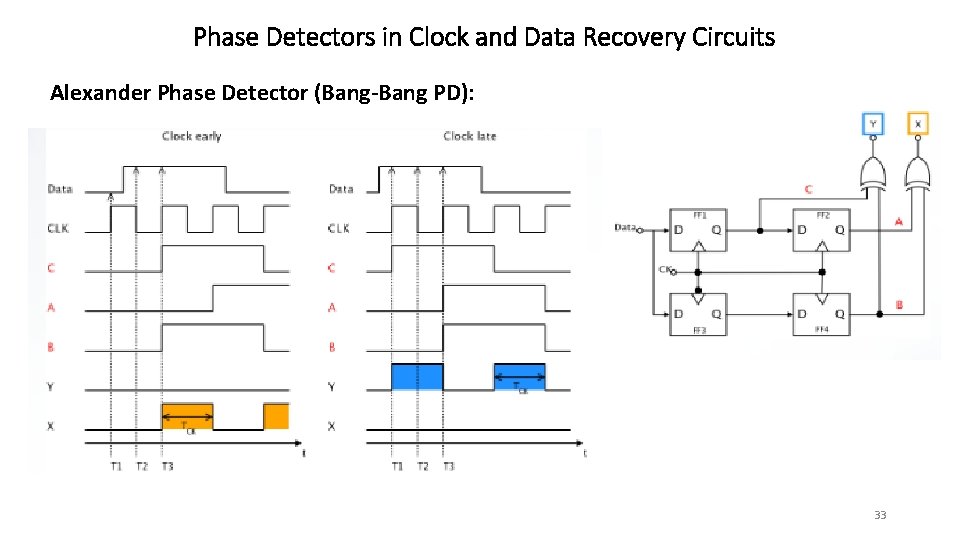

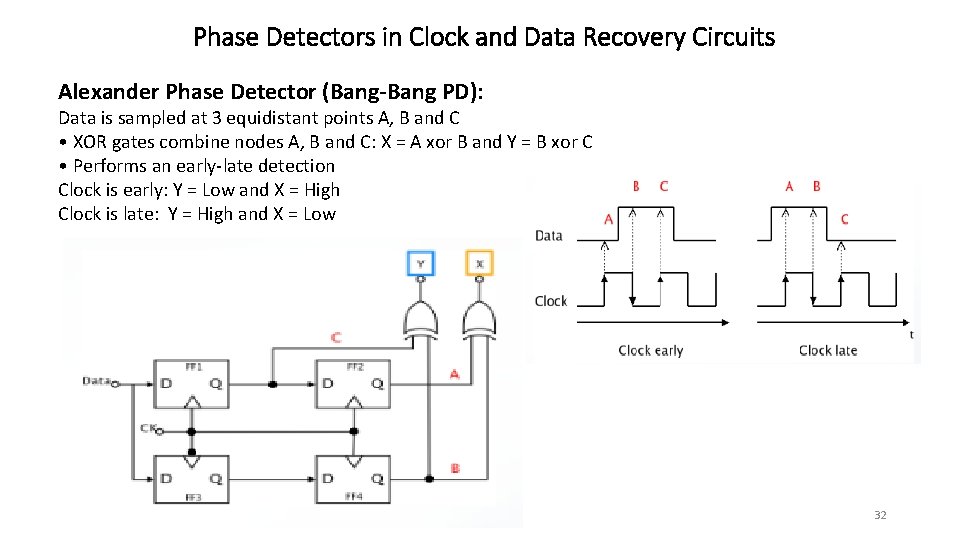

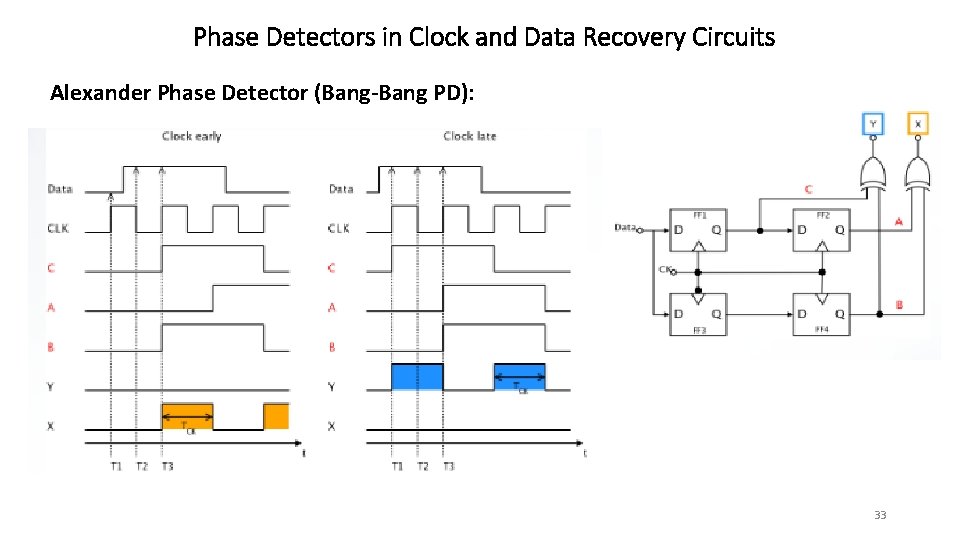

Phase Detectors in Clock and Data Recovery Circuits Alexander Phase Detector (Bang-Bang PD): Data is sampled at 3 equidistant points A, B and C • XOR gates combine nodes A, B and C: X = A xor B and Y = B xor C • Performs an early-late detection Clock is early: Y = Low and X = High Clock is late: Y = High and X = Low 32

Phase Detectors in Clock and Data Recovery Circuits Alexander Phase Detector (Bang-Bang PD): 33

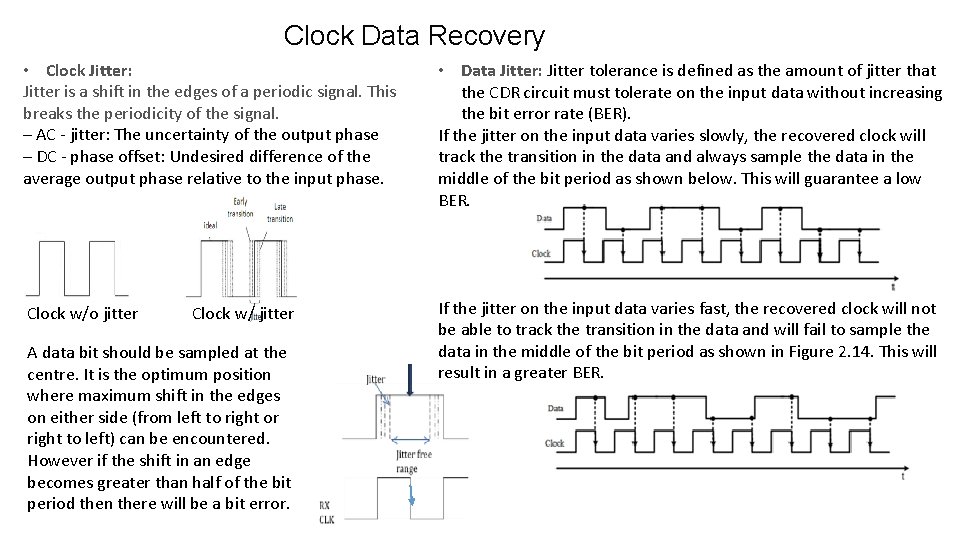

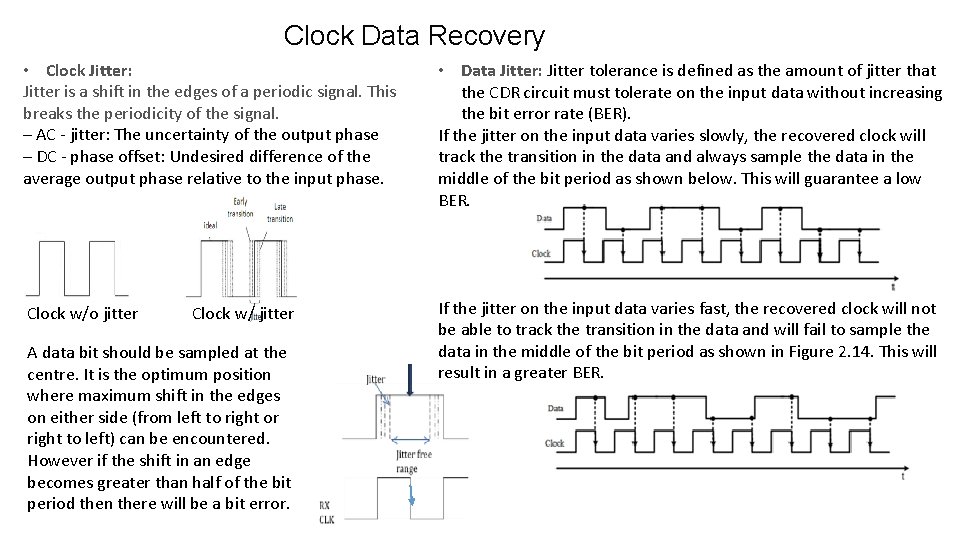

Clock Data Recovery • Clock Jitter: Jitter is a shift in the edges of a periodic signal. This breaks the periodicity of the signal. – AC - jitter: The uncertainty of the output phase – DC - phase offset: Undesired difference of the average output phase relative to the input phase. • Data Jitter: Jitter tolerance is defined as the amount of jitter that the CDR circuit must tolerate on the input data without increasing the bit error rate (BER). If the jitter on the input data varies slowly, the recovered clock will track the transition in the data and always sample the data in the middle of the bit period as shown below. This will guarantee a low BER. Clock w/o jitter Clock w/ jitter If the jitter on the input data varies fast, the recovered clock will not be able to track the transition in the data and will fail to sample the data in the middle of the bit period as shown in Figure 2. 14. This will result in a greater BER. A data bit should be sampled at the centre. It is the optimum position where maximum shift in the edges on either side (from left to right or right to left) can be encountered. However if the shift in an edge becomes greater than half of the bit period then there will be a bit error.

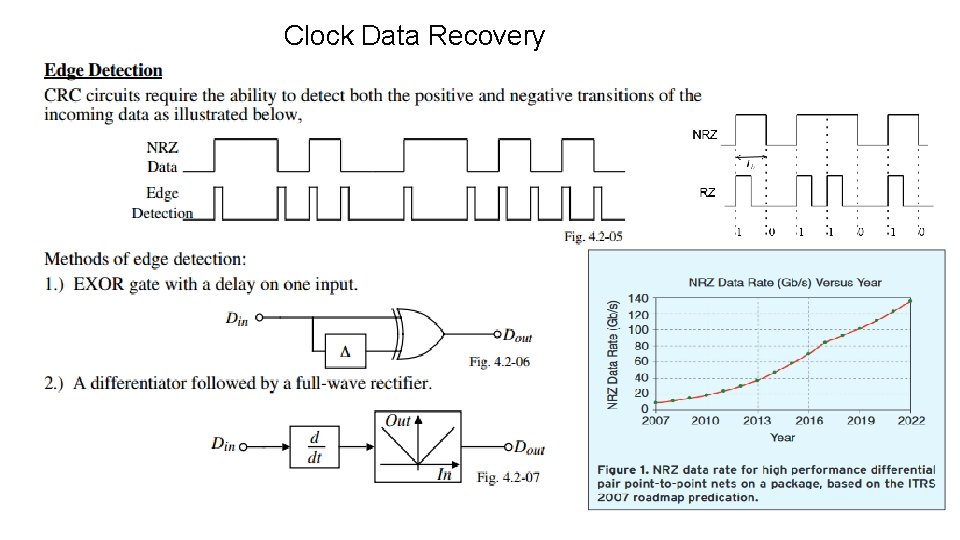

Clock Data Recovery

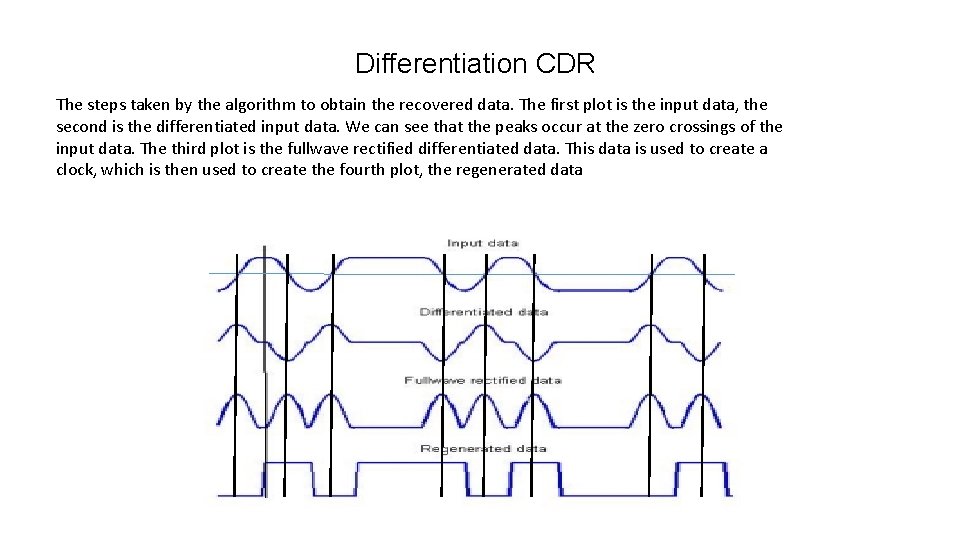

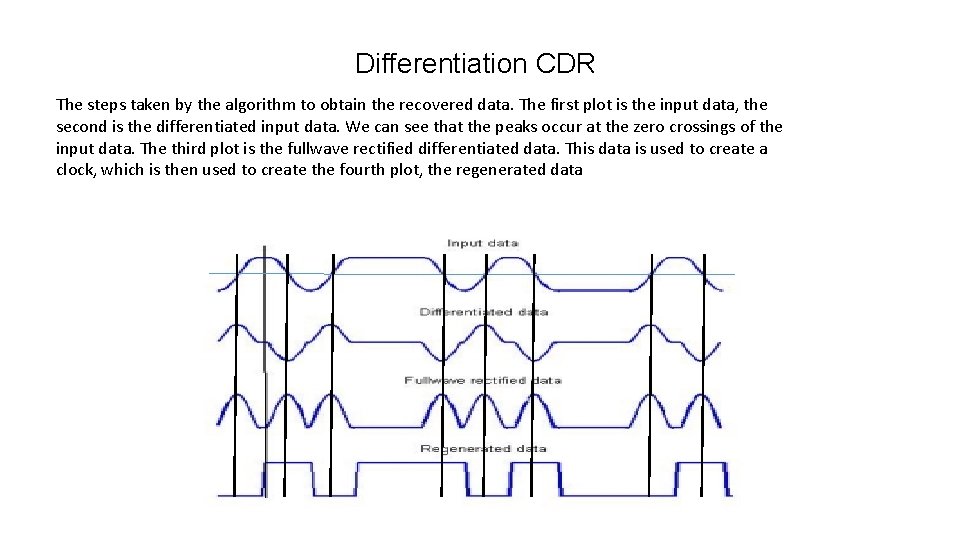

Differentiation CDR The steps taken by the algorithm to obtain the recovered data. The first plot is the input data, the second is the differentiated input data. We can see that the peaks occur at the zero crossings of the input data. The third plot is the fullwave rectified differentiated data. This data is used to create a clock, which is then used to create the fourth plot, the regenerated data

References: http: //www. onsemi. com/pub/Collateral/FS 7140 -D. PDF http: //www. scribd. com/doc/237983665/PLL http: //www. delroy. com/PLL_dir/tutorial/PLL_tutorial_slides. pdf Phase Locked Loops 6/e, 6 th Edition by Roland Best https: //www. google. com/webhp? sourceid=chrome-instant&ion=1&espv=2&ie=UTF 8#q=an 535 http: //eprints. lancs. ac. uk/52334/1/PLLbook_chapter_final_2. pdf http: //www. ti. com/lit/ds/symlink/lm 565. pdf PLL-74 HC 4046_Application_Note%20(1). pdf http: //users. ece. gatech. edu/pallen/Academic/ECE_6440/Summer_2003/L 170 Freq. Syn-I(2 UP). pdf http: //iris. lib. neu. edu/cgi/viewcontent. cgi? article=1007&context=elec_comp_theses

References: ecee. colorado. edu/~ecen 4002/manuals/dsp 56300 family/ch 6 -pll-clk. pdf http: //www. arrowdevices. com/blog/beginners-guide-to-clock-data-recovery/ http: //www. twyman. org. uk/clock_recovery/#pn-seq http: //web. stanford. edu/class/archive/ee/ee 371. 1066/lectures/Older/lect_17_CDR_2 up. pdf http: //www. seas. ucla. edu/brweb/teaching/215 C_W 2013/PLLs. pdf http: //www. ece. ucsb. edu/~long/ece 594 a/PLL_intro_594 a_s 05. pdf http: //www. ti. com/lit/an/snoa 351. pdf http: //memo. cgu. edu. tw/jtkuo/files/eelab%202014%28 III%29/1230_Lab 12_Expxx_Phase. Locked. Loop. pdf http: //siihr 64. iihr. uiowa. edu/My. Web/Teaching/ece_55141_2013/Homework. Assignment 08 Solution. p df http: //www. freeclassnotesonline. com/VCO-and-PLL-Calculations-HW. php http: //ecee. colorado. edu/~ecen 4618/lab 4. pdf http: //www. analog. com/media/en/training-seminars/tutorials/MT-086. pdf www. ti. com/lit/an/swra 029. pdf

References: http: //www. scribd. com/doc/237983665/PLL http: //www. delroy. com/PLL_dir/tutorial/PLL_tutorial_slides. pdf Phase Locked Loops 6/e, 6 th Edition by Roland Best https: //www. google. com/webhp? sourceid=chrome-instant&ion=1&espv=2&ie=UTF 8#q=an 535 http: //eprints. lancs. ac. uk/52334/1/PLLbook_chapter_final_2. pdf http: //www. ti. com/lit/ds/symlink/lm 565. pdf PLL-74 HC 4046_Application_Note%20(1). pdf http: //users. ece. gatech. edu/pallen/Academic/ECE_6440/Summer_2003/L 170 Freq. Syn-I(2 UP). pdf http: //iris. lib. neu. edu/cgi/viewcontent. cgi? article=1007&context=elec_comp_theses 39

References: http: //scholarworks. sjsu. edu/cgi/viewcontent. cgi? article=8032&context=etd_theses http: //www. scribd. com/doc/237983665/PLL http: //www. seas. ucla. edu/brweb/teaching/215 C_W 2013/PLLs. pdf http: //www. ece. ucsb. edu/~long/ece 594 a/PLL_intro_594 a_s 05. pdf http: //www. ti. com/lit/an/snoa 351. pdf http: //memo. cgu. edu. tw/jtkuo/files/eelab%202014%28 III%29/1230_Lab 12_Expxx_Phase. L ocked. Loop. pdf http: //siihr 64. iihr. uiowa. edu/My. Web/Teaching/ece_55141_2013/Homework. A ssignment 08 Solution. pdf http: //www. freeclassnotesonline. com/VCO-and-PLL-Calculations-HW. php http: //ecee. colorado. edu/~ecen 4618/lab 4. pdf http: //www. eas. uccs. edu/~mwickert/ece 5675/lecture_notes/N 5675_1. pdf http: //hft. uni-duisburg-essen. de/arbeiten/Vortrag_Forcan_Milan. pdf https: //ocw. mit. edu/courses/electrical-engineering-and-computer-science/6 -976 -highspeed-communication-circuits-and-systems-spring-2003/lecture-notes/lec 21. pdf https: //pdfs. semanticscholar. org/de 17/8 a 088507 a 387 e 98 a 1 dc 06 ccf 628 e 3015 fcd 3. pdf 40