Power Optimization for Clock Network with Clock Gate

![Previous Work of CG Cloning • [Teng & Soin, ICSE'10] Ø Introduced cutting-based algorithm Previous Work of CG Cloning • [Teng & Soin, ICSE'10] Ø Introduced cutting-based algorithm](https://slidetodoc.com/presentation_image_h/7e324de200b3d6ab34145c6753a141b8/image-8.jpg)

![Previous Work of FF Merging • [Kretchmer, EE Times Asia'01], [Chen et al. , Previous Work of FF Merging • [Kretchmer, EE Times Asia'01], [Chen et al. ,](https://slidetodoc.com/presentation_image_h/7e324de200b3d6ab34145c6753a141b8/image-9.jpg)

- Slides: 37

Power Optimization for Clock Network with Clock Gate Cloning and Flip-Flop Merging Shih-Chuan Lo Chih-Cheng Hsu Mark Po-Hung Lin Department of Electrical Engineering National Chung Cheng University, Chiayi, Taiwan page 1

Outline • • • Introduction Preliminaries The Proposed Algorithms Experimental Results Conclusions page 2

Outline • Introduction Ø Low Power Design Methodologies Ø The Concept of Clock-Gating Cell Ø The Concept of Clock-Gate Cloning Ø The Concept of Flip-Flop Merging Ø Previous Work Ø Our Contributions • • Preliminaries The Proposed Algorithms Experimental Results Conclusions page 3

Low Power Design Methodologies • Clock gating cell (CG) Ø [Wu et al. , TCAS'00], [Shen et al. , TVLSI'10], • Clock gate cloning Ø [Teng & Soin, ICSE'10], [Vishweshwara et al. , ISQED'12] • Multi-bit flip-flop (MBFF) Ø [Pokala et al. , ASIC 92], [Kretchmer, EE Times Asia'01], [Chen et al. , SNUG 10], [Lin et al. , TCAD'11], [Wang et al. , TCAD'12], [Jiang et al. , TCAD'12], [Shyu et al. , TVLSI 13], [Tsai et al. , ISPD 13] • … page 4

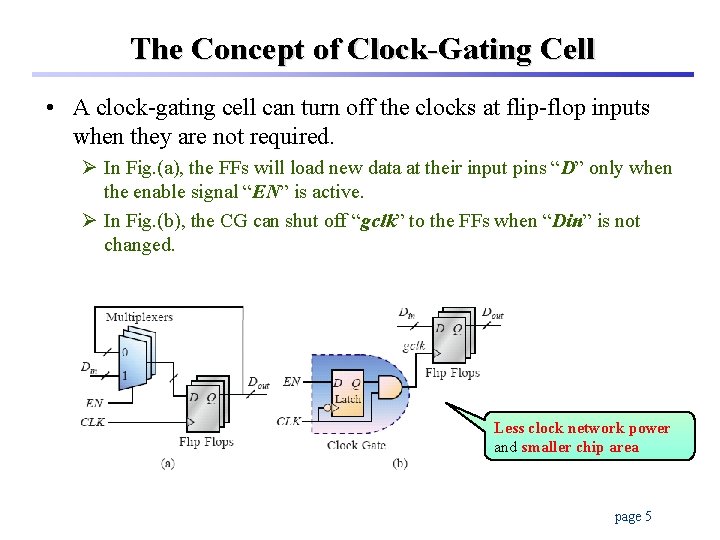

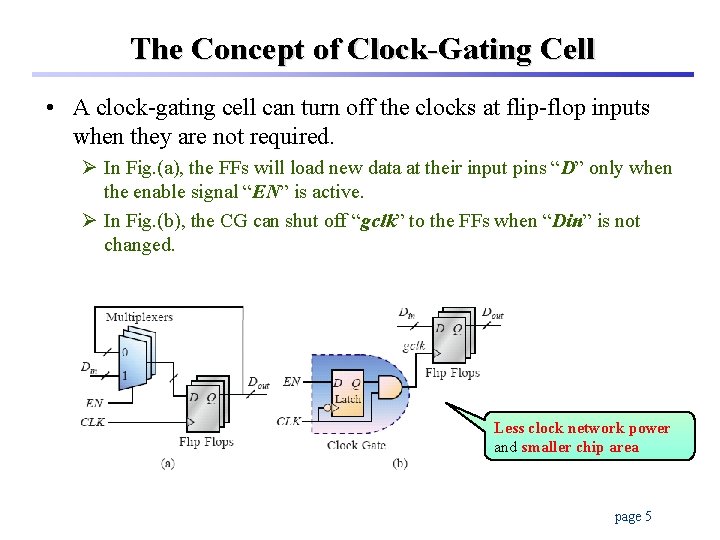

The Concept of Clock-Gating Cell • A clock-gating cell can turn off the clocks at flip-flop inputs when they are not required. Ø In Fig. (a), the FFs will load new data at their input pins “D” only when the enable signal “EN” is active. Ø In Fig. (b), the CG can shut off “gclk” to the FFs when “Din” is not changed. Less clock network power and smaller chip area page 5

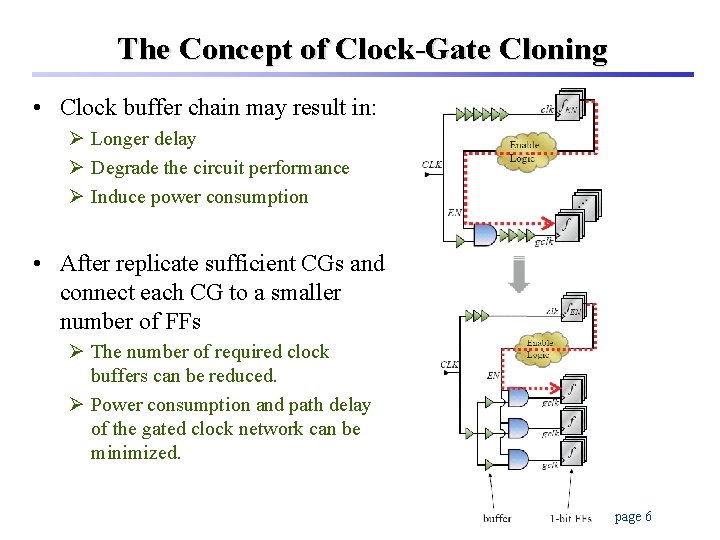

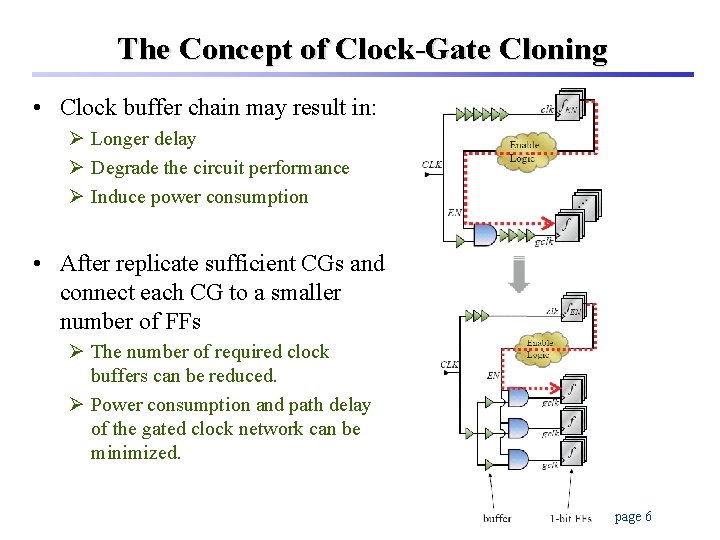

The Concept of Clock-Gate Cloning • Clock buffer chain may result in: Ø Longer delay Ø Degrade the circuit performance Ø Induce power consumption • After replicate sufficient CGs and connect each CG to a smaller number of FFs Ø The number of required clock buffers can be reduced. Ø Power consumption and path delay of the gated clock network can be minimized. page 6

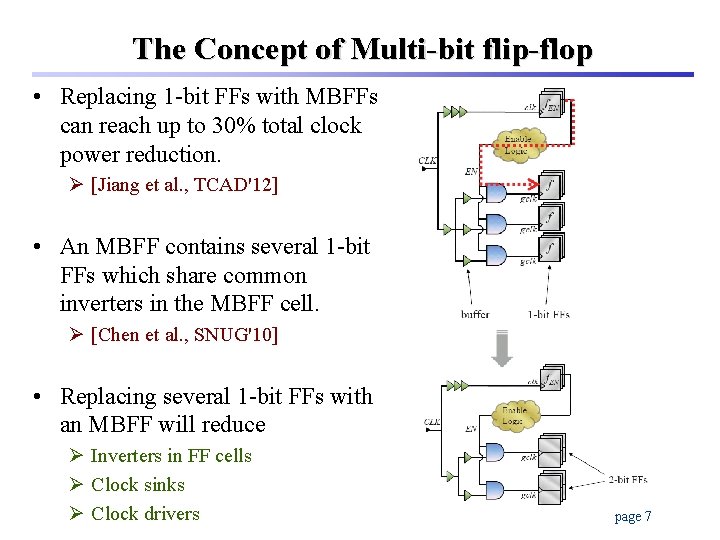

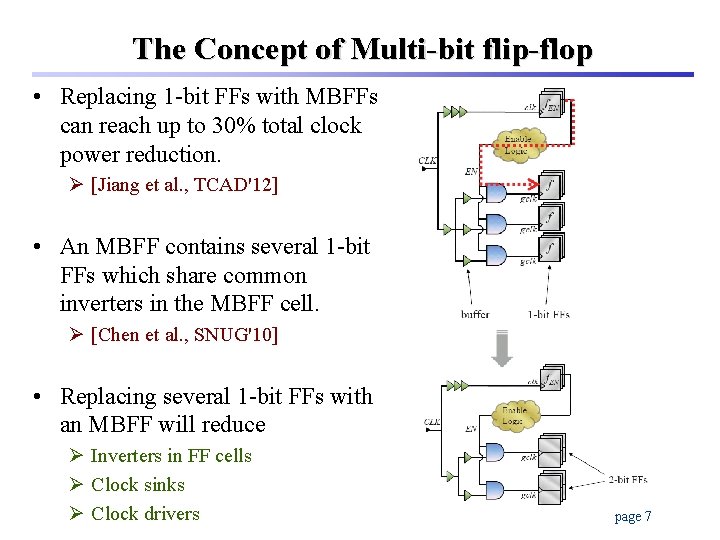

The Concept of Multi-bit flip-flop • Replacing 1 -bit FFs with MBFFs can reach up to 30% total clock power reduction. Ø [Jiang et al. , TCAD'12] • An MBFF contains several 1 -bit FFs which share common inverters in the MBFF cell. Ø [Chen et al. , SNUG'10] • Replacing several 1 -bit FFs with an MBFF will reduce Ø Inverters in FF cells Ø Clock sinks Ø Clock drivers page 7

![Previous Work of CG Cloning Teng Soin ICSE10 Ø Introduced cuttingbased algorithm Previous Work of CG Cloning • [Teng & Soin, ICSE'10] Ø Introduced cutting-based algorithm](https://slidetodoc.com/presentation_image_h/7e324de200b3d6ab34145c6753a141b8/image-8.jpg)

Previous Work of CG Cloning • [Teng & Soin, ICSE'10] Ø Introduced cutting-based algorithm to split a CG and redistribute the CG fanout according to the cut line. Ø The CG splitting algorithm is iteratively performed until the timing violation of each CG’s enable signal is eliminated. • [Vishweshwara et al. , ISQED'12] Ø Proposed a clustering-based algorithm to recursively replicate a CG when the CG has a large number of fanout, or when the spreading area of its fanout is larger than a limit. page 8

![Previous Work of FF Merging Kretchmer EE Times Asia01 Chen et al Previous Work of FF Merging • [Kretchmer, EE Times Asia'01], [Chen et al. ,](https://slidetodoc.com/presentation_image_h/7e324de200b3d6ab34145c6753a141b8/image-9.jpg)

Previous Work of FF Merging • [Kretchmer, EE Times Asia'01], [Chen et al. , SNUG 10] Ø Demonstrated the feasibility of applying MBFFs during logic synthesis. • [Pokala et al. , ASIC 92] Ø Applied MBFFs before placement optimization. • [Tsai et al. , ISPD 13] Ø Applied MBFFs during placement optimization. • [Lin et al. , TCAD'11], [Wang et al. , TCAD'12], [Jiang et al. , TCAD'12], [Shyu et al. , TVLSI 13] Ø Perform power optimization with MBFFs at the post-placement stage for better timing budgeting. page 9

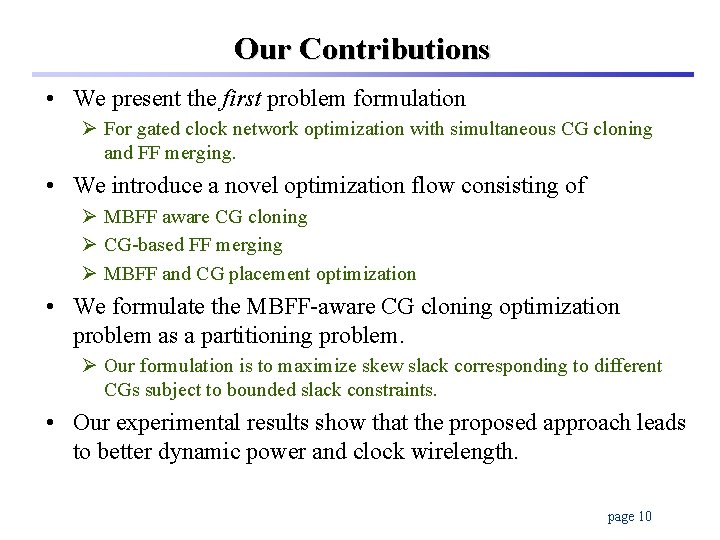

Our Contributions • We present the first problem formulation Ø For gated clock network optimization with simultaneous CG cloning and FF merging. • We introduce a novel optimization flow consisting of Ø MBFF aware CG cloning Ø CG-based FF merging Ø MBFF and CG placement optimization • We formulate the MBFF-aware CG cloning optimization problem as a partitioning problem. Ø Our formulation is to maximize skew slack corresponding to different CGs subject to bounded slack constraints. • Our experimental results show that the proposed approach leads to better dynamic power and clock wirelength. page 10

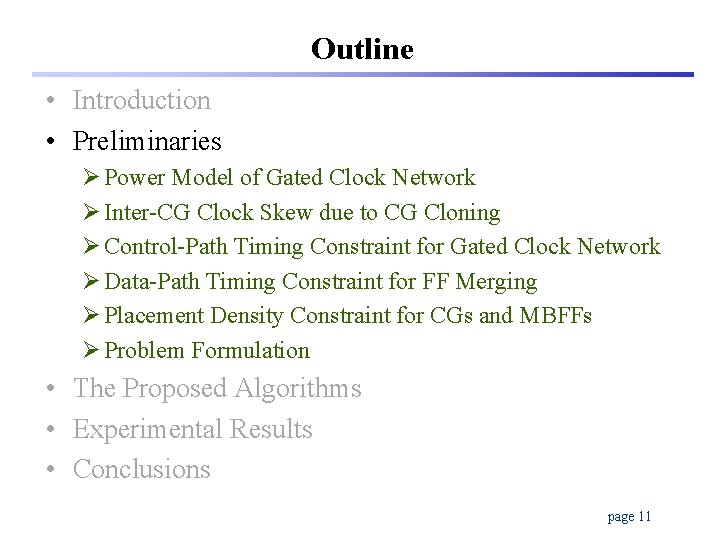

Outline • Introduction • Preliminaries Ø Power Model of Gated Clock Network Ø Inter-CG Clock Skew due to CG Cloning Ø Control-Path Timing Constraint for Gated Clock Network Ø Data-Path Timing Constraint for FF Merging Ø Placement Density Constraint for CGs and MBFFs Ø Problem Formulation • The Proposed Algorithms • Experimental Results • Conclusions page 11

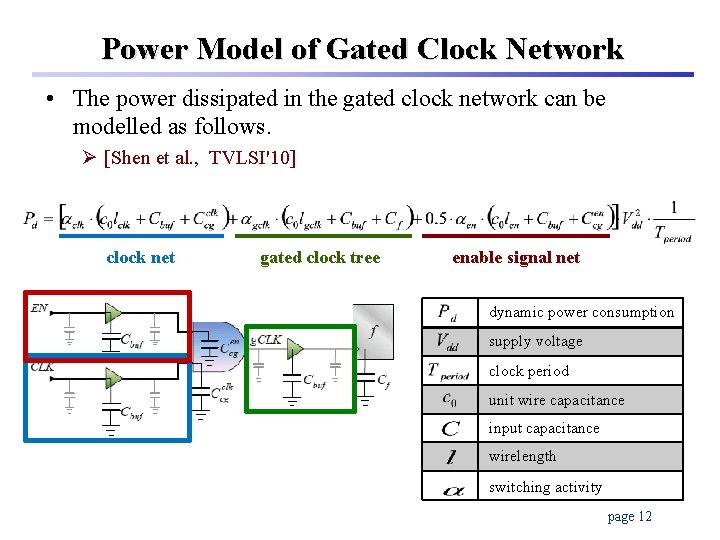

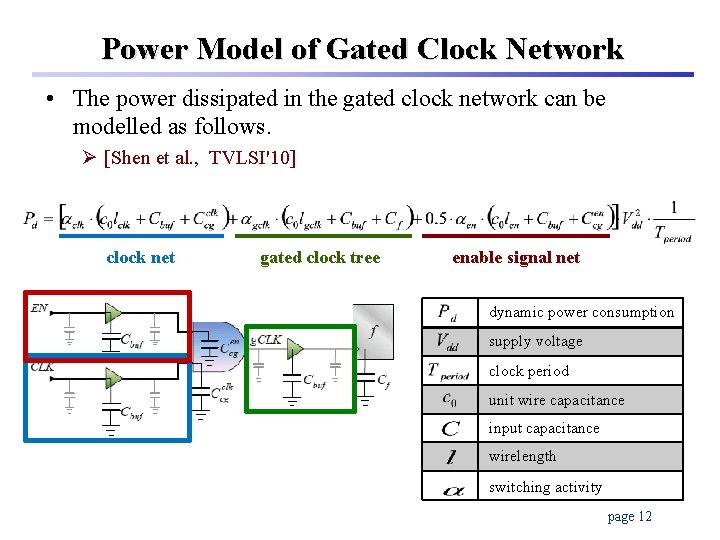

Power Model of Gated Clock Network • The power dissipated in the gated clock network can be modelled as follows. Ø [Shen et al. , TVLSI'10] clock net gated clock tree enable signal net dynamic power consumption supply voltage clock period unit wire capacitance input capacitance wirelength switching activity page 12

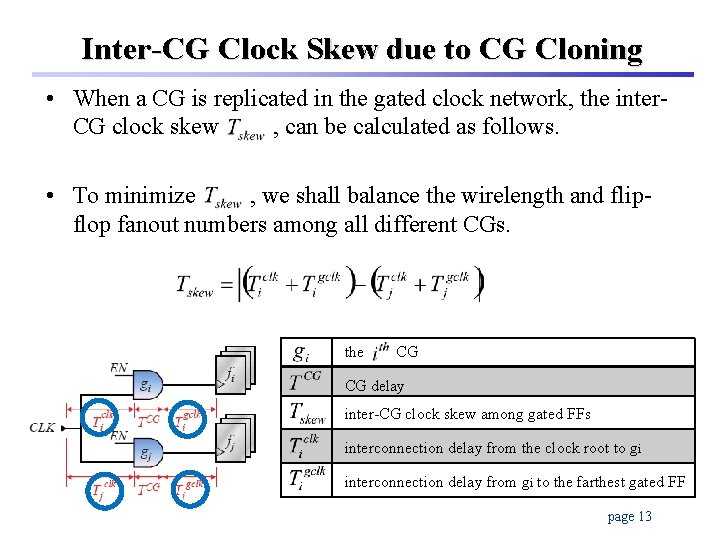

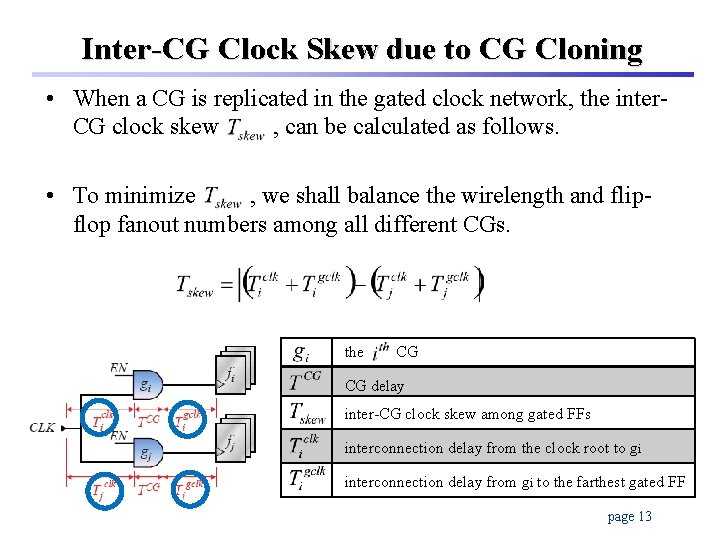

Inter-CG Clock Skew due to CG Cloning • When a CG is replicated in the gated clock network, the inter. CG clock skew , can be calculated as follows. • To minimize , we shall balance the wirelength and flipflop fanout numbers among all different CGs. the CG CG delay inter-CG clock skew among gated FFs interconnection delay from the clock root to gi interconnection delay from gi to the farthest gated FF page 13

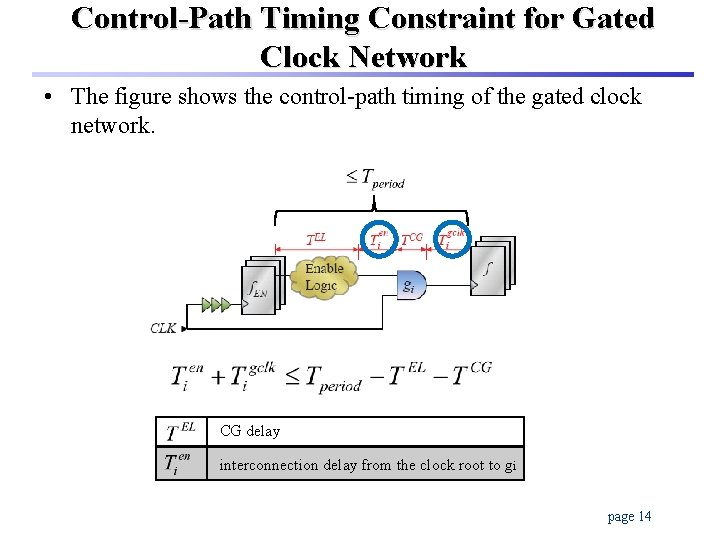

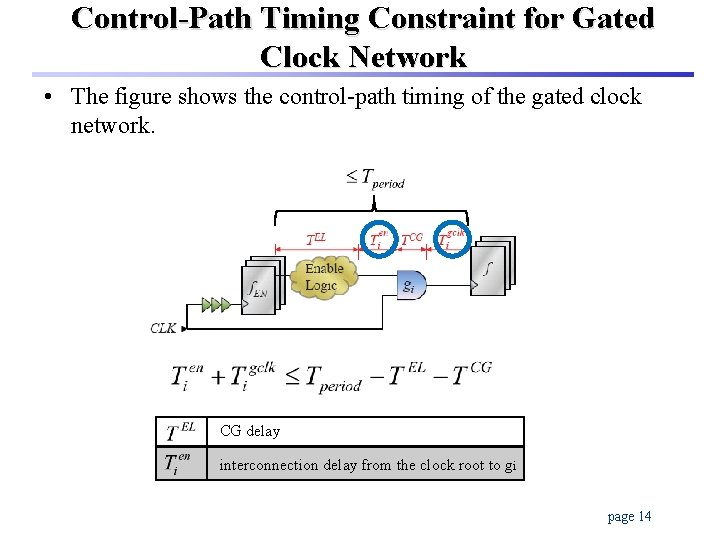

Control-Path Timing Constraint for Gated Clock Network • The figure shows the control-path timing of the gated clock network. CG delay interconnection delay from the clock root to gi page 14

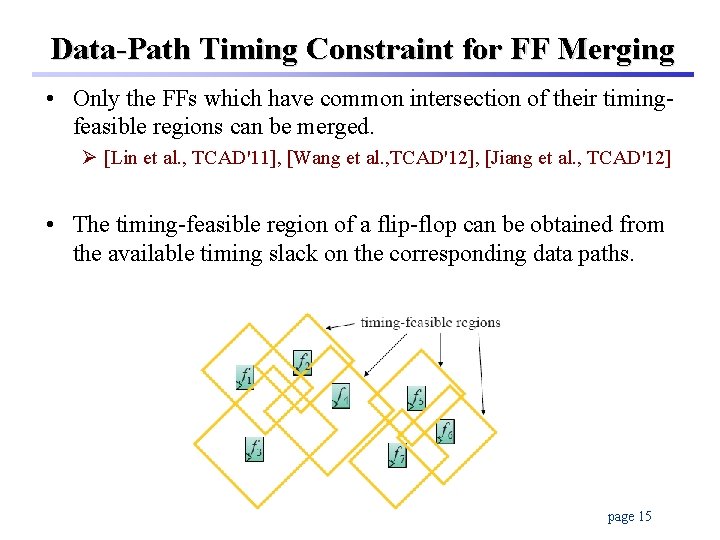

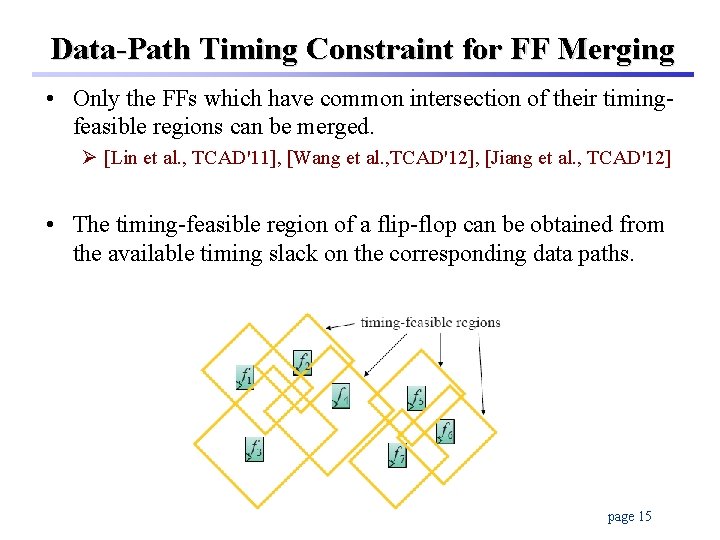

Data-Path Timing Constraint for FF Merging • Only the FFs which have common intersection of their timingfeasible regions can be merged. Ø [Lin et al. , TCAD'11], [Wang et al. , TCAD'12], [Jiang et al. , TCAD'12] • The timing-feasible region of a flip-flop can be obtained from the available timing slack on the corresponding data paths. page 15

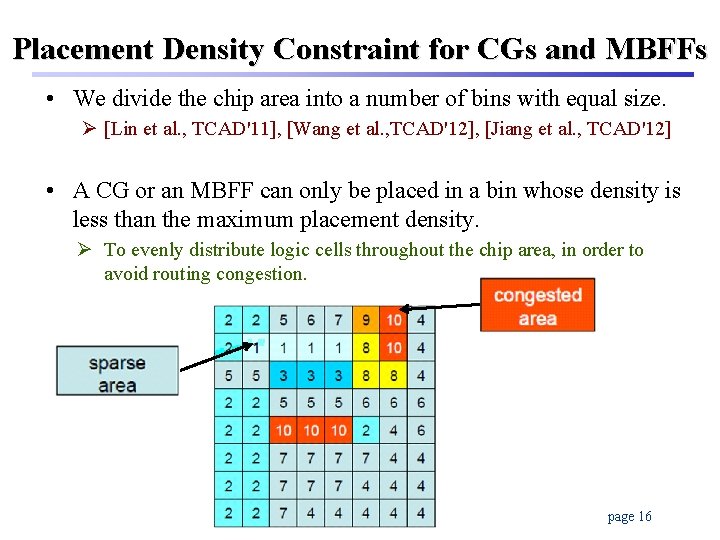

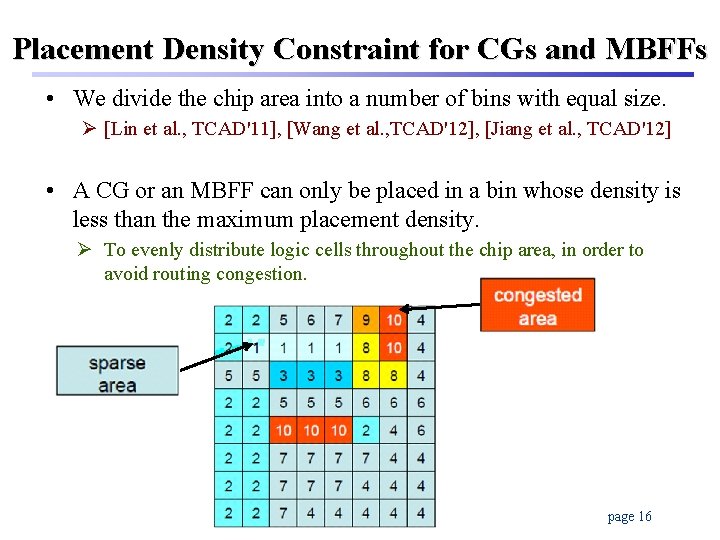

Placement Density Constraint for CGs and MBFFs • We divide the chip area into a number of bins with equal size. Ø [Lin et al. , TCAD'11], [Wang et al. , TCAD'12], [Jiang et al. , TCAD'12] • A CG or an MBFF can only be placed in a bin whose density is less than the maximum placement density. Ø To evenly distribute logic cells throughout the chip area, in order to avoid routing congestion. page 16

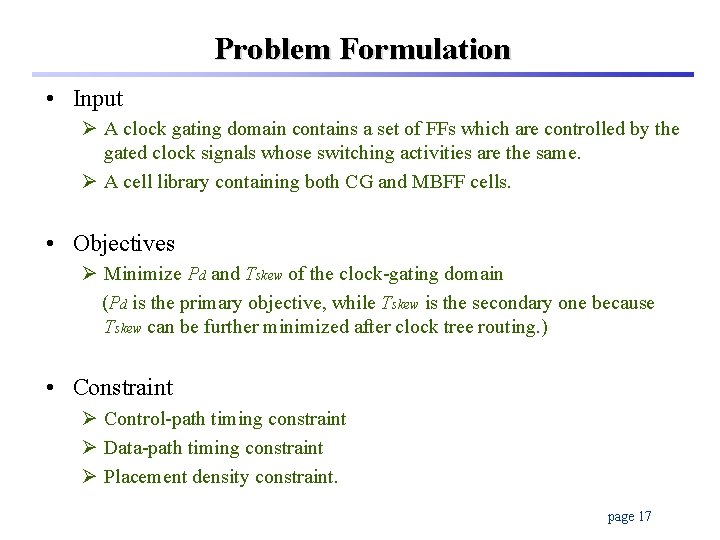

Problem Formulation • Input Ø A clock gating domain contains a set of FFs which are controlled by the gated clock signals whose switching activities are the same. Ø A cell library containing both CG and MBFF cells. • Objectives Ø Minimize Pd and Tskew of the clock-gating domain (Pd is the primary objective, while Tskew is the secondary one because Tskew can be further minimized after clock tree routing. ) • Constraint Ø Control-path timing constraint Ø Data-path timing constraint Ø Placement density constraint. page 17

Outline • Introduction • Preliminaries • The Proposed Algorithms Ø The Proposed Algorithms Flow Ø MBFF-aware CG Cloning Ø CG-based FF Merging Ø MBFF and CG Placement Optimization • Experimental Results • Conclusions page 18

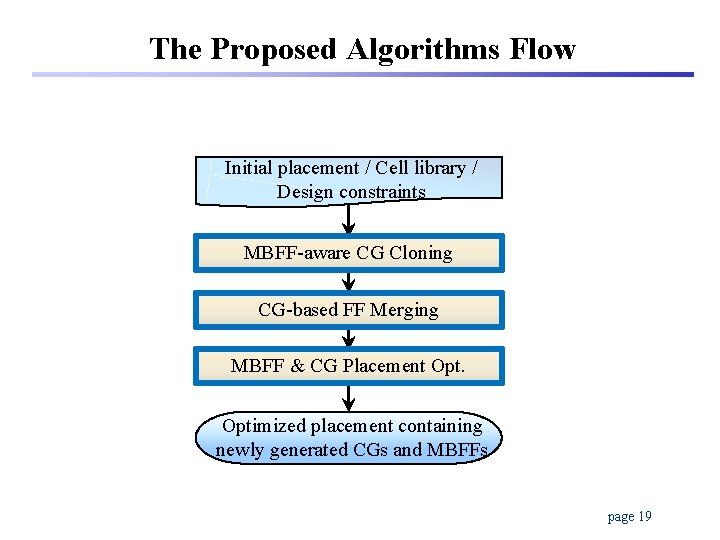

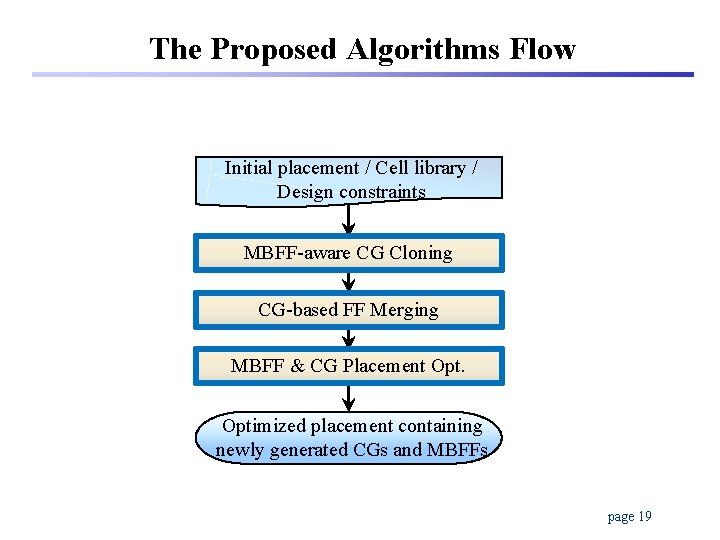

The Proposed Algorithms Flow Initial placement / Cell library / Design constraints MBFF-aware CG Cloning CG-based FF Merging MBFF & CG Placement Optimized placement containing newly generated CGs and MBFFs page 19

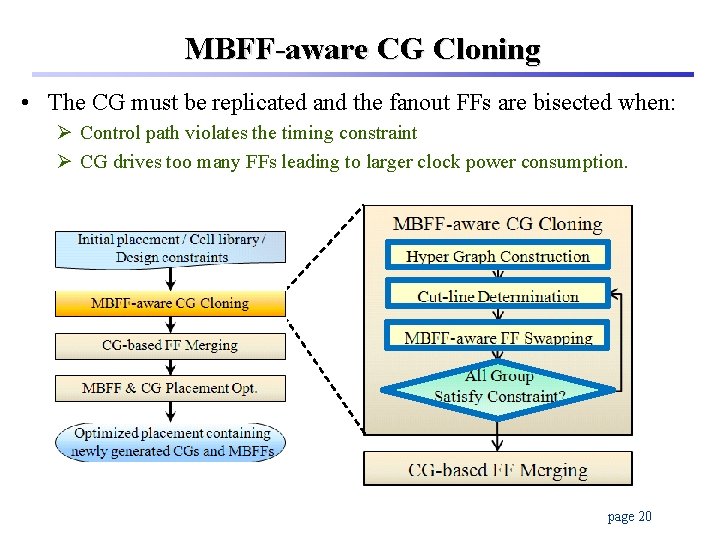

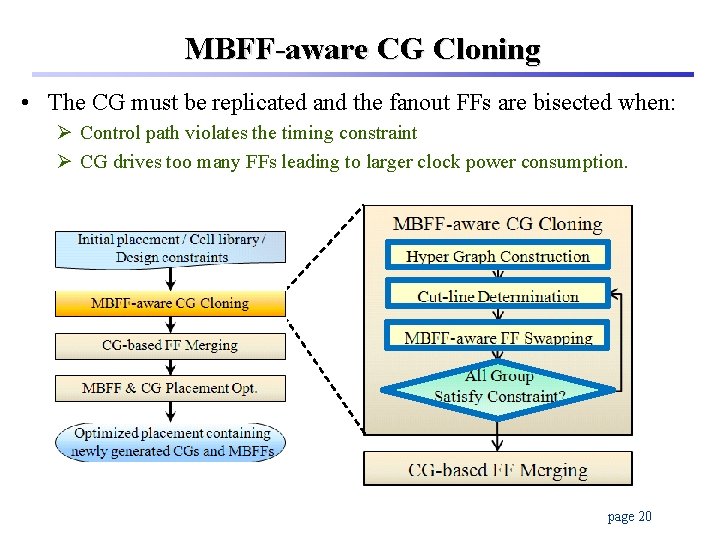

MBFF-aware CG Cloning • The CG must be replicated and the fanout FFs are bisected when: Ø Control path violates the timing constraint Ø CG drives too many FFs leading to larger clock power consumption. page 20

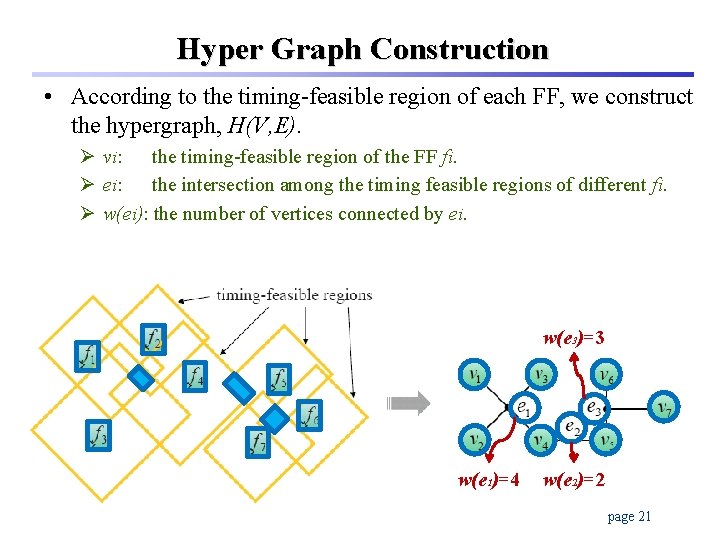

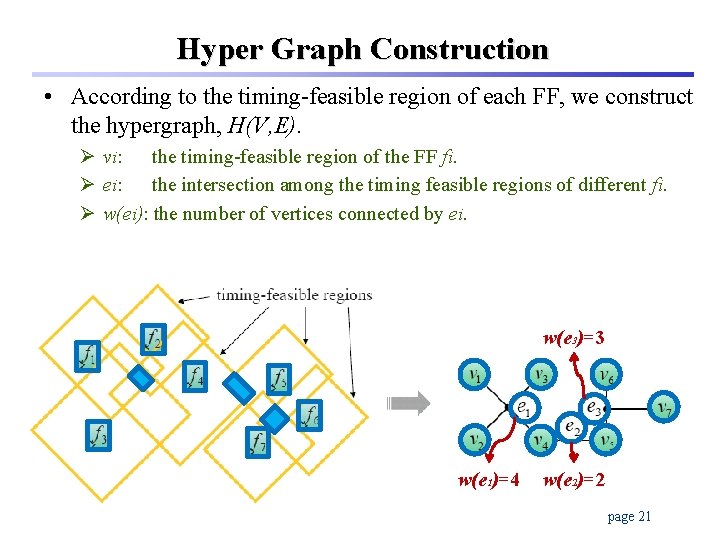

Hyper Graph Construction • According to the timing-feasible region of each FF, we construct the hypergraph, H(V, E). Ø vi: the timing-feasible region of the FF fi. Ø ei: the intersection among the timing feasible regions of different fi. Ø w(ei): the number of vertices connected by ei. w(e 3)=3 w(e 1)=4 w(e 2)=2 page 21

Cut-line Determination with Inter-CG Skew Budgeting • The cut direction is determined by the physical dimension of the FF bounding box. [Teng & Soin, ICSE'10] Ø A vertical (horizontal) cut is applied if the dimension in x-direction is larger (smaller) than that in y-direction. • To balance the delay passing through different CGs, we sweep the cut line to search for the maximum skew slack. page 22

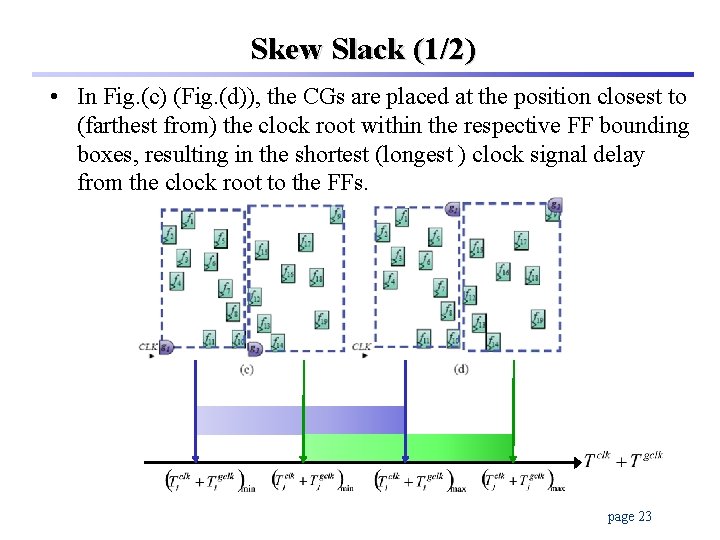

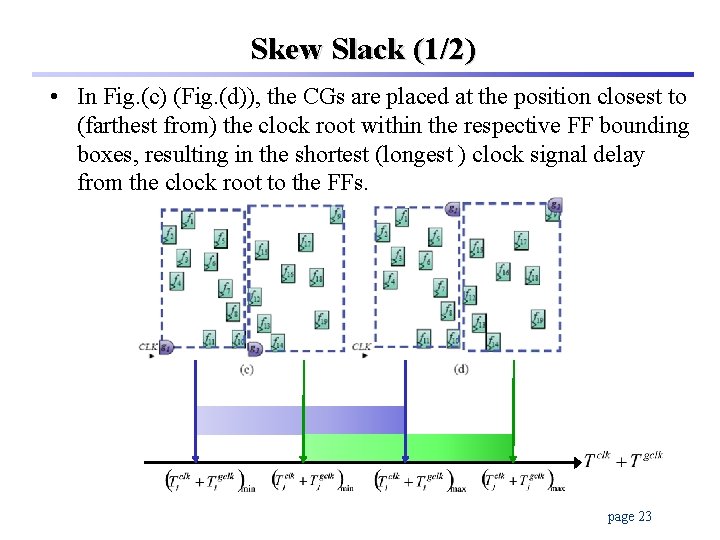

Skew Slack (1/2) • In Fig. (c) (Fig. (d)), the CGs are placed at the position closest to (farthest from) the clock root within the respective FF bounding boxes, resulting in the shortest (longest ) clock signal delay from the clock root to the FFs. page 23

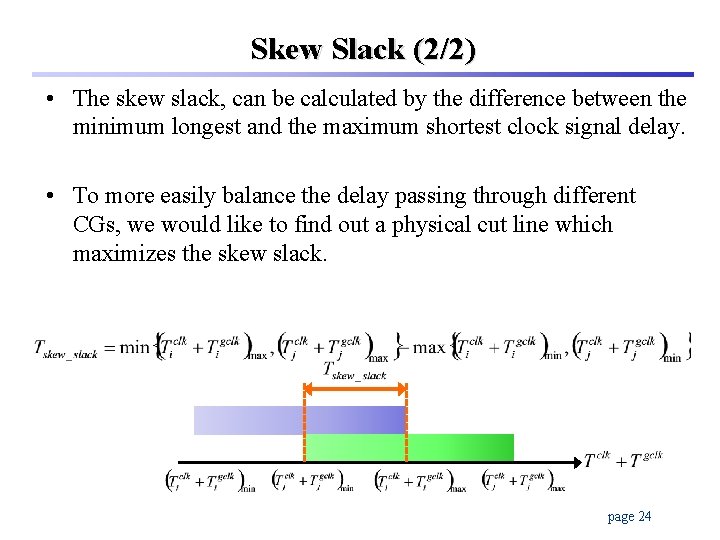

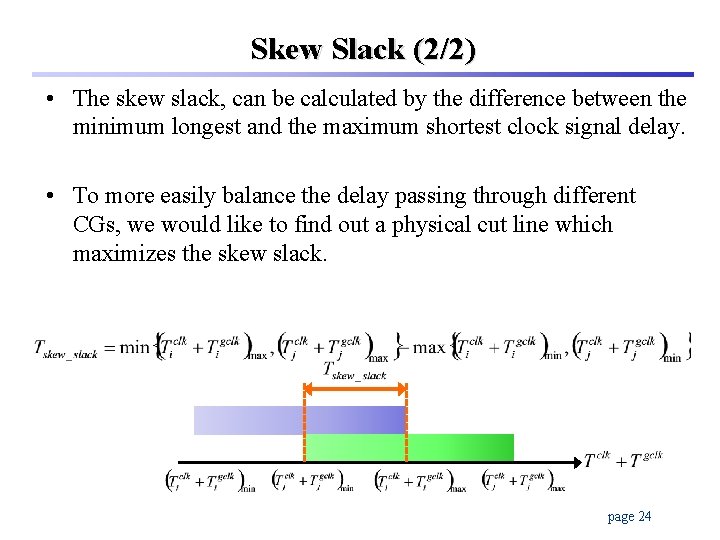

Skew Slack (2/2) • The skew slack, can be calculated by the difference between the minimum longest and the maximum shortest clock signal delay. • To more easily balance the delay passing through different CGs, we would like to find out a physical cut line which maximizes the skew slack. page 24

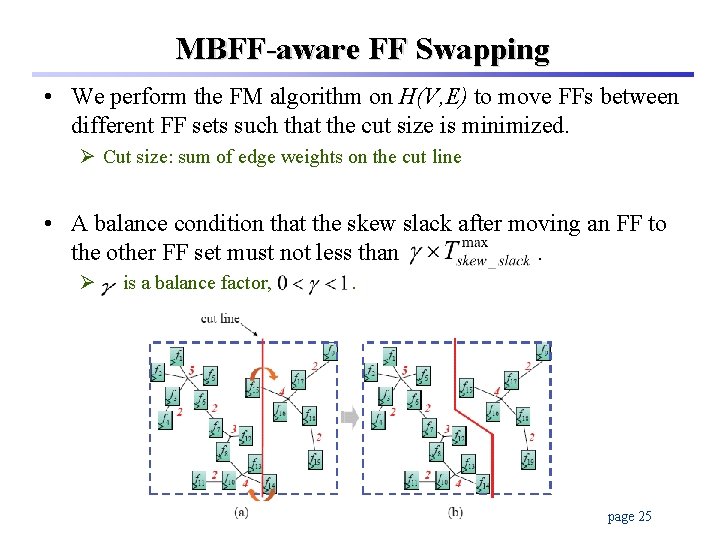

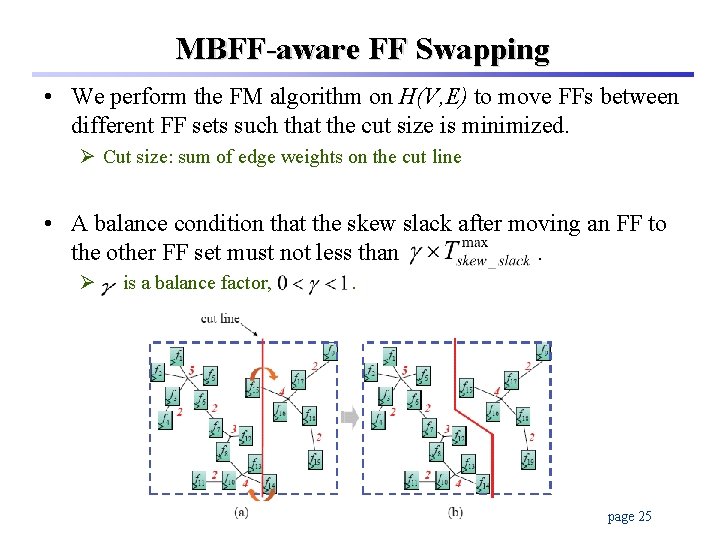

MBFF-aware FF Swapping • We perform the FM algorithm on H(V, E) to move FFs between different FF sets such that the cut size is minimized. Ø Cut size: sum of edge weights on the cut line • A balance condition that the skew slack after moving an FF to the other FF set must not less than. Ø is a balance factor, . page 25

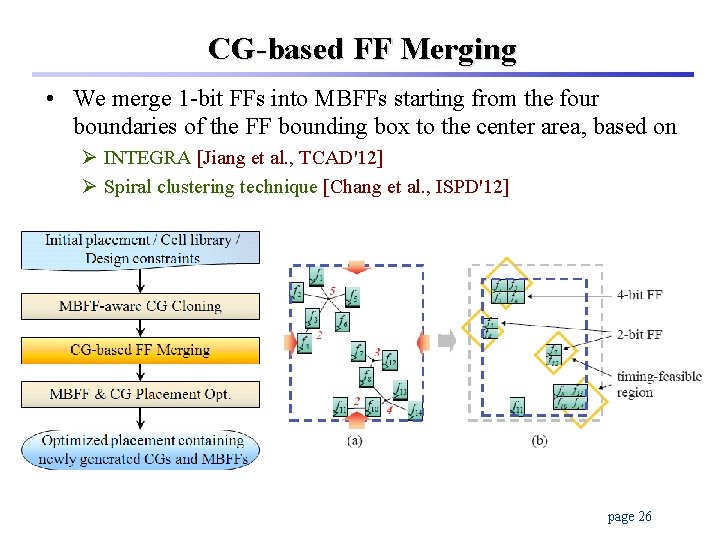

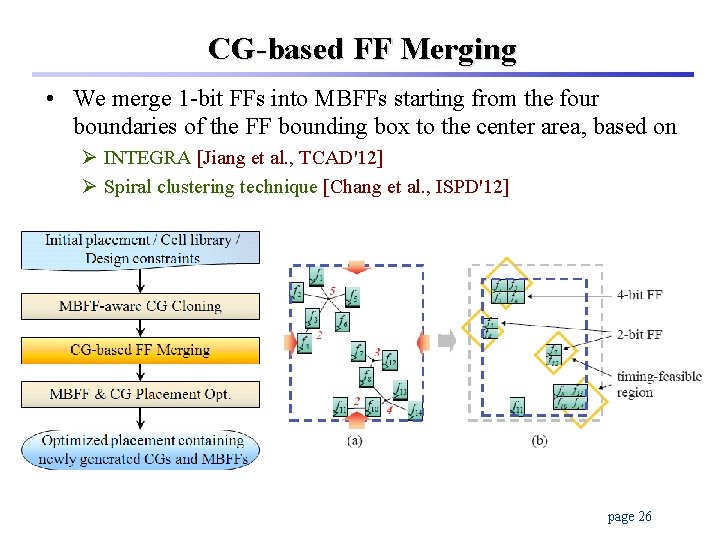

CG-based FF Merging • We merge 1 -bit FFs into MBFFs starting from the four boundaries of the FF bounding box to the center area, based on Ø INTEGRA [Jiang et al. , TCAD'12] Ø Spiral clustering technique [Chang et al. , ISPD'12] page 26

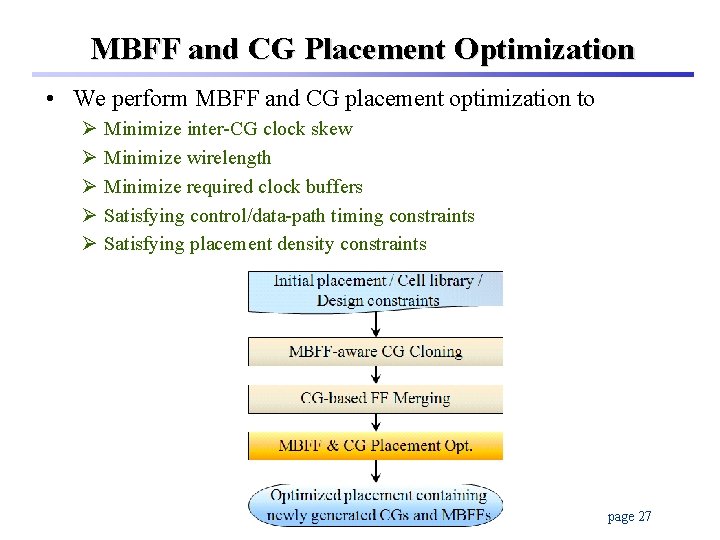

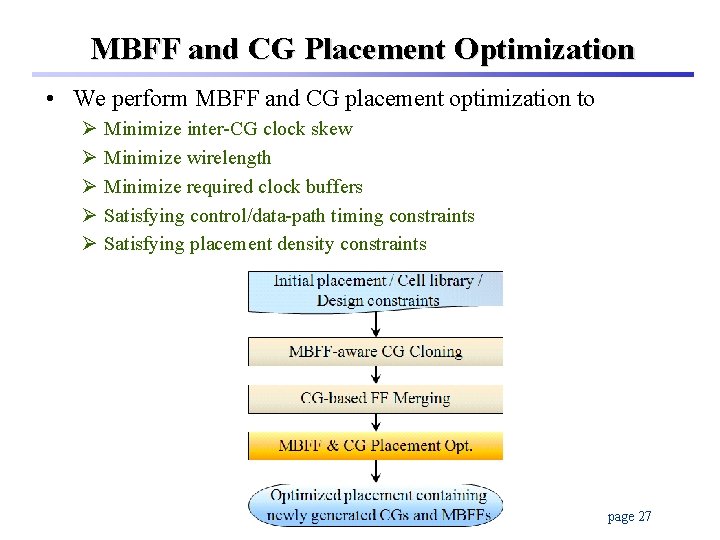

MBFF and CG Placement Optimization • We perform MBFF and CG placement optimization to Ø Ø Ø Minimize inter-CG clock skew Minimize wirelength Minimize required clock buffers Satisfying control/data-path timing constraints Satisfying placement density constraints page 27

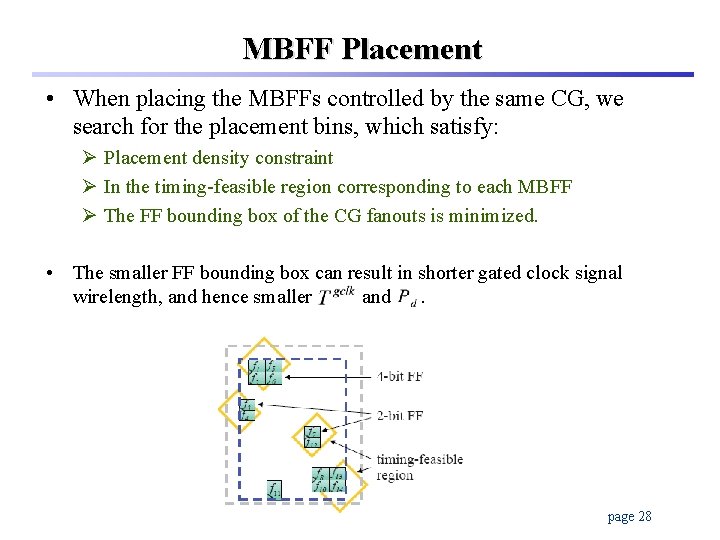

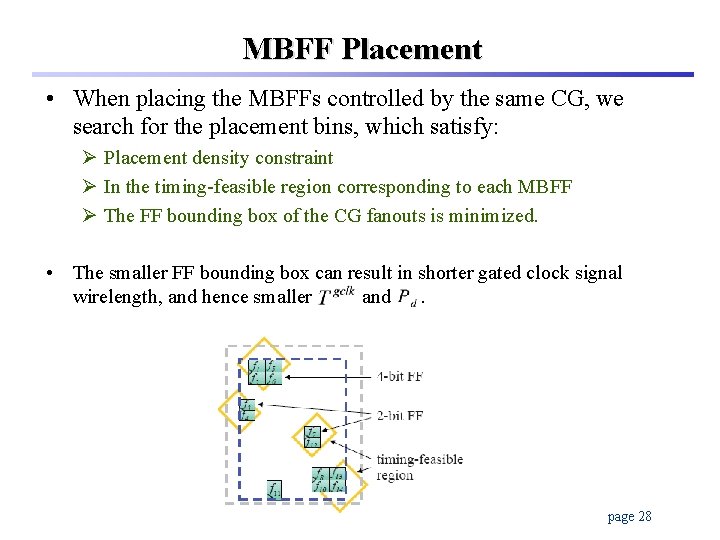

MBFF Placement • When placing the MBFFs controlled by the same CG, we search for the placement bins, which satisfy: Ø Placement density constraint Ø In the timing-feasible region corresponding to each MBFF Ø The FF bounding box of the CG fanouts is minimized. • The smaller FF bounding box can result in shorter gated clock signal wirelength, and hence smaller and. page 28

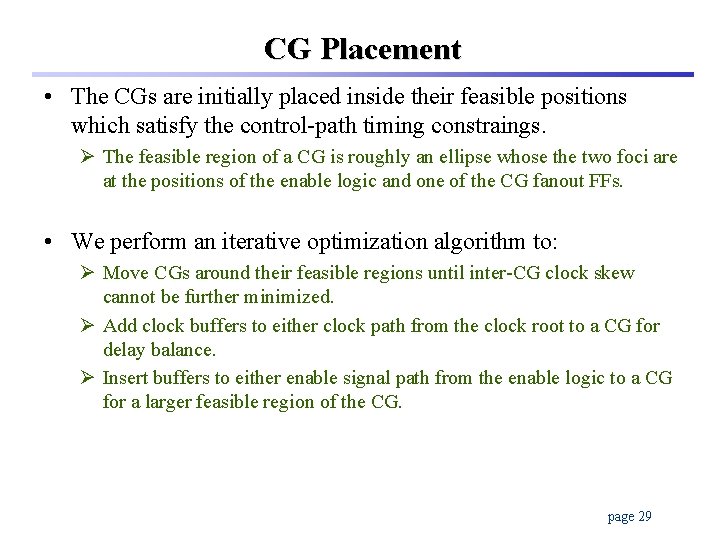

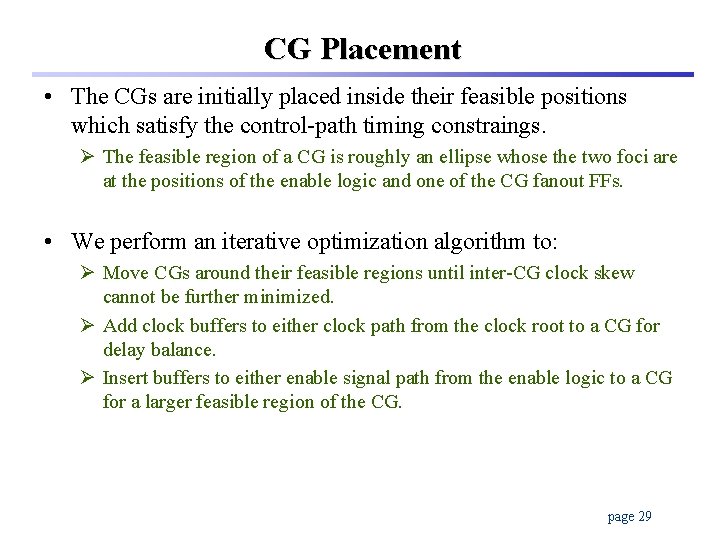

CG Placement • The CGs are initially placed inside their feasible positions which satisfy the control-path timing constraings. Ø The feasible region of a CG is roughly an ellipse whose the two foci are at the positions of the enable logic and one of the CG fanout FFs. • We perform an iterative optimization algorithm to: Ø Move CGs around their feasible regions until inter-CG clock skew cannot be further minimized. Ø Add clock buffers to either clock path from the clock root to a CG for delay balance. Ø Insert buffers to either enable signal path from the enable logic to a CG for a larger feasible region of the CG. page 29

Outline • • Introduction Preliminaries The Proposed Algorithms Experiments Ø Experimental Setups Ø Experimental Comparisons Ø Experimental Results • Conclusions page 30

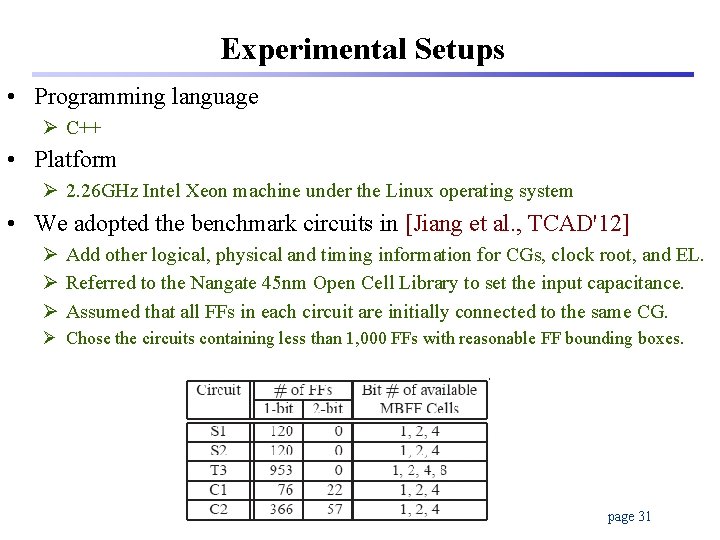

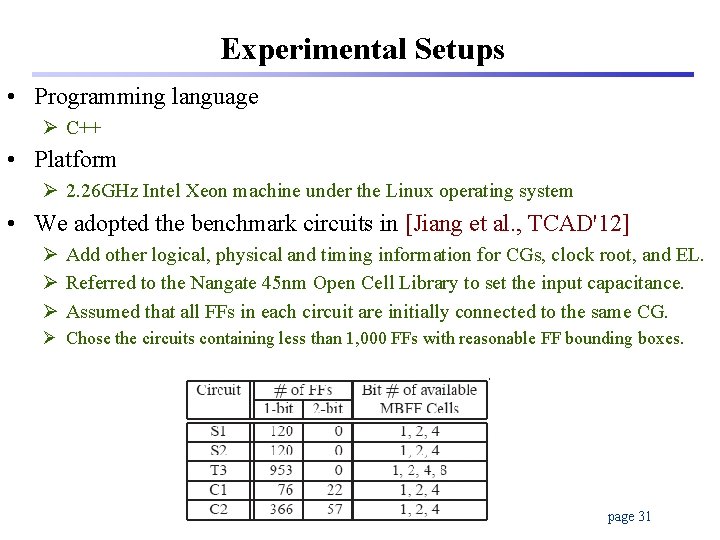

Experimental Setups • Programming language Ø C++ • Platform Ø 2. 26 GHz Intel Xeon machine under the Linux operating system • We adopted the benchmark circuits in [Jiang et al. , TCAD'12] Ø Add other logical, physical and timing information for CGs, clock root, and EL. Ø Referred to the Nangate 45 nm Open Cell Library to set the input capacitance. Ø Assumed that all FFs in each circuit are initially connected to the same CG. Ø Chose the circuits containing less than 1, 000 FFs with reasonable FF bounding boxes. page 31

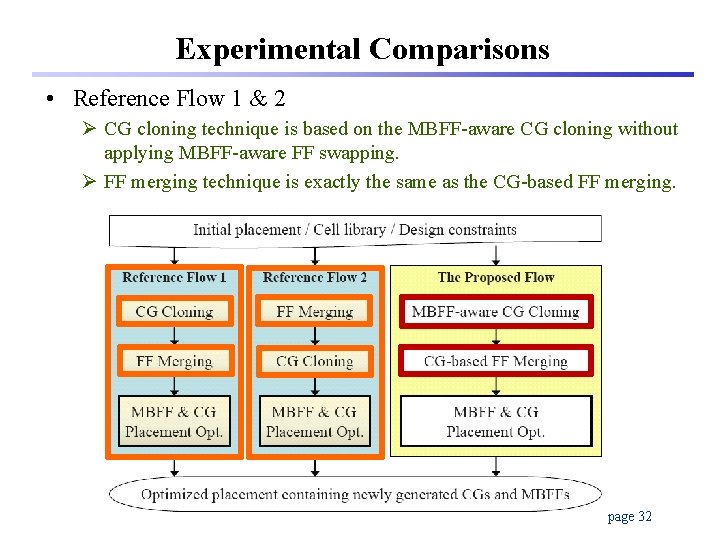

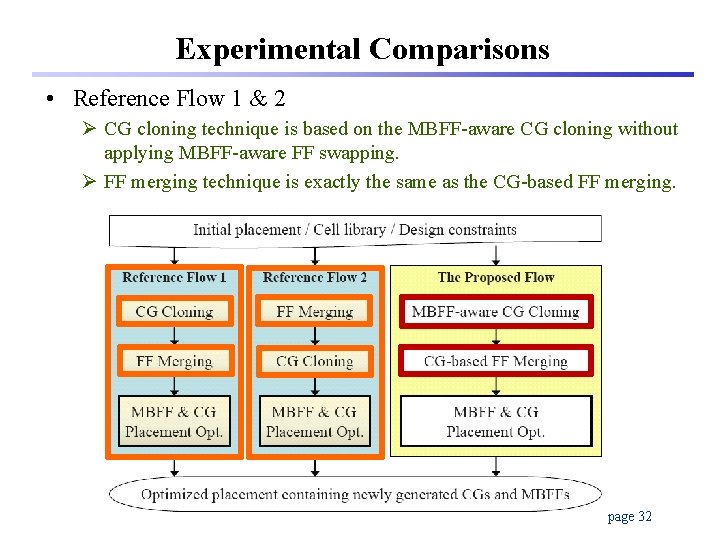

Experimental Comparisons • Reference Flow 1 & 2 Ø CG cloning technique is based on the MBFF-aware CG cloning without applying MBFF-aware FF swapping. Ø FF merging technique is exactly the same as the CG-based FF merging. page 32

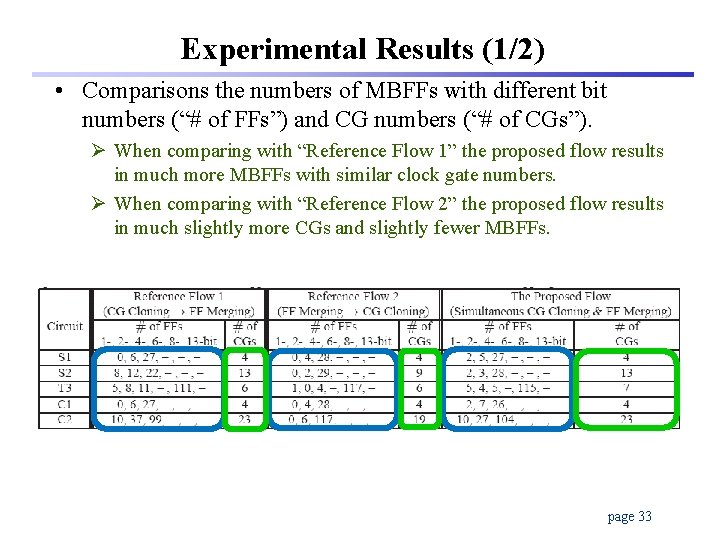

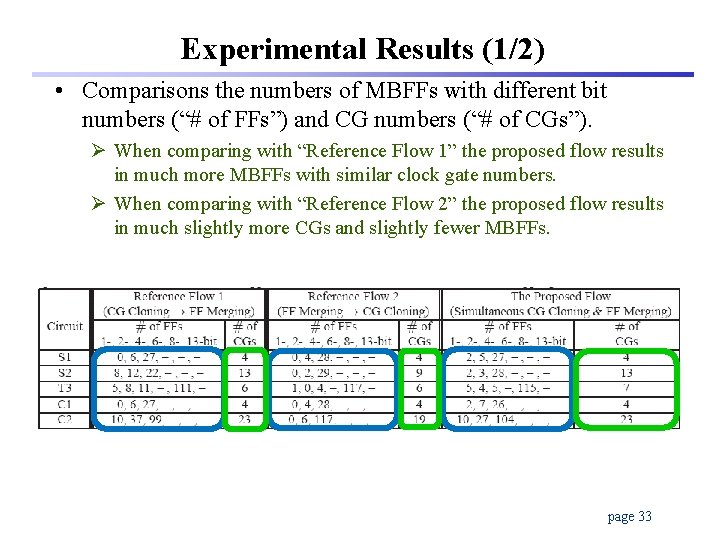

Experimental Results (1/2) • Comparisons the numbers of MBFFs with different bit numbers (“# of FFs”) and CG numbers (“# of CGs”). Ø When comparing with “Reference Flow 1” the proposed flow results in much more MBFFs with similar clock gate numbers. Ø When comparing with “Reference Flow 2” the proposed flow results in much slightly more CGs and slightly fewer MBFFs. page 33

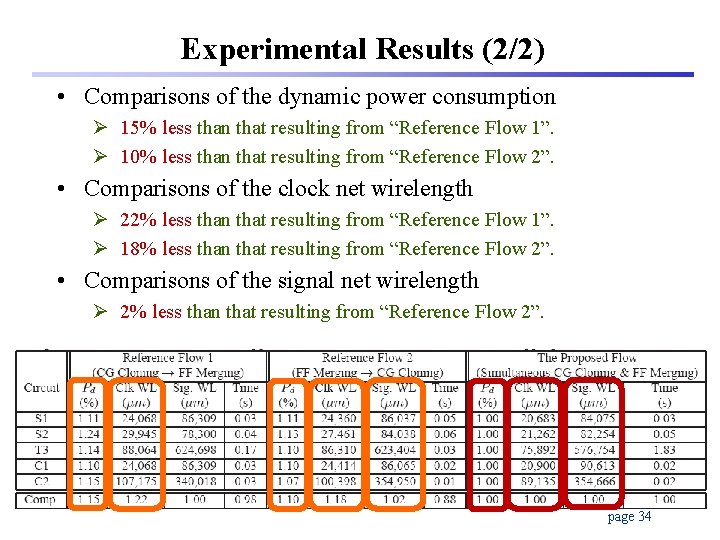

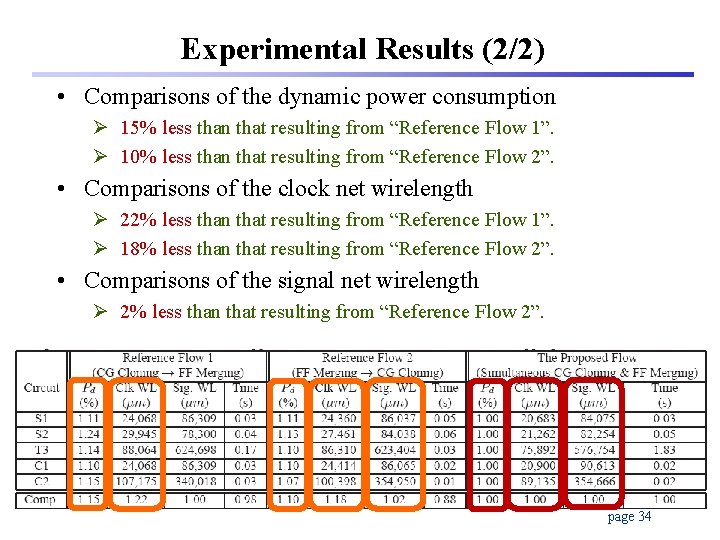

Experimental Results (2/2) • Comparisons of the dynamic power consumption Ø 15% less than that resulting from “Reference Flow 1”. Ø 10% less than that resulting from “Reference Flow 2”. • Comparisons of the clock net wirelength Ø 22% less than that resulting from “Reference Flow 1”. Ø 18% less than that resulting from “Reference Flow 2”. • Comparisons of the signal net wirelength Ø 2% less than that resulting from “Reference Flow 2”. page 34

Outline • • • Introduction Preliminaries The Proposed Algorithms Experimental Results Conclusions page 35

Conclusions • We have presented a new problem formulation for clock network optimization with both CGs and MBFFs. • We have also introduced novel techniques to optimize gated clock network with CG cloning and FF merging simultaneously. • The experimental results have shown that the proposed approach results in better dynamic power and clock wirelength compared with those which optimize gated clock network with CGs and MBFFs separately. page 36

Thanks for Your Attention page 37