Data Strobe DS Encoding Sam Stratton sam strattonaeroflex

Data Strobe (DS) Encoding Sam Stratton sam. stratton@aeroflex. com 2006 MAPLD International Conference Washington, D. C. September 25, 2006 MAPLD International Conference 1 Space. Wire 101 Seminar

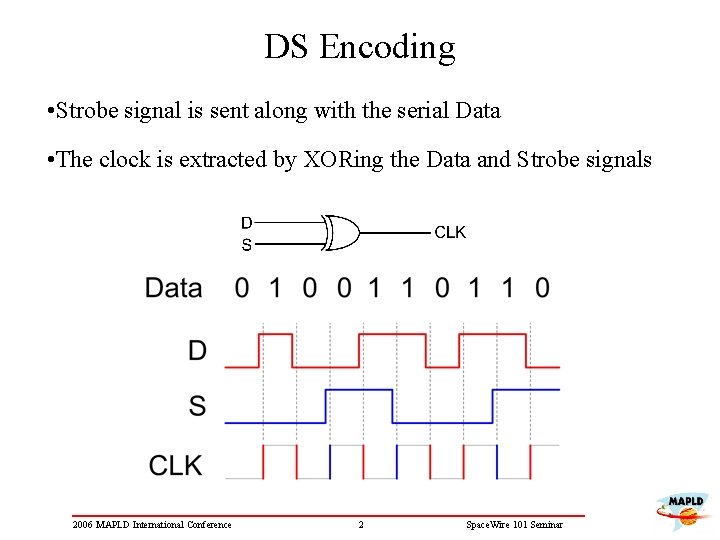

DS Encoding • Strobe signal is sent along with the serial Data • The clock is extracted by XORing the Data and Strobe signals 2006 MAPLD International Conference 2 Space. Wire 101 Seminar

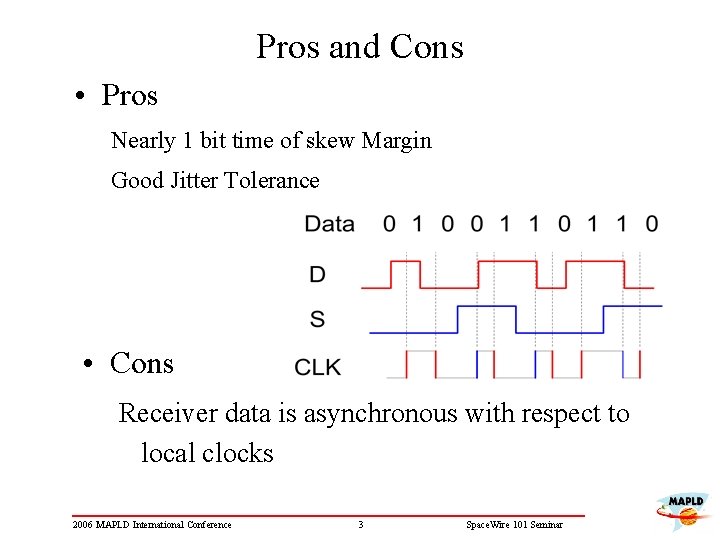

Pros and Cons • Pros Nearly 1 bit time of skew Margin Good Jitter Tolerance • Cons Receiver data is asynchronous with respect to local clocks 2006 MAPLD International Conference 3 Space. Wire 101 Seminar

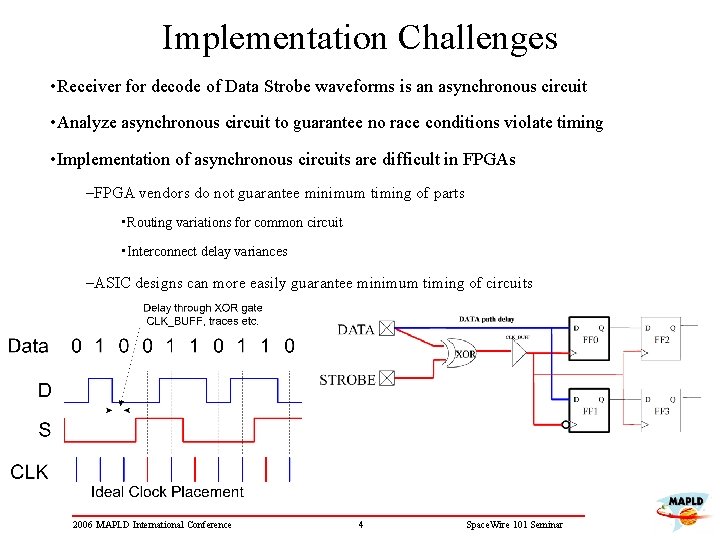

Implementation Challenges • Receiver for decode of Data Strobe waveforms is an asynchronous circuit • Analyze asynchronous circuit to guarantee no race conditions violate timing • Implementation of asynchronous circuits are difficult in FPGAs –FPGA vendors do not guarantee minimum timing of parts • Routing variations for common circuit • Interconnect delay variances –ASIC designs can more easily guarantee minimum timing of circuits 2006 MAPLD International Conference 4 Space. Wire 101 Seminar

DS Circuit Analysis • Only first 2 Flips (FFs) are asynchronous – FF 0 & FF 1 • All other FFs in shift register are synchronous with single clock edge • Timing Checks – Setup • – Hold • – • Data changing Strobe changing Minimum pulse width Conditions – Data changing – Strobe changing DATA path delay DATA D CLK_BUFF Q D FF 0 Q I_3 FF 2 XOR STROBE D Q FF 1 2006 MAPLD International Conference 5 Space. Wire 101 Seminar D Q FF 3

Timing Checks Set-up Time • Setup Checks – Ensure Data that generated the clock arrives before the clock • Blue is faster than Red • T(Data to FF[D]) < T(Data to FF[Clk]) - T(Set-up FF) • For FPGA - use longest path and shortest path together for worst case – Consider rising and falling edge permutations DATA path delay D CLK_BUFF Q D FF 0 Q I_3 FF 2 XOR STROBE D Q FF 1 2006 MAPLD International Conference 6 D Q FF 3 Space. Wire 101 Seminar

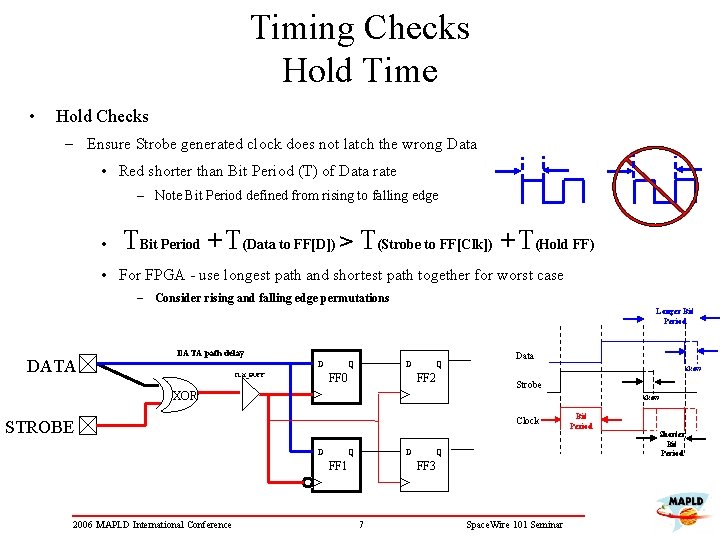

Timing Checks Hold Time • Hold Checks – Ensure Strobe generated clock does not latch the wrong Data • Red shorter than Bit Period (T) of Data rate – Note Bit Period defined from rising to falling edge • TBit Period + T(Data to FF[D]) > T(Strobe to FF[Clk]) + T(Hold FF) • For FPGA - use longest path and shortest path together for worst case – Consider rising and falling edge permutations Longer Bit Period DATA path delay D CLK_BUFF Q D FF 0 Q I_3 FF 2 skew Strobe XOR skew Clock STROBE D Q D FF 1 2006 MAPLD International Conference Data Q FF 3 7 Space. Wire 101 Seminar Bit Period Shorter Bit Period

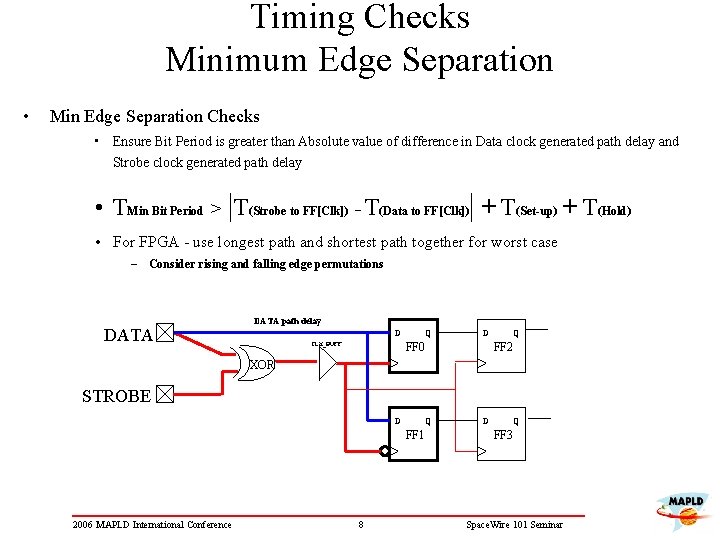

Timing Checks Minimum Edge Separation • Min Edge Separation Checks • Ensure Bit Period is greater than Absolute value of difference in Data clock generated path delay and Strobe clock generated path delay • TMin Bit Period > |T(Strobe to FF[Clk]) - T(Data to FF[Clk])| + T(Set-up) + T(Hold) • For FPGA - use longest path and shortest path together for worst case – Consider rising and falling edge permutations DATA path delay D CLK_BUFF Q D FF 0 Q I_3 FF 2 XOR STROBE D Q FF 1 2006 MAPLD International Conference 8 D Q FF 3 Space. Wire 101 Seminar

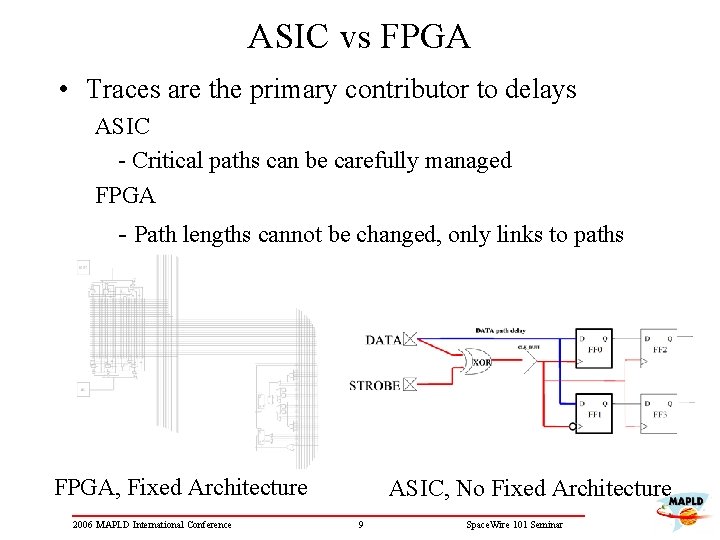

ASIC vs FPGA • Traces are the primary contributor to delays ASIC - Critical paths can be carefully managed FPGA - Path lengths cannot be changed, only links to paths FPGA, Fixed Architecture 2006 MAPLD International Conference ASIC, No Fixed Architecture 9 Space. Wire 101 Seminar

Summary • DS Encoding offers good Skew and jitter margins • Better suited for ASIC Implementations • FPGA Implementations can be facilitated by – offloading the critical timing to an external device – doing worst case timing analysis • use longest and shortest paths together 2006 MAPLD International Conference 10 Space. Wire 101 Seminar

- Slides: 10