CLOCK GENERATION MODULE CGM Clock Generation Module MTT

- Slides: 20

CLOCK GENERATION MODULE (CGM) Clock Generation Module MTT 48 4 -1

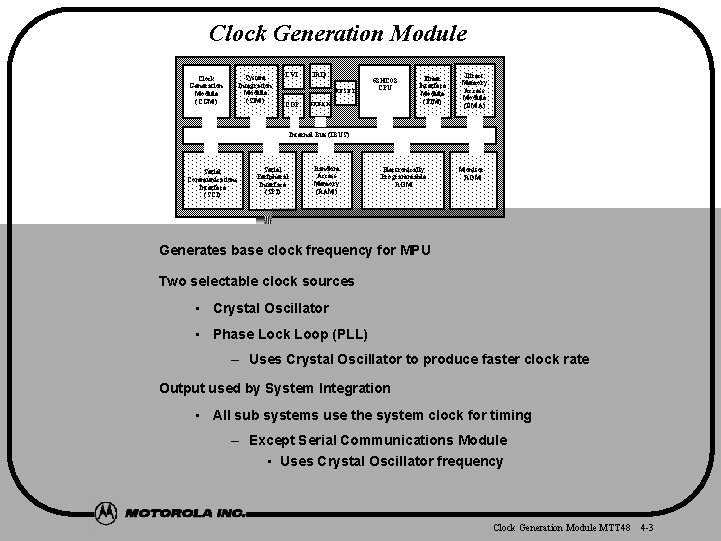

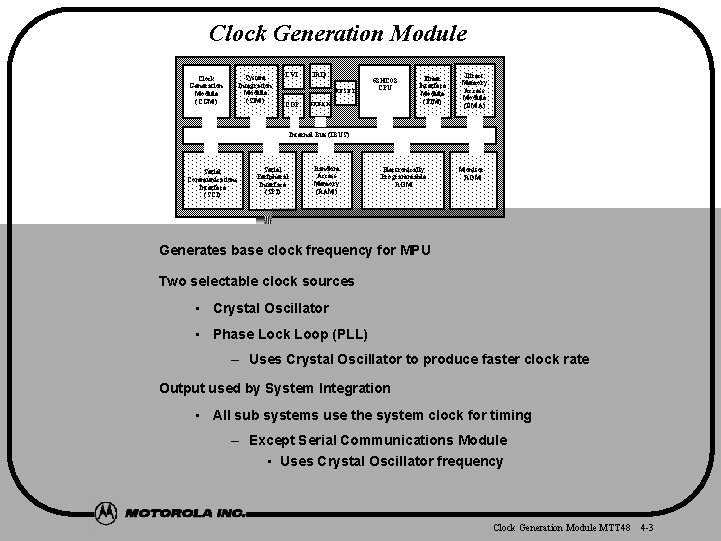

Clock Generation Module System Integration Module (SIM) Clock Generation Module (CGM) LVI IRQ COP BREAK RESET 68 HC 08 CPU Timer Interface Module (TIM) Direct Memory Access Module (DMA) Internal Bus (IBUS) Serial Communications Interface (SCI) Serial Peripheral Interface (SPI) Random Access Memory (RAM) Electronically Programmable ROM Monitor ROM Generates base clock frequency for MPU Two selectable clock sources • Crystal Oscillator • Phase Lock Loop (PLL) – Uses Crystal Oscillator to produce faster clock rate Output used by System Integration • All sub systems use the system clock for timing – Except Serial Communications Module • Uses Crystal Oscillator frequency Clock Generation Module MTT 48 4 -3

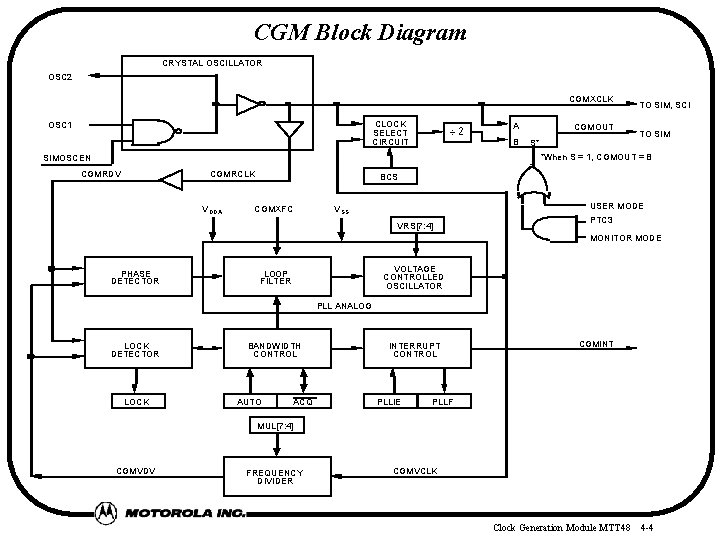

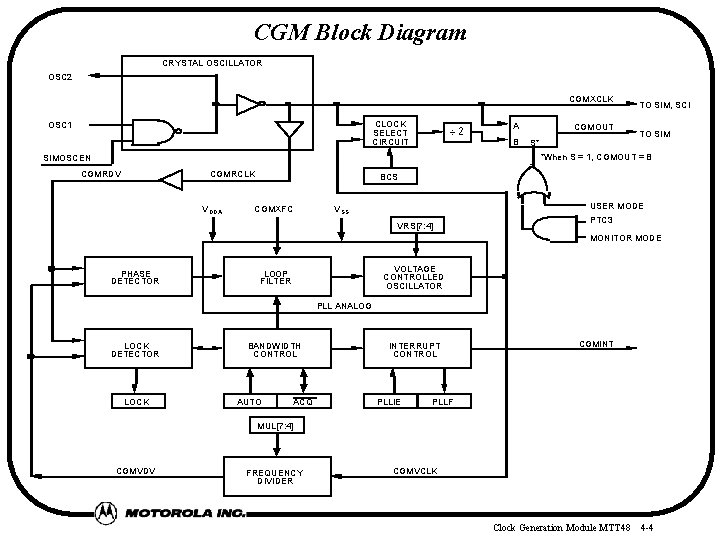

CGM Block Diagram CRYSTAL OSCILLATOR OSC 2 CGMXCLK CLOCK SELECT CIRCUIT OSC 1 A B CGMOUT S* TO SIM, SCI TO SIM *When S = 1, CGMOUT = B SIMOSCEN CGMRDV CGMRCLK V DDA BCS CGMXFC USER MODE V SS VRS[7: 4] PTC 3 MONITOR MODE PHASE DETECTOR VOLTAGE CONTROLLED OSCILLATOR LOOP FILTER PLL ANALOG LOCK DETECTOR LOCK BANDWIDTH CONTROL AUTO ACQ INTERRUPT CONTROL PLLIE CGMINT PLLF MUL[7: 4] CGMVDV FREQUENCY DIVIDER CGMVCLK Clock Generation Module MTT 48 4 -4

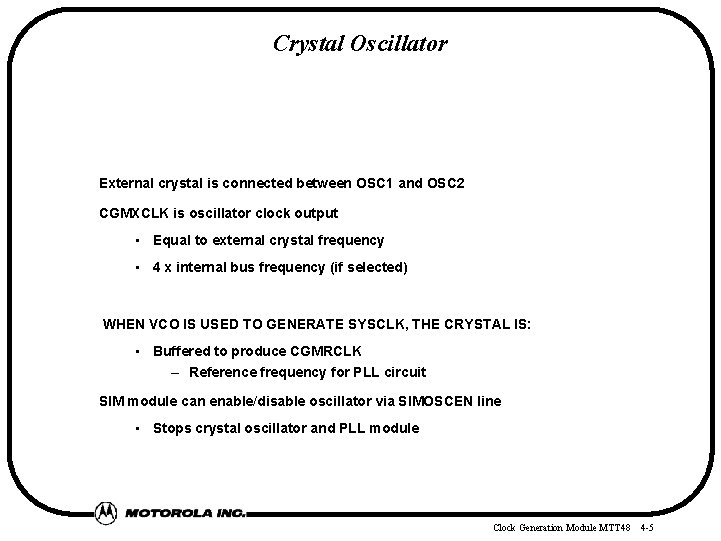

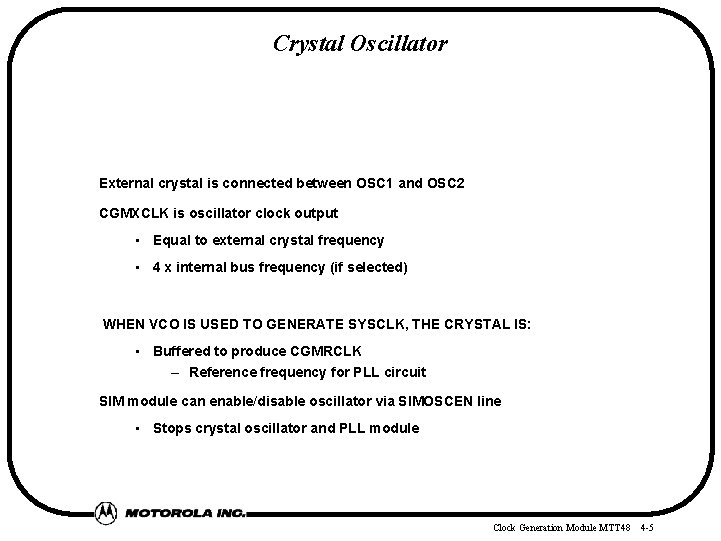

Crystal Oscillator External crystal is connected between OSC 1 and OSC 2 CGMXCLK is oscillator clock output • Equal to external crystal frequency • 4 x internal bus frequency (if selected) WHEN VCO IS USED TO GENERATE SYSCLK, THE CRYSTAL IS: • Buffered to produce CGMRCLK – Reference frequency for PLL circuit SIM module can enable/disable oscillator via SIMOSCEN line • Stops crystal oscillator and PLL module Clock Generation Module MTT 48 4 -5

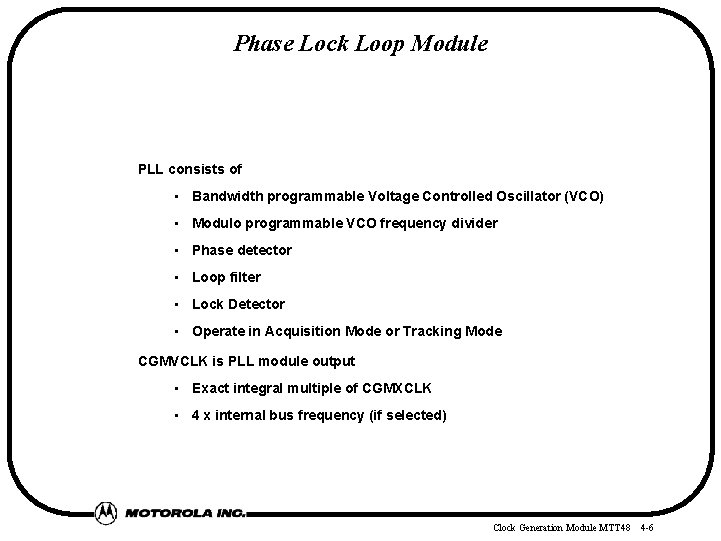

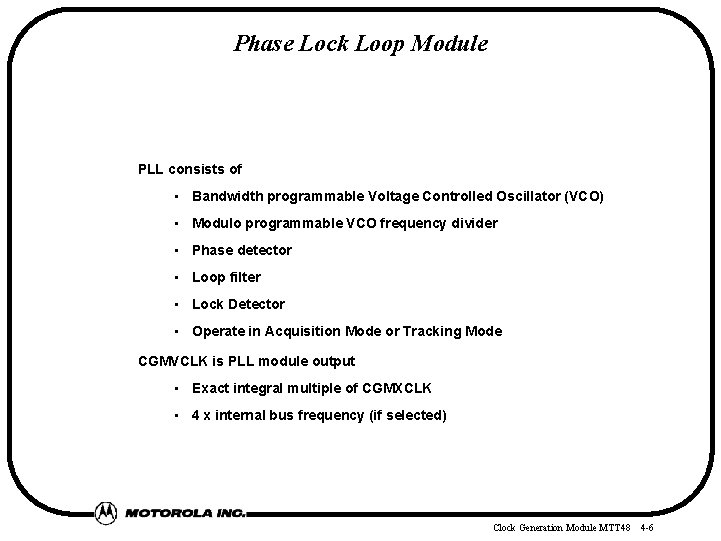

Phase Lock Loop Module PLL consists of • Bandwidth programmable Voltage Controlled Oscillator (VCO) • Modulo programmable VCO frequency divider • Phase detector • Loop filter • Lock Detector • Operate in Acquisition Mode or Tracking Mode CGMVCLK is PLL module output • Exact integral multiple of CGMXCLK • 4 x internal bus frequency (if selected) Clock Generation Module MTT 48 4 -6

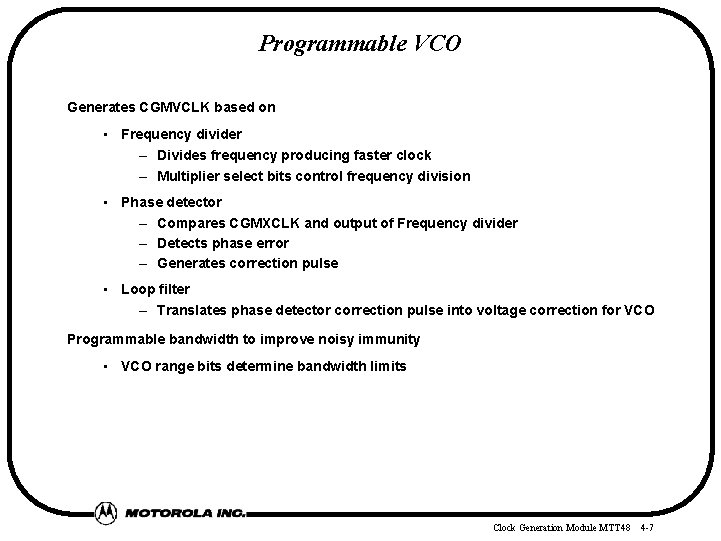

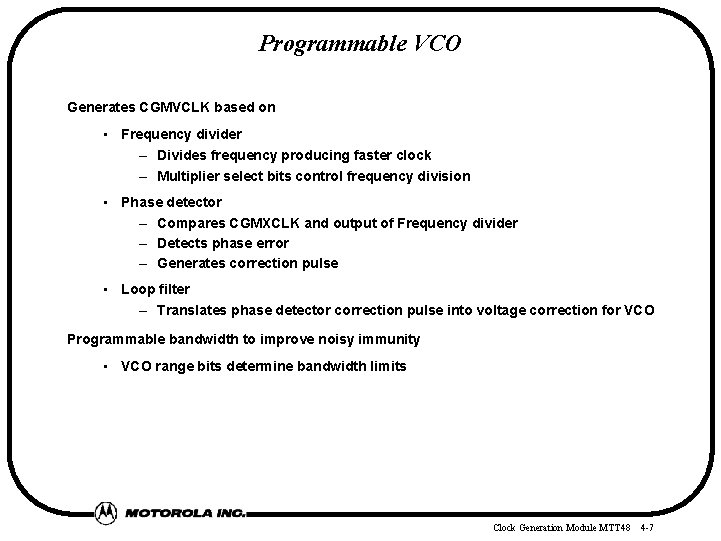

Programmable VCO Generates CGMVCLK based on • Frequency divider – Divides frequency producing faster clock – Multiplier select bits control frequency division • Phase detector – Compares CGMXCLK and output of Frequency divider – Detects phase error – Generates correction pulse • Loop filter – Translates phase detector correction pulse into voltage correction for VCO Programmable bandwidth to improve noisy immunity • VCO range bits determine bandwidth limits Clock Generation Module MTT 48 4 -7

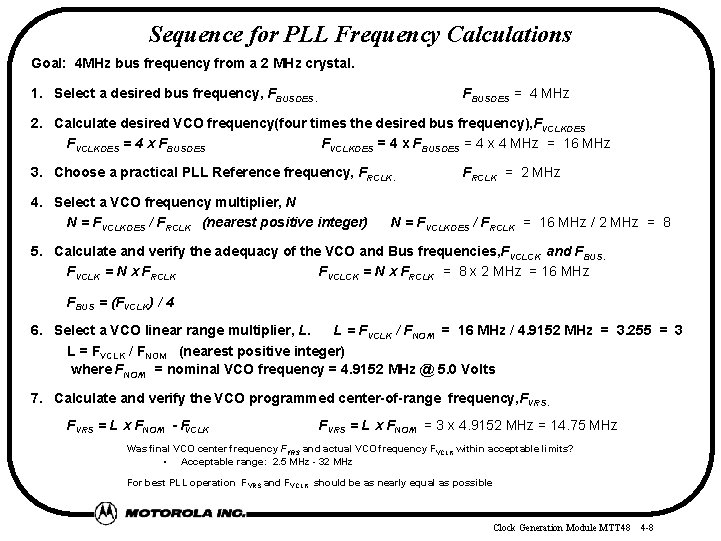

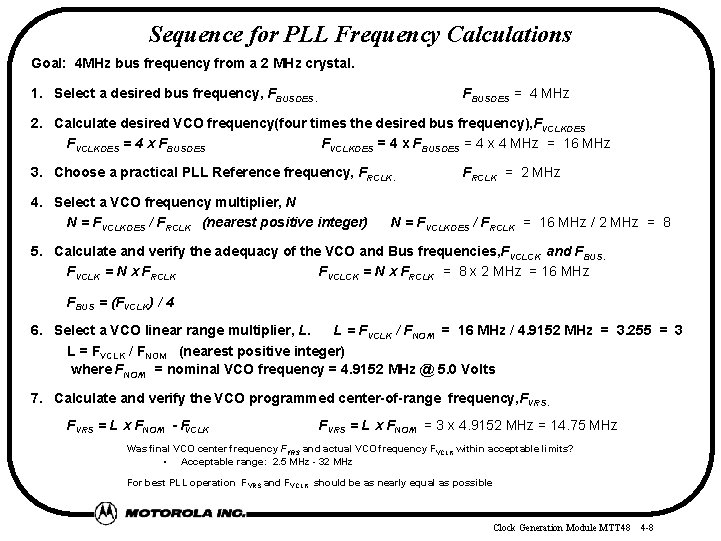

Sequence for PLL Frequency Calculations Goal: 4 MHz bus frequency from a 2 MHz crystal. 1. Select a desired bus frequency, FBUSDES = 4 MHz 2. Calculate desired VCO frequency(four times the desired bus frequency), FVCLKDES = 4 x FBUSDES = 4 x 4 MHz = 16 MHz 3. Choose a practical PLL Reference frequency, FRCLK. 4. Select a VCO frequency multiplier, N N = FVCLKDES / FRCLK (nearest positive integer) FRCLK = 2 MHz N = FVCLKDES / FRCLK = 16 MHz / 2 MHz = 8 5. Calculate and verify the adequacy of the VCO and Bus frequencies, FVCLCK and FBUS. FVCLK = N x FRCLK FVCLCK = N x FRCLK = 8 x 2 MHz = 16 MHz FBUS = (FVCLK) / 4 6. Select a VCO linear range multiplier, L. L = FVCLK / FNOM = 16 MHz / 4. 9152 MHz = 3. 255 = 3 L = FVCLK / FNOM (nearest positive integer) where FNOM = nominal VCO frequency = 4. 9152 MHz @ 5. 0 Volts 7. Calculate and verify the VCO programmed center-of-range frequency, FVRS = L x FNOM FVCLK FVRS = L x FNOM = 3 x 4. 9152 MHz = 14. 75 MHz Was final VCO center frequency FVRS and actual VCO frequency FVCLK within acceptable limits? • Acceptable range: 2. 5 MHz - 32 MHz For best PLL operation FVRS and FVCLK should be as nearly equal as possible Clock Generation Module MTT 48 4 -8

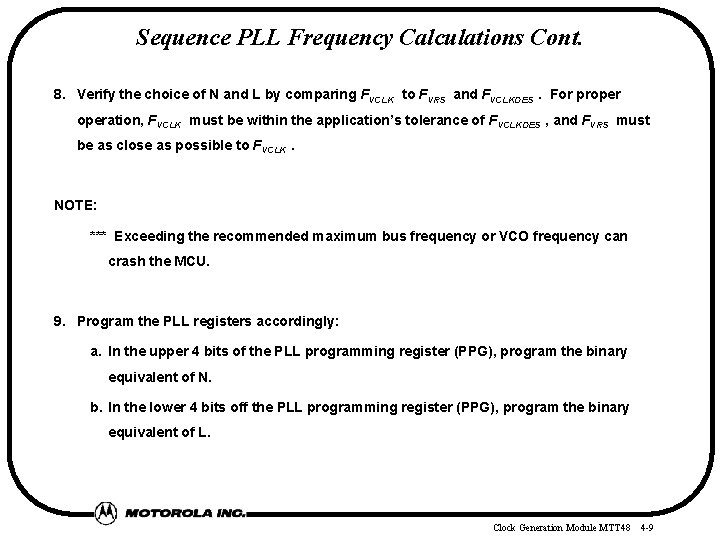

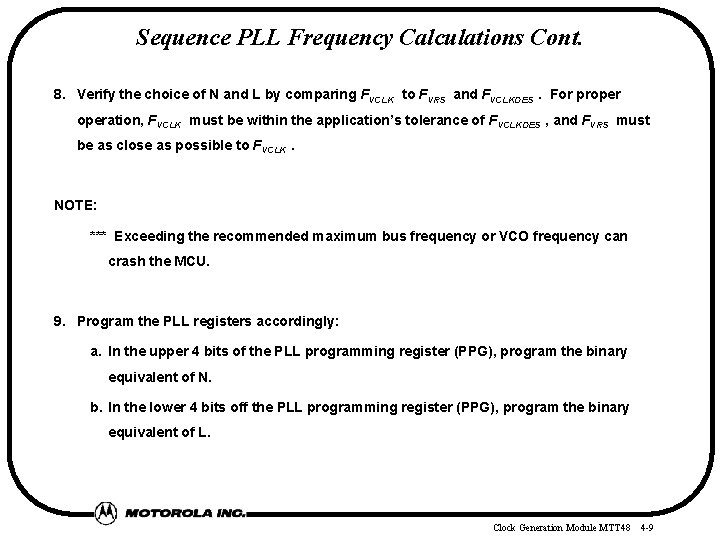

Sequence PLL Frequency Calculations Cont. 8. Verify the choice of N and L by comparing FVCLK to FVRS and FVCLKDES. For properation, FVCLK must be within the application’s tolerance of FVCLKDES , and FVRS must be as close as possible to FVCLK. NOTE: *** Exceeding the recommended maximum bus frequency or VCO frequency can crash the MCU. 9. Program the PLL registers accordingly: a. In the upper 4 bits of the PLL programming register (PPG), program the binary equivalent of N. b. In the lower 4 bits off the PLL programming register (PPG), program the binary equivalent of L. Clock Generation Module MTT 48 4 -9

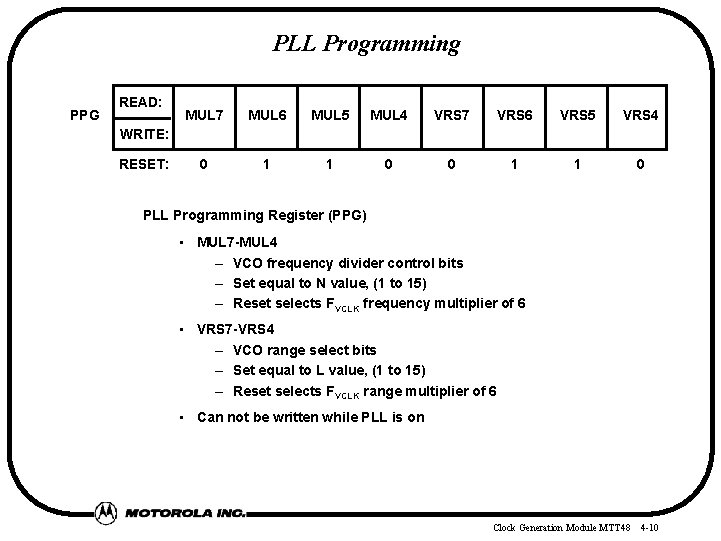

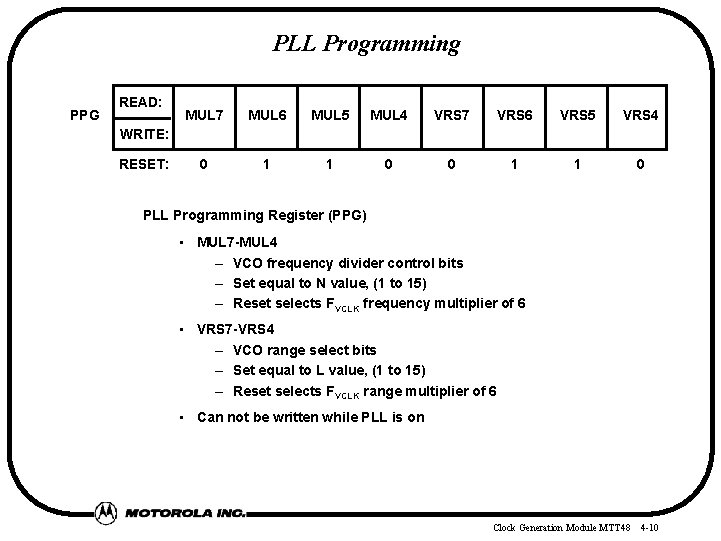

PLL Programming PPG READ: MUL 7 MUL 6 MUL 5 MUL 4 VRS 7 VRS 6 VRS 5 VRS 4 0 1 1 0 WRITE: RESET: PLL Programming Register (PPG) • MUL 7 -MUL 4 – VCO frequency divider control bits – Set equal to N value, (1 to 15) – Reset selects FVCLK frequency multiplier of 6 • VRS 7 -VRS 4 – VCO range select bits – Set equal to L value, (1 to 15) – Reset selects FVCLK range multiplier of 6 • Can not be written while PLL is on Clock Generation Module MTT 48 4 -10

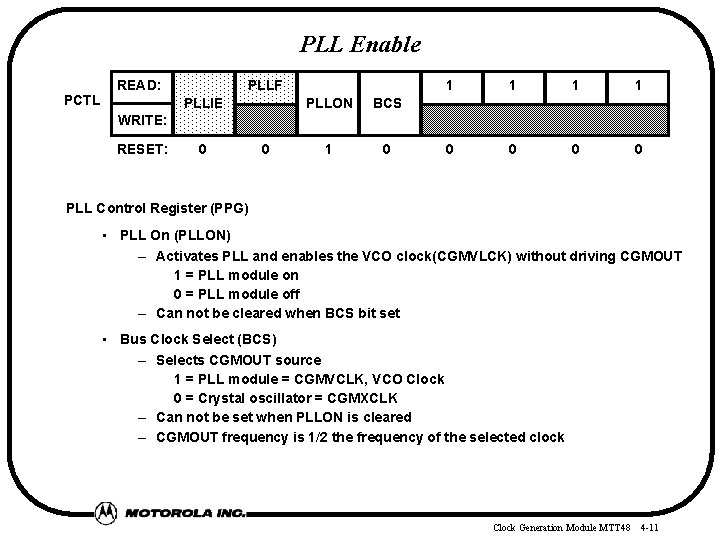

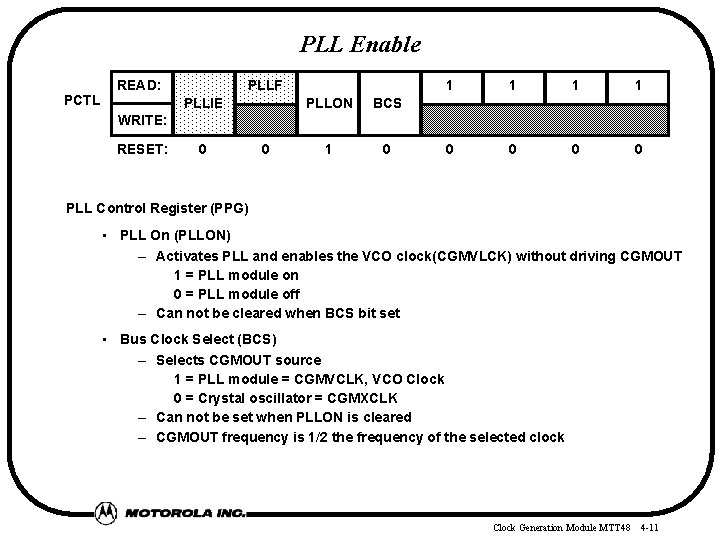

PLL Enable PCTL READ: PLLF PLLIE PLLON BCS 1 0 1 1 0 0 WRITE: RESET: 0 0 PLL Control Register (PPG) • PLL On (PLLON) – Activates PLL and enables the VCO clock(CGMVLCK) without driving CGMOUT 1 = PLL module on 0 = PLL module off – Can not be cleared when BCS bit set • Bus Clock Select (BCS) – Selects CGMOUT source 1 = PLL module = CGMVCLK, VCO Clock 0 = Crystal oscillator = CGMXCLK – Can not be set when PLLON is cleared – CGMOUT frequency is 1/2 the frequency of the selected clock Clock Generation Module MTT 48 4 -11

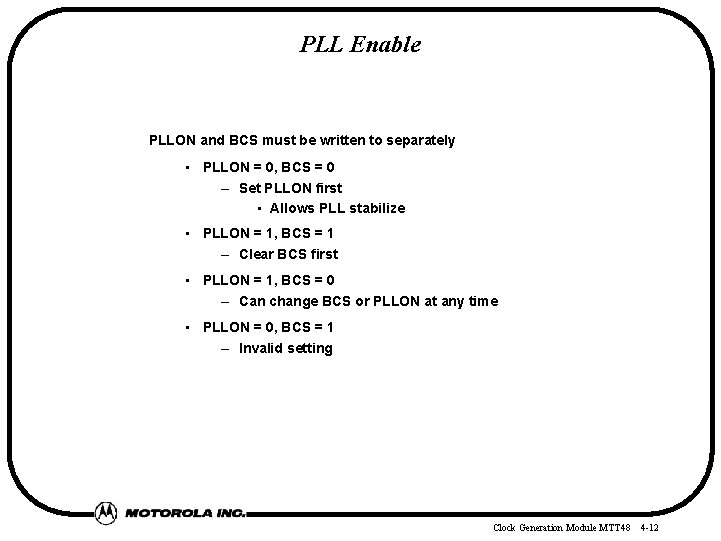

PLL Enable PLLON and BCS must be written to separately • PLLON = 0, BCS = 0 – Set PLLON first • Allows PLL stabilize • PLLON = 1, BCS = 1 – Clear BCS first • PLLON = 1, BCS = 0 – Can change BCS or PLLON at any time • PLLON = 0, BCS = 1 – Invalid setting Clock Generation Module MTT 48 4 -12

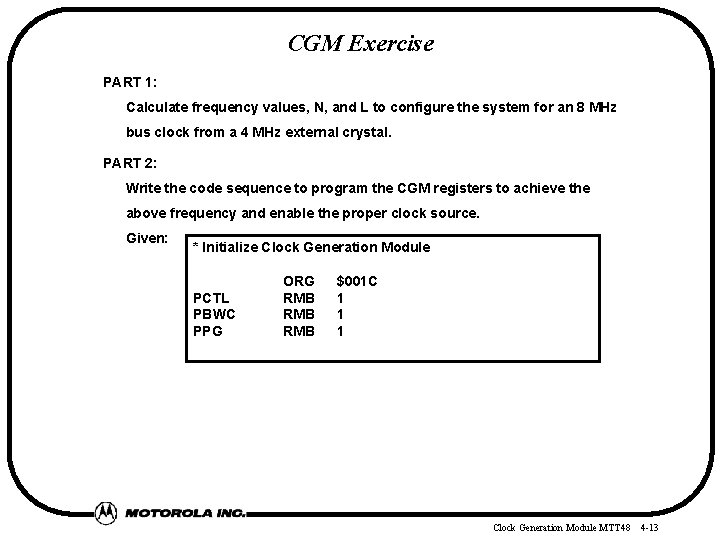

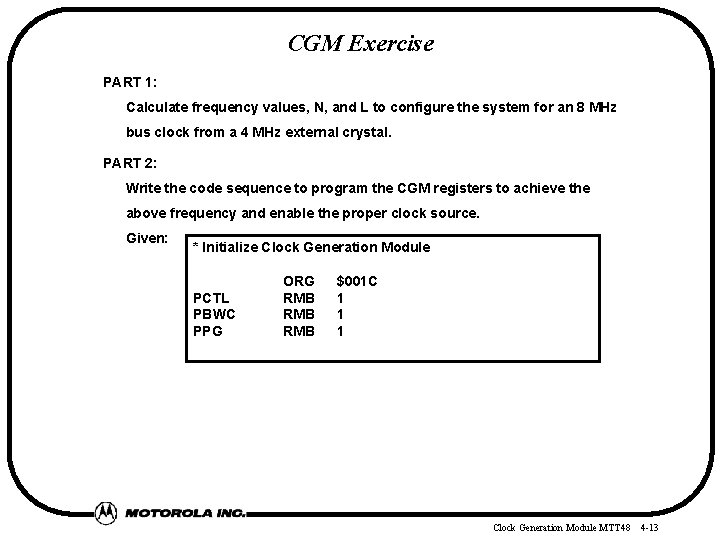

CGM Exercise PART 1: Calculate frequency values, N, and L to configure the system for an 8 MHz bus clock from a 4 MHz external crystal. PART 2: Write the code sequence to program the CGM registers to achieve the above frequency and enable the proper clock source. Given: * Initialize Clock Generation Module PCTL PBWC PPG ORG RMB RMB $001 C 1 1 1 Clock Generation Module MTT 48 4 -13

Additional Information - Acquisition vs Tracking - Acquisition Mode • Large frequency corrections required to PLL module • Frequency is not locked in Tracking Mode • VCO frequency is near programmed frequency, small corrections required • Frequency is locked in Clock Generation Module MTT 48 4 -14

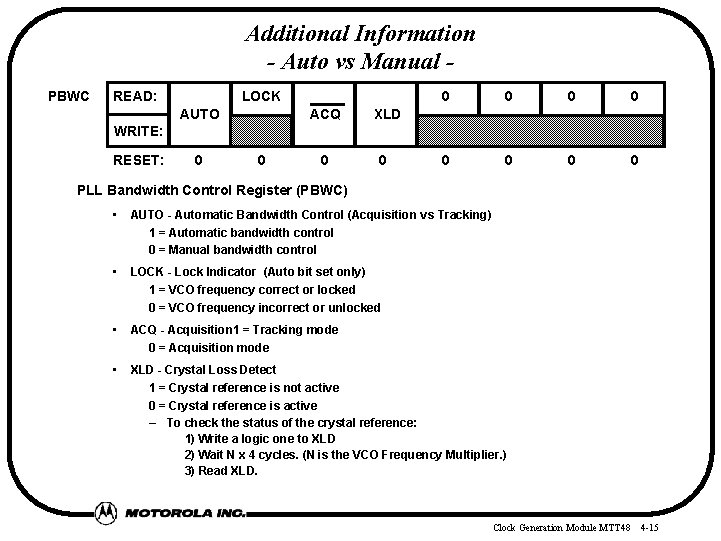

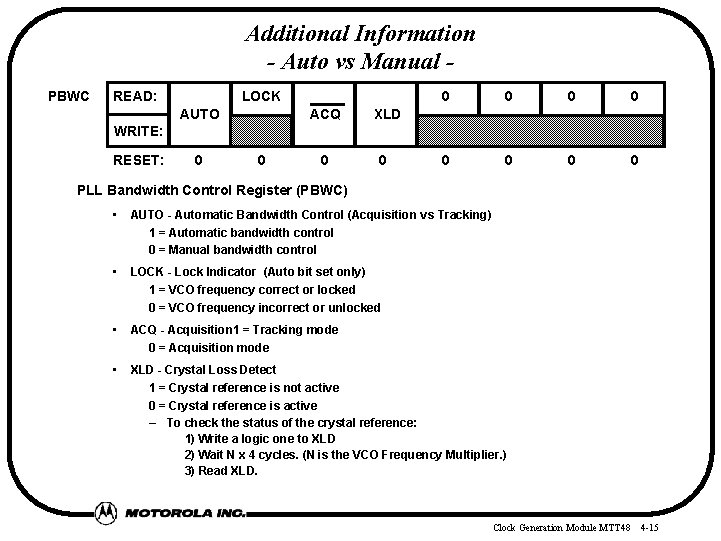

Additional Information - Auto vs Manual PBWC READ: LOCK AUTO ACQ 0 0 0 0 XLD WRITE: RESET: 0 0 PLL Bandwidth Control Register (PBWC) • AUTO - Automatic Bandwidth Control (Acquisition vs Tracking) 1 = Automatic bandwidth control 0 = Manual bandwidth control • LOCK - Lock Indicator (Auto bit set only) 1 = VCO frequency correct or locked 0 = VCO frequency incorrect or unlocked • ACQ - Acquisition 1 = Tracking mode 0 = Acquisition mode • XLD - Crystal Loss Detect 1 = Crystal reference is not active 0 = Crystal reference is active – To check the status of the crystal reference: 1) Write a logic one to XLD 2) Wait N x 4 cycles. (N is the VCO Frequency Multiplier. ) 3) Read XLD. Clock Generation Module MTT 48 4 -15

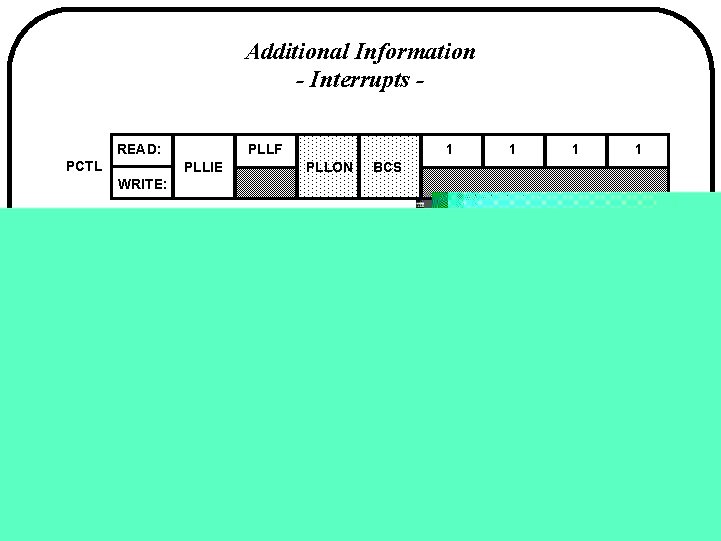

Additional Information - Interrupts READ: PCTL PLLF PLLIE PLLON BCS 1 0 1 1 1 1 WRITE: RESET: 0 0 PLL Control Register(PCTL) • PLL Interrupt Enable (PLLIE) – Enables CPU interrupt when LOCK bit changes – Disabled when in manual mode • PLL Interrupt Flag (PLLF) – Becomes set when PLL enters or leaves locked state Clock Generation Module MTT 48 4 -16

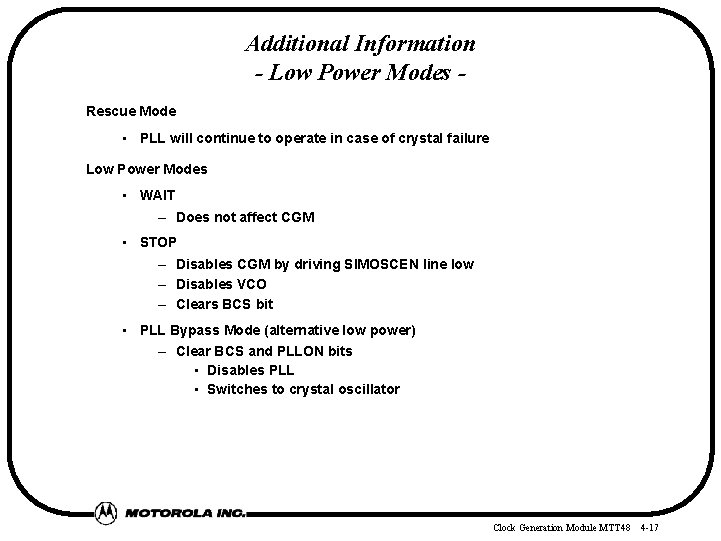

Additional Information - Low Power Modes Rescue Mode • PLL will continue to operate in case of crystal failure Low Power Modes • WAIT – Does not affect CGM • STOP – Disables CGM by driving SIMOSCEN line low – Disables VCO – Clears BCS bit • PLL Bypass Mode (alternative low power) – Clear BCS and PLLON bits • Disables PLL • Switches to crystal oscillator Clock Generation Module MTT 48 4 -17

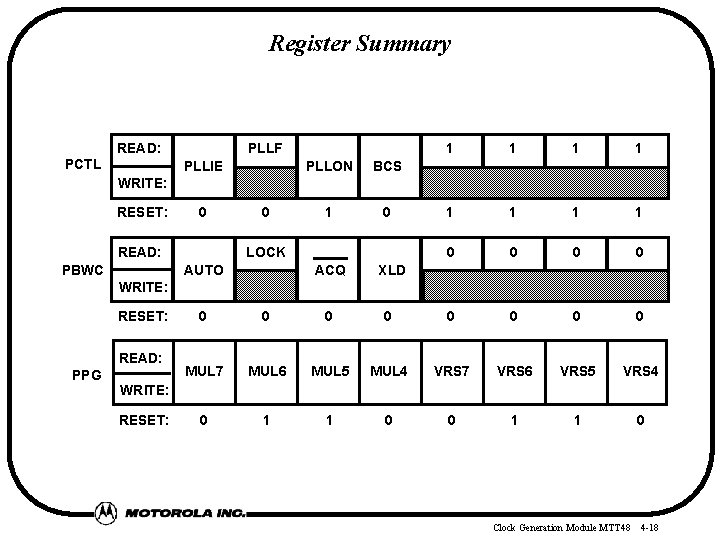

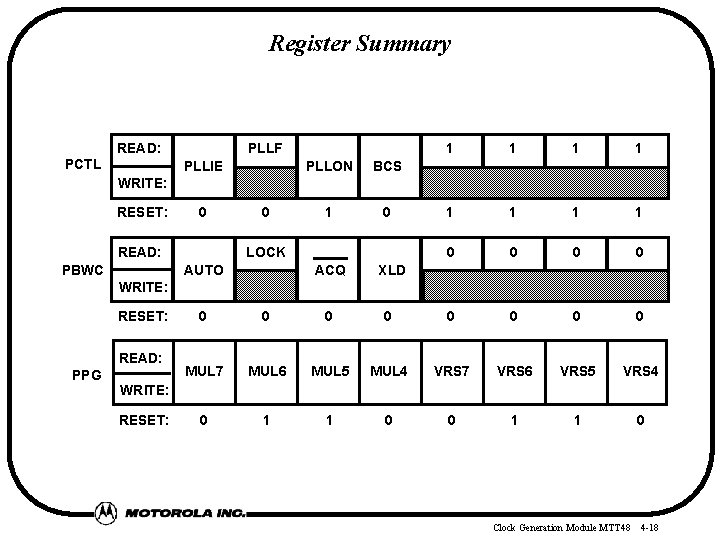

Register Summary READ: PCTL PLLF PLLIE PLLON BCS 1 0 1 1 1 1 0 0 WRITE: RESET: 0 READ: 0 LOCK AUTO PBWC ACQ XLD WRITE: RESET: READ: PPG 0 0 0 0 MUL 7 MUL 6 MUL 5 MUL 4 VRS 7 VRS 6 VRS 5 VRS 4 0 1 1 0 WRITE: RESET: Clock Generation Module MTT 48 4 -18

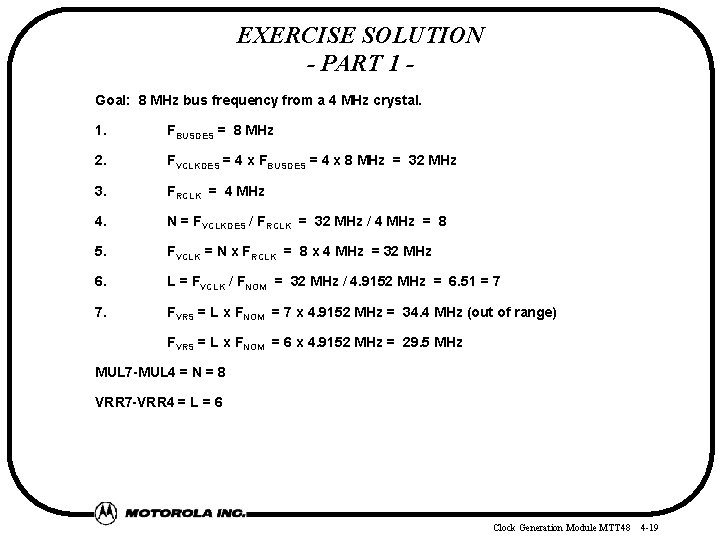

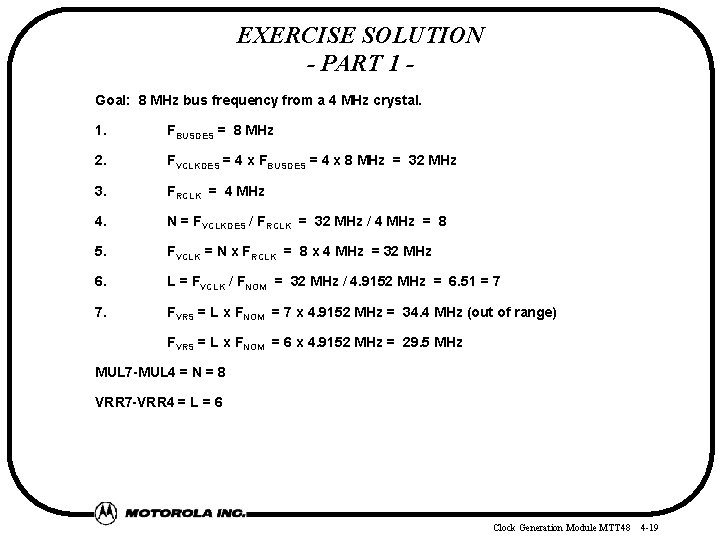

EXERCISE SOLUTION - PART 1 Goal: 8 MHz bus frequency from a 4 MHz crystal. 1. FBUSDES = 8 MHz 2. FVCLKDES = 4 x FBUSDES = 4 x 8 MHz = 32 MHz 3. FRCLK = 4 MHz 4. N = FVCLKDES / FRCLK = 32 MHz / 4 MHz = 8 5. FVCLK = N x FRCLK = 8 x 4 MHz = 32 MHz 6. L = FVCLK / FNOM = 32 MHz / 4. 9152 MHz = 6. 51 = 7 7. FVRS = L x FNOM = 7 x 4. 9152 MHz = 34. 4 MHz (out of range) FVRS = L x FNOM = 6 x 4. 9152 MHz = 29. 5 MHz MUL 7 -MUL 4 = N = 8 VRR 7 -VRR 4 = L = 6 Clock Generation Module MTT 48 4 -19

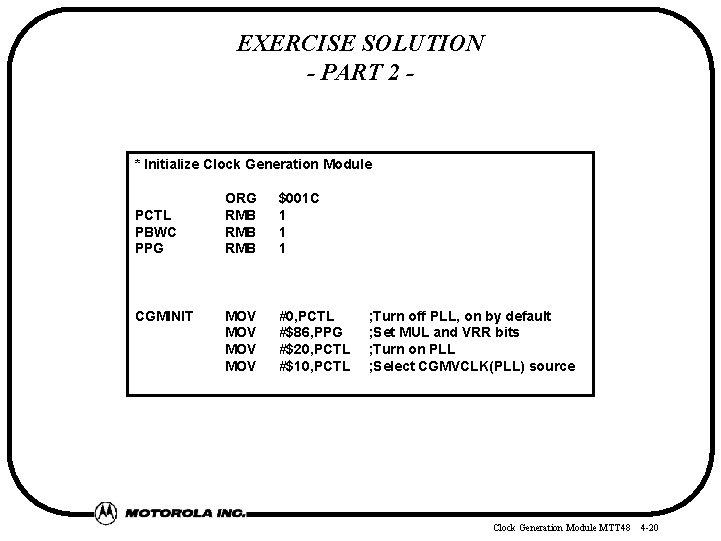

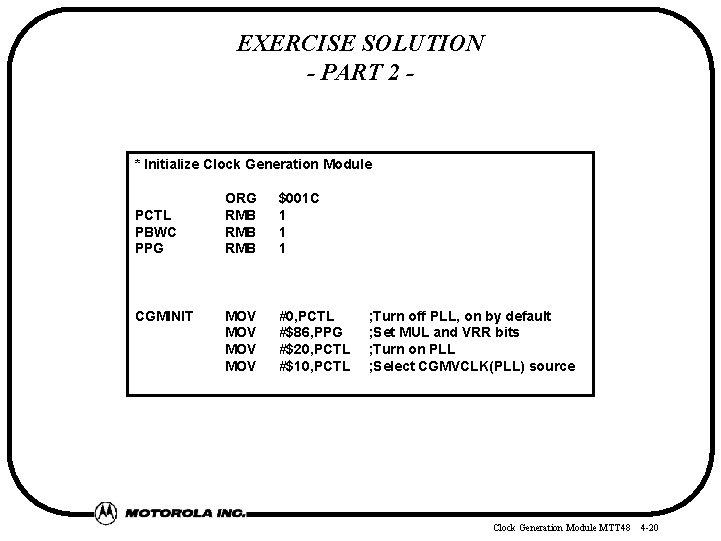

EXERCISE SOLUTION - PART 2 - * Initialize Clock Generation Module PCTL PBWC PPG CGMINIT ORG RMB RMB $001 C 1 1 1 MOV MOV #0, PCTL #$86, PPG #$20, PCTL #$10, PCTL ; Turn off PLL, on by default ; Set MUL and VRR bits ; Turn on PLL ; Select CGMVCLK(PLL) source Clock Generation Module MTT 48 4 -20