TIMER INTERFACE MODULE TIM Timer Interface Module MTT

- Slides: 44

TIMER INTERFACE MODULE (TIM) Timer Interface Module MTT 48 9 - 1

Module Objectives Understand input capture function Understand output compare function Understand pulse width modulation functions Program TIM free running reference clock and options Configure any TIM channel as either: • Input capture • Output compare • PWM TIM Module Exercises Initialize TIM and timer reference counter for 250 ns resolution from 8 MHz system clock Configure channel 1 as input capture Configure channel 2 as output compare Configure channel 3 as buffered 75% duty cycle PWM Timer Interface Module MTT 48 9 - 2

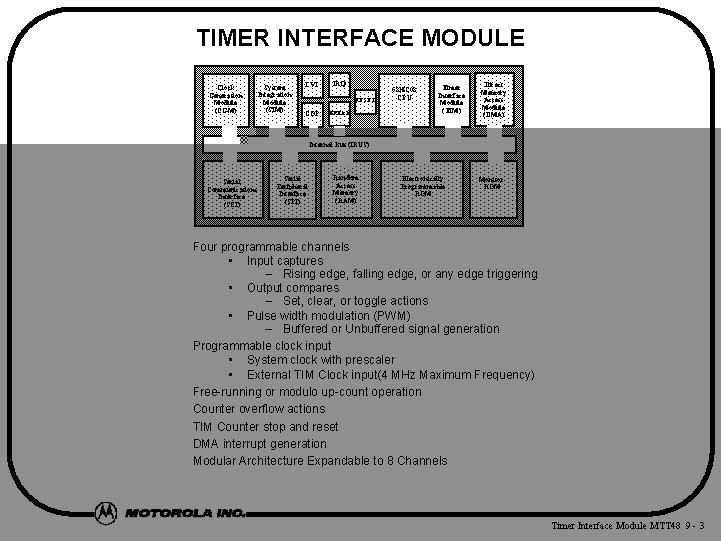

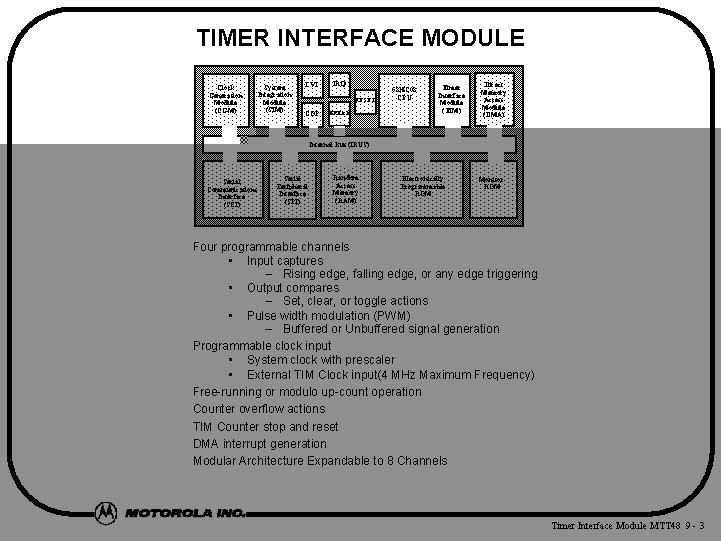

TIMER INTERFACE MODULE Clock Generation Module (CGM) System Integration Module (SIM) LVI IRQ COP BREAK RESET 68 HC 08 CPU Timer Interface Module (TIM) Direct Memory Access Module (DMA) Internal Bus (IBUS) Serial Communications Interface (SCI) Serial Peripheral Interface (SPI) Random Access Memory (RAM) Electronically Programmable ROM Monitor ROM Four programmable channels • Input captures – Rising edge, falling edge, or any edge triggering • Output compares – Set, clear, or toggle actions • Pulse width modulation (PWM) – Buffered or Unbuffered signal generation Programmable clock input • System clock with prescaler • External TIM Clock input(4 MHz Maximum Frequency) Free running or modulo up count operation Counter overflow actions TIM Counter stop and reset DMA interrupt generation Modular Architecture Expandable to 8 Channels Timer Interface Module MTT 48 9 - 3

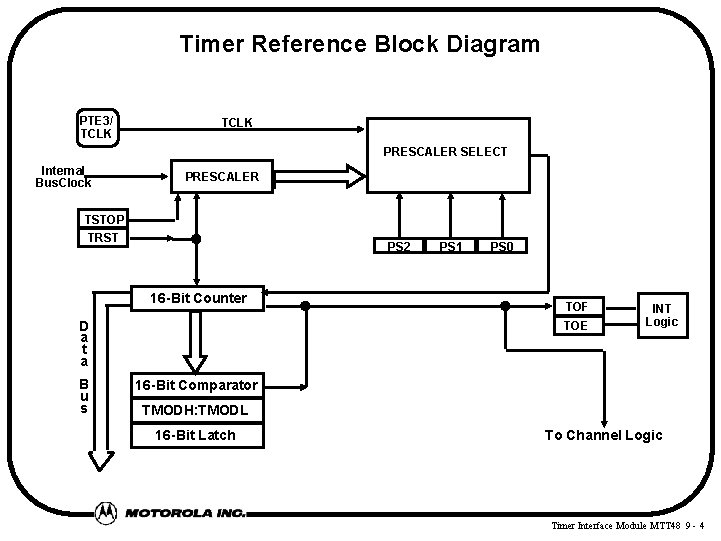

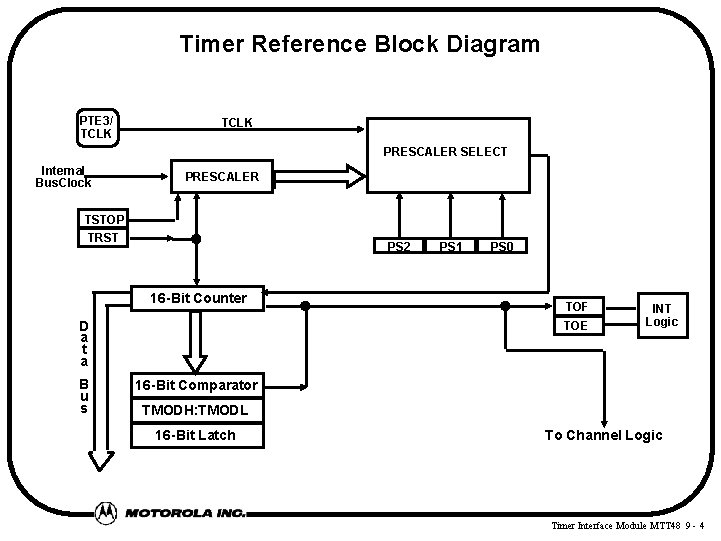

Timer Reference Block Diagram PTE 3/ TCLK PRESCALER SELECT Internal Bus. Clock PRESCALER TSTOP TRST PS 2 16 -Bit Counter D a t a B u s PS 1 PS 0 TOF TOE INT Logic 16 -Bit Comparator TMODH: TMODL 16 -Bit Latch To Channel Logic Timer Interface Module MTT 48 9 - 4

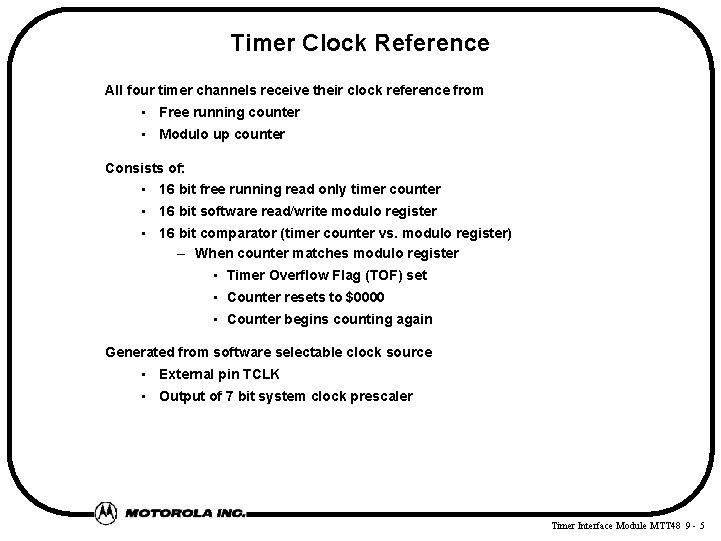

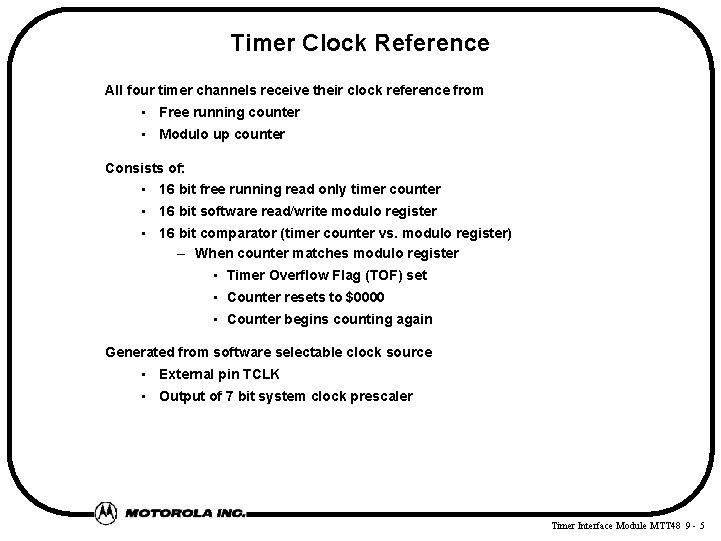

Timer Clock Reference All four timer channels receive their clock reference from • Free running counter • Modulo up counter Consists of: • 16 bit free running read only timer counter • 16 bit software read/write modulo register • 16 bit comparator (timer counter vs. modulo register) – When counter matches modulo register • Timer Overflow Flag (TOF) set • Counter resets to $0000 • Counter begins counting again Generated from software selectable clock source • External pin TCLK • Output of 7 bit system clock prescaler Timer Interface Module MTT 48 9 - 5

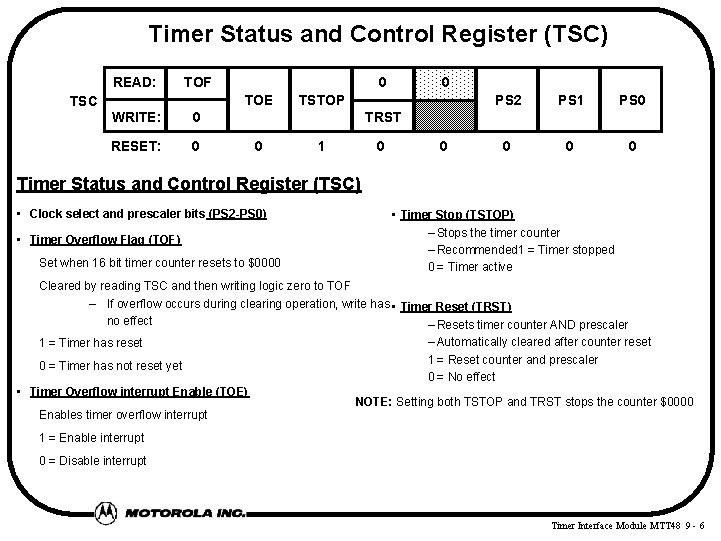

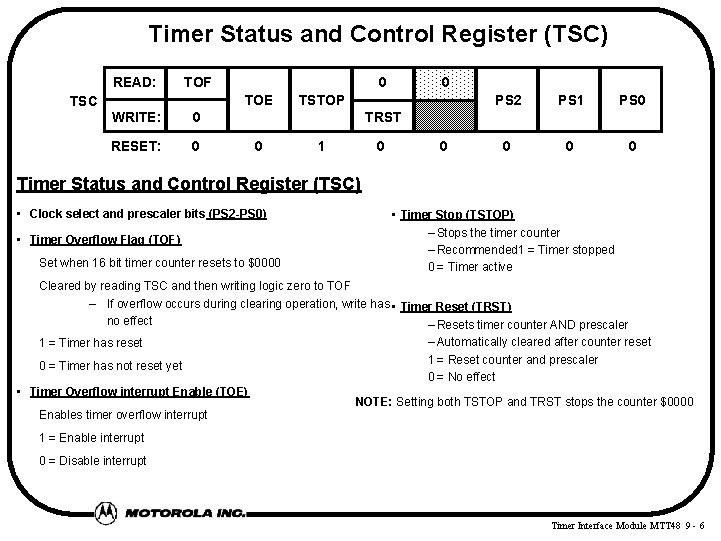

Timer Status and Control Register (TSC) READ: TOF 0 TOE TSC WRITE: 0 RESET: 0 0 TSTOP PS 2 PS 1 PS 0 0 TRST 0 1 0 0 Timer Status and Control Register (TSC) • Clock select and prescaler bits (PS 2 -PS 0) • Timer Overflow Flag (TOF) Set when 16 bit timer counter resets to $0000 • Timer Stop (TSTOP) – Stops the timer counter – Recommended 1 = Timer stopped 0 = Timer active Cleared by reading TSC and then writing logic zero to TOF – If overflow occurs during clearing operation, write has • Timer Reset (TRST) no effect – Resets timer counter AND prescaler – Automatically cleared after counter reset 1 = Timer has reset 1 = Reset counter and prescaler 0 = Timer has not reset yet 0 = No effect • Timer Overflow interrupt Enable (TOE) NOTE: Setting both TSTOP and TRST stops the counter $0000 Enables timer overflow interrupt 1 = Enable interrupt 0 = Disable interrupt Timer Interface Module MTT 48 9 - 6

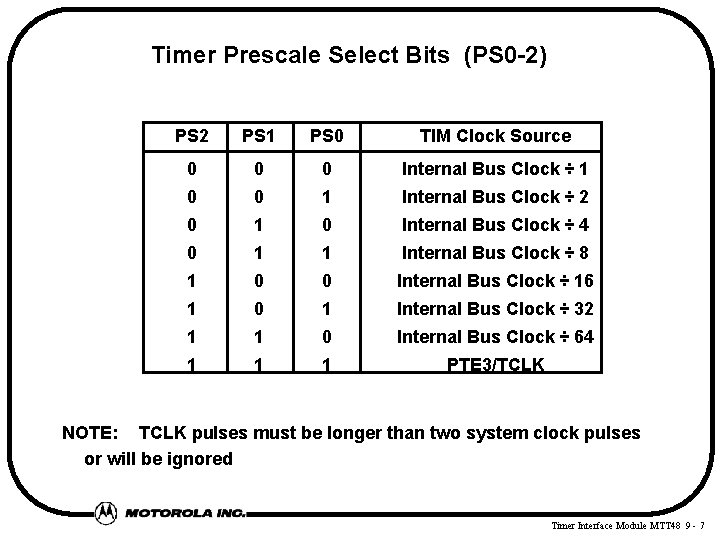

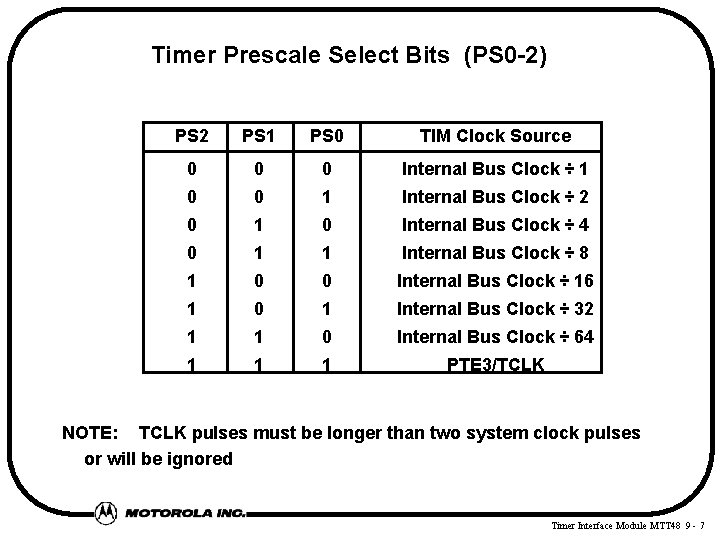

Timer Prescale Select Bits (PS 0 -2) PS 2 PS 1 PS 0 TIM Clock Source 0 0 0 Internal Bus Clock ÷ 1 0 0 1 Internal Bus Clock ÷ 2 0 1 0 Internal Bus Clock ÷ 4 0 1 1 Internal Bus Clock ÷ 8 1 0 0 Internal Bus Clock ÷ 16 1 0 1 Internal Bus Clock ÷ 32 1 1 0 Internal Bus Clock ÷ 64 1 1 1 PTE 3/TCLK NOTE: TCLK pulses must be longer than two system clock pulses or will be ignored Timer Interface Module MTT 48 9 - 7

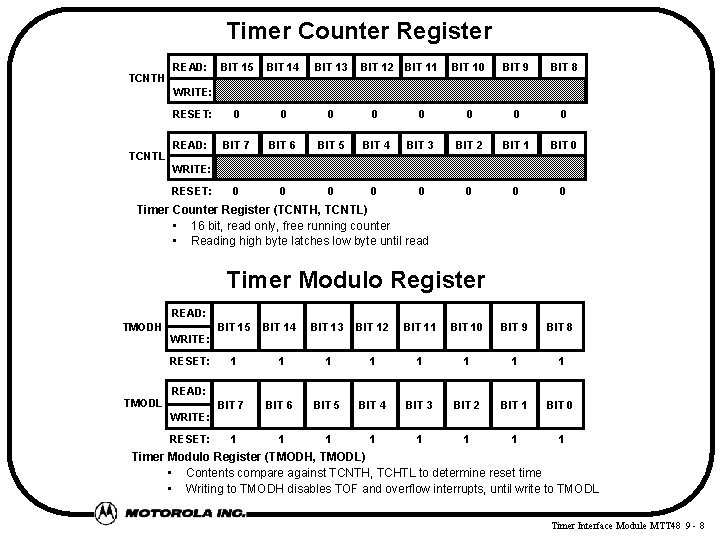

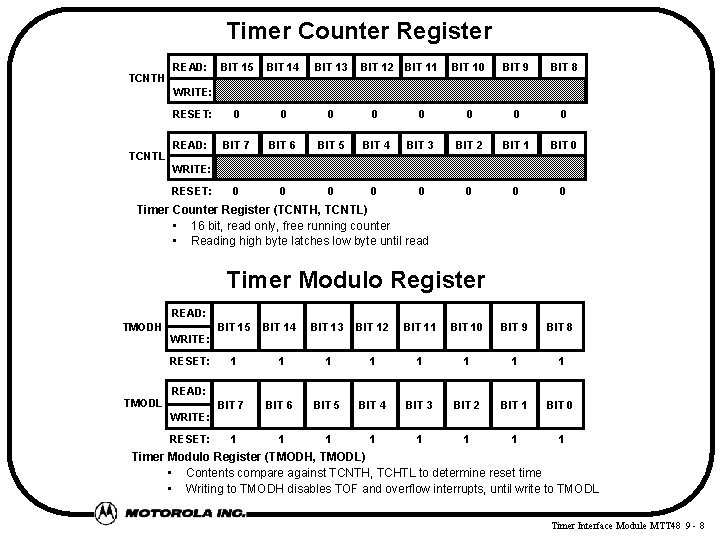

Timer Counter Register TCNTH READ: BIT 15 BIT 14 BIT 13 BIT 12 BIT 11 BIT 10 BIT 9 BIT 8 RESET: 0 0 0 0 READ: BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 0 0 0 0 WRITE: TCNTL WRITE: RESET: Timer Counter Register (TCNTH, TCNTL) • 16 bit, read only, free running counter • Reading high byte latches low byte until read Timer Modulo Register READ: TMODH BIT 15 BIT 14 BIT 13 BIT 12 BIT 11 BIT 10 BIT 9 BIT 8 1 1 1 1 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 1 1 1 1 WRITE: RESET: TMODL READ: BIT 7 WRITE: RESET: 1 Timer Modulo Register (TMODH, TMODL) • Contents compare against TCNTH, TCHTL to determine reset time • Writing to TMODH disables TOF and overflow interrupts, until write to TMODL Timer Interface Module MTT 48 9 - 8

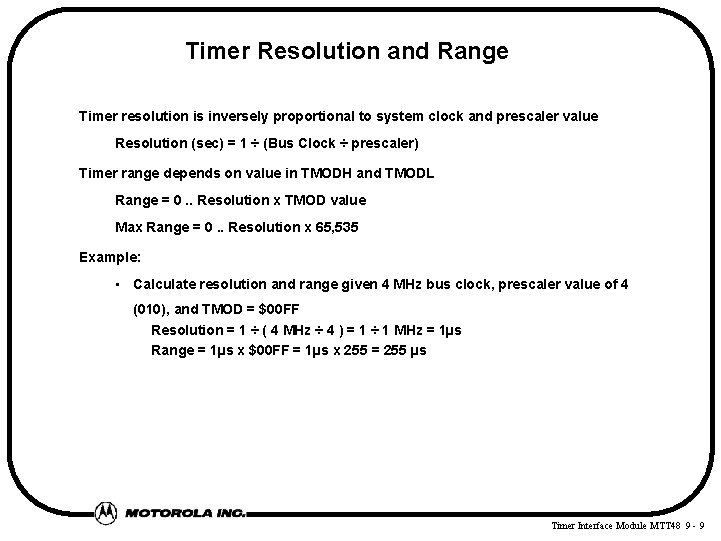

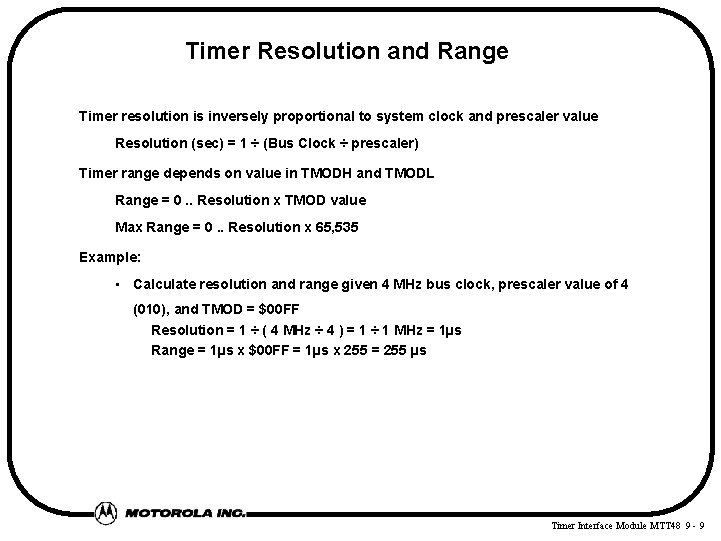

Timer Resolution and Range Timer resolution is inversely proportional to system clock and prescaler value Resolution (sec) = 1 ÷ (Bus Clock ÷ prescaler) Timer range depends on value in TMODH and TMODL Range = 0. . Resolution x TMOD value Max Range = 0. . Resolution x 65, 535 Example: • Calculate resolution and range given 4 MHz bus clock, prescaler value of 4 (010), and TMOD = $00 FF Resolution = 1 ÷ ( 4 MHz ÷ 4 ) = 1 ÷ 1 MHz = 1µs Range = 1µs x $00 FF = 1µs x 255 = 255 µs Timer Interface Module MTT 48 9 - 9

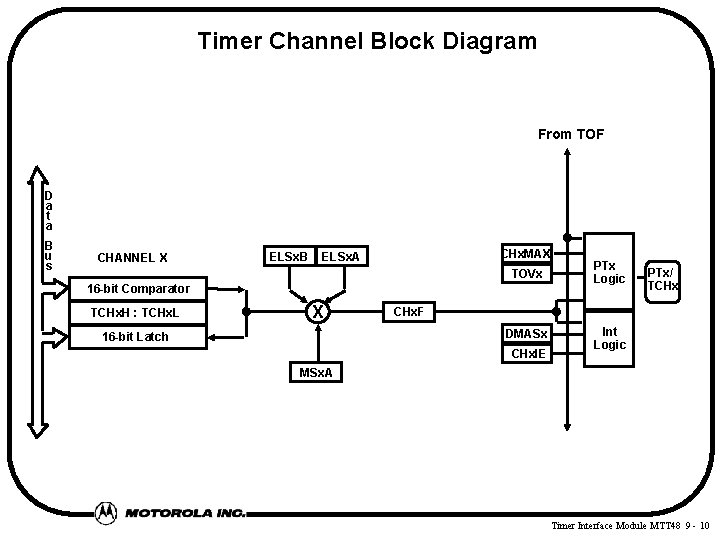

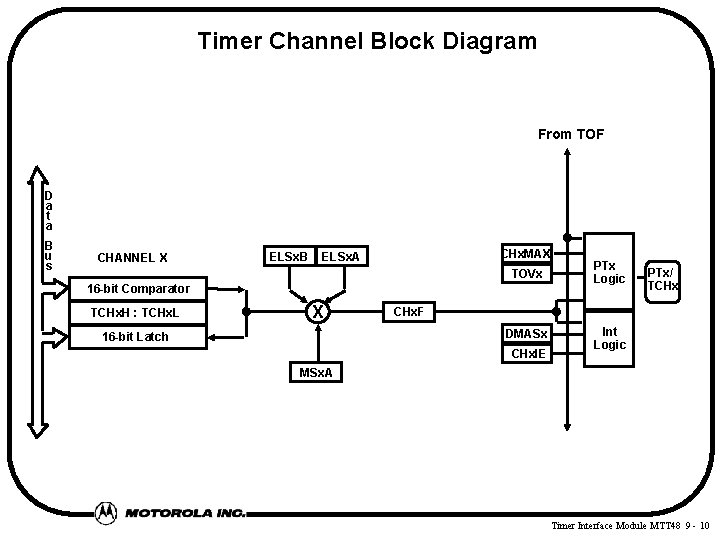

Timer Channel Block Diagram From TOF D a t a B u s CHANNEL X ELSx. B CHx. MAX ELSx. A TOVx PTx Logic DMASx Int Logic 16 -bit Comparator TCHx. H : TCHx. L X 16 -bit Latch PTx/ TCHx CHx. F CHx. IE MSx. A Timer Interface Module MTT 48 9 - 10

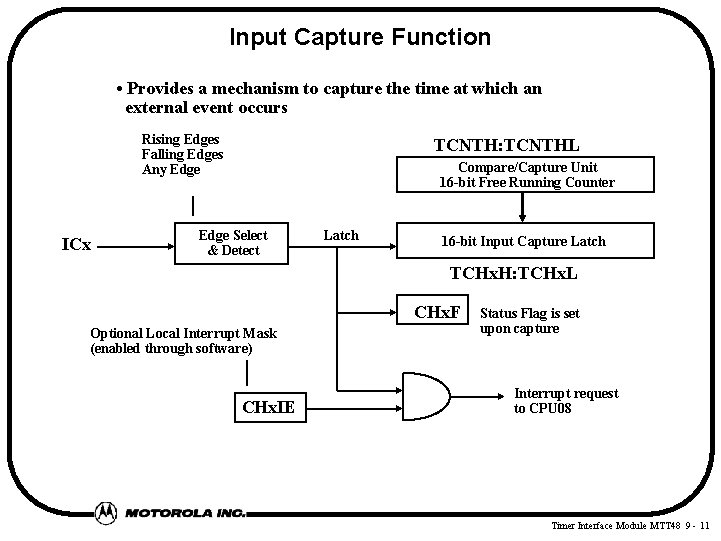

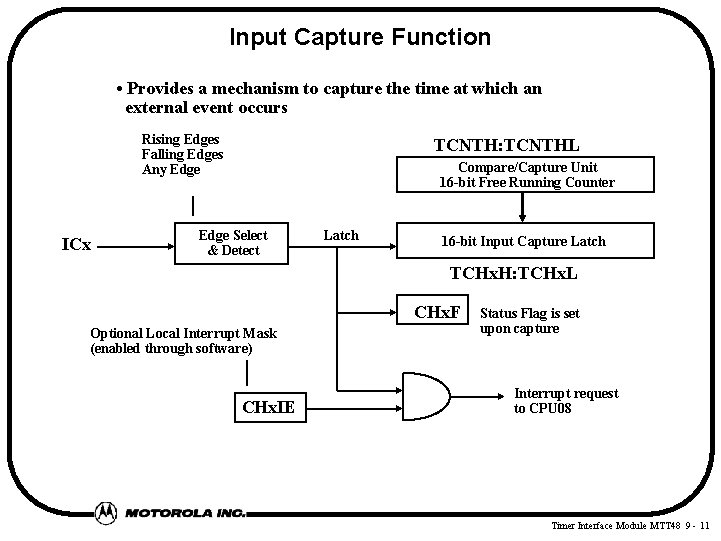

Input Capture Function • Provides a mechanism to capture the time at which an external event occurs Rising Edges Falling Edges Any Edge ICx TCNTH: TCNTHL Compare/Capture Unit 16 -bit Free Running Counter Edge Select & Detect Latch 16 -bit Input Capture Latch TCHx. H: TCHx. L CHx. F Optional Local Interrupt Mask (enabled through software) CHx. IE Status Flag is set upon capture Interrupt request to CPU 08 Timer Interface Module MTT 48 9 - 11

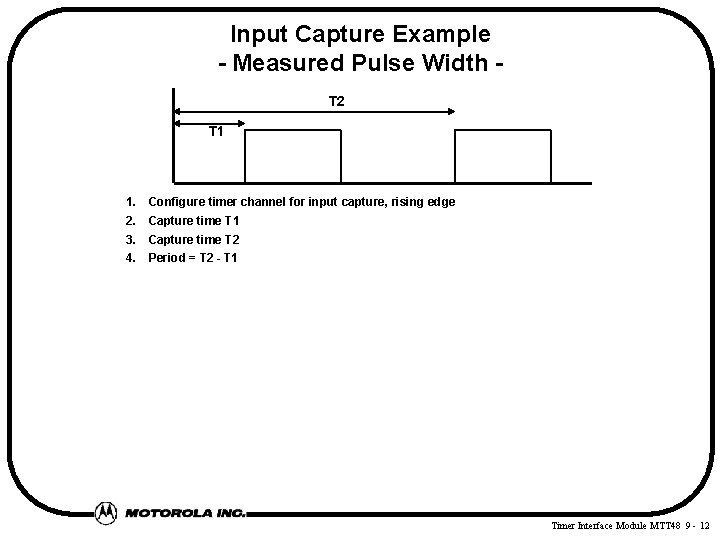

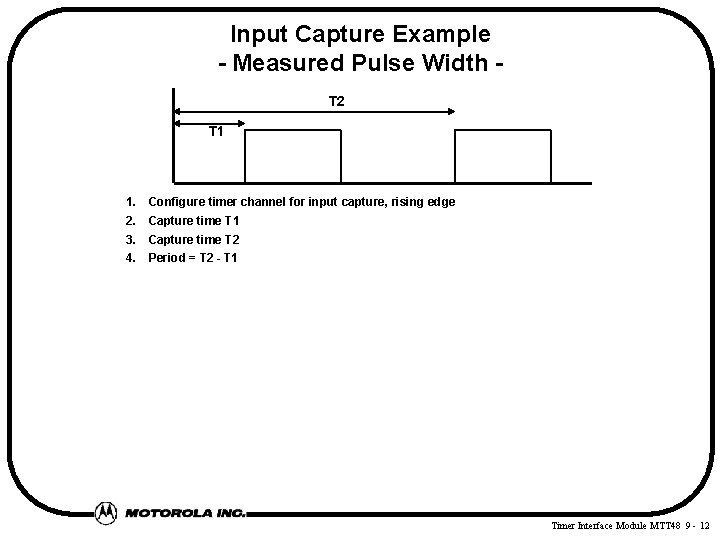

Input Capture Example - Measured Pulse Width T 2 T 1 1. Configure timer channel for input capture, rising edge 2. Capture time T 1 3. Capture time T 2 4. Period = T 2 - T 1 Timer Interface Module MTT 48 9 - 12

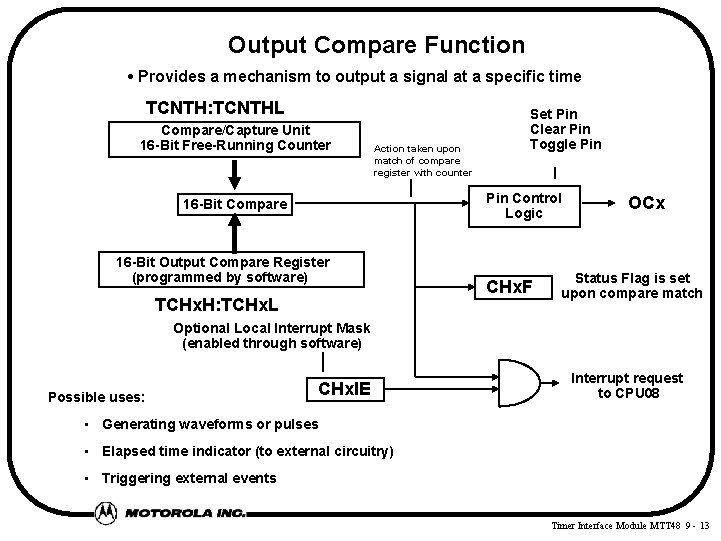

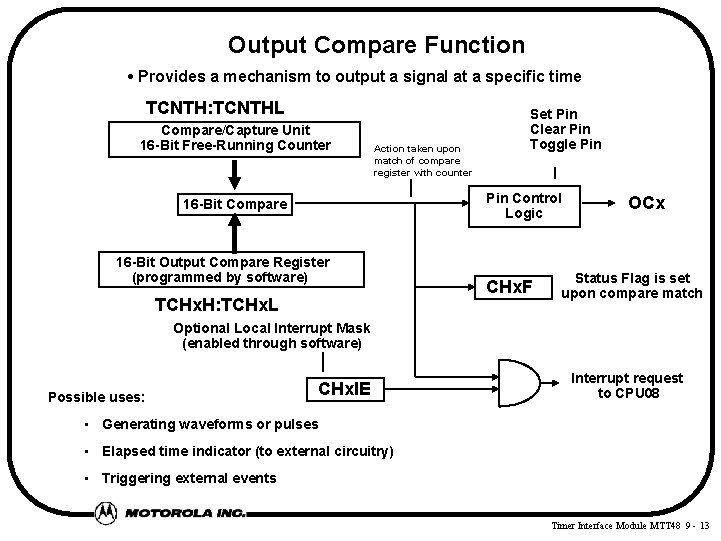

Output Compare Function • Provides a mechanism to output a signal at a specific time TCNTH: TCNTHL Compare/Capture Unit 16 -Bit Free-Running Counter Action taken upon match of compare register with counter Set Pin Clear Pin Toggle Pin Control Logic 16 -Bit Compare 16 -Bit Output Compare Register (programmed by software) TCHx. H: TCHx. L CHx. F OCx Status Flag is set upon compare match Optional Local Interrupt Mask (enabled through software) Possible uses: CHx. IE Interrupt request to CPU 08 • Generating waveforms or pulses • Elapsed time indicator (to external circuitry) • Triggering external events Timer Interface Module MTT 48 9 - 13

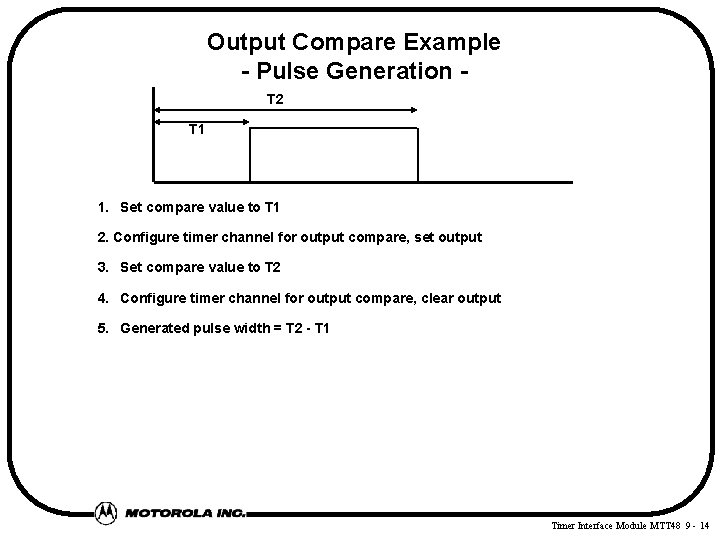

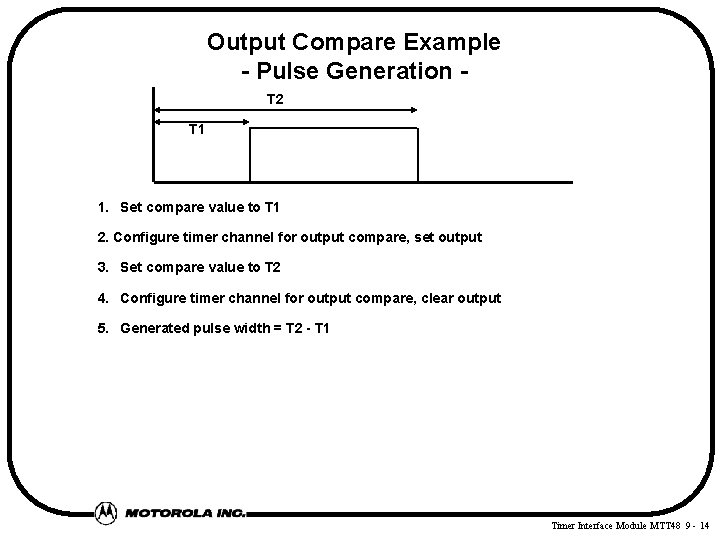

Output Compare Example - Pulse Generation T 2 T 1 1. Set compare value to T 1 2. Configure timer channel for output compare, set output 3. Set compare value to T 2 4. Configure timer channel for output compare, clear output 5. Generated pulse width = T 2 - T 1 Timer Interface Module MTT 48 9 - 14

Output Compare Synchronization Method Interrupt latency and execution time may limit minimum pulse width possible using interrupt on overflow method To maximize resolution and avoid unsynchronized writes: • Enable the output compare interrupt function when new pulse width value required • Write new value to output compare register within output compare interrupt routine Timer Interface Module MTT 48 9 - 15

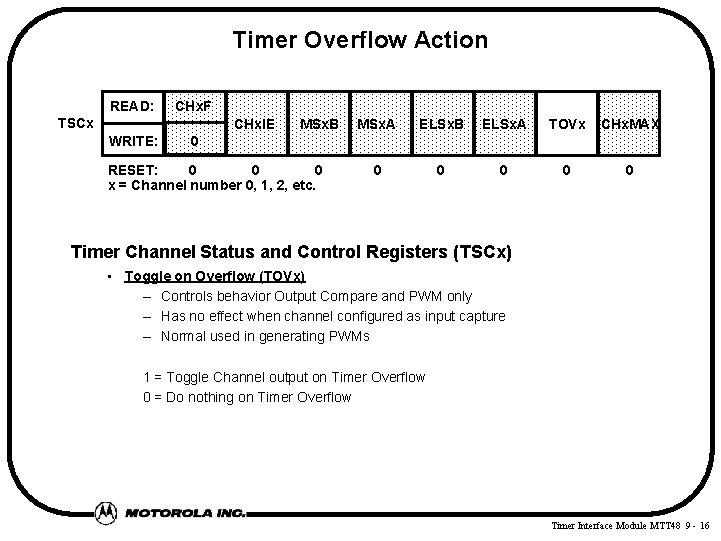

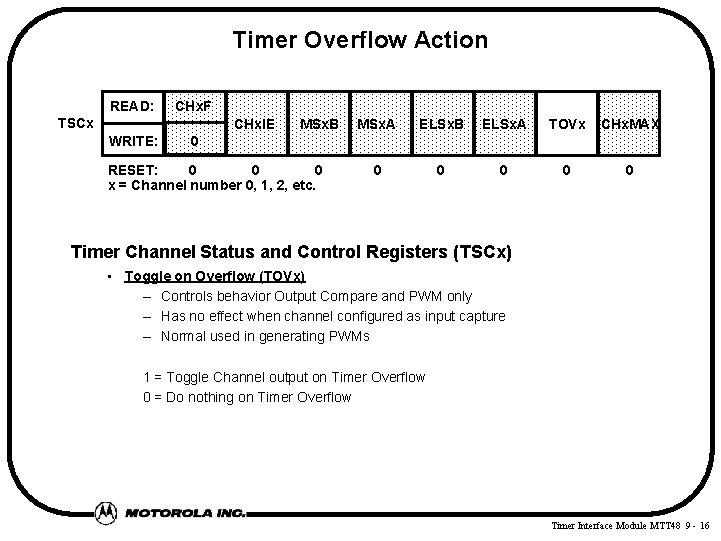

Timer Overflow Action READ: CHx. F TSCx CHx. IE WRITE: MSx. B MSx. A ELSx. B ELSx. A TOVx CHx. MAX 0 0 0 RESET: 0 0 0 x = Channel number 0, 1, 2, etc. Timer Channel Status and Control Registers (TSCx) • Toggle on Overflow (TOVx) – Controls behavior Output Compare and PWM only – Has no effect when channel configured as input capture – Normal used in generating PWMs 1 = Toggle Channel output on Timer Overflow 0 = Do nothing on Timer Overflow Timer Interface Module MTT 48 9 - 16

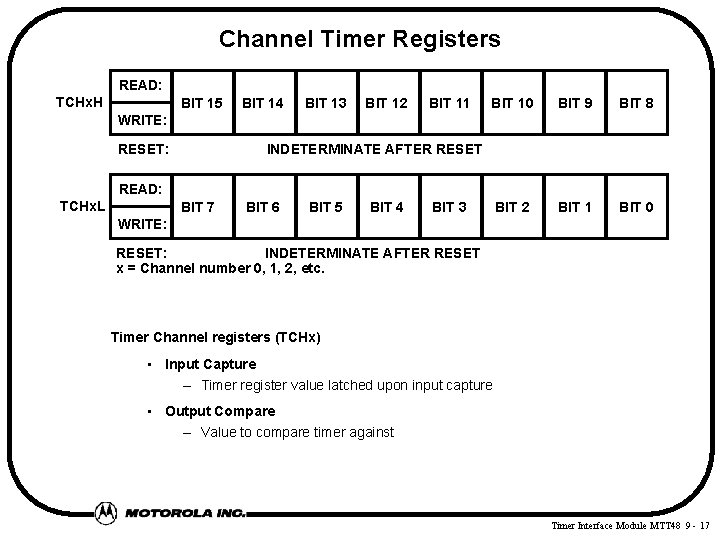

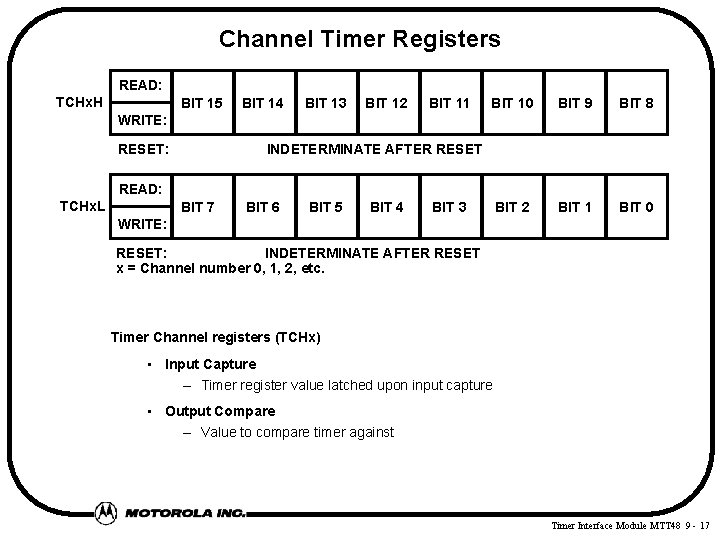

Channel Timer Registers READ: TCHx. H BIT 15 BIT 14 BIT 13 BIT 12 BIT 11 BIT 10 BIT 9 BIT 8 BIT 2 BIT 1 BIT 0 WRITE: RESET: INDETERMINATE AFTER RESET READ: TCHx. L BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 WRITE: RESET: INDETERMINATE AFTER RESET x = Channel number 0, 1, 2, etc. Timer Channel registers (TCHx) • Input Capture – Timer register value latched upon input capture • Output Compare – Value to compare timer against Timer Interface Module MTT 48 9 - 17

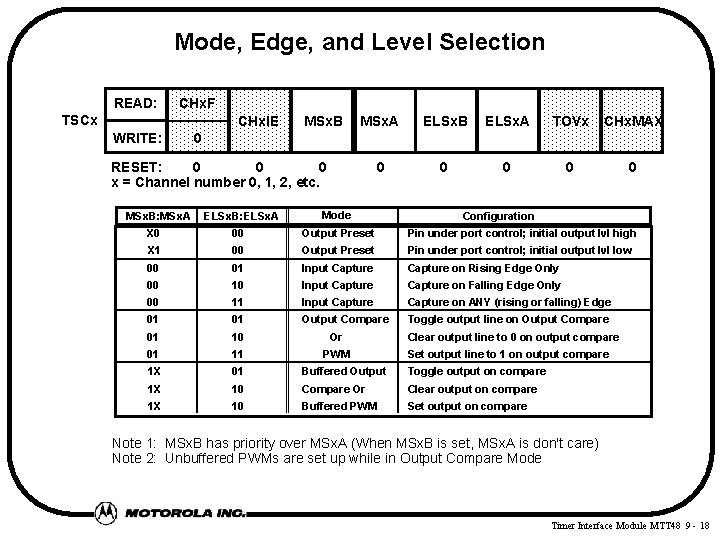

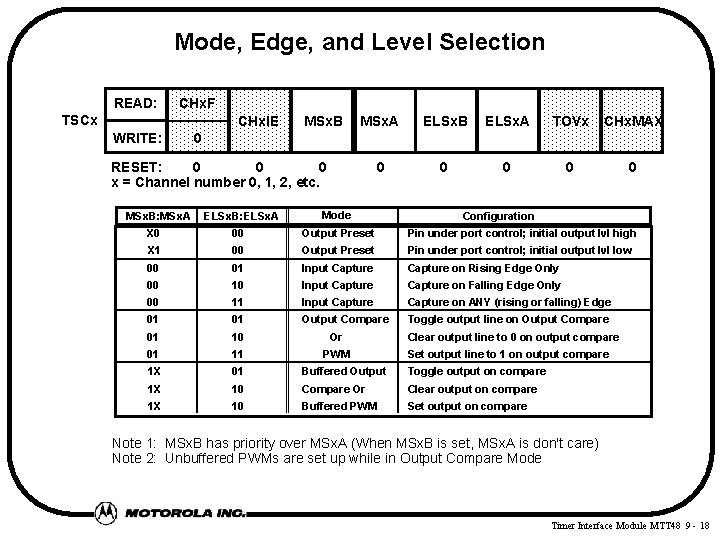

Mode, Edge, and Level Selection READ: CHx. F TSCx CHx. IE WRITE: MSx. B MSx. A ELSx. B ELSx. A TOVx CHx. MAX 0 0 0 RESET: 0 0 0 x = Channel number 0, 1, 2, etc. MSx. B: MSx. A ELSx. B: ELSx. A Mode Configuration X 0 00 Output Preset Pin under port control; initial output lvl high X 1 00 Output Preset Pin under port control; initial output lvl low 00 01 Input Capture on Rising Edge Only 00 10 Input Capture on Falling Edge Only 00 11 Input Capture on ANY (rising or falling) Edge 01 01 Output Compare Toggle output line on Output Compare 01 10 Or 01 11 PWM 1 X 01 Buffered Output Toggle output on compare 1 X 10 Compare Or Clear output on compare 1 X 10 Buffered PWM Set output on compare Clear output line to 0 on output compare Set output line to 1 on output compare Note 1: MSx. B has priority over MSx. A (When MSx. B is set, MSx. A is don't care) Note 2: Unbuffered PWMs are set up while in Output Compare Mode Timer Interface Module MTT 48 9 - 18

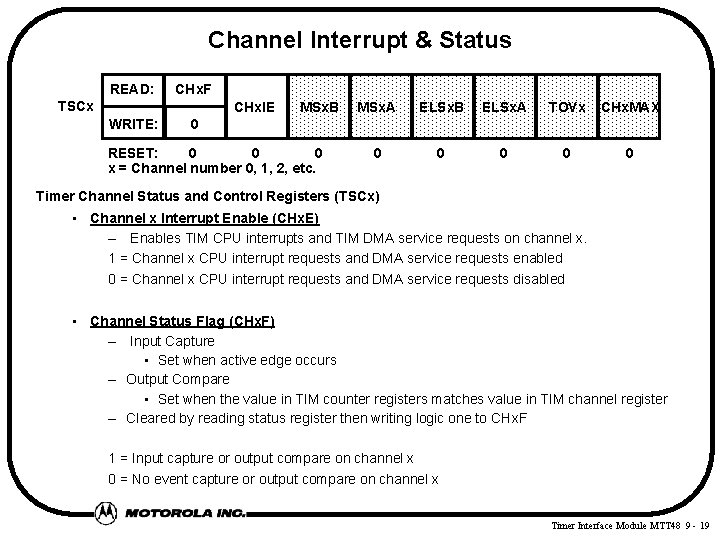

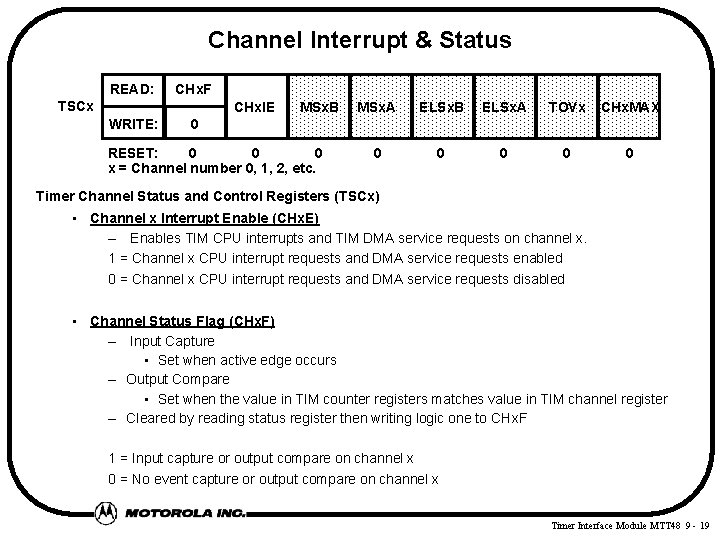

Channel Interrupt & Status READ: CHx. F TSCx CHx. IE WRITE: MSx. B MSx. A ELSx. B ELSx. A TOVx CHx. MAX 0 0 0 RESET: 0 0 0 x = Channel number 0, 1, 2, etc. Timer Channel Status and Control Registers (TSCx) • Channel x Interrupt Enable (CHx. E) – Enables TIM CPU interrupts and TIM DMA service requests on channel x. 1 = Channel x CPU interrupt requests and DMA service requests enabled 0 = Channel x CPU interrupt requests and DMA service requests disabled • Channel Status Flag (CHx. F) – Input Capture • Set when active edge occurs – Output Compare • Set when the value in TIM counter registers matches value in TIM channel register – Cleared by reading status register then writing logic one to CHx. F 1 = Input capture or output compare on channel x 0 = No event capture or output compare on channel x Timer Interface Module MTT 48 9 - 19

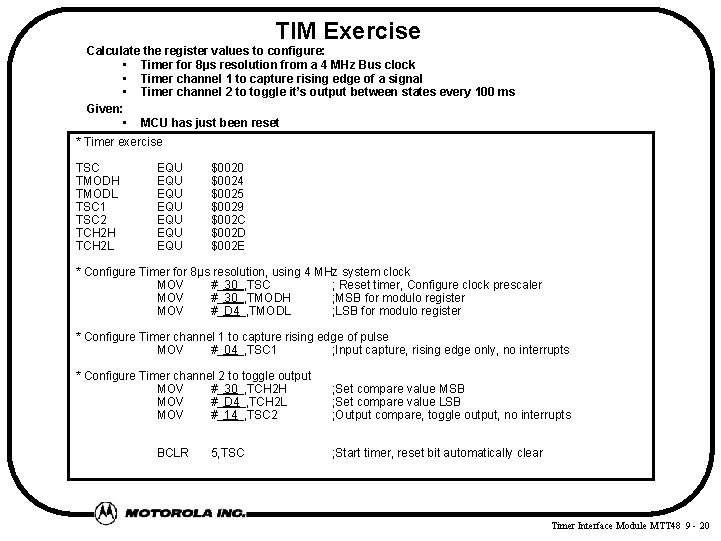

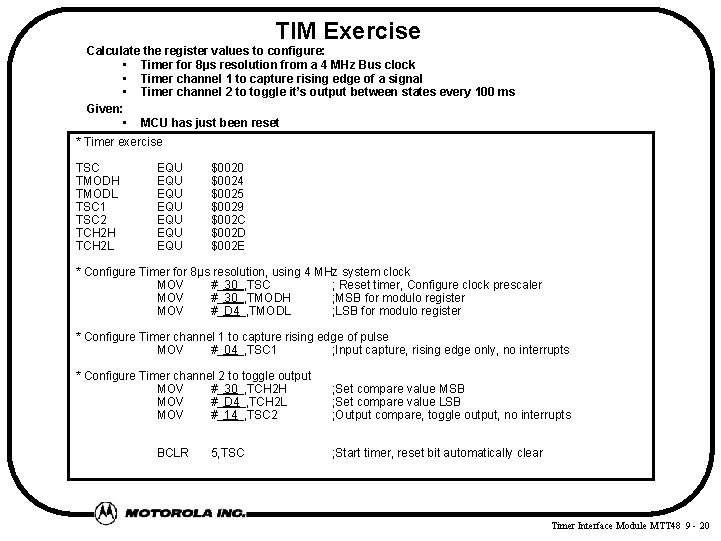

TIM Exercise Calculate the register values to configure: • Timer for 8µs resolution from a 4 MHz Bus clock • Timer channel 1 to capture rising edge of a signal • Timer channel 2 to toggle it’s output between states every 100 ms Given: • MCU has just been reset * Timer exercise TSC TMODH TMODL TSC 1 TSC 2 TCH 2 H TCH 2 L EQU EQU $0020 $0024 $0025 $0029 $002 C $002 D $002 E * Configure Timer for 8µs resolution, using 4 MHz system clock MOV #_30_, TSC ; Reset timer, Configure clock prescaler MOV #_30_, TMODH ; MSB for modulo register MOV #_D 4_, TMODL ; LSB for modulo register * Configure Timer channel 1 to capture rising edge of pulse MOV #_04_, TSC 1 ; Input capture, rising edge only, no interrupts * Configure Timer channel 2 to toggle output MOV #_30_, TCH 2 H MOV #_D 4_, TCH 2 L MOV #_14_, TSC 2 BCLR 5, TSC ; Set compare value MSB ; Set compare value LSB ; Output compare, toggle output, no interrupts ; Start timer, reset bit automatically clear Timer Interface Module MTT 48 9 - 20

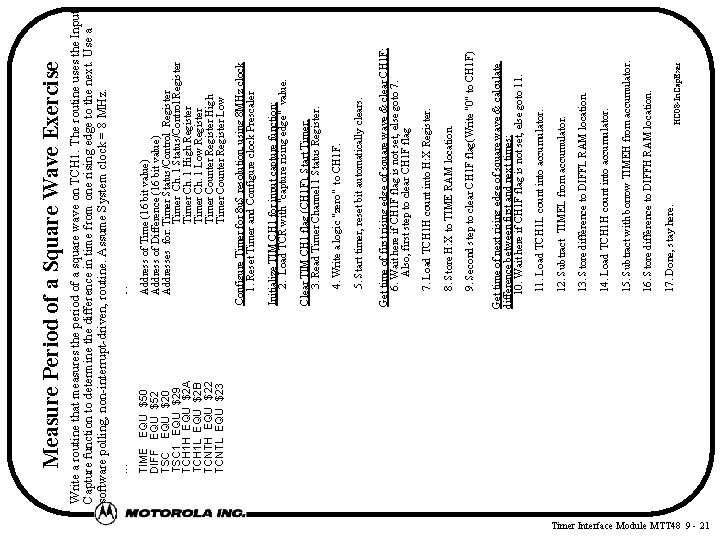

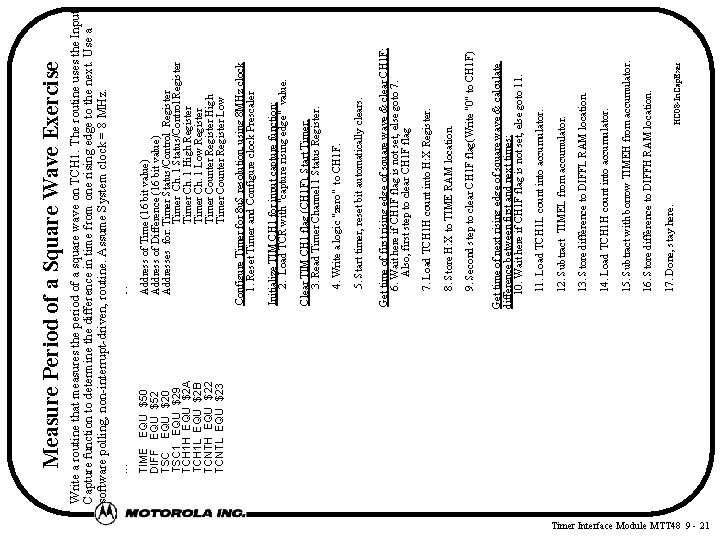

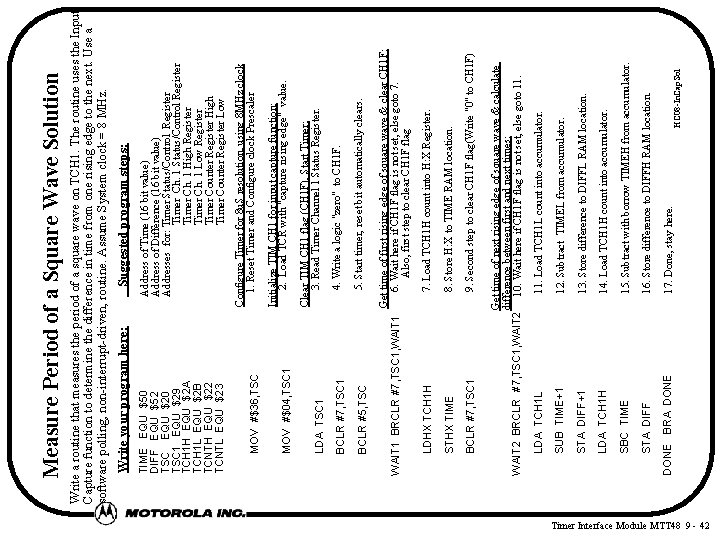

Timer Interface Module MTT 48 9 - 21 TIME EQU $50 DIFF EQU $52 TSC EQU $20 TSC 1 EQU $29 TCH 1 H EQU $2 A TCH 1 L EQU $2 B TCNTH EQU $22 TCNTL EQU $23 Write your program here: 17. Done, stay here. HC 08 -In. Cap. Exer 16. Store difference to DIFFH RAM location. 15. Subtract with borrow TIMEH from accumulator. 14. Load TCH 1 H count into accumulator. 13. Store difference to DIFFL RAM location. 12. Subtract TIMEL from accumulator. 11. Load TCH 1 L count into accumulator. Get time of next rising edge of square wave & calculate difference between first and next times: 10. Wait here if CH 1 F flag is not set, else goto 11. 9. Second step to clear CH 1 F flag(Write "0" to CH 1 F) 8. Store H: X to TIME RAM location. 7. Load TCH 1 H count into H: X Register. Get time of first rising edge of square wave & clear CH 1 F: 6. Wait here if CH 1 F flag is not set, else goto 7. Also, first step to clear CH 1 F flag 5. Start timer, reset bit automatically clears. 4. Write a logic "zero" to CH 1 F. Clear TIM CH 1 flag (CH 1 F), Start Timer; 3. Read Timer Channel 1 Status Register. Initialize TIM CH 1 for input capture function: 2. Load TCR with "capture rising edge" value. Configure Timer for 8 u. S resolution, using 8 MHz clock 1. Reset Timer and Configure clock Prescaler Address of Time (16 bit value) Address of Difference (16 bit value) Addresses for: Timer Status/Control Register Timer Ch. 1 High Register Timer Ch. 1 Low Register Timer Counter Register High Timer Counter Register Low Suggested program steps: Write a routine that measures the period of a square wave on TCH 1. The routine uses the Input Capture function to determine the difference in time from one rising edge to the next. Use a software polling, non-interrupt-driven, routine. Assume System clock = 8 MHz. Measure Period of a Square Wave Exercise

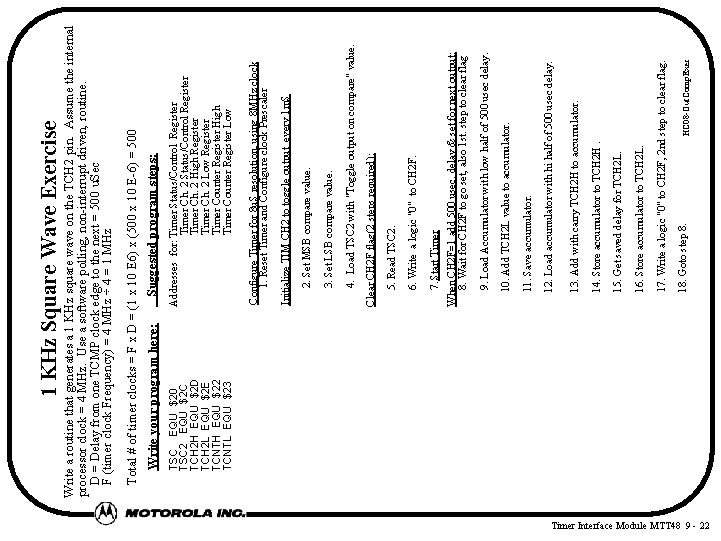

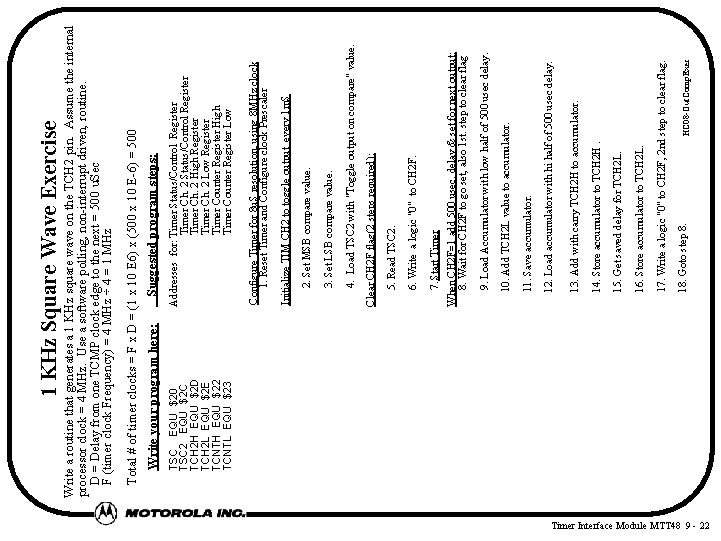

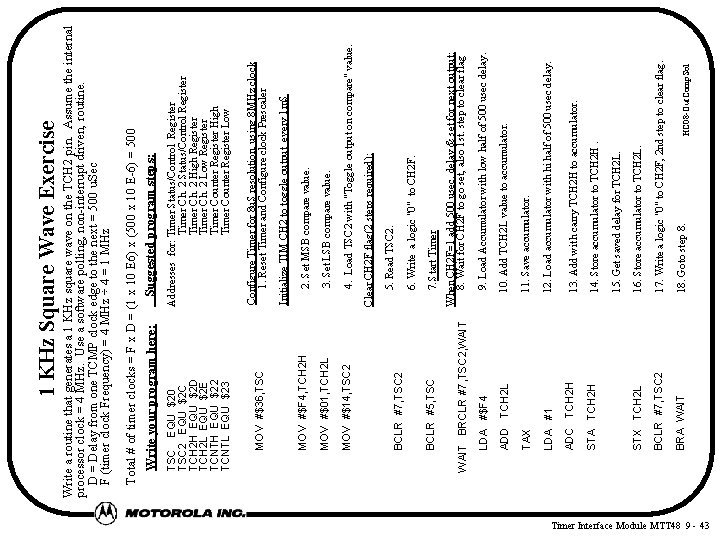

Timer Interface Module MTT 48 9 - 22 TSC EQU $20 TSC 2 EQU $2 C TCH 2 H EQU $2 D TCH 2 L EQU $2 E TCNTH EQU $22 TCNTL EQU $23 Write your program here: 18. Goto step 8. HC 08 -Out. Comp. Exer 17. Write a logic "0" to CH 2 F, 2 nd step to clear flag. 16. Store accumulator to TCH 2 L. 15. Get saved delay for TCH 2 L. 14. Store accumulator to TCH 2 H. 13. Add with carry TCH 2 H to accumulator. 12. Load accumulator with hi half of 500 usec delay. 11. Save accumulator. 10. Add TCH 2 L value to accumulator. 9. Load Accumulator with low half of 500 usec delay. When CH 2 F=1 add 500 usec. delay & set for next output: 8. Wait for CH 2 F to go set, also 1 st. step to clear flag 7. Start Timer 6. Write a logic "0" to CH 2 F. 5. Read TSC 2. Clear CH 2 F flag(2 steps required): 4. Load TSC 2 with "Toggle output on compare" value. 3. Set LSB compare value. 2. Set MSB compare value. Initialize TIM CH 2 to toggle output every 1 m. S Configure Timer for 8 u. S resolution, using 8 MHz clock 1. Reset Timer and Configure clock Prescaler Addresses for: Timer Status/Control Register Timer Ch. 2 High Register Timer Ch. 2 Low Register Timer Counter Register High Timer Counter Register Low Suggested program steps: Total # of timer clocks = F x D = (1 x 10 E 6) x (500 x 10 E-6) = 500 Write a routine that generates a 1 KHz square wave on the TCH 2 pin. Assume the internal processor clock = 4 MHz. Use a software polling, non-interrupt driven, routine. D = Delay from one TCMP clock edge to the next = 500 u. Sec F (timer clock Frequency) = 4 MHz ÷ 4 = 1 MHz 1 KHz Square Wave Exercise

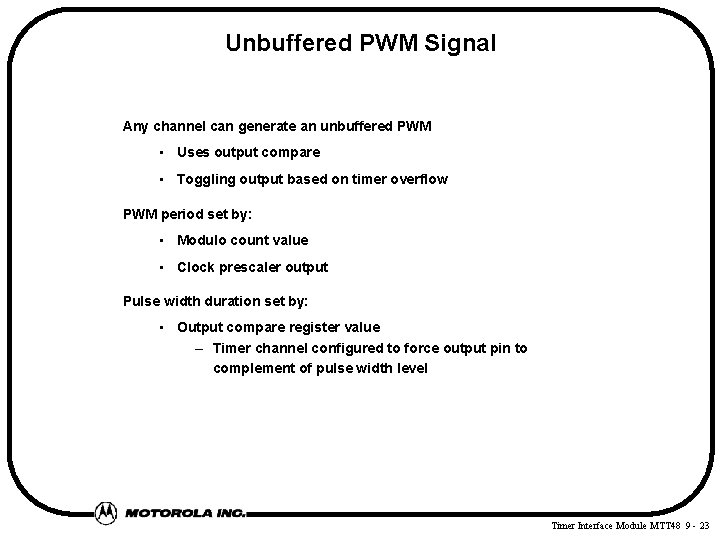

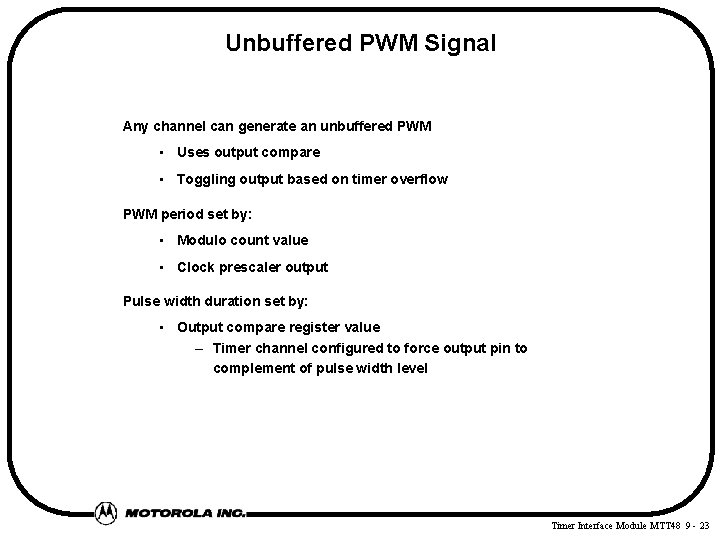

Unbuffered PWM Signal Any channel can generate an unbuffered PWM • Uses output compare • Toggling output based on timer overflow PWM period set by: • Modulo count value • Clock prescaler output Pulse width duration set by: • Output compare register value – Timer channel configured to force output pin to complement of pulse width level Timer Interface Module MTT 48 9 - 23

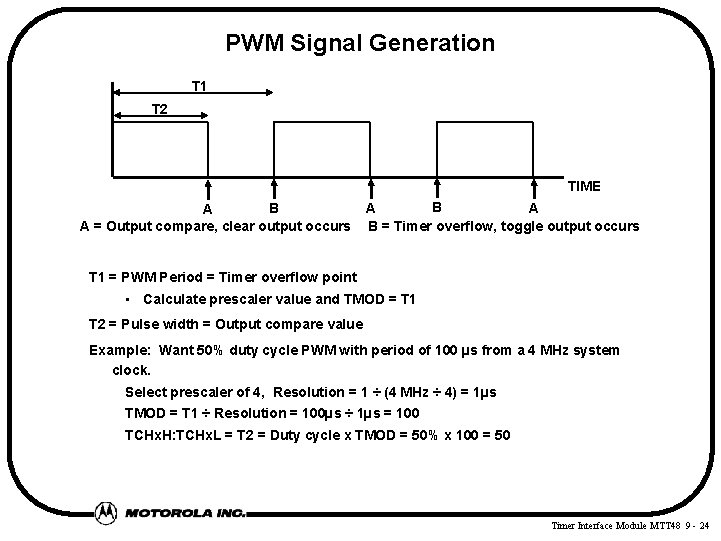

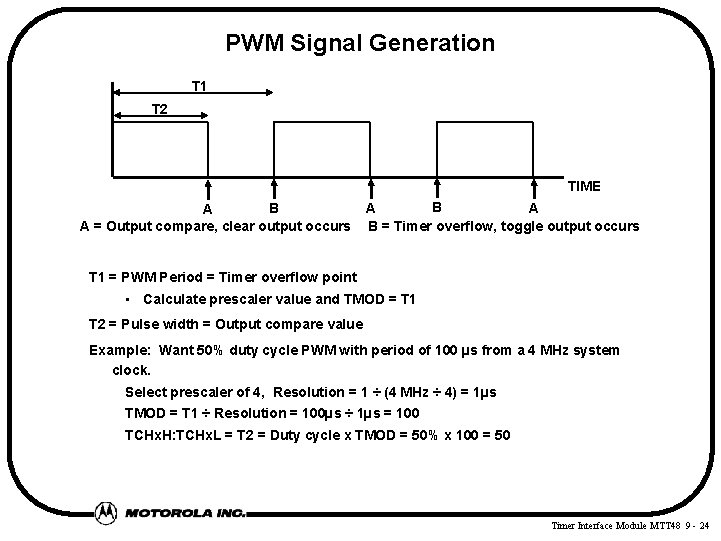

PWM Signal Generation T 1 T 2 TIME B A A = Output compare, clear output occurs B A A B = Timer overflow, toggle output occurs T 1 = PWM Period = Timer overflow point • Calculate prescaler value and TMOD = T 1 T 2 = Pulse width = Output compare value Example: Want 50% duty cycle PWM with period of 100 µs from a 4 MHz system clock. Select prescaler of 4, Resolution = 1 ÷ (4 MHz ÷ 4) = 1µs TMOD = T 1 ÷ Resolution = 100µs ÷ 1µs = 100 TCHx. H: TCHx. L = T 2 = Duty cycle x TMOD = 50% x 100 = 50 Timer Interface Module MTT 48 9 - 24

PWM Resolution Period • 8 -bit PWMs – Variable in 256 increments of system clock • 16 -bit PWMs – Variable in 65536 increments of system clock Pulse width is variable up to N increments of system clock N = System clock counts for Period – Pulse width = N/4 = 25% duty cycle – Pulse width = N/2 = 50% duty cycle – Pulse width = 3 N/4 = 75% duty cycle Timer Interface Module MTT 48 9 - 25

Unbuffered PWM Initialization 1) Stop and reset timer 2) Select timer counter modulo value and timer clock prescaler to provide required PWM period 3) Load output compare register with pulse width value 4) Configure timer channel for output compare operation 5) Select the timer counter toggle on overflow function 6) Configure timer channel to force output pin to complement of pulse width level • Toggle on output compare should not be used 7) Enable the timer Timer Interface Module MTT 48 9 - 26

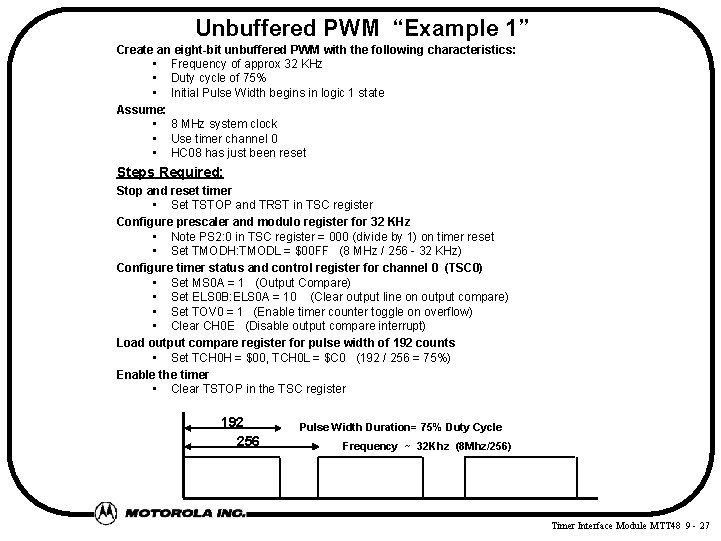

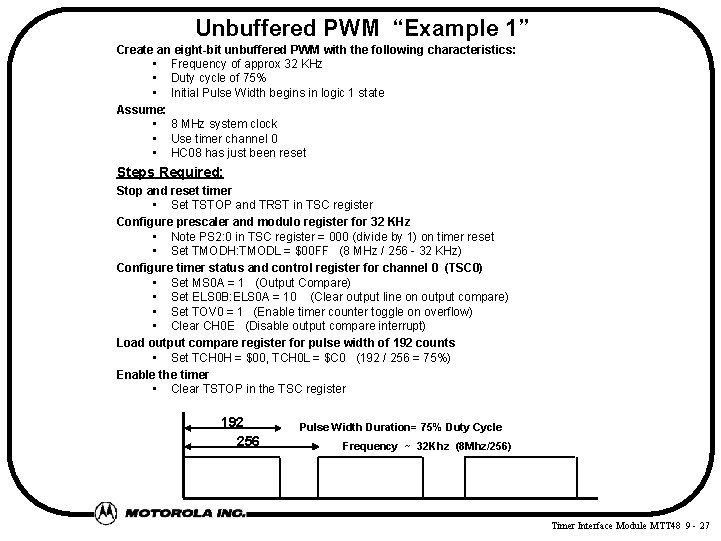

Unbuffered PWM “Example 1” Create an eight-bit unbuffered PWM with the following characteristics: • Frequency of approx 32 KHz • Duty cycle of 75% • Initial Pulse Width begins in logic 1 state Assume: • 8 MHz system clock • Use timer channel 0 • HC 08 has just been reset Steps Required: Stop and reset timer • Set TSTOP and TRST in TSC register Configure prescaler and modulo register for 32 KHz • Note PS 2: 0 in TSC register = 000 (divide by 1) on timer reset • Set TMODH: TMODL = $00 FF (8 MHz / 256 32 KHz) Configure timer status and control register for channel 0 (TSC 0) • Set MS 0 A = 1 (Output Compare) • Set ELS 0 B: ELS 0 A = 10 (Clear output line on output compare) • Set TOV 0 = 1 (Enable timer counter toggle on overflow) • Clear CH 0 E (Disable output compare interrupt) Load output compare register for pulse width of 192 counts • Set TCH 0 H = $00, TCH 0 L = $C 0 (192 / 256 = 75%) Enable the timer • Clear TSTOP in the TSC register 192 256 Pulse Width Duration= 75% Duty Cycle Frequency ~ 32 Khz (8 Mhz/256) Timer Interface Module MTT 48 9 - 27

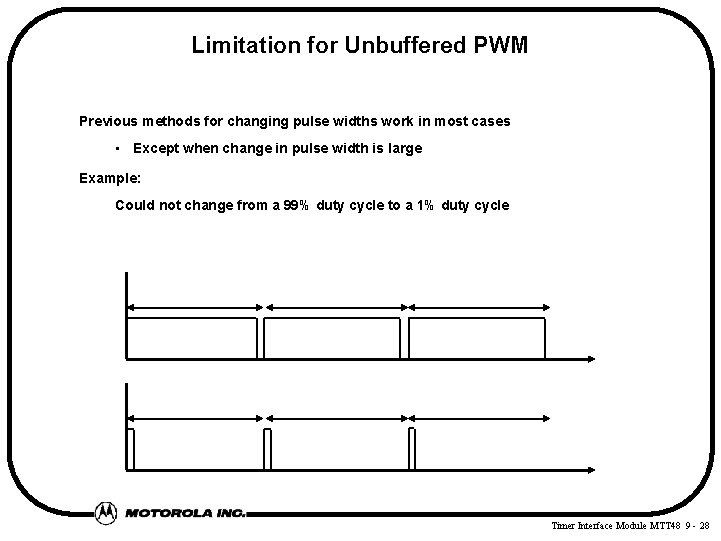

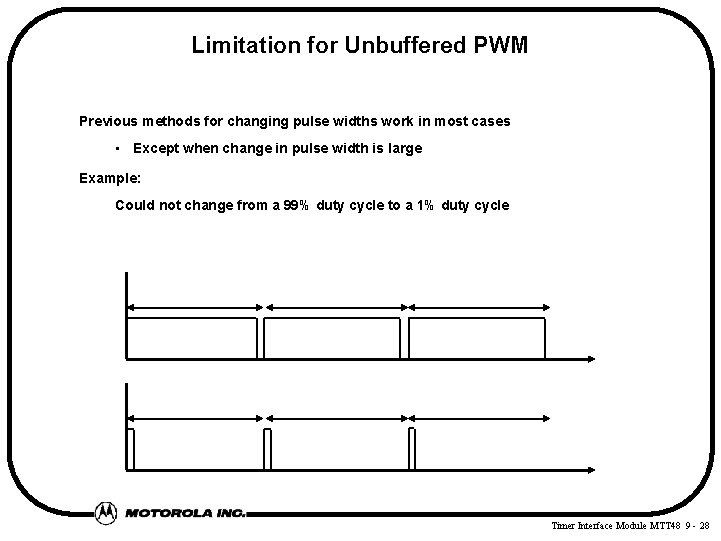

Limitation for Unbuffered PWM Previous methods for changing pulse widths work in most cases • Except when change in pulse width is large Example: Could not change from a 99% duty cycle to a 1% duty cycle Timer Interface Module MTT 48 9 - 28

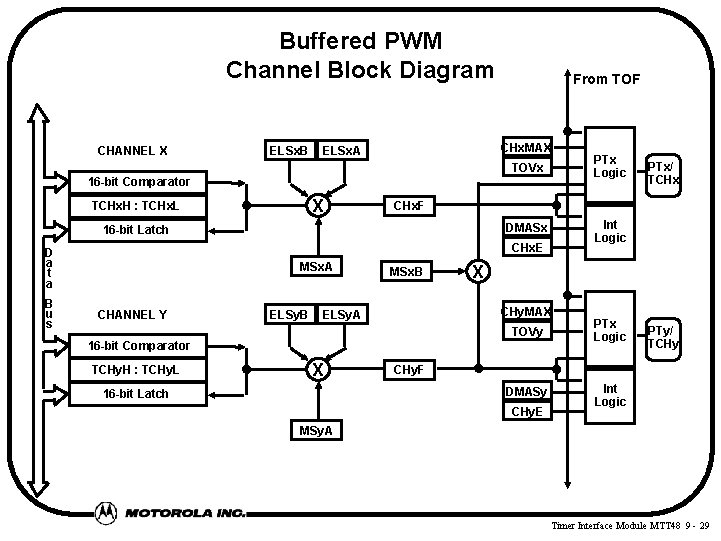

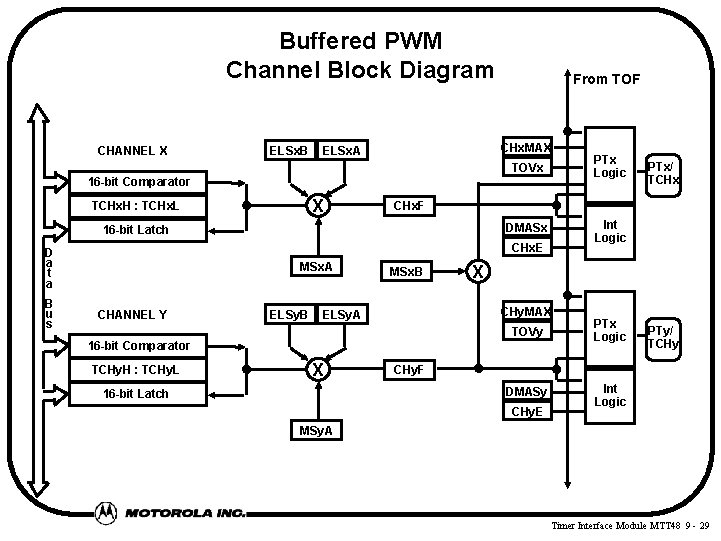

Buffered PWM Channel Block Diagram CHANNEL X ELSx. B From TOF CHx. MAX ELSx. A TOVx PTx Logic DMASx Int Logic 16 -bit Comparator X TCHx. H : TCHx. L CHx. F 16 -bit Latch CHx. E D a t a B u s MSx. A CHANNEL Y ELSy. B MSx. B X CHy. MAX ELSy. A TOVy PTx Logic DMASy Int Logic 16 -bit Comparator TCHy. H : TCHy. L X 16 -bit Latch PTx/ TCHx PTy/ TCHy CHy. F CHy. E MSy. A Timer Interface Module MTT 48 9 - 29

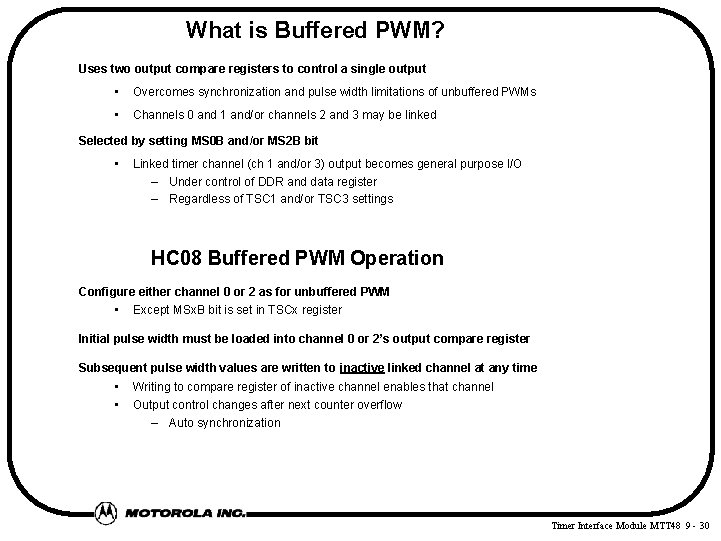

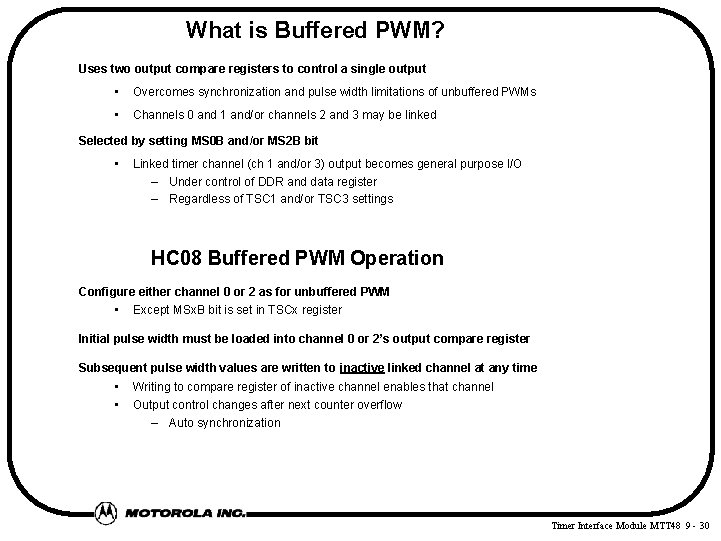

What is Buffered PWM? Uses two output compare registers to control a single output • Overcomes synchronization and pulse width limitations of unbuffered PWMs • Channels 0 and 1 and/or channels 2 and 3 may be linked Selected by setting MS 0 B and/or MS 2 B bit • Linked timer channel (ch 1 and/or 3) output becomes general purpose I/O – Under control of DDR and data register – Regardless of TSC 1 and/or TSC 3 settings HC 08 Buffered PWM Operation Configure either channel 0 or 2 as for unbuffered PWM • Except MSx. B bit is set in TSCx register Initial pulse width must be loaded into channel 0 or 2’s output compare register Subsequent pulse width values are written to inactive linked channel at any time • • Writing to compare register of inactive channel enables that channel Output control changes after next counter overflow – Auto synchronization Timer Interface Module MTT 48 9 - 30

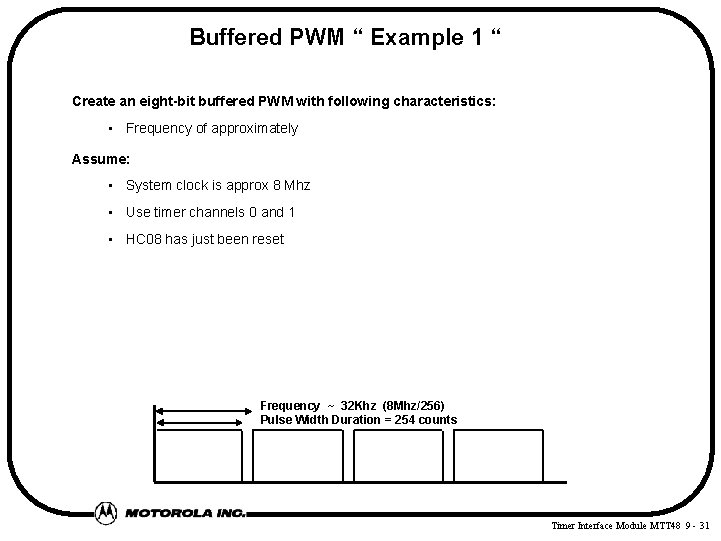

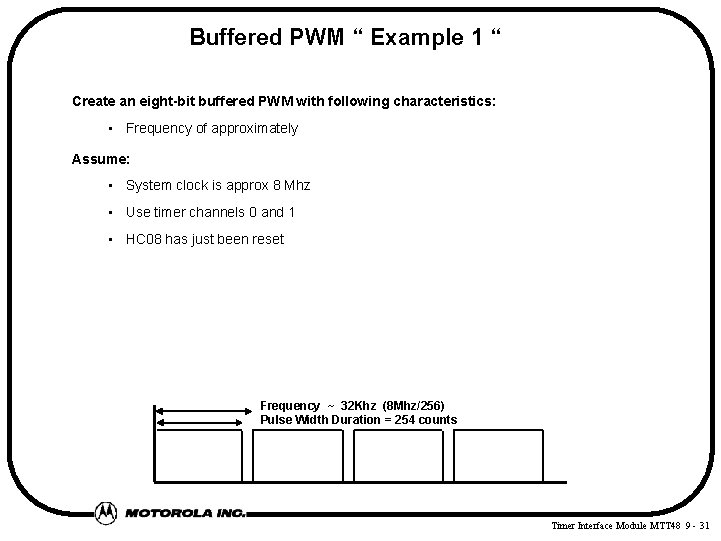

Buffered PWM “ Example 1 “ Create an eight-bit buffered PWM with following characteristics: • Frequency of approximately Assume: • System clock is approx 8 Mhz • Use timer channels 0 and 1 • HC 08 has just been reset Frequency ~ 32 Khz (8 Mhz/256) Pulse Width Duration = 254 counts Timer Interface Module MTT 48 9 - 31

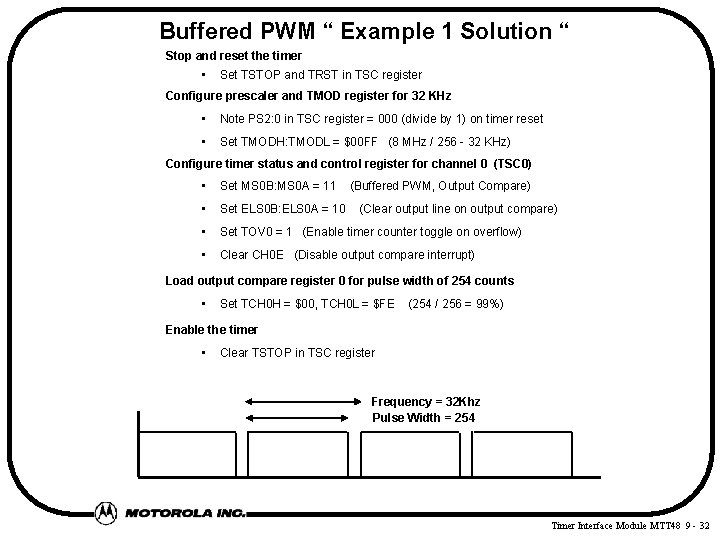

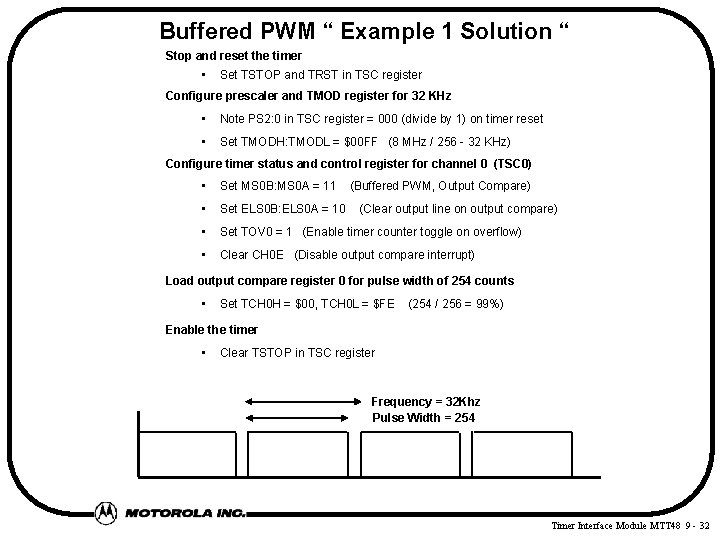

Buffered PWM “ Example 1 Solution “ Stop and reset the timer • Set TSTOP and TRST in TSC register Configure prescaler and TMOD register for 32 KHz • Note PS 2: 0 in TSC register = 000 (divide by 1) on timer reset • Set TMODH: TMODL = $00 FF (8 MHz / 256 32 KHz) Configure timer status and control register for channel 0 (TSC 0) • Set MS 0 B: MS 0 A = 11 • Set ELS 0 B: ELS 0 A = 10 • Set TOV 0 = 1 (Enable timer counter toggle on overflow) • Clear CH 0 E (Disable output compare interrupt) (Buffered PWM, Output Compare) (Clear output line on output compare) Load output compare register 0 for pulse width of 254 counts • Set TCH 0 H = $00, TCH 0 L = $FE (254 / 256 = 99%) Enable the timer • Clear TSTOP in TSC register Frequency = 32 Khz Pulse Width = 254 Timer Interface Module MTT 48 9 - 32

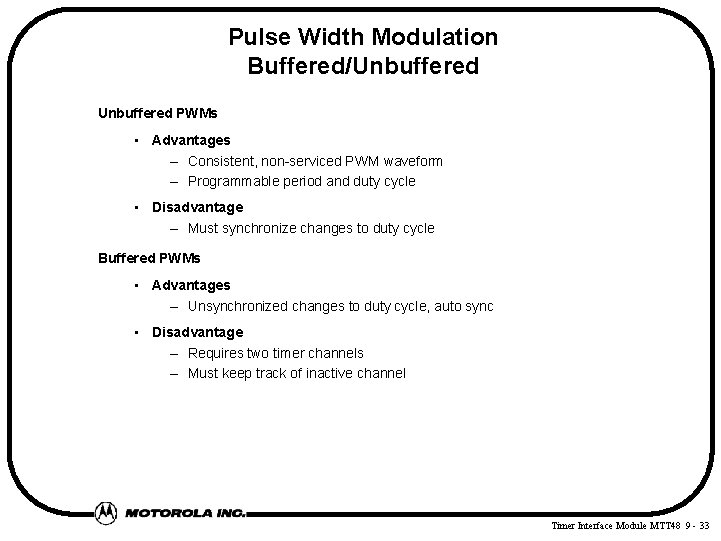

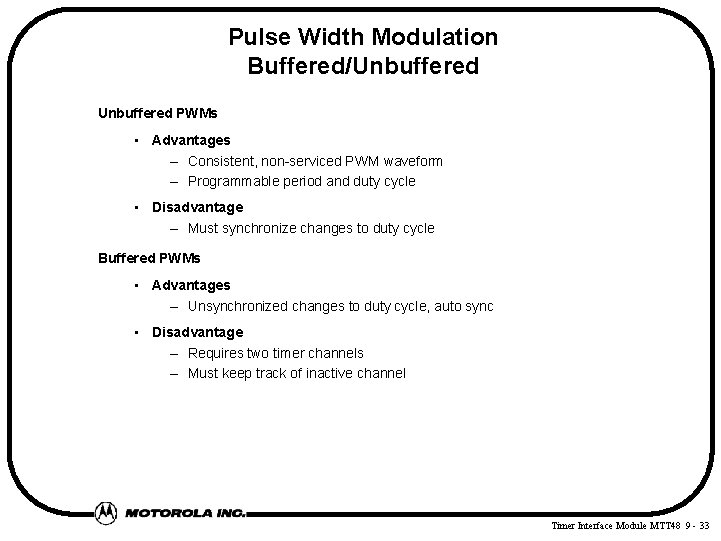

Pulse Width Modulation Buffered/Unbuffered PWMs • Advantages – Consistent, non serviced PWM waveform – Programmable period and duty cycle • Disadvantage – Must synchronize changes to duty cycle Buffered PWMs • Advantages – Unsynchronized changes to duty cycle, auto sync • Disadvantage – Requires two timer channels – Must keep track of inactive channel Timer Interface Module MTT 48 9 - 33

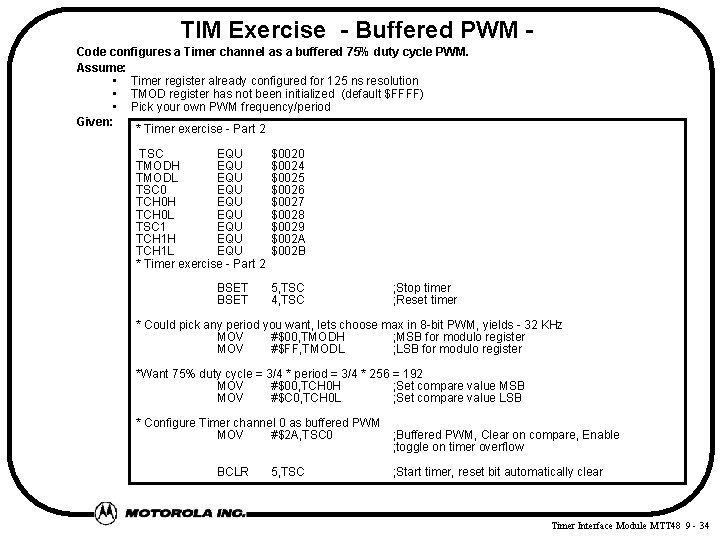

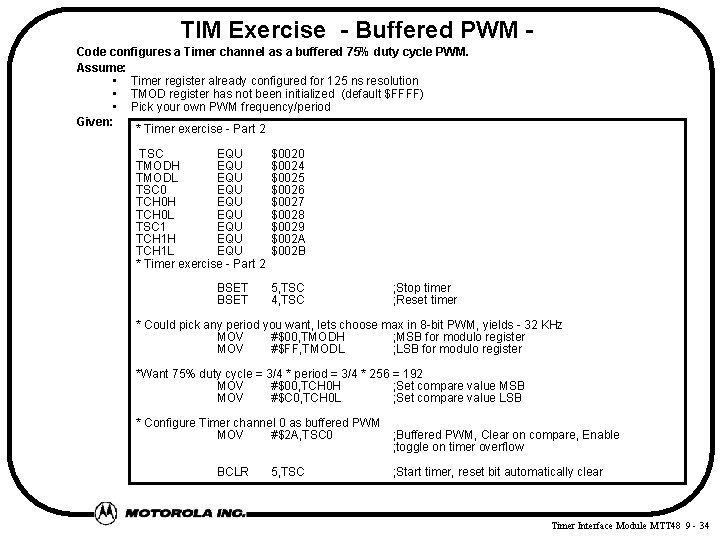

TIM Exercise - Buffered PWM Code configures a Timer channel as a buffered 75% duty cycle PWM. Assume: • Timer register already configured for 125 ns resolution • TMOD register has not been initialized (default $FFFF) • Pick your own PWM frequency/period Given: * Timer exercise Part 2 TSC EQU TMODH EQU TMODL EQU TSC 0 EQU TCH 0 H EQU TCH 0 L EQU TSC 1 EQU TCH 1 H EQU TCH 1 L EQU * Timer exercise Part 2 BSET $0020 $0024 $0025 $0026 $0027 $0028 $0029 $002 A $002 B 5, TSC 4, TSC ; Stop timer ; Reset timer * Could pick any period you want, lets choose max in 8 bit PWM, yields 32 KHz MOV #$00, TMODH ; MSB for modulo register MOV #$FF, TMODL ; LSB for modulo register *Want 75% duty cycle = 3/4 * period = 3/4 * 256 = 192 MOV #$00, TCH 0 H ; Set compare value MSB MOV #$C 0, TCH 0 L ; Set compare value LSB * Configure Timer channel 0 as buffered PWM MOV #$2 A, TSC 0 ; Buffered PWM, Clear on compare, Enable ; toggle on timer overflow BCLR 5, TSC ; Start timer, reset bit automatically clear Timer Interface Module MTT 48 9 - 34

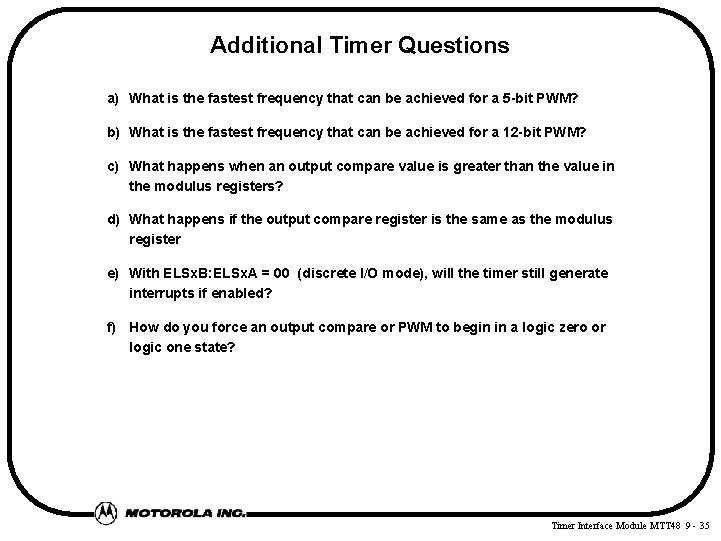

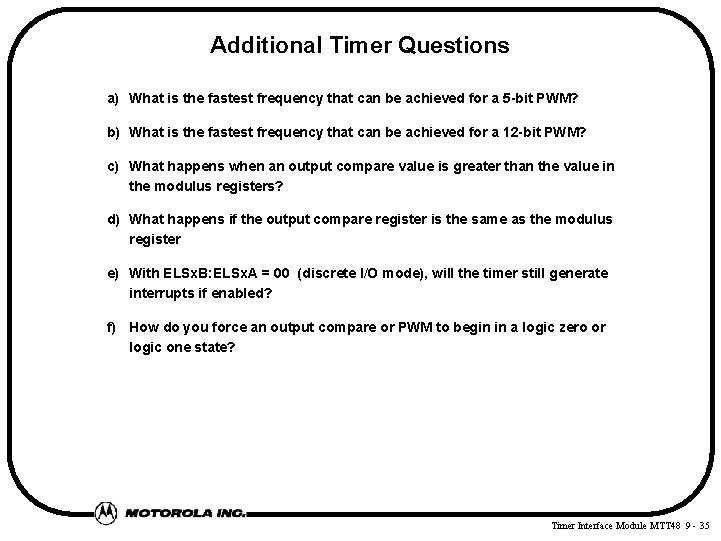

Additional Timer Questions a) What is the fastest frequency that can be achieved for a 5 -bit PWM? b) What is the fastest frequency that can be achieved for a 12 -bit PWM? c) What happens when an output compare value is greater than the value in the modulus registers? d) What happens if the output compare register is the same as the modulus register e) With ELSx. B: ELSx. A = 00 (discrete I/O mode), will the timer still generate interrupts if enabled? f) How do you force an output compare or PWM to begin in a logic zero or logic one state? Timer Interface Module MTT 48 9 - 35

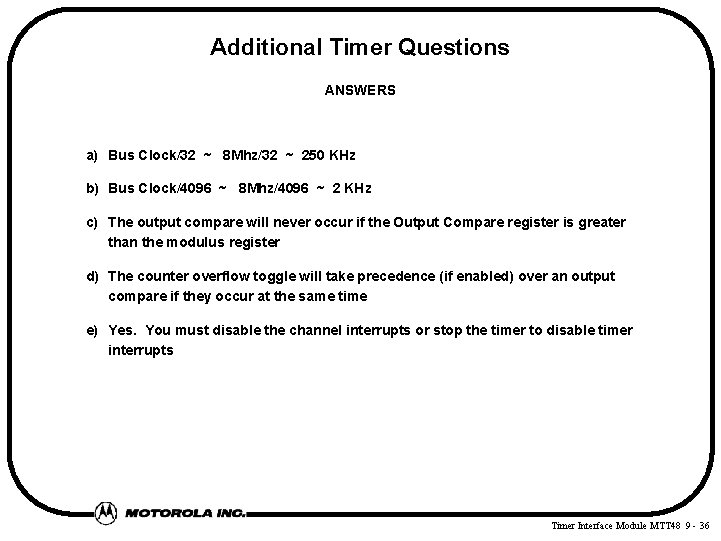

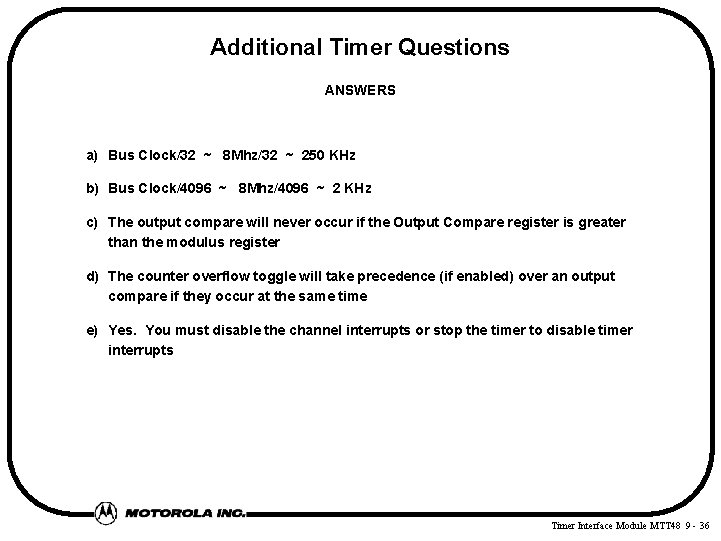

Additional Timer Questions ANSWERS a) Bus Clock/32 ~ 8 Mhz/32 ~ 250 KHz b) Bus Clock/4096 ~ 8 Mhz/4096 ~ 2 KHz c) The output compare will never occur if the Output Compare register is greater than the modulus register d) The counter overflow toggle will take precedence (if enabled) over an output compare if they occur at the same time e) Yes. You must disable the channel interrupts or stop the timer to disable timer interrupts Timer Interface Module MTT 48 9 - 36

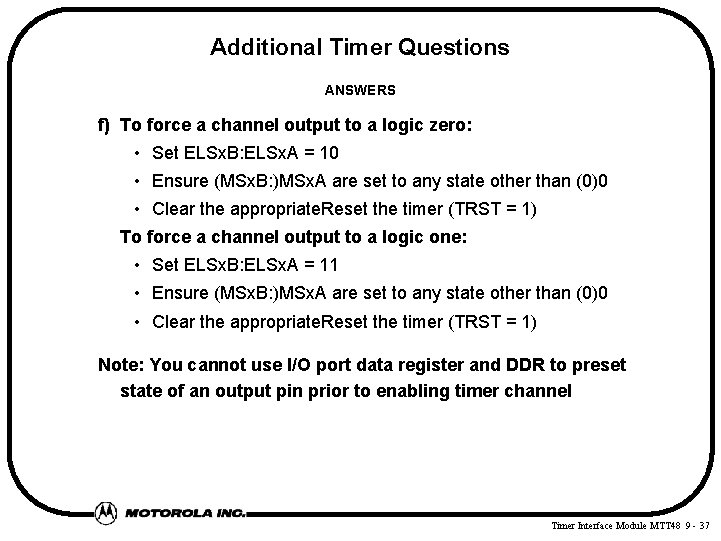

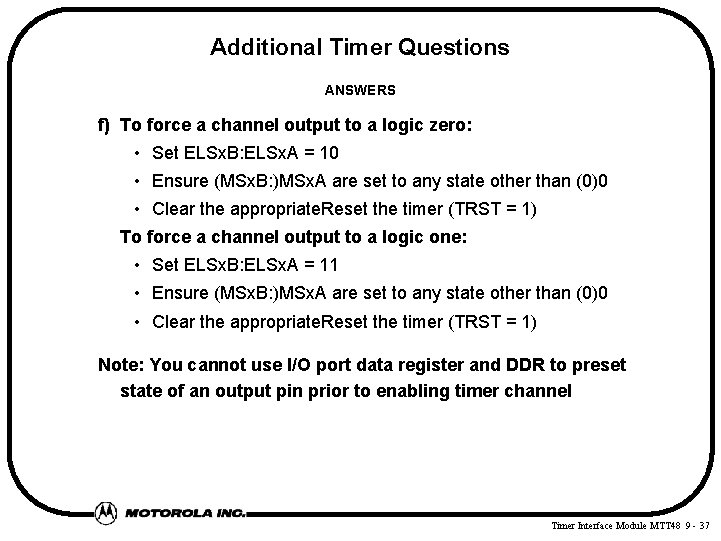

Additional Timer Questions ANSWERS f) To force a channel output to a logic zero: • Set ELSx. B: ELSx. A = 10 • Ensure (MSx. B: )MSx. A are set to any state other than (0)0 • Clear the appropriate. Reset the timer (TRST = 1) To force a channel output to a logic one: • Set ELSx. B: ELSx. A = 11 • Ensure (MSx. B: )MSx. A are set to any state other than (0)0 • Clear the appropriate. Reset the timer (TRST = 1) Note: You cannot use I/O port data register and DDR to preset state of an output pin prior to enabling timer channel Timer Interface Module MTT 48 9 - 37

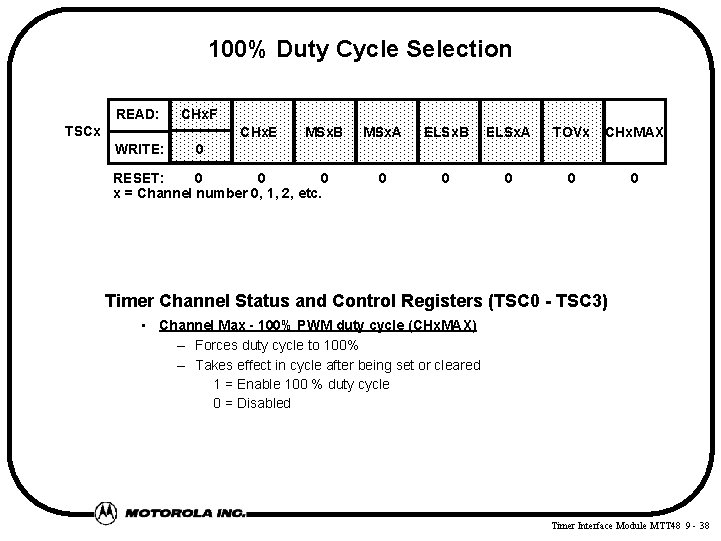

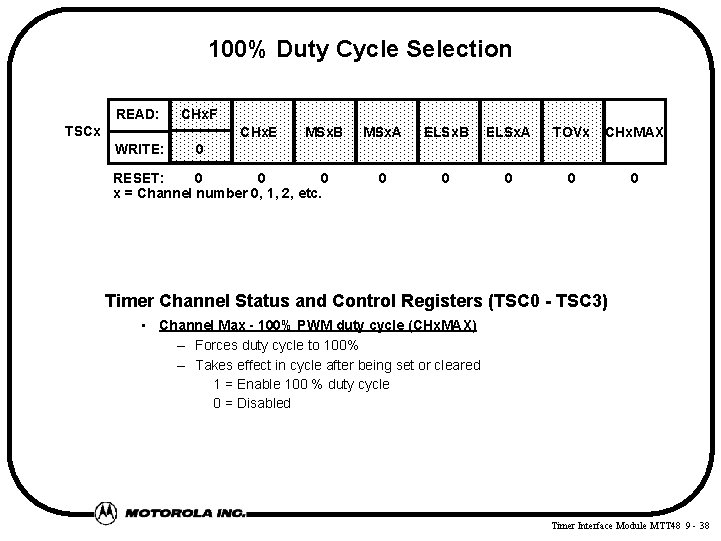

100% Duty Cycle Selection READ: CHx. F TSCx CHx. E WRITE: MSx. B MSx. A ELSx. B ELSx. A TOVx CHx. MAX 0 0 0 RESET: 0 0 0 x = Channel number 0, 1, 2, etc. Timer Channel Status and Control Registers (TSC 0 - TSC 3) • Channel Max - 100% PWM duty cycle (CHx. MAX) – Forces duty cycle to 100% – Takes effect in cycle after being set or cleared 1 = Enable 100 % duty cycle 0 = Disabled Timer Interface Module MTT 48 9 - 38

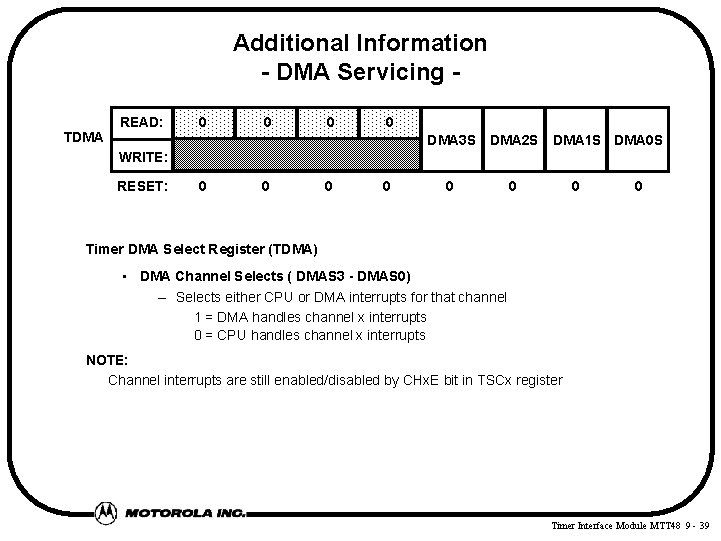

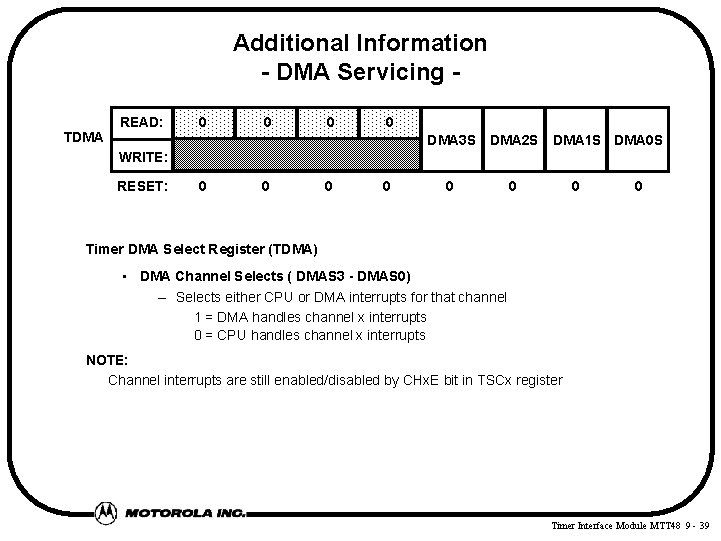

Additional Information - DMA Servicing TDMA READ: 0 0 DMA 3 S DMA 2 S DMA 1 S DMA 0 S WRITE: RESET: 0 0 0 0 Timer DMA Select Register (TDMA) • DMA Channel Selects ( DMAS 3 - DMAS 0) – Selects either CPU or DMA interrupts for that channel 1 = DMA handles channel x interrupts 0 = CPU handles channel x interrupts NOTE: Channel interrupts are still enabled/disabled by CHx. E bit in TSCx register Timer Interface Module MTT 48 9 - 39

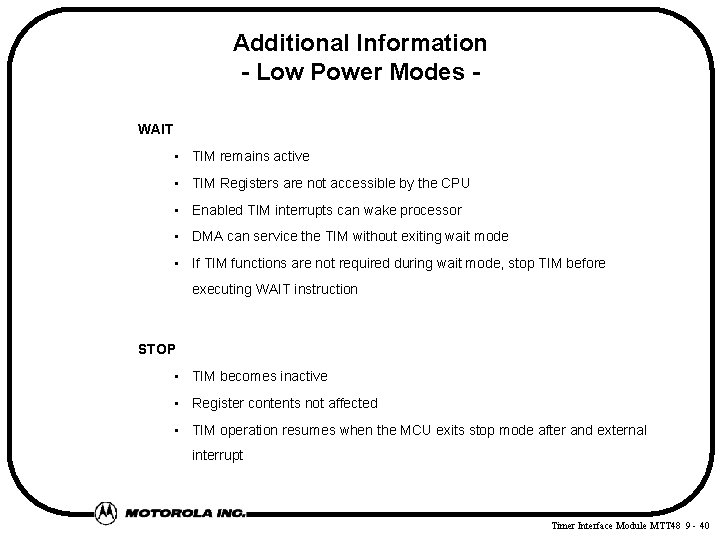

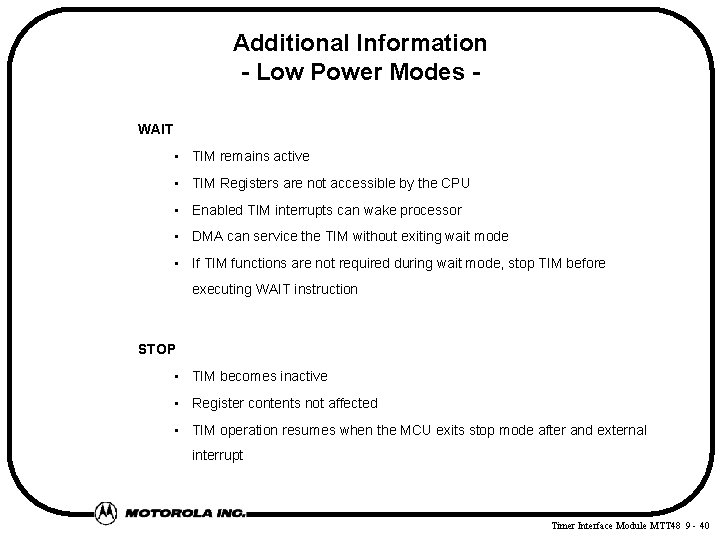

Additional Information - Low Power Modes WAIT • TIM remains active • TIM Registers are not accessible by the CPU • Enabled TIM interrupts can wake processor • DMA can service the TIM without exiting wait mode • If TIM functions are not required during wait mode, stop TIM before executing WAIT instruction STOP • TIM becomes inactive • Register contents not affected • TIM operation resumes when the MCU exits stop mode after and external interrupt Timer Interface Module MTT 48 9 - 40

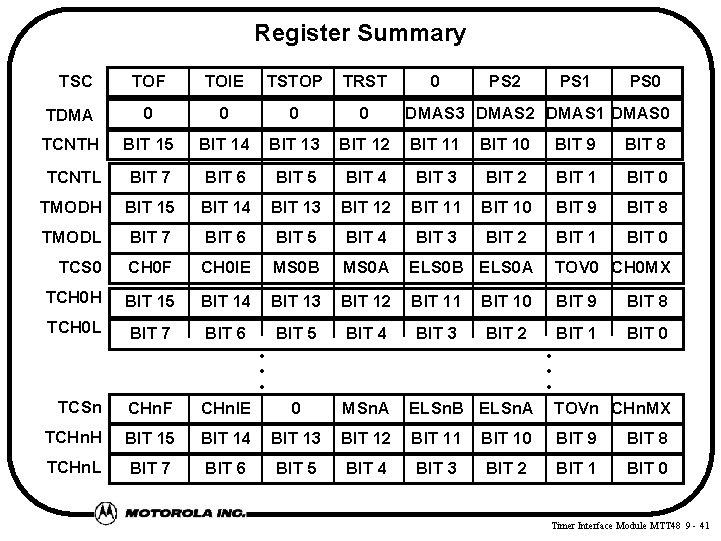

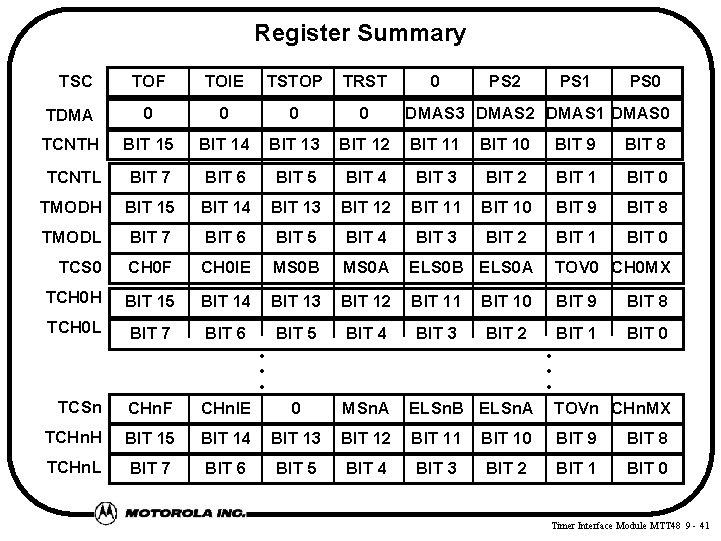

Register Summary TSC TOF TOIE TSTOP TRST 0 PS 2 PS 1 PS 0 TDMA 0 0 TCNTH BIT 15 BIT 14 BIT 13 BIT 12 BIT 11 BIT 10 BIT 9 BIT 8 TCNTL BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 TMODH BIT 15 BIT 14 BIT 13 BIT 12 BIT 11 BIT 10 BIT 9 BIT 8 TMODL BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 TCS 0 CH 0 F CH 0 IE MS 0 B MS 0 A ELS 0 B ELS 0 A TOV 0 CH 0 MX TCH 0 H BIT 15 BIT 14 BIT 13 BIT 12 BIT 11 BIT 10 BIT 9 BIT 8 TCH 0 L BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 DMAS 3 DMAS 2 DMAS 1 DMAS 0 • • • TCSn CHn. F CHn. IE 0 MSn. A ELSn. B ELSn. A TOVn CHn. MX TCHn. H BIT 15 BIT 14 BIT 13 BIT 12 BIT 11 BIT 10 BIT 9 BIT 8 TCHn. L BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 Timer Interface Module MTT 48 9 - 41

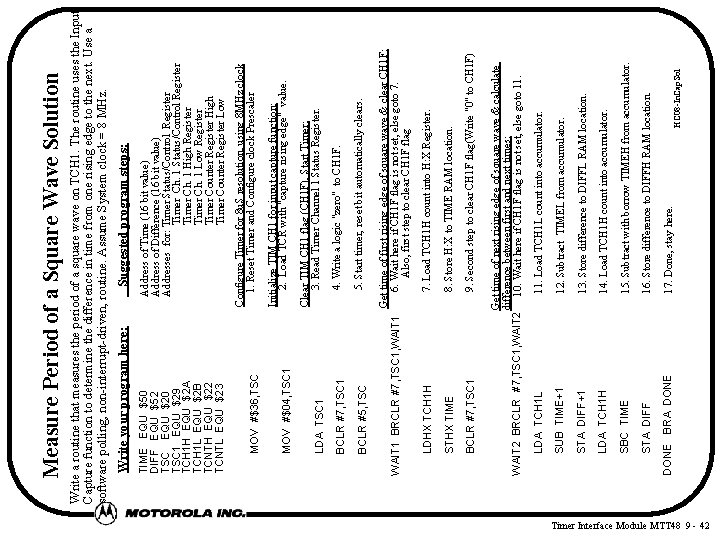

Timer Interface Module MTT 48 9 - 42 8. Store H: X to TIME RAM location. 9. Second step to clear CH 1 F flag(Write "0" to CH 1 F) STHX TIME BCLR #7, TSC 1 15. Subtract with borrow TIMEH from accumulator. 16. Store difference to DIFFH RAM location. SBC TIME STA DIFF HC 08 -In. Cap. Sol 14. Load TCH 1 H count into accumulator. LDA TCH 1 H 17. Done, stay here. 13. Store difference to DIFFL RAM location. STA DIFF+1 DONE BRA DONE 12. Subtract TIMEL from accumulator. 11. Load TCH 1 L count into accumulator. SUB TIME+1 LDA TCH 1 L Get time of next rising edge of square wave & calculate difference between first and next times: WAIT 2 BRCLR #7, TSC 1, WAIT 2 10. Wait here if CH 1 F flag is not set, else goto 11. 7. Load TCH 1 H count into H: X Register. Get time of first rising edge of square wave & clear CH 1 F: 6. Wait here if CH 1 F flag is not set, else goto 7. Also, first step to clear CH 1 F flag 5. Start timer, reset bit automatically clears. 4. Write a logic "zero" to CH 1 F. Clear TIM CH 1 flag (CH 1 F), Start Timer; 3. Read Timer Channel 1 Status Register. Initialize TIM CH 1 for input capture function: 2. Load TCR with "capture rising edge" value. Configure Timer for 8 u. S resolution, using 8 MHz clock 1. Reset Timer and Configure clock Prescaler Address of Time (16 bit value) Address of Difference (16 bit value) Addresses for: Timer Status/Control Register Timer Ch. 1 High Register Timer Ch. 1 Low Register Timer Counter Register High Timer Counter Register Low Suggested program steps: LDHX TCH 1 H WAIT 1 BRCLR #7, TSC 1, WAIT 1 BCLR #5, TSC BCLR #7, TSC 1 LDA TSC 1 MOV #$04, TSC 1 MOV #$36, TSC TIME EQU $50 DIFF EQU $52 TSC EQU $20 TSC 1 EQU $29 TCH 1 H EQU $2 A TCH 1 L EQU $2 B TCNTH EQU $22 TCNTL EQU $23 Write your program here: Write a routine that measures the period of a square wave on TCH 1. The routine uses the Input Capture function to determine the difference in time from one rising edge to the next. Use a software polling, non-interrupt-driven, routine. Assume System clock = 8 MHz. Measure Period of a Square Wave Solution

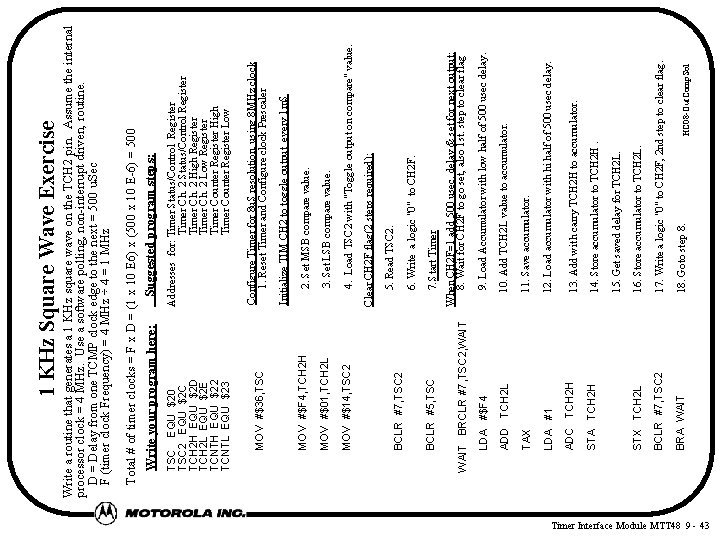

Timer Interface Module MTT 48 9 - 43 4. Load TSC 2 with "Toggle output on compare" value. MOV #$14, TSC 2 11. Save accumulator. 12. Load accumulator with hi half of 500 usec delay. TAX LDA #1 17. Write a logic "0" to CH 2 F, 2 nd step to clear flag. 18. Goto step 8. BCLR #7, TSC 2 BRA WAIT HC 08 -Out. Comp. Sol 16. Store accumulator to TCH 2 L. 15. Get saved delay for TCH 2 L. 14. Store accumulator to TCH 2 H. STX TCH 2 L STA TCH 2 H 13. Add with carry TCH 2 H to accumulator. 10. Add TCH 2 L value to accumulator. ADD TCH 2 L ADC TCH 2 H 9. Load Accumulator with low half of 500 usec delay. When CH 2 F=1 add 500 usec. delay & set for next output: 8. Wait for CH 2 F to go set, also 1 st. step to clear flag 7. Start Timer 6. Write a logic "0" to CH 2 F. 5. Read TSC 2. LDA #$F 4 WAIT BRCLR #7, TSC 2, WAIT BCLR #5, TSC BCLR #7, TSC 2 3. Set LSB compare value. MOV #$01, TCH 2 L Clear CH 2 F flag(2 steps required): 2. Set MSB compare value. Initialize TIM CH 2 to toggle output every 1 m. S Configure Timer for 8 u. S resolution, using 8 MHz clock 1. Reset Timer and Configure clock Prescaler Addresses for: Timer Status/Control Register Timer Ch. 2 High Register Timer Ch. 2 Low Register Timer Counter Register High Timer Counter Register Low Suggested program steps: MOV #$F 4, TCH 2 H MOV #$36, TSC EQU $20 TSC 2 EQU $2 C TCH 2 H EQU $2 D TCH 2 L EQU $2 E TCNTH EQU $22 TCNTL EQU $23 Write your program here: Total # of timer clocks = F x D = (1 x 10 E 6) x (500 x 10 E-6) = 500 Write a routine that generates a 1 KHz square wave on the TCH 2 pin. Assume the internal processor clock = 4 MHz. Use a software polling, non-interrupt driven, routine. D = Delay from one TCMP clock edge to the next = 500 u. Sec F (timer clock Frequency) = 4 MHz ÷ 4 = 1 MHz 1 KHz Square Wave Exercise

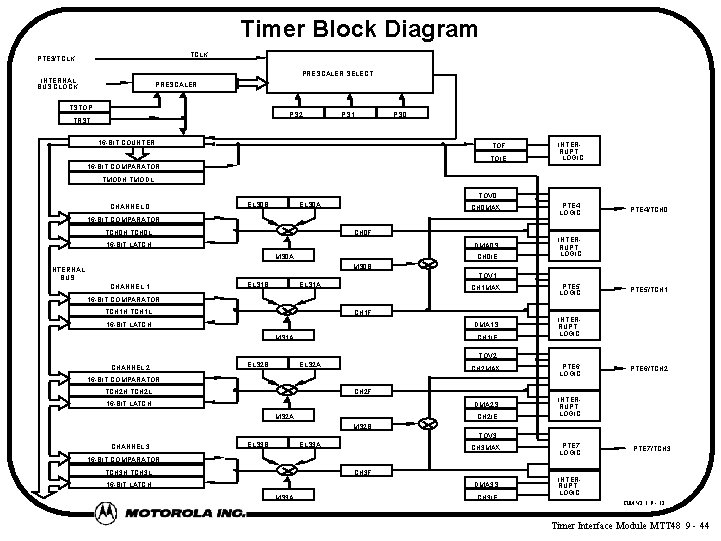

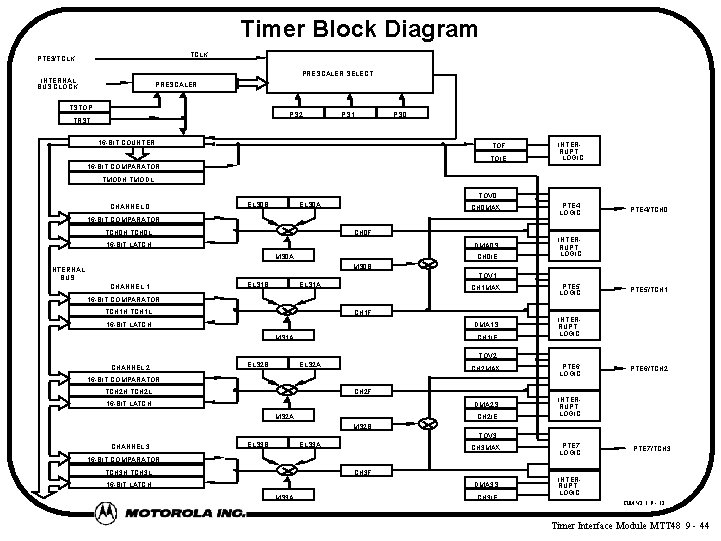

Timer Block Diagram TCLK PTE 3/TCLK PRESCALER SELECT INTERNAL BUS CLOCK PRESCALER TSTOP PS 2 TRST PS 1 16 BIT COUNTER PS 0 TOF TOIE 16 BIT COMPARATOR INTER RUPT LOGIC TMODH: TMODL TOV 0 CHANNEL 0 ELS 0 B ELS 0 A CH 0 MAX PTE 4 LOGIC DMA 0 S INTER RUPT LOGIC 16 BIT COMPARATOR TCH 0 H: TCH 0 L CH 0 F 16 BIT LATCH MS 0 A CH 0 IE PTE 4/TCH 0 MS 0 B INTERNAL BUS TOV 1 CHANNEL 1 ELS 1 B ELS 1 A CH 1 MAX PTE 5 LOGIC DMA 1 S INTER RUPT LOGIC 16 BIT COMPARATOR TCH 1 H: TCH 1 L CH 1 F 16 BIT LATCH MS 1 A CH 1 IE PTE 5/TCH 1 TOV 2 CHANNEL 2 ELS 2 B ELS 2 A CH 2 MAX PTE 6 LOGIC DMA 2 S INTER RUPT LOGIC 16 BIT COMPARATOR TCH 2 H: TCH 2 L CH 2 F 16 BIT LATCH MS 2 A CH 2 IE PTE 6/TCH 2 MS 2 B TOV 3 CHANNEL 3 ELS 3 B ELS 3 A CH 3 MAX PTE 7 LOGIC DMA 3 S INTER RUPT LOGIC 16 BIT COMPARATOR TCH 3 H: TCH 3 L CH 3 F 16 BIT LATCH MS 3 A CH 3 IE PTE 7/TCH 3 TIM V 2. 1 9 - 12 Timer Interface Module MTT 48 9 - 44