BREAK MODULE Break Module MTT 48 V 2

BREAK MODULE Break Module MTT 48 V 2. 1 16 - 1

Break Module Objective Learn how to use the BREAK function to generate a break interrupt that stops normal program flow at a defined address to enter background program. Break Module MTT 48 V 2. 1 16 - 3

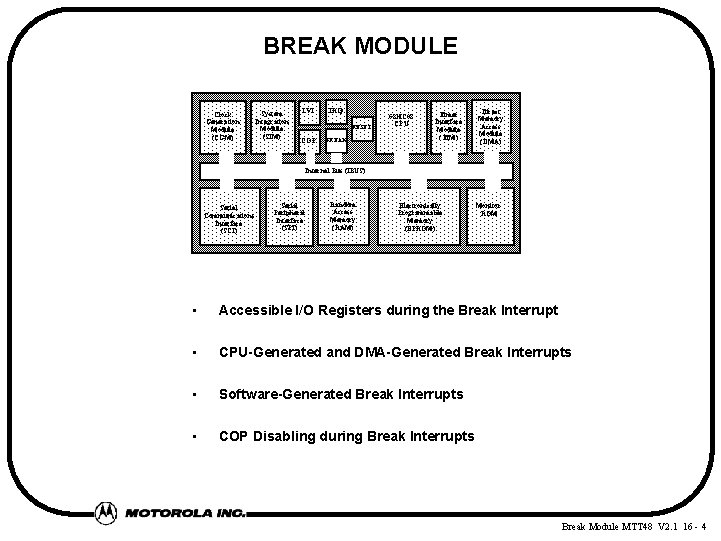

BREAK MODULE Clock Generation Module (CGM) System Integration Module (SIM) LVI IRQ COP BREAK RESET 68 HC 08 CPU Timer Interface Module (TIM) Direct Memory Access Module (DMA) Internal Bus (IBUS) Serial Communications Interface (SCI) Serial Peripheral Interface (SPI) Random Access Memory (RAM) Electronically Programmable Memory (EPROM) Monitor ROM • Accessible I/O Registers during the Break Interrupt • CPU-Generated and DMA-Generated Break Interrupts • Software-Generated Break Interrupts • COP Disabling during Break Interrupts Break Module MTT 48 V 2. 1 16 - 4

Break Module Operation • Internal address bus matches the value in the break address registers • Break module issues a breakpoint signal (BKPT) to the SIM • After completion of current CPU instruction – SIM cause CPU to load instruction register with SWI instruction – Program counter vectors to $FFFC and $FFFD ($FEFC and $FEFD in monitor mode) • Execute Break Interrupt Service Routine – Return from Interrupt(RTI) instruction in the break routine • Ends break interrupt • Returns MCU to normal operation Break Module MTT 48 V 2. 1 16 - 5

![Break Module Block Diagram IAB[15: 8] BREAK ADDRESS REGISTER HIGH 8 -BIT COMPARATOR IAB[15: Break Module Block Diagram IAB[15: 8] BREAK ADDRESS REGISTER HIGH 8 -BIT COMPARATOR IAB[15:](http://slidetodoc.com/presentation_image/ffe0ac536516f1ff6f2cbdefd3c33975/image-6.jpg)

Break Module Block Diagram IAB[15: 8] BREAK ADDRESS REGISTER HIGH 8 -BIT COMPARATOR IAB[15: 0] CONTROL BKPT (TO SIM) 8 -BIT COMPARATOR BREAK ADDRESS REGISTER LOW IAB[7: 0] Break Module MTT 48 V 2. 1 16 - 6

Events Leading to a Break interrupt • CPU-generated address (the address in the program counter) matches the contents of the break address registers. • During a DMA transfer, a DMA-generated address matches the contents of the break address registers. • Software writes a logic one to the BRKA bit in the break status and control register. Break Module MTT 48 V 2. 1 16 - 7

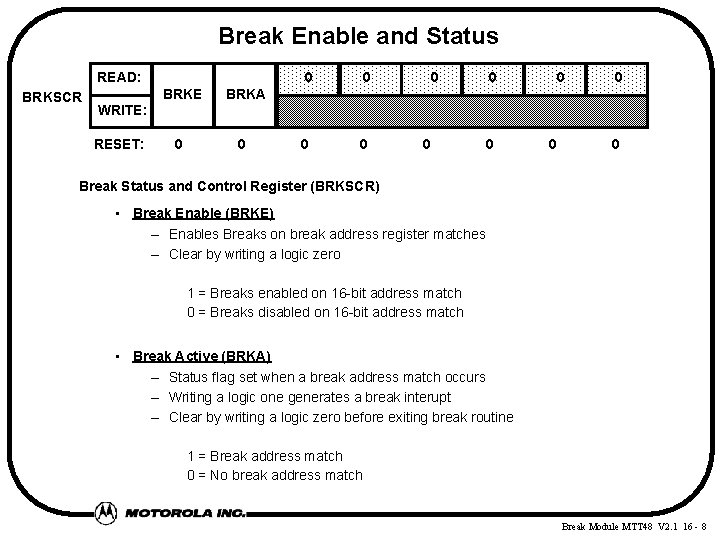

Break Enable and Status READ: BRKSCR BRKE BRKA 0 0 0 0 0 WRITE: RESET: 0 0 Break Status and Control Register (BRKSCR) • Break Enable (BRKE) – Enables Breaks on break address register matches – Clear by writing a logic zero 1 = Breaks enabled on 16 -bit address match 0 = Breaks disabled on 16 -bit address match • Break Active (BRKA) – Status flag set when a break address match occurs – Writing a logic one generates a break interupt – Clear by writing a logic zero before exiting break routine 1 = Break address match 0 = No break address match Break Module MTT 48 V 2. 1 16 - 8

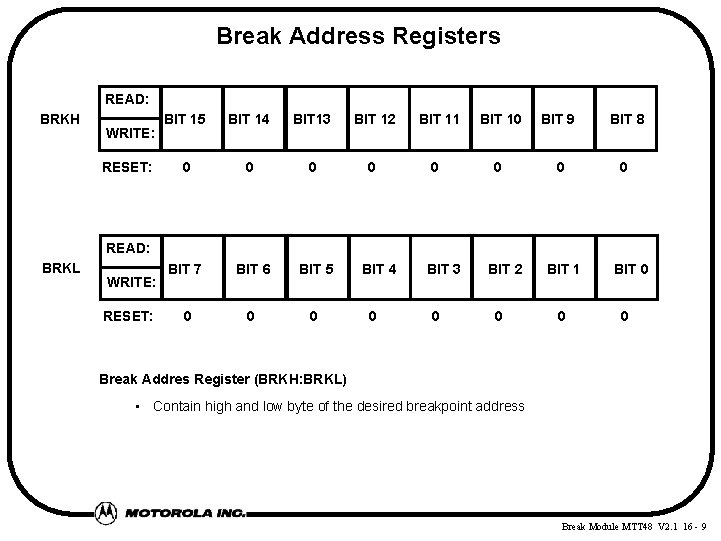

Break Address Registers READ: BRKH WRITE: RESET: BIT 15 BIT 14 BIT 13 BIT 12 0 0 BIT 7 BIT 6 BIT 5 0 0 0 BIT 11 0 BIT 10 BIT 9 BIT 8 0 0 0 READ: BRKL WRITE: RESET: BIT 4 0 BIT 3 0 BIT 2 0 BIT 1 0 BIT 0 0 Break Addres Register (BRKH: BRKL) • Contain high and low byte of the desired breakpoint address Break Module MTT 48 V 2. 1 16 - 9

Additional Information - Affected Modules during Break Interrupts Central Processor Unit (CPU) • CPU starts Break Interrupt • Begins after completion of CPU instruction in progress • Loads the instruction register with the SWI instruction • Loads the program counter with $FFFC: $FFFD ($FEFC: $FEFD in monitor mode) Timer Interface Module (TIM) • Timer Counter is stopped Computer Operating Properly (COP) • COP is disabled when VDD + VHI is preset on the RST pin Direct Memory Acces (DMA) • DMA is Inactive • If a DMA-generated address matches contents of the break address registers – Break interrupt begins at the end of current CPU instruction Break Module MTT 48 V 2. 1 16 - 10

Additional Information - Low Power Modes - Low Power modes • STOP – Break interrupt causes exit from stop mode – Sets the SBSW(SIM break Stop/Wait) bit in the SIM break status register • WAIT – Break Module Active – SBSW bit becomes set if a DMA-generated address matches the break address registers – DMA can use Break Status and Control Register(BRKSCR) as its destination address in order to write to the BRKA and BRKE bits during wait mode – SBSW(SIM break Stop/Wait) bit is set if DMA writes to BRKSCR Break Module MTT 48 V 2. 1 16 - 11

- Slides: 11