CLK CLKout DATAin DATAout CLK CLK Count 0s

- Slides: 56

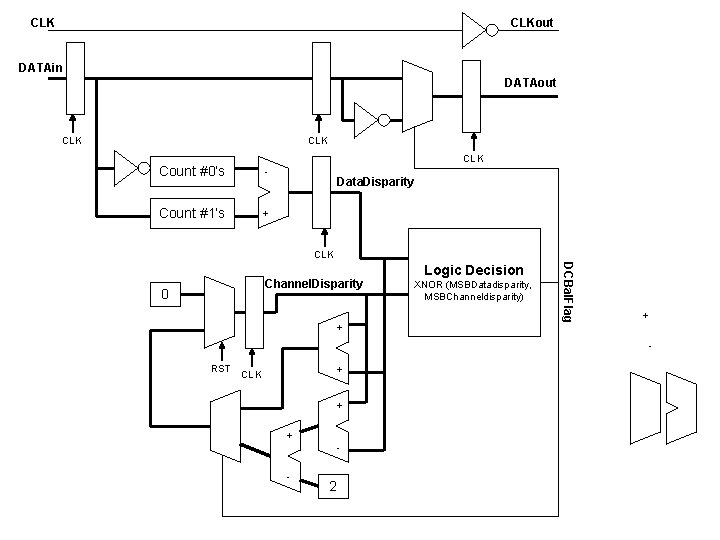

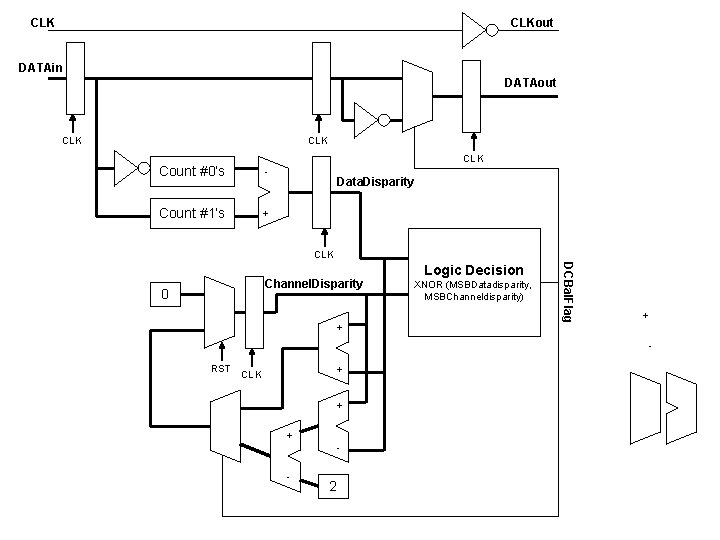

CLK CLKout DATAin DATAout CLK CLK Count #0’s - Count #1’s + Data. Disparity CLK 0 + Logic Decision XNOR (MSBDatadisparity, MSBChanneldisparity) DCBal. Flag Channel. Disparity + - RST + CLK + + - 2

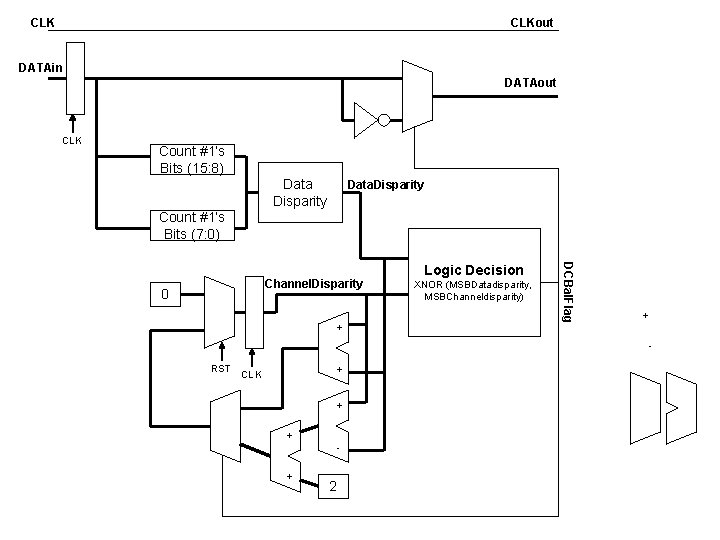

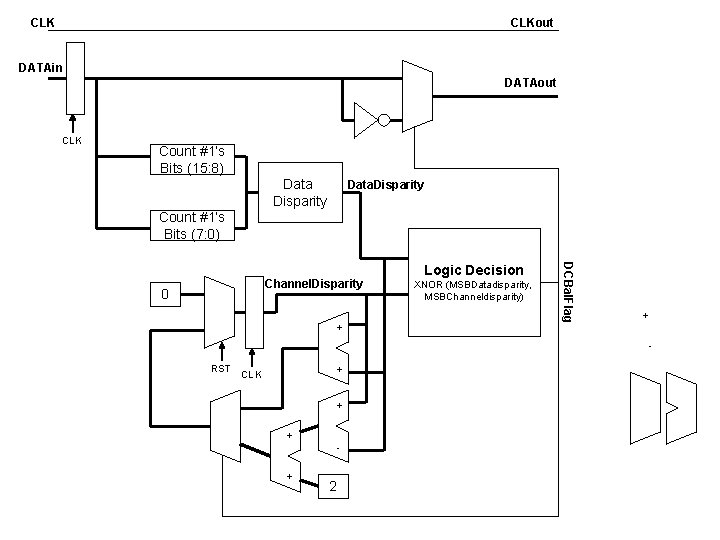

CLK CLKout DATAin DATAout CLK Count #1’s Bits (15: 8) Data Disparity Data. Disparity Count #1’s Bits (7: 0) 0 + Logic Decision XNOR (MSBDatadisparity, MSBChanneldisparity) DCBal. Flag Channel. Disparity + - RST + CLK + + + 2

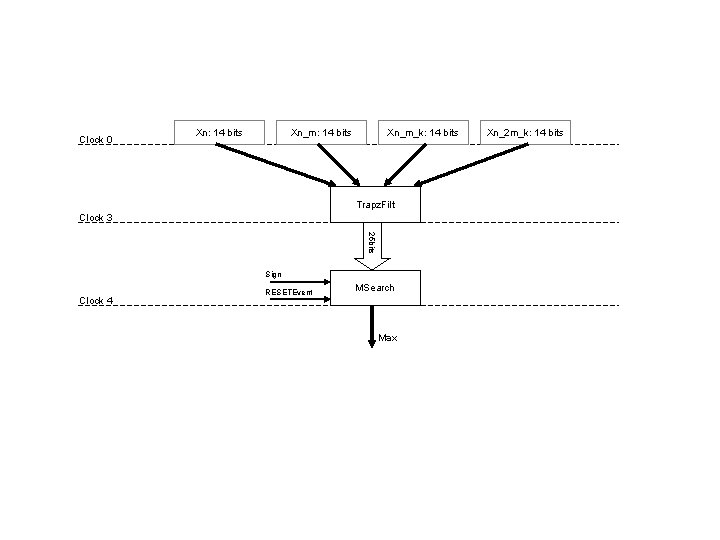

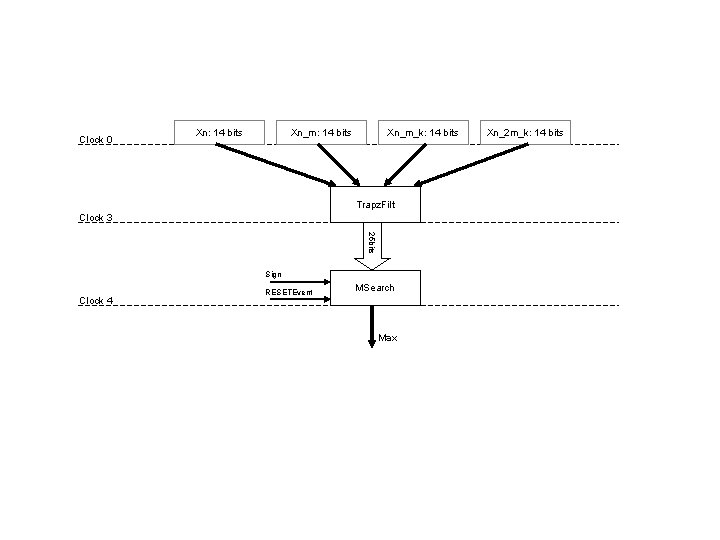

Clock 0 Xn: 14 bits Xn_m_k: 14 bits Trapz. Filt Clock 3 25 bits Sign Clock 4 RESETEvent MSearch Max Xn_2 m_k: 14 bits

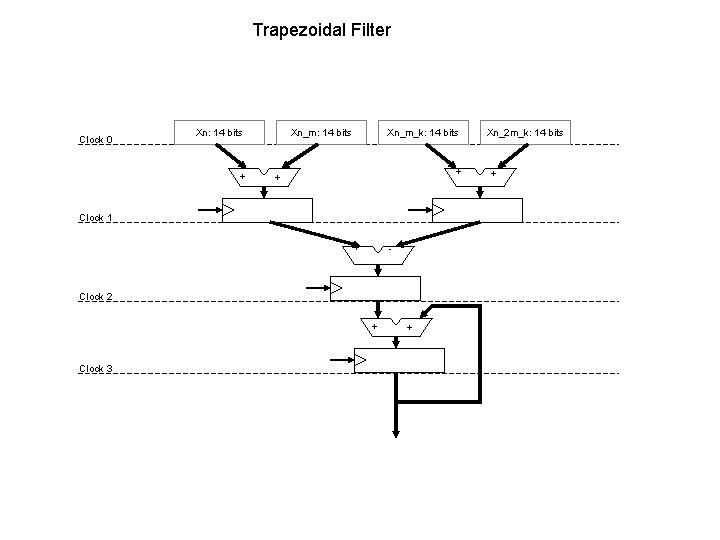

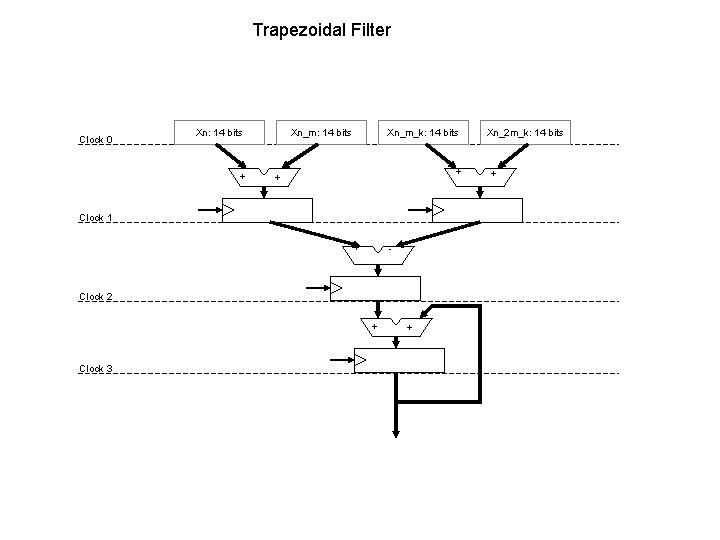

Trapezoidal Filter Clock 0 Xn: 14 bits + Xn_m: 14 bits Xn_m_k: 14 bits + + Clock 1 + - Clock 2 + Clock 3 + Xn_2 m_k: 14 bits +

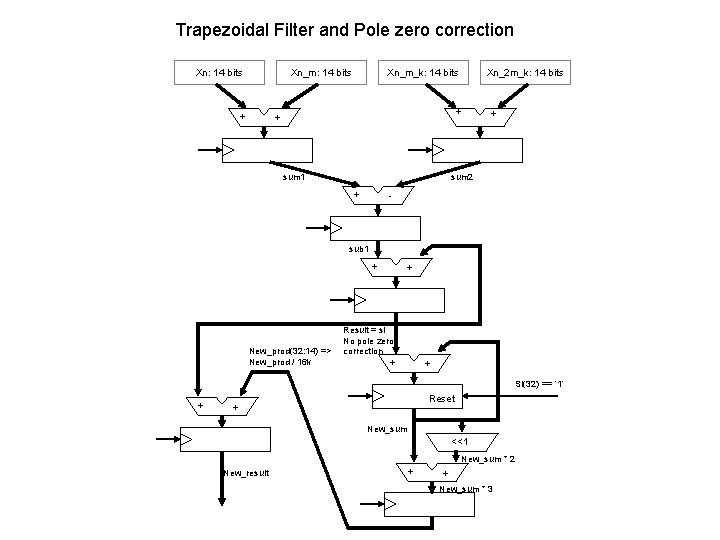

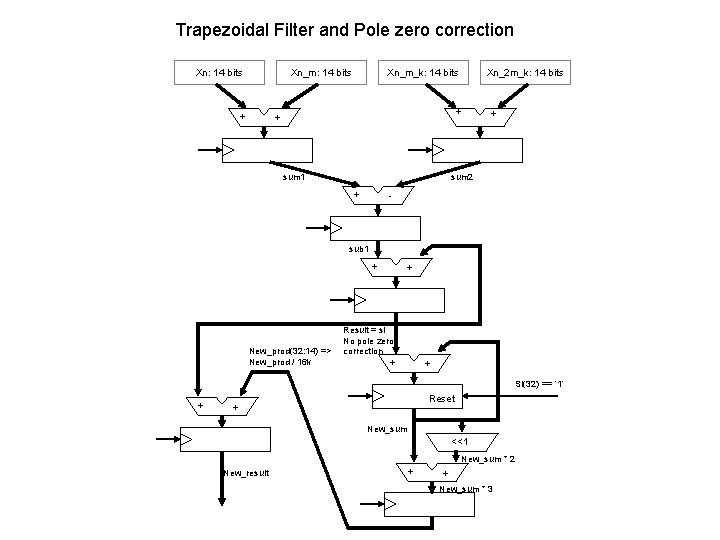

Trapezoidal Filter and Pole zero correction Xn: 14 bits Xn_m: 14 bits + Xn_m_k: 14 bits Xn_2 m_k: 14 bits + + sum 1 + sum 2 + - sub 1 + New_prod(32: 14) => New_prod / 16 k + Result = si No pole zero correction + + Si(32) == ‘ 1’ + Reset + New_sum <<1 New_sum * 2 New_result + + New_sum * 3

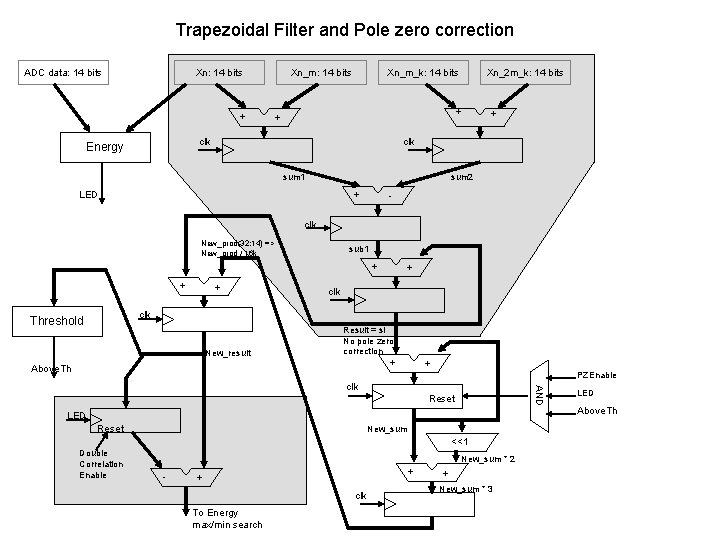

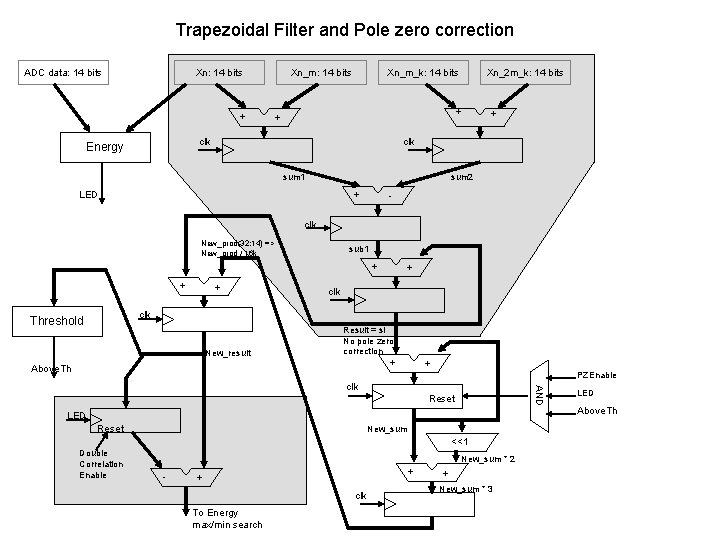

Trapezoidal Filter and Pole zero correction ADC data: 14 bits Xn: 14 bits + Xn_m: 14 bits Xn_m_k: 14 bits + + clk Energy Xn_2 m_k: 14 bits + clk sum 1 sum 2 LED + - clk New_prod(32: 14) => New_prod / 16 k sub 1 + + clk Threshold New_result Result = si No pole zero correction + Above. Th + PZEnable AND clk Reset LED Reset New_sum <<1 Double Correlation Enable New_sum * 2 - + + clk To Energy max/min search + New_sum * 3 LED Above. Th

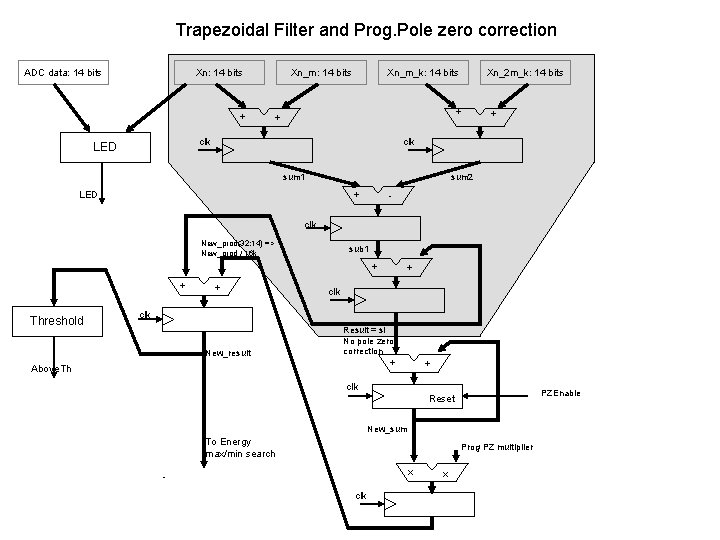

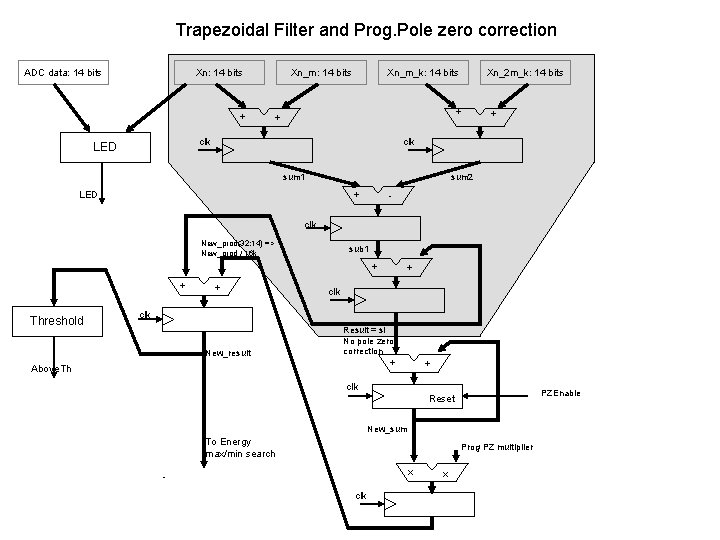

Trapezoidal Filter and Prog. Pole zero correction ADC data: 14 bits Xn: 14 bits + Xn_m: 14 bits Xn_m_k: 14 bits + + clk LED Xn_2 m_k: 14 bits + clk sum 1 sum 2 LED + - clk New_prod(32: 14) => New_prod / 16 k sub 1 + + Threshold + + clk New_result Result = si No pole zero correction + Above. Th + clk PZEnable Reset New_sum To Energy max/min search Prog PZ multiplier x clk x

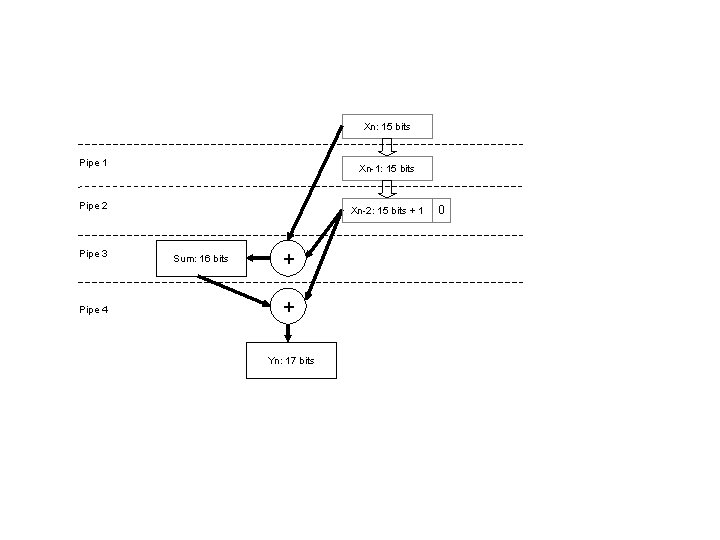

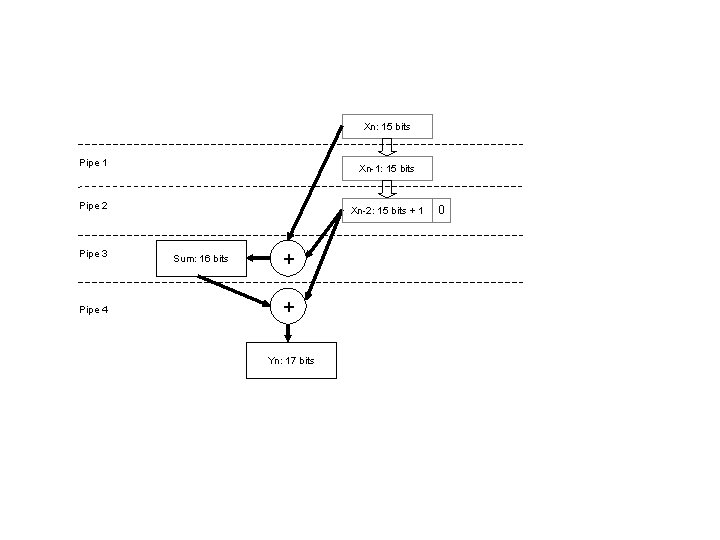

Xn: 15 bits Pipe 1 Xn-1: 15 bits Pipe 2 Pipe 3 Pipe 4 Xn-2: 15 bits + 1 Sum: 16 bits + + Yn: 17 bits 0

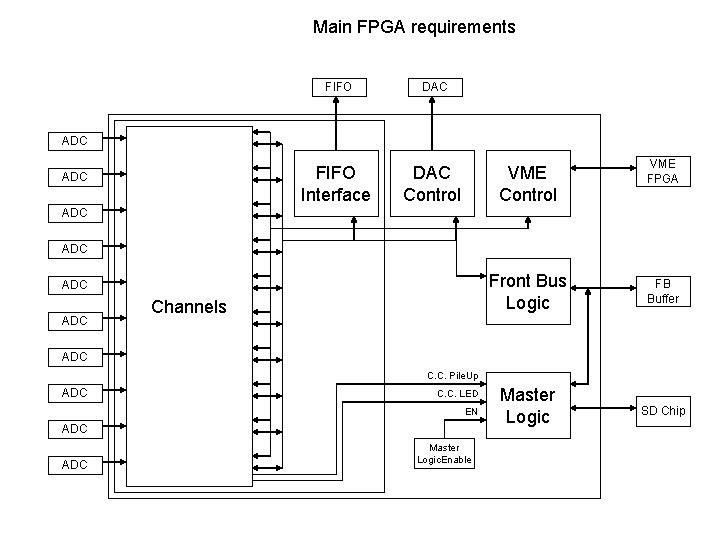

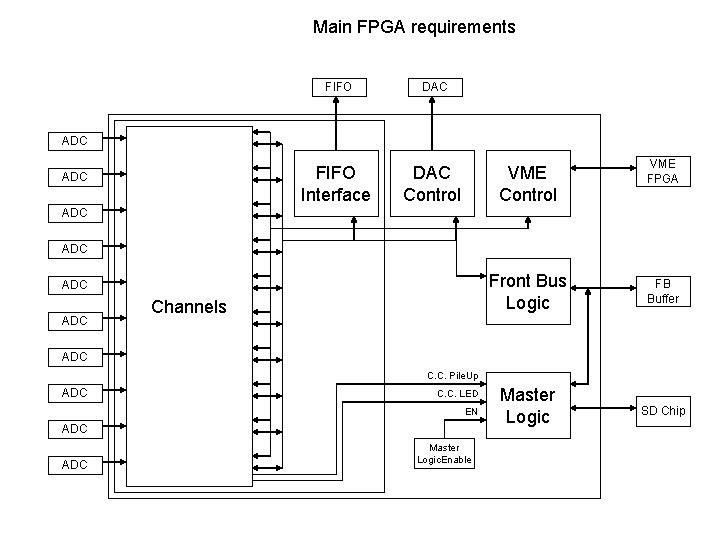

Main FPGA requirements FIFO DAC FIFO Interface DAC Control ADC VME Control VME FPGA ADC ADC Channels Front Bus Logic FB Buffer Master Logic SD Chip ADC C. C. Pile. Up ADC C. C. LED EN ADC Master Logic. Enable

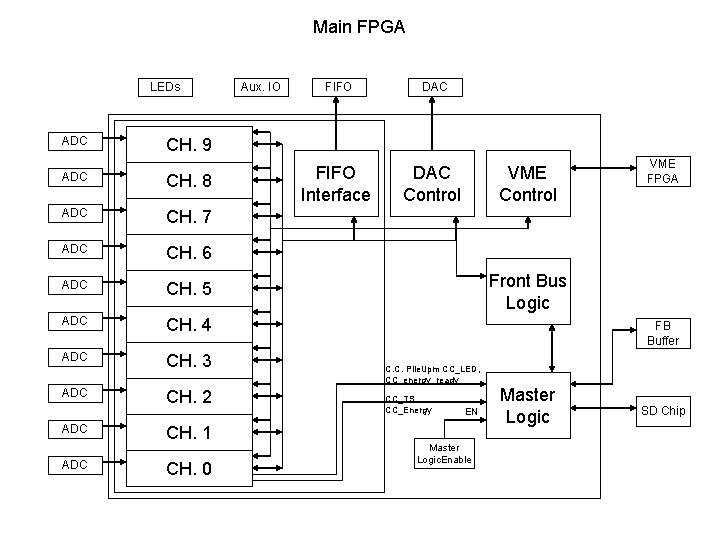

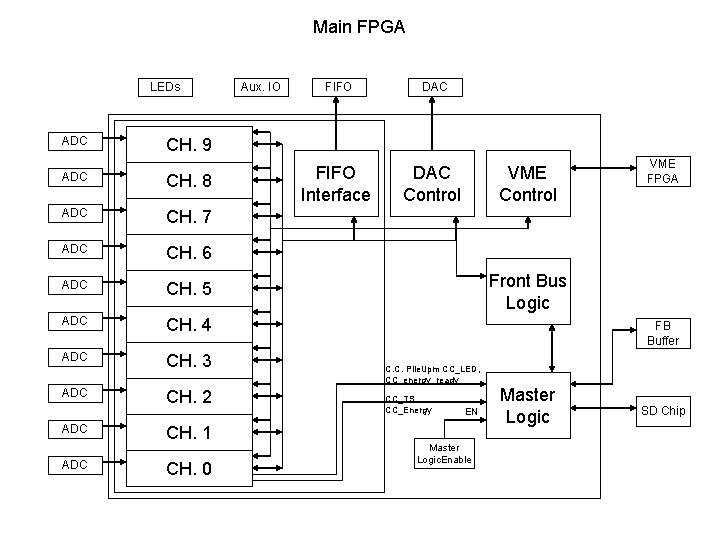

Main FPGA LEDs ADC CH. 8 ADC CH. 7 ADC CH. 6 ADC CH. 5 ADC CH. 4 ADC CH. 3 ADC FIFO DAC FIFO Interface DAC Control CH. 9 ADC Aux. IO CH. 2 CH. 1 CH. 0 VME Control VME FPGA Front Bus Logic FB Buffer C. C. Pile. Upm CC_LED, CC_energy_ready CC_TS, CC_Energy EN Master Logic. Enable Master Logic SD Chip

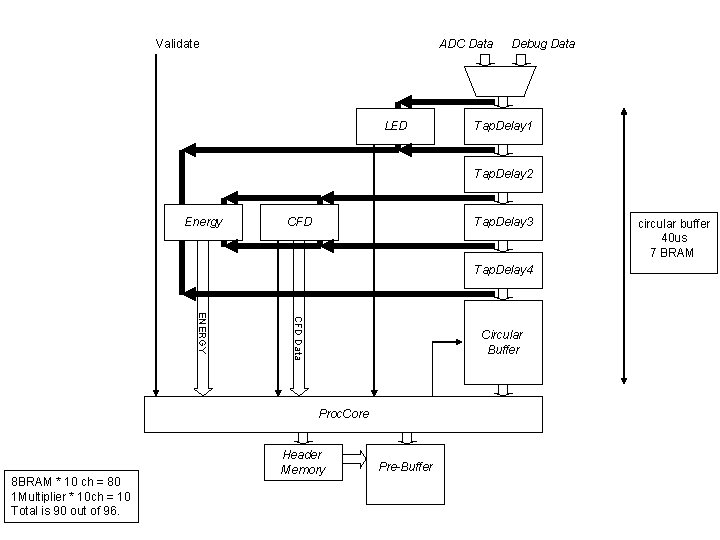

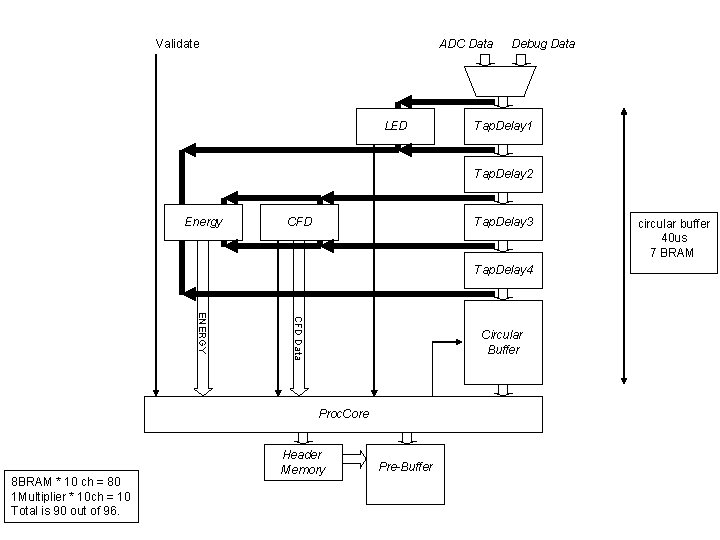

Validate ADC Data LED Debug Data Tap. Delay 1 Tap. Delay 2 Energy CFD Tap. Delay 3 Tap. Delay 4 CFD Data ENERGY Circular Buffer Proc. Core 8 BRAM * 10 ch = 80 1 Multiplier * 10 ch = 10 Total is 90 out of 96. Header Memory Pre-Buffer circular buffer 40 us 7 BRAM

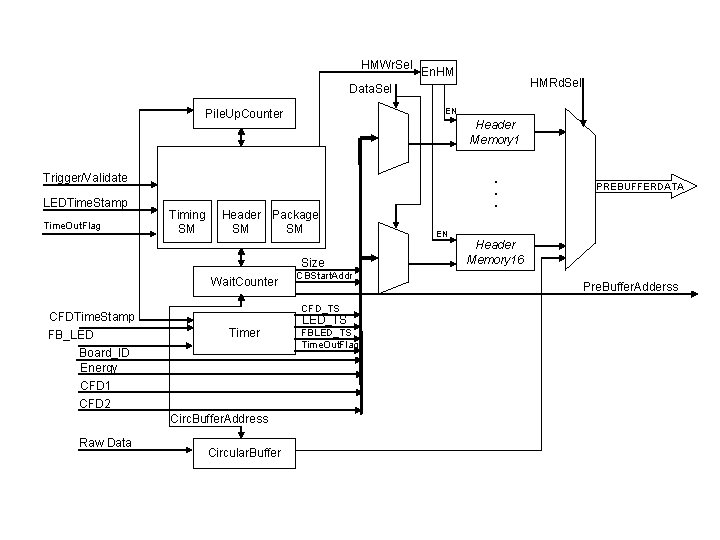

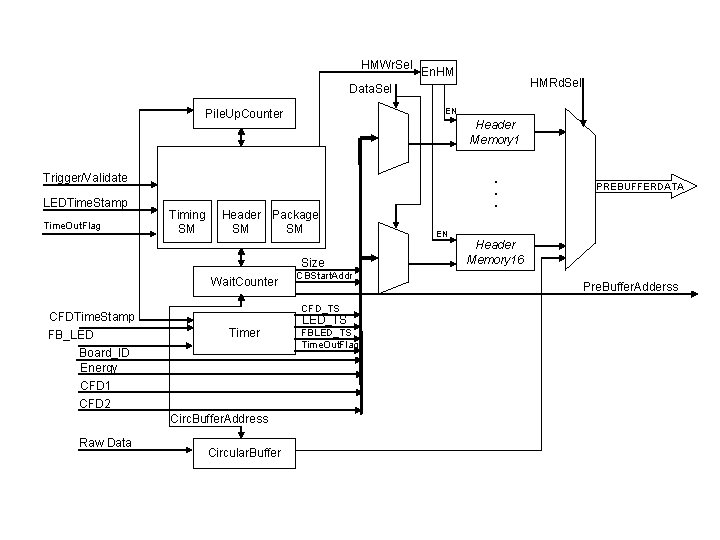

HMWr. Sel En. HM HMRd. Sel Data. Sel EN Pile. Up. Counter Header Memory 1 . . . Trigger/Validate LEDTime. Stamp Time. Out. Flag Timing SM Header Package SM SM Size Wait. Counter CFDTime. Stamp FB_LED Board_ID Energy CFD 1 CFD 2 CFD_TS LED_TS Timer Circ. Buffer. Address Raw Data CBStart. Addr Circular. Buffer FBLED_TS Time. Out. Flag EN PREBUFFERDATA Header Memory 16 Pre. Buffer. Adderss

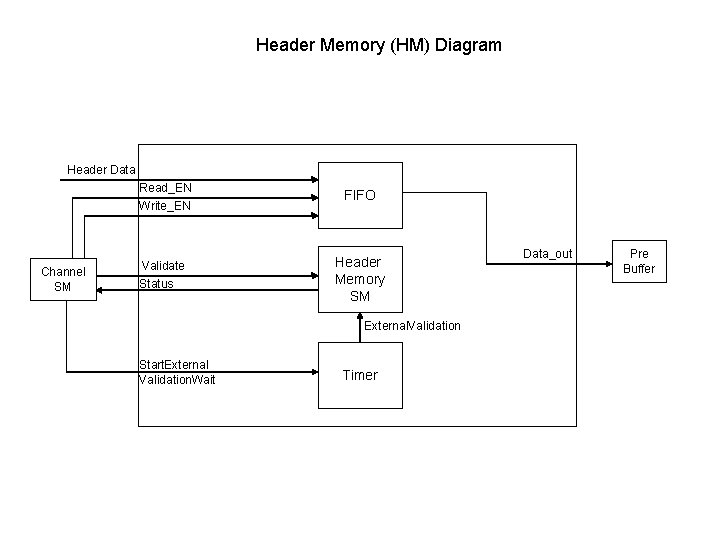

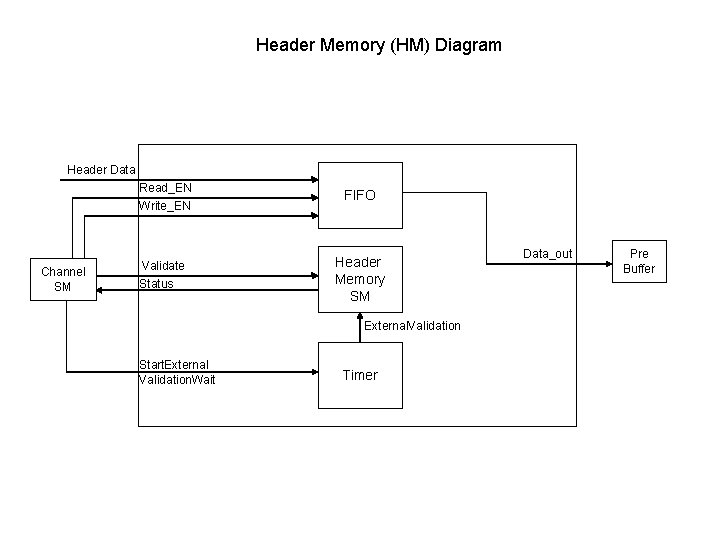

Header Memory (HM) Diagram Header Data Channel SM Read_EN Write_EN FIFO Validate Status Header Memory SM External. Validation Start. External Validation. Wait Timer Data_out Pre Buffer

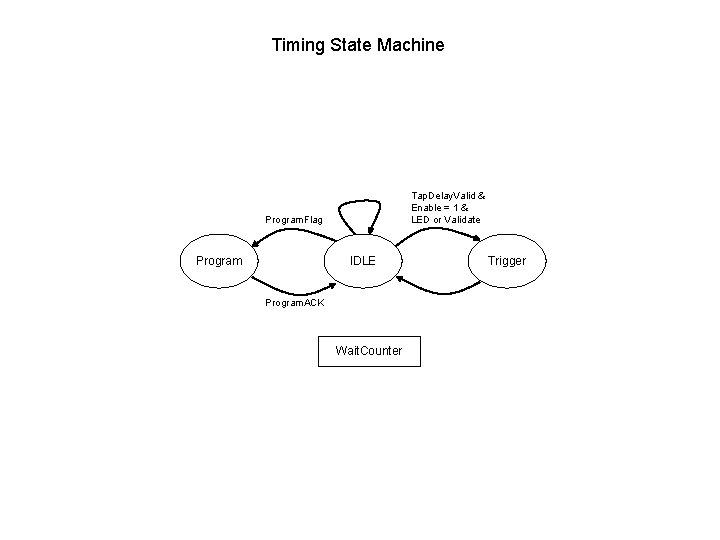

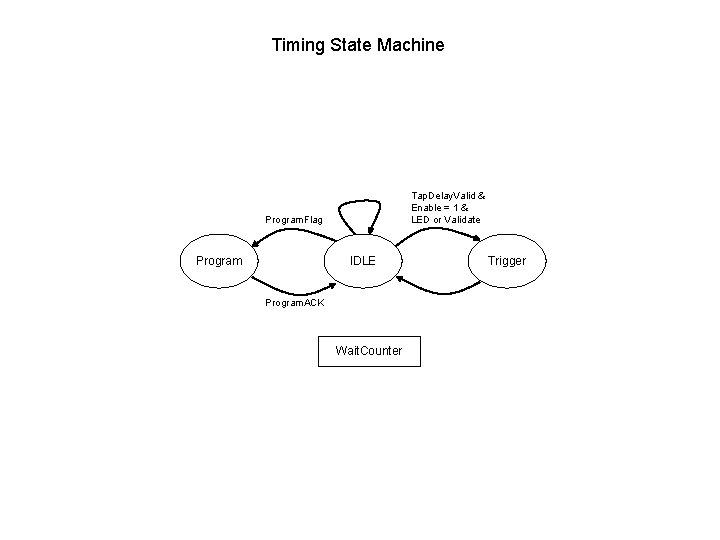

Timing State Machine Tap. Delay. Valid & Enable = 1 & LED or Validate Program. Flag Program IDLE Program. ACK Wait. Counter Trigger

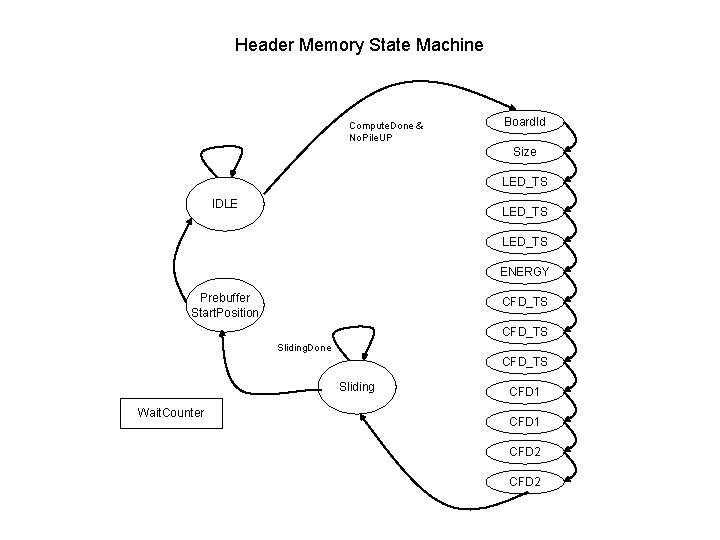

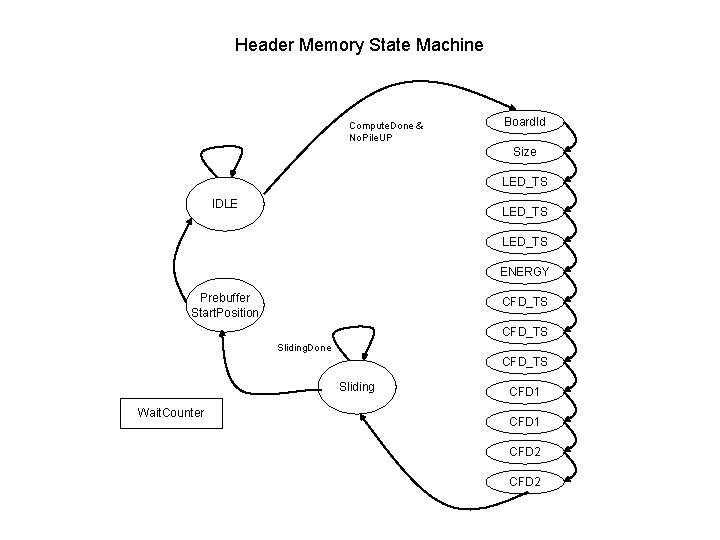

Header Memory State Machine Compute. Done & No. Pile. UP Board. Id Size LED_TS IDLE LED_TS ENERGY Prebuffer Start. Position CFD_TS Sliding. Done CFD_TS Sliding Wait. Counter CFD 1 CFD 2

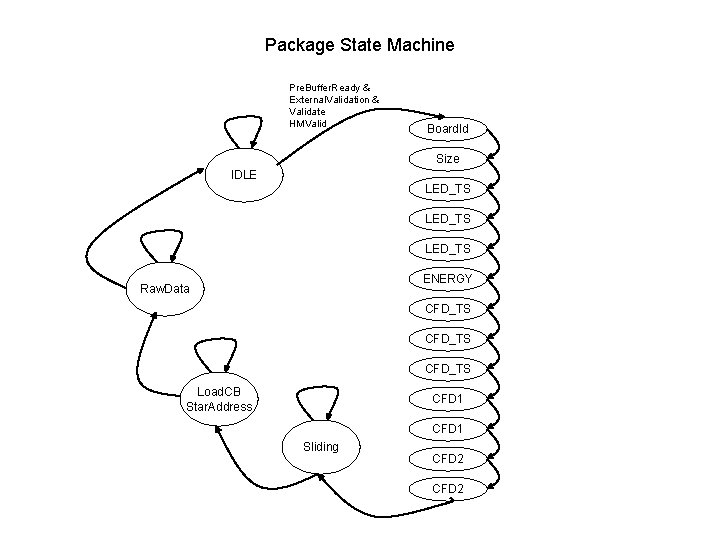

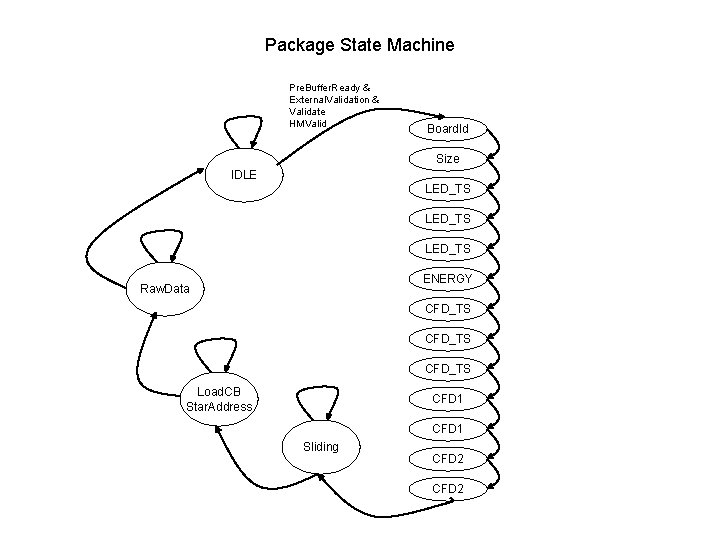

Package State Machine Pre. Buffer. Ready & External. Validation & Validate HMValid Board. Id Size IDLE LED_TS ENERGY Raw. Data CFD_TS Load. CB Star. Address CFD 1 Sliding CFD 2

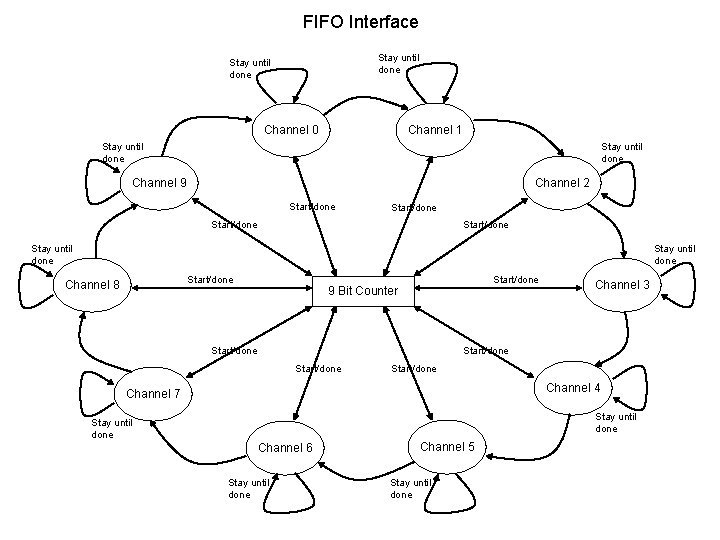

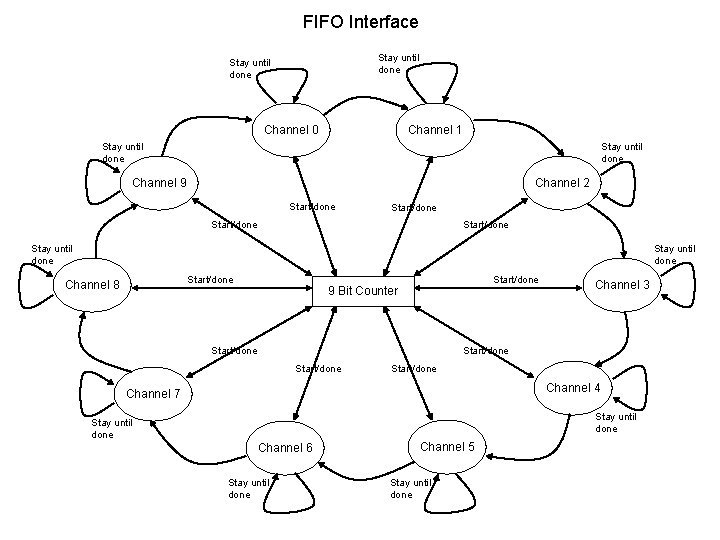

FIFO Interface Stay until done Channel 0 Channel 1 Stay until done Channel 9 Channel 2 Start/done Stay until done Start/done Channel 8 Start/done 9 Bit Counter Start/done Channel 3 Start/done Channel 4 Channel 7 Stay until done Channel 6 Stay until done Channel 5 Stay until done

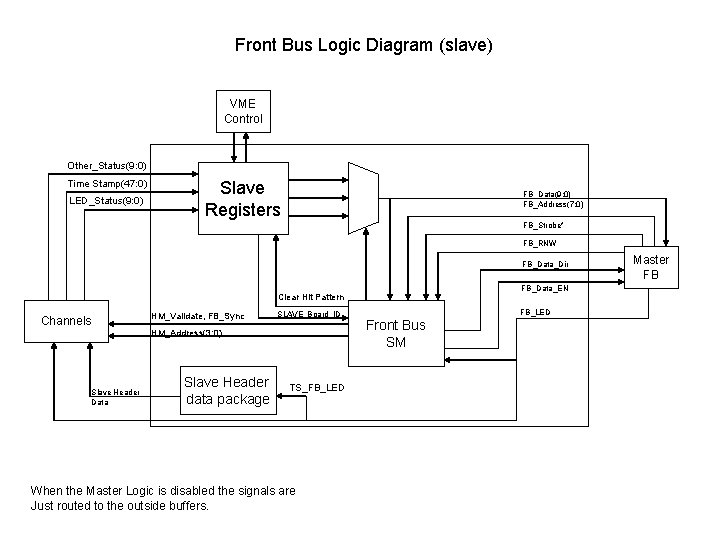

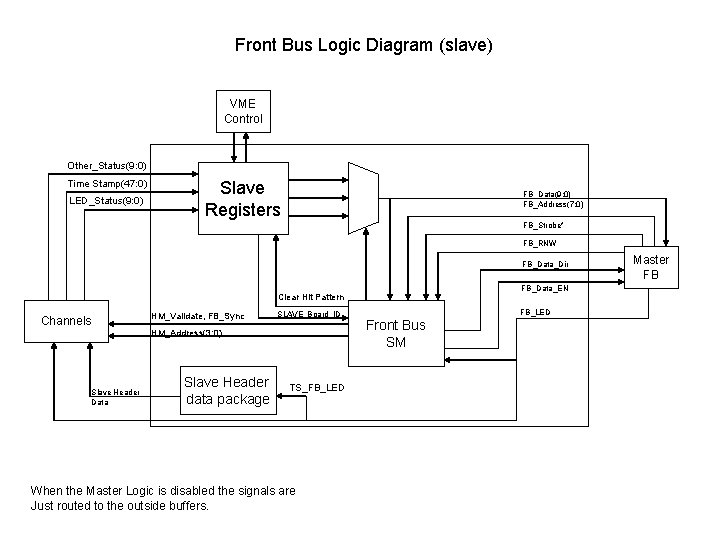

Front Bus Logic Diagram (slave) VME Control Other_Status(9: 0) Time Stamp(47: 0) LED_Status(9: 0) Slave Registers FB_Data(9: 0) FB_Address(7: 0) FB_Strobe* FB_RNW FB_Data_Dir FB_Data_EN Clear Hit Pattern Channels HM_Validate, FB_Sync SLAVE_Board_ID HM_Address(3: 0) Slave Header Data Slave Header data package TS_FB_LED When the Master Logic is disabled the signals are Just routed to the outside buffers. FB_LED Front Bus SM Master FB

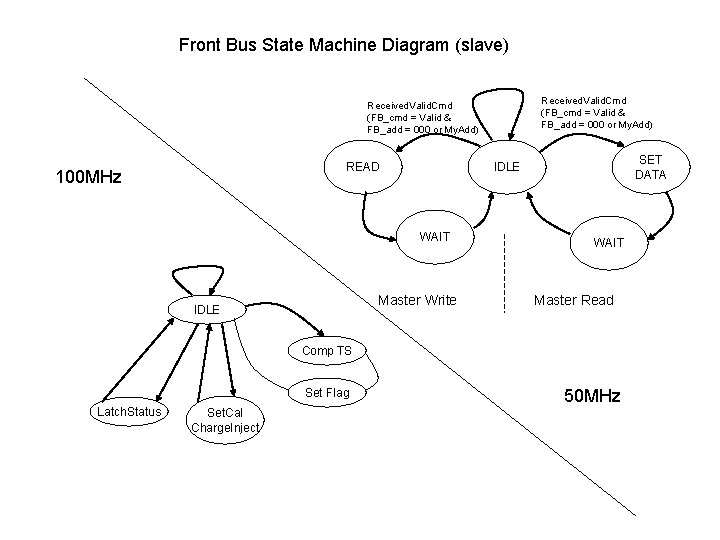

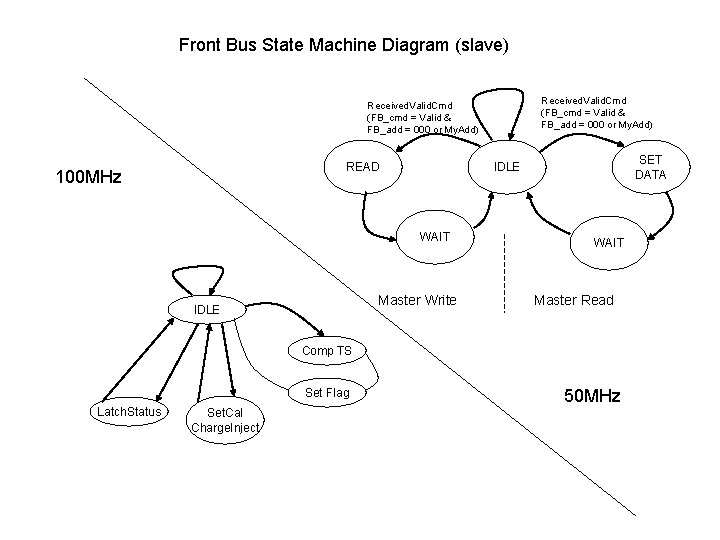

Front Bus State Machine Diagram (slave) Received. Valid. Cmd (FB_cmd = Valid & FB_add = 000 or My. Add) READ 100 MHz WAIT Master Write IDLE SET DATA IDLE WAIT Master Read Comp TS Set Flag Latch. Status Set. Cal Charge. Inject 50 MHz

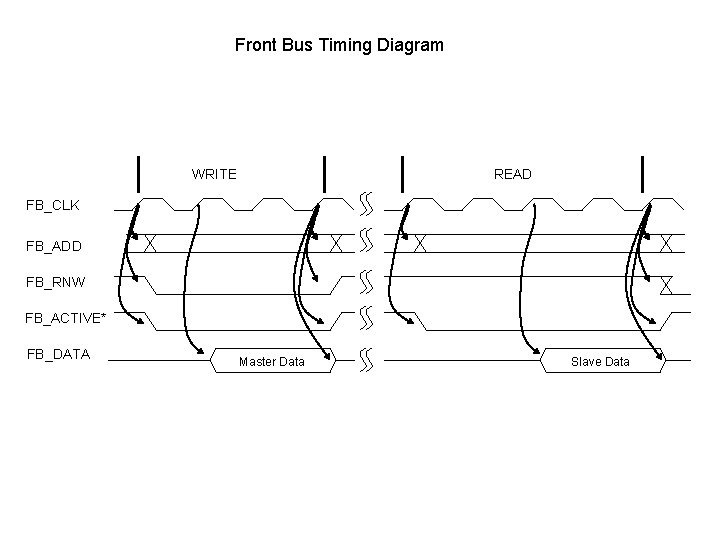

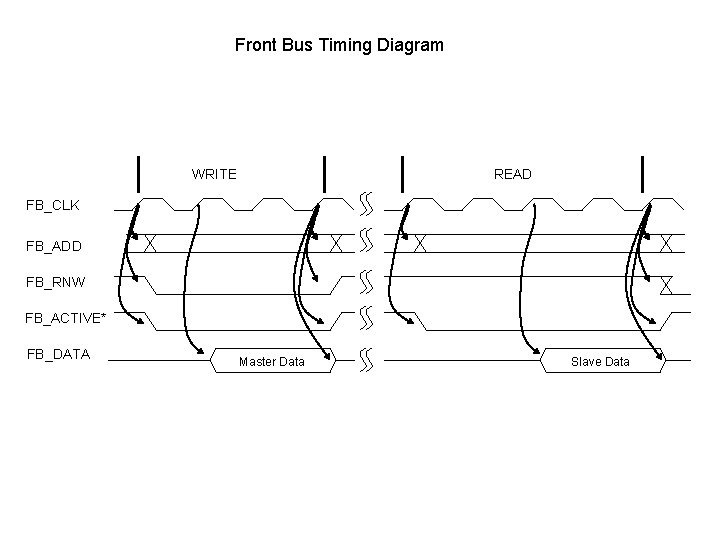

Front Bus Timing Diagram WRITE READ FB_CLK FB_ADD FB_RNW FB_ACTIVE* FB_DATA Master Data Slave Data

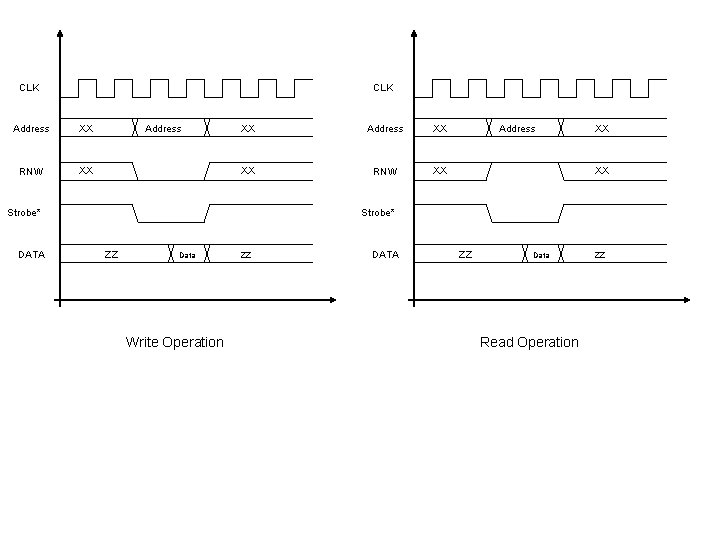

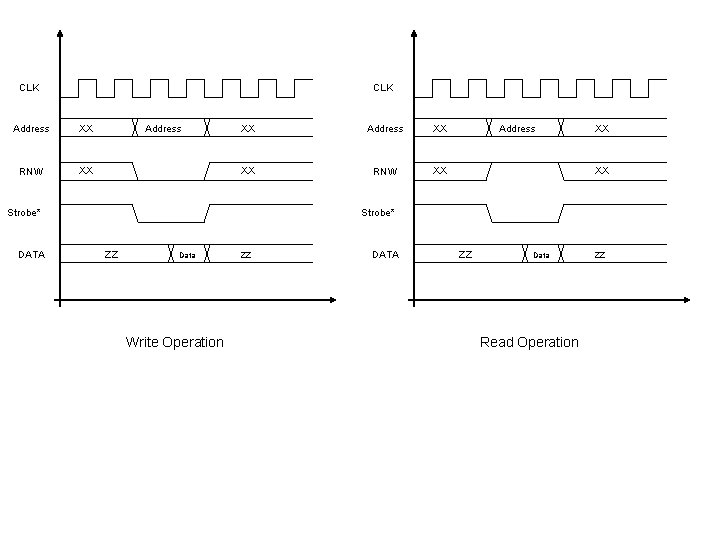

CLK Address XX RNW XX Address XX XX RNW XX Strobe* DATA Address XX XX Strobe* ZZ Data Write Operation ZZ DATA ZZ Data Read Operation ZZ

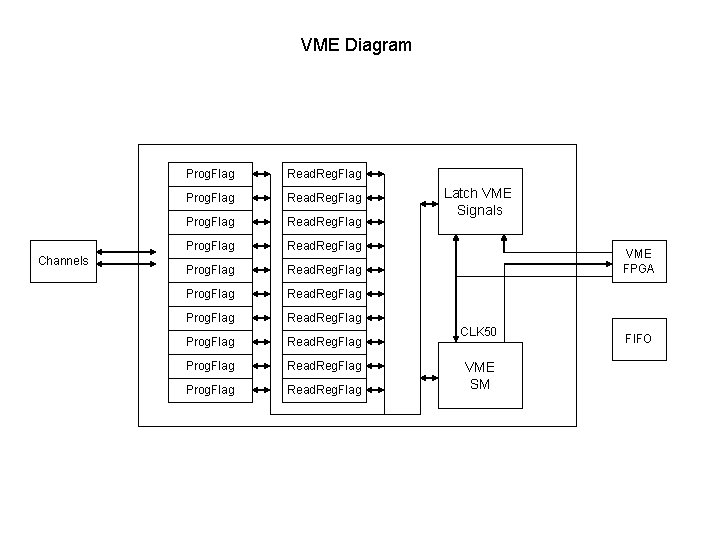

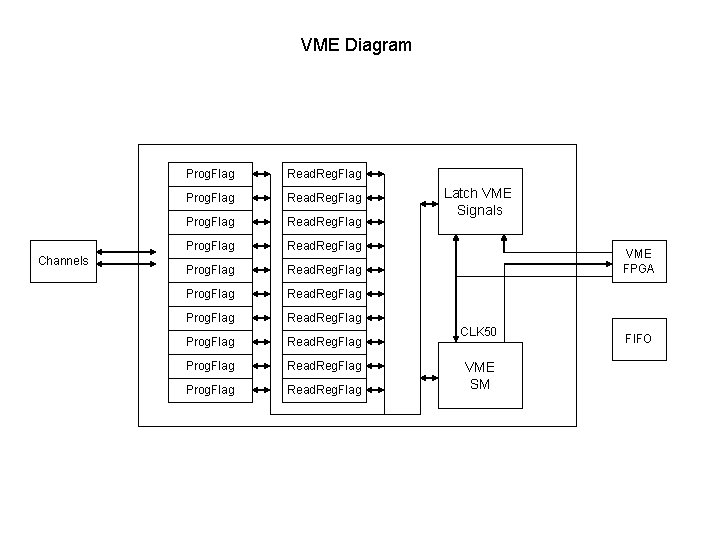

VME Diagram Channels Prog. Flag Read. Reg. Flag Prog. Flag Read. Reg. Flag Latch VME Signals VME FPGA CLK 50 VME SM FIFO

VME State Machine

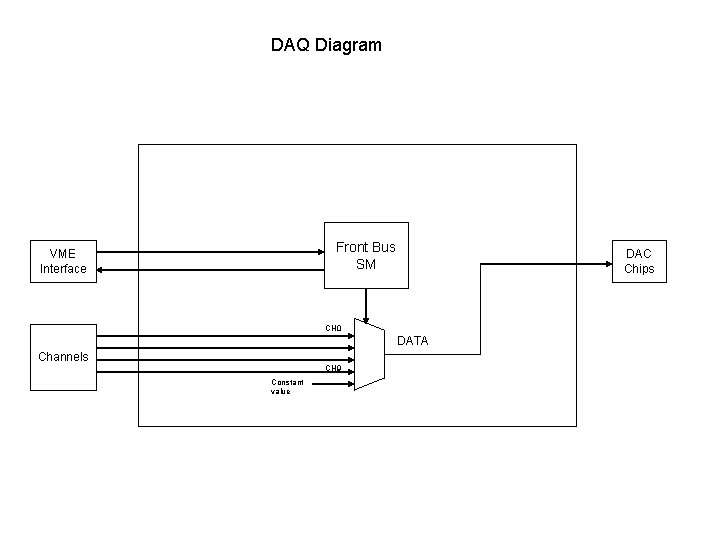

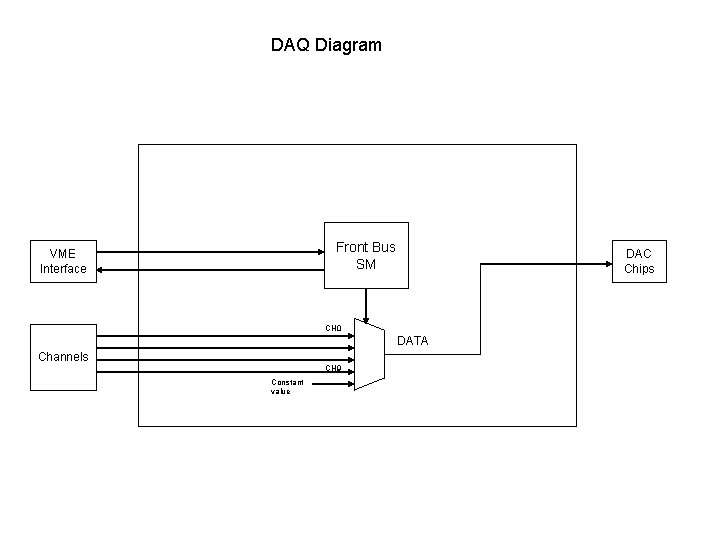

DAQ Diagram Front Bus SM VME Interface DAC Chips CH 0 DATA Channels CH 9 Constant value

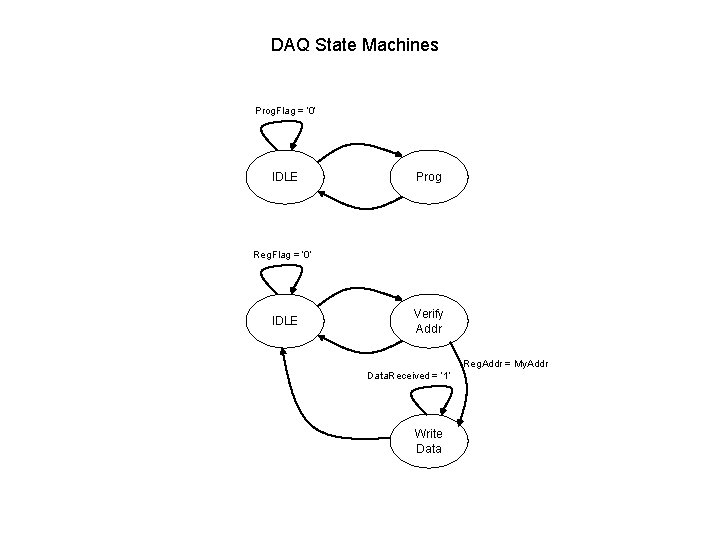

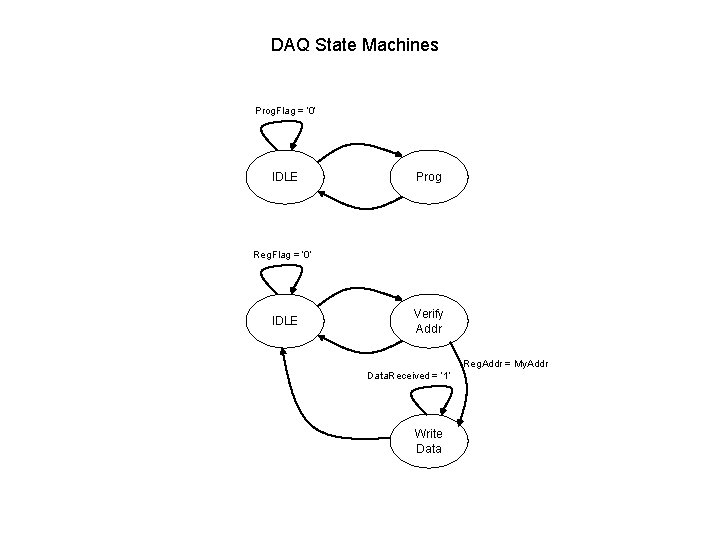

DAQ State Machines Prog. Flag = ‘ 0’ IDLE Prog Reg. Flag = ‘ 0’ IDLE Verify Addr Reg. Addr = My. Addr Data. Received = ‘ 1’ Write Data

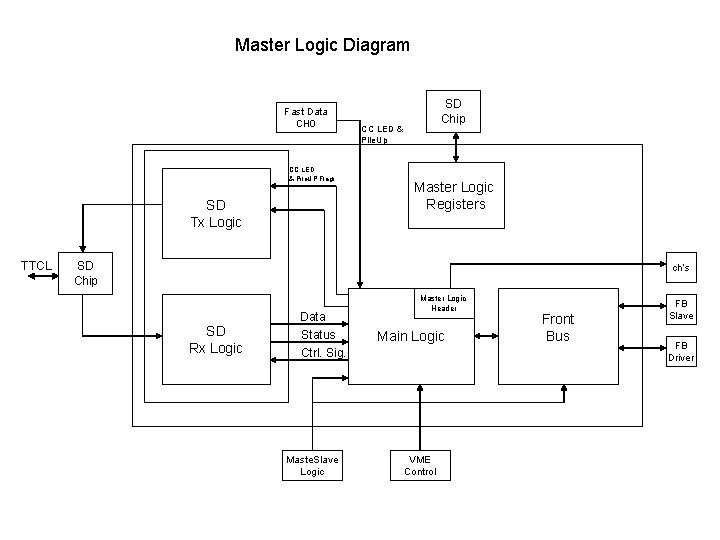

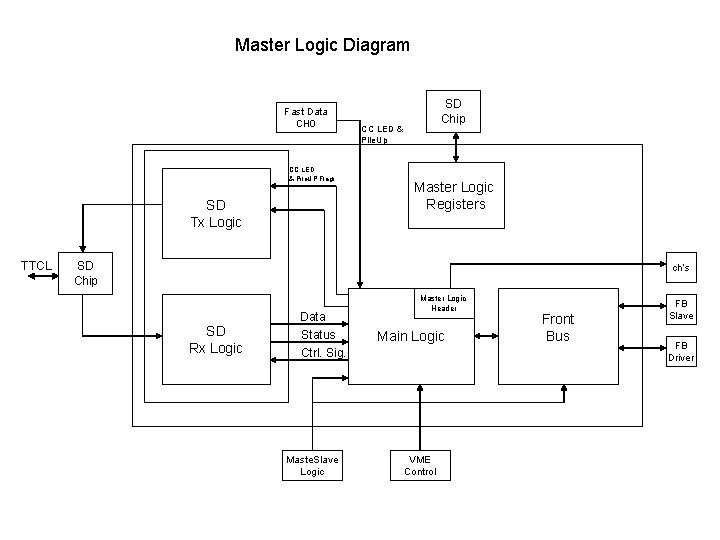

Master Logic Diagram Fast Data CH 0 CC LED & Pile. UP Flags SD Tx Logic TTCL SD Chip CC LED & Pile. Up Master Logic Registers SD Chip ch’s SD Rx Logic Data Status Ctrl. Sig. Maste. Slave Logic Master Logic Header Main Logic VME Control Front Bus FB Slave FB Driver

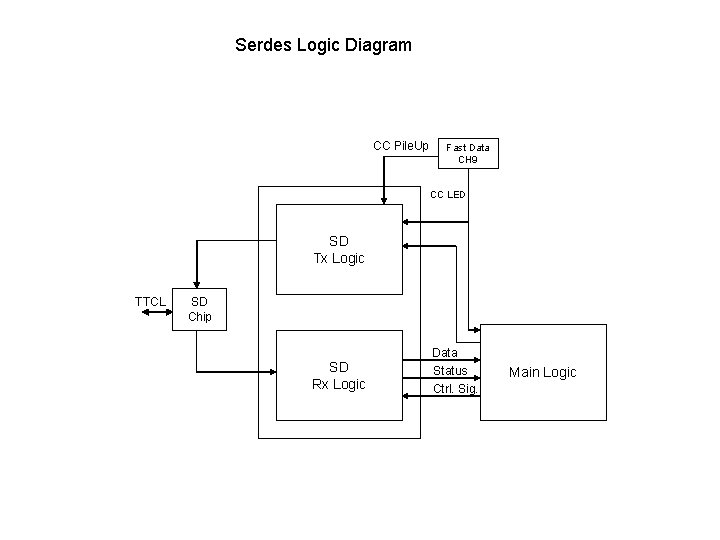

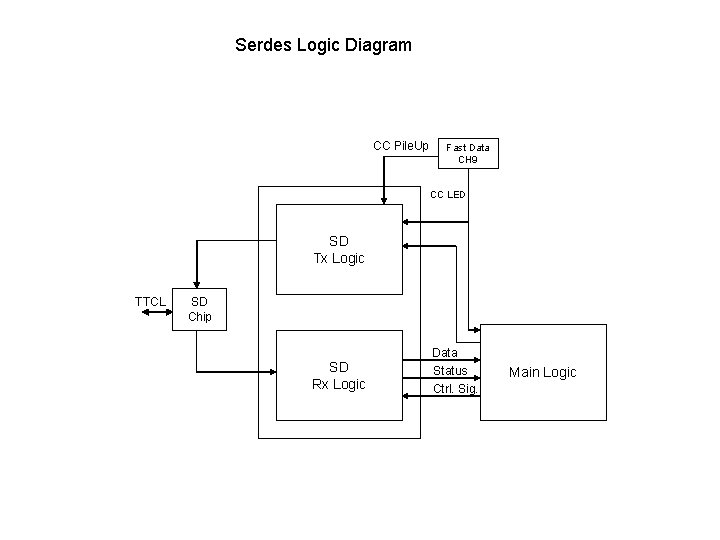

Serdes Logic Diagram CC Pile. Up Fast Data CH 9 CC LED SD Tx Logic TTCL SD Chip SD Rx Logic Data Status Ctrl. Sig. Main Logic

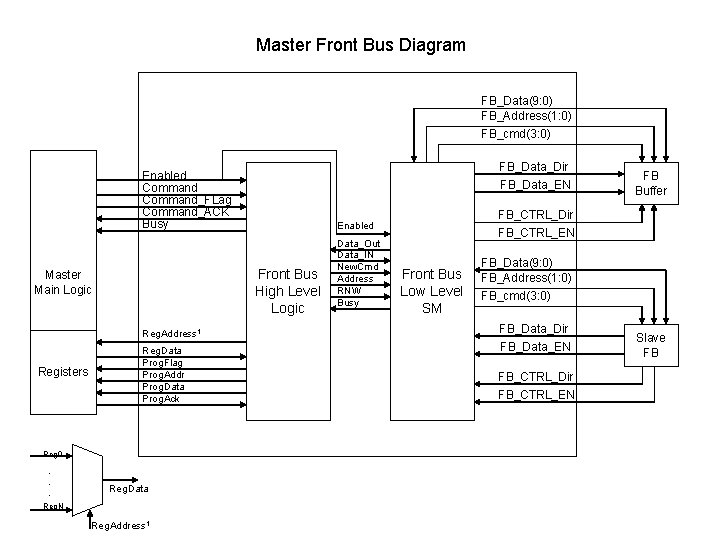

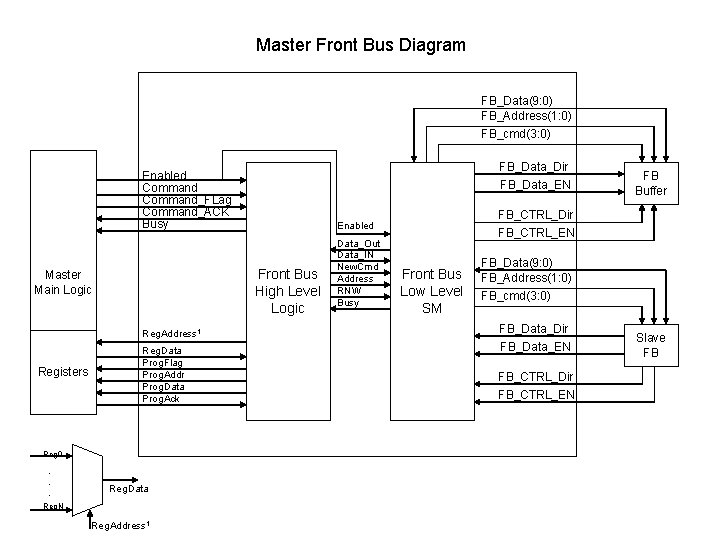

Master Front Bus Diagram FB_Data(9: 0) FB_Address(1: 0) FB_cmd(3: 0) FB_Data_Dir FB_Data_EN Enabled Command_FLag Command_ACK Busy Front Bus High Level Logic Master Main Logic Reg. Address 1 Registers Reg. Data Prog. Flag Prog. Addr Prog. Data Prog. Ack Reg 0 . . . Reg. Data Reg. N Reg. Address 1 FB_CTRL_Dir FB_CTRL_EN Enabled Data_Out Data_IN New. Cmd Address RNW Busy FB Buffer Front Bus Low Level SM FB_Data(9: 0) FB_Address(1: 0) FB_cmd(3: 0) FB_Data_Dir FB_Data_EN FB_CTRL_Dir FB_CTRL_EN Slave FB

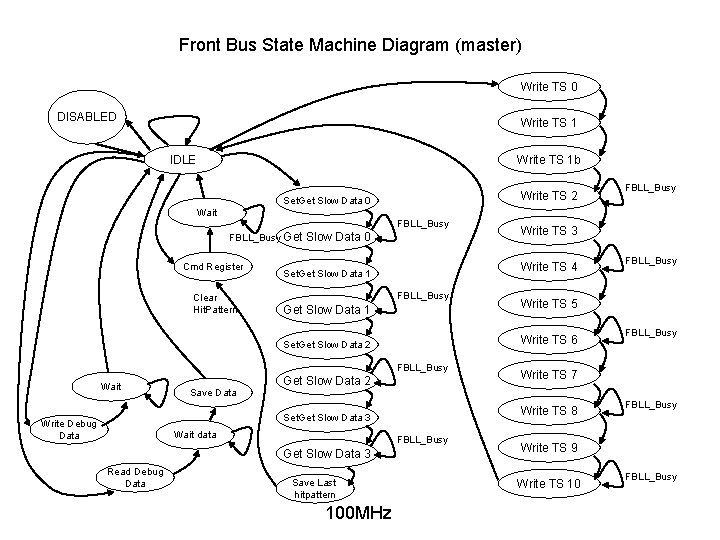

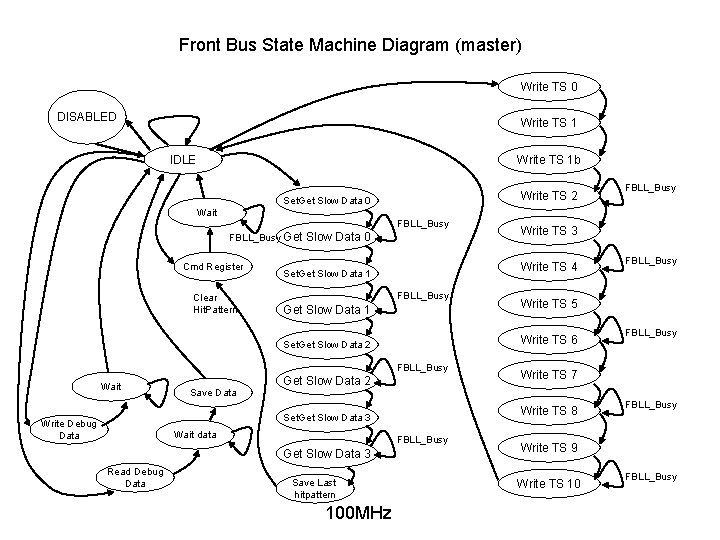

Front Bus State Machine Diagram (master) Write TS 0 DISABLED Write TS 1 IDLE Write TS 1 b Write TS 2 Set. Get Slow Data 0 Wait FBLL_Busy Get Cmd Register Clear Hit. Pattern Slow Data 0 FBLL_Busy Get Slow Data 1 FBLL_Busy Save Data Get Slow Data 2 Write Debug Data Wait data FBLL_Busy Get Slow Data 3 Read Debug Data Save Last hitpattern 100 MHz FBLL_Busy Write TS 7 Write TS 8 Set. Get Slow Data 3 FBLL_Busy Write TS 5 Write TS 6 Set. Get Slow Data 2 Wait Write TS 3 Write TS 4 Set. Get Slow Data 1 FBLL_Busy Write TS 9 Write TS 10 FBLL_Busy

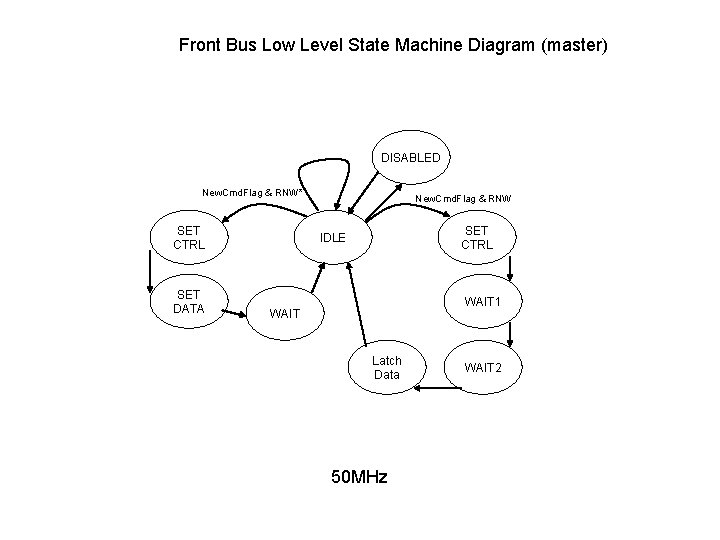

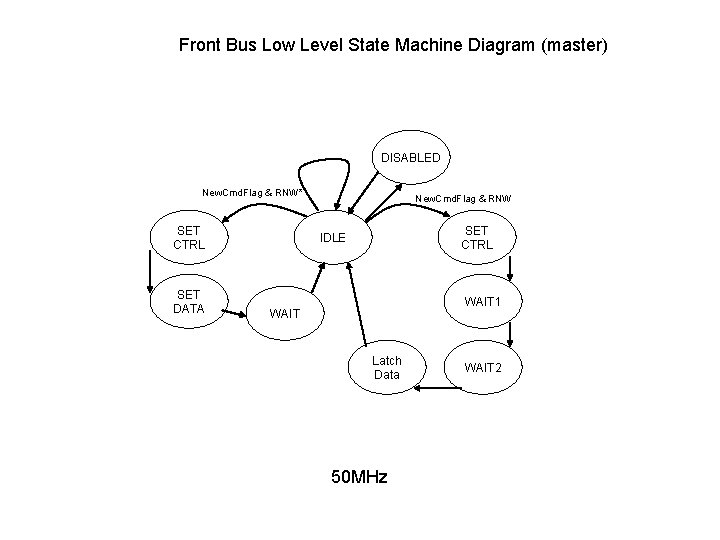

Front Bus Low Level State Machine Diagram (master) DISABLED New. Cmd. Flag & RNW* SET CTRL SET DATA New. Cmd. Flag & RNW SET CTRL IDLE WAIT 1 WAIT Latch Data 50 MHz WAIT 2

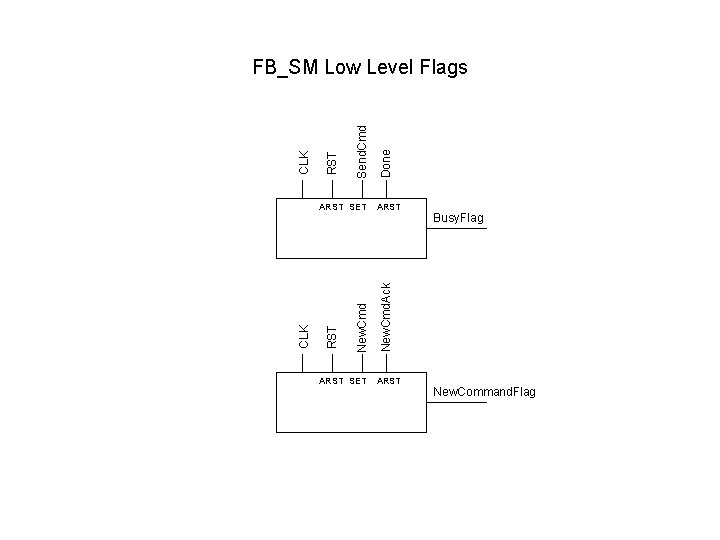

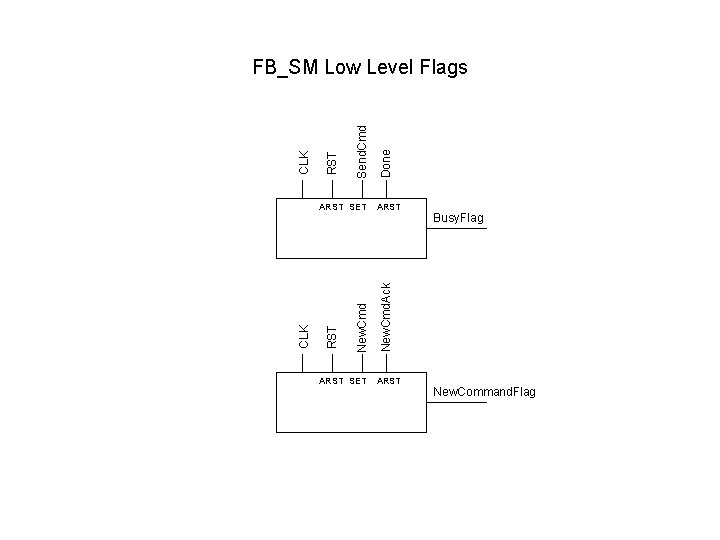

New. Cmd RST CLK ARST SET Done ARST Busy. Flag New. Cmd. Ack Send. Cmd RST CLK FB_SM Low Level Flags ARST New. Command. Flag

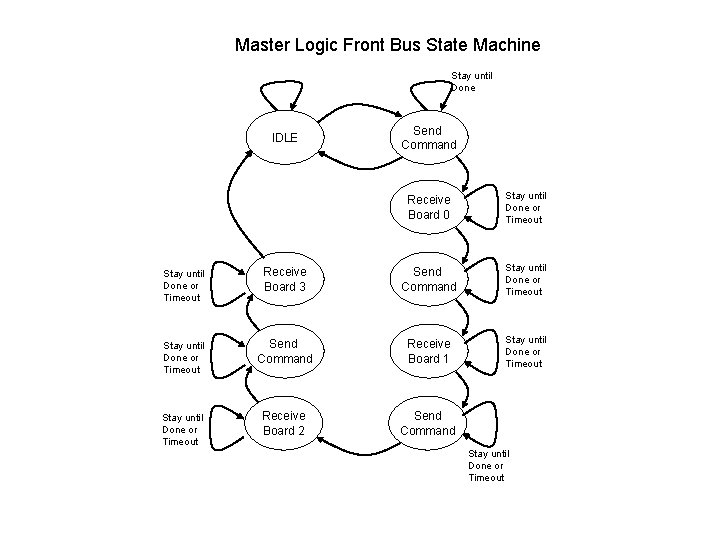

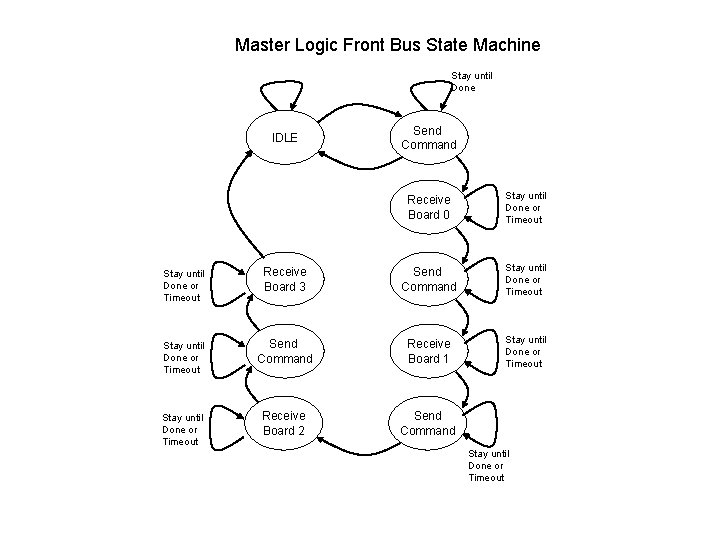

Master Logic Front Bus State Machine Stay until Done IDLE Send Command Receive Board 0 Stay until Done or Timeout Receive Board 3 Send Command Stay until Done or Timeout Send Command Receive Board 1 Stay until Done or Timeout Receive Board 2 Send Command Stay until Done or Timeout

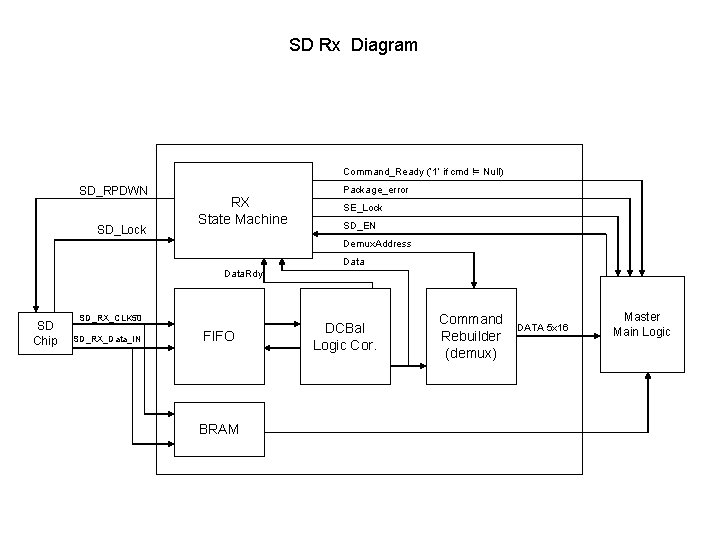

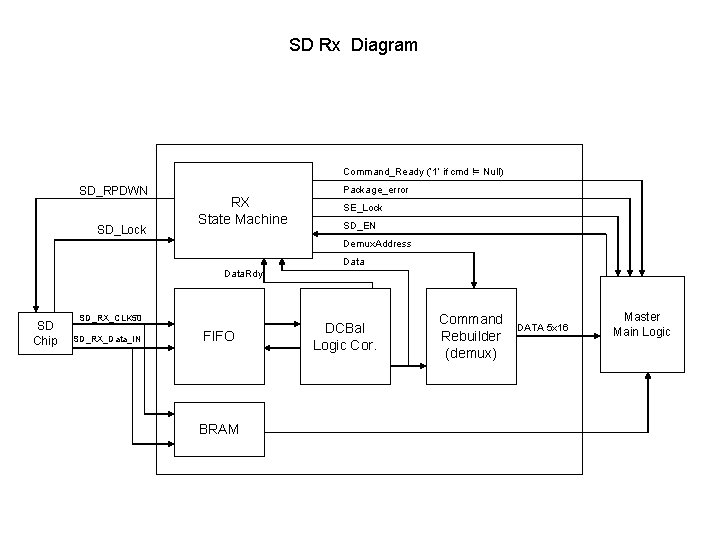

SD Rx Diagram Command_Ready (‘ 1’ if cmd != Null) SD_RPDWN SD_Lock RX State Machine Package_error SE_Lock SD_EN Demux. Address Data. Rdy SD Chip SD_RX_CLK 50 SD_RX_Data_IN FIFO BRAM DCBal Logic Cor. Command Rebuilder (demux) DATA 5 x 16 Master Main Logic

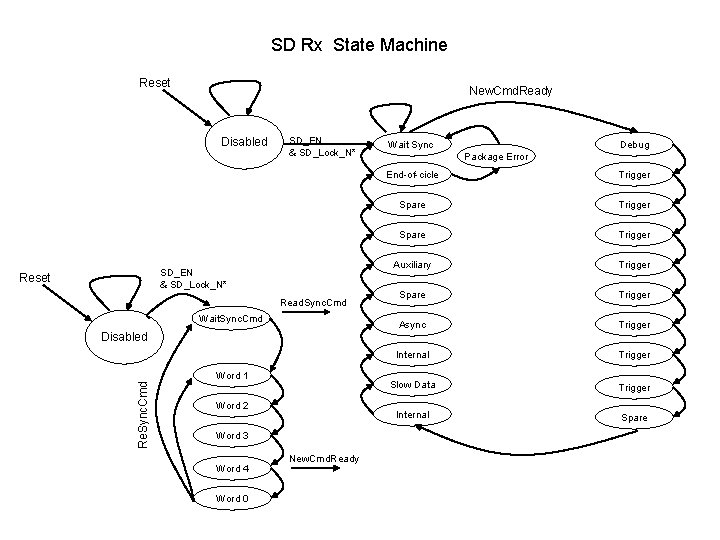

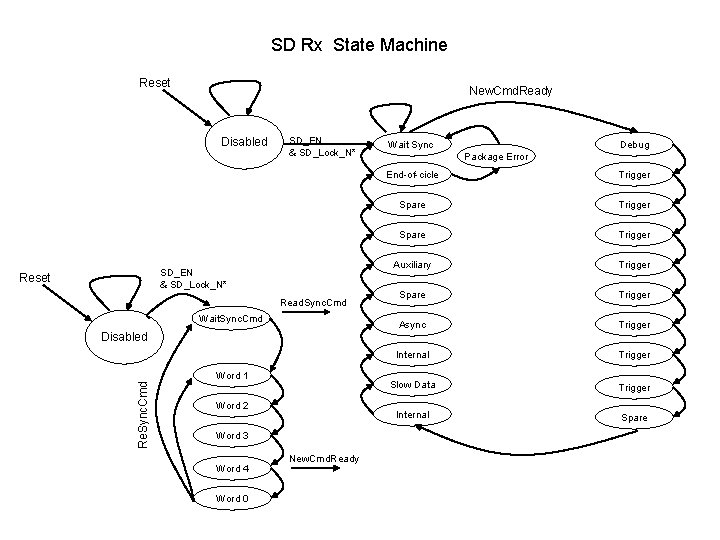

SD Rx State Machine Reset New. Cmd. Ready Disabled SD_EN & SD_Lock_N* Reset Read. Sync. Cmd Wait Sync Debug Package Error End-of-cicle Trigger Spare Trigger Auxiliary Trigger Spare Trigger Async Trigger Internal Trigger Slow Data Trigger Internal Spare Disabled Re. Sync. Cmd Word 1 Word 2 Word 3 Word 4 Word 0 New. Cmd. Ready

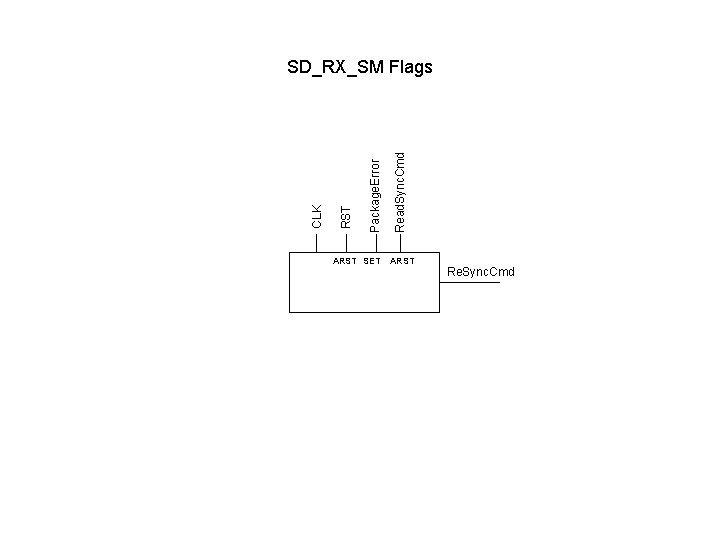

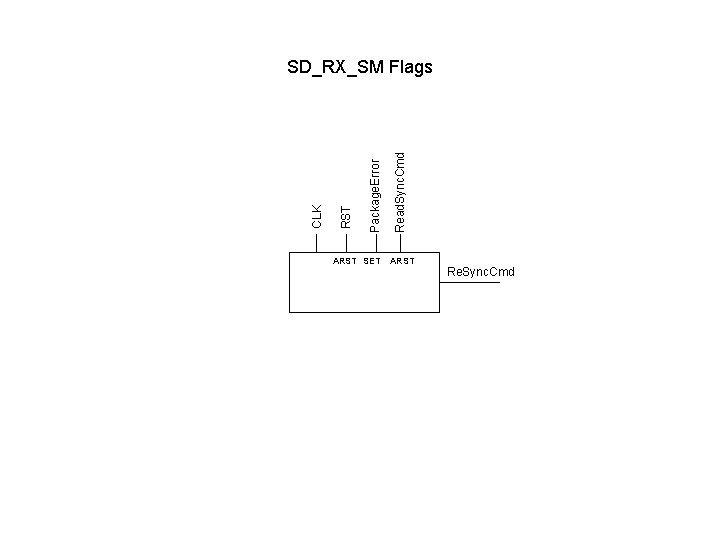

ARST SET Read. Sync. Cmd Package. Error RST CLK SD_RX_SM Flags ARST Re. Sync. Cmd

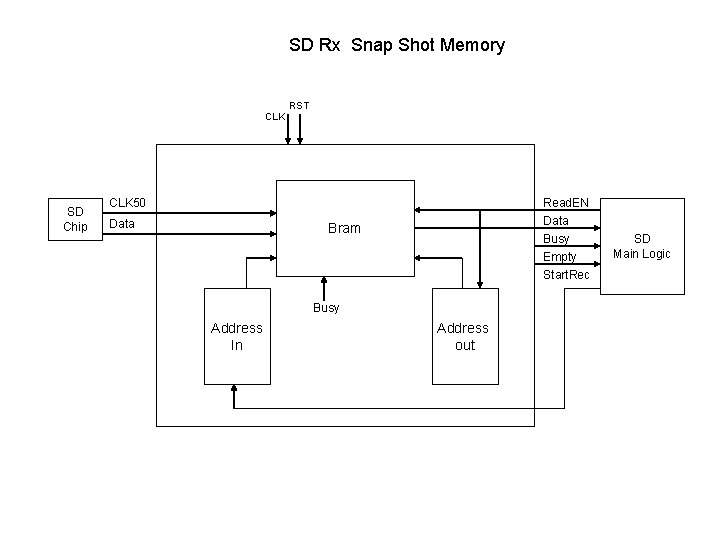

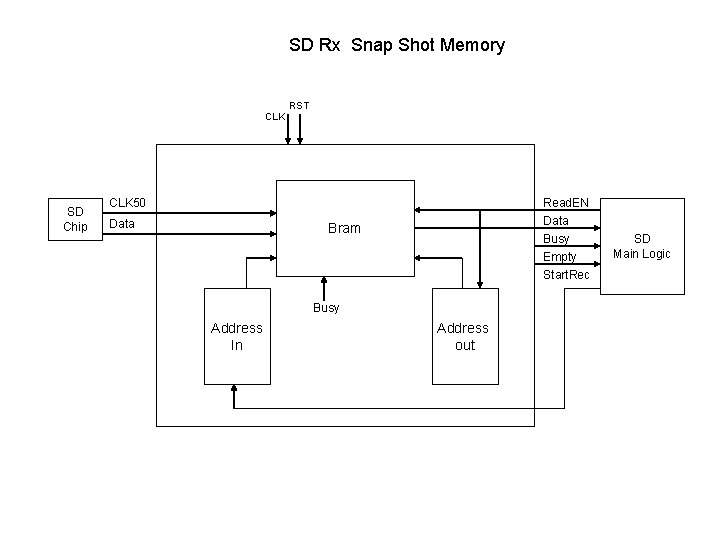

SD Rx Snap Shot Memory CLK SD Chip RST CLK 50 Data Read. EN Data Busy Empty Bram Start. Rec Busy Address In Address out SD Main Logic

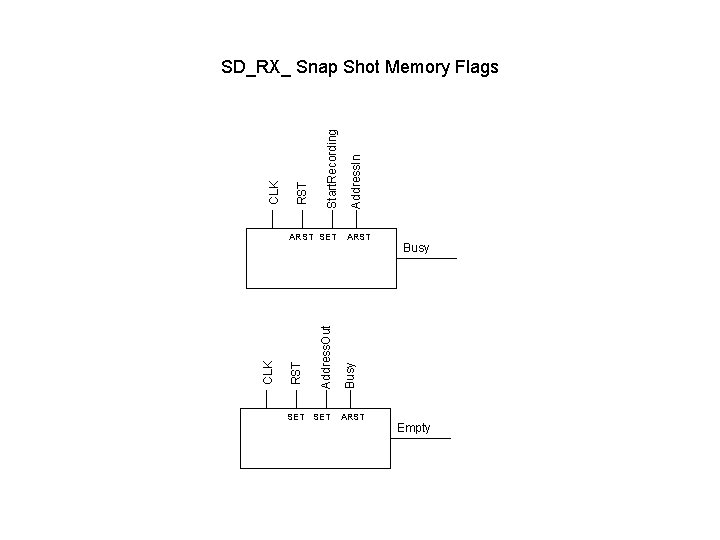

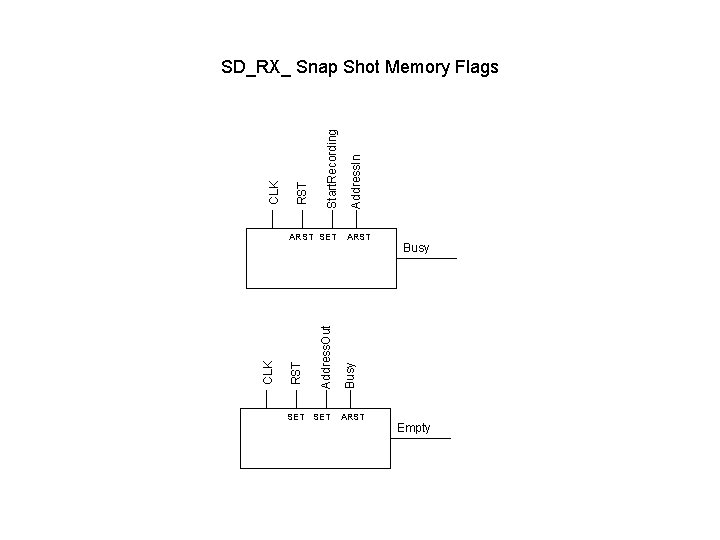

Address. Out RST CLK ARST SET SET Address. In ARST Busy Start. Recording RST CLK SD_RX_ Snap Shot Memory Flags ARST Empty

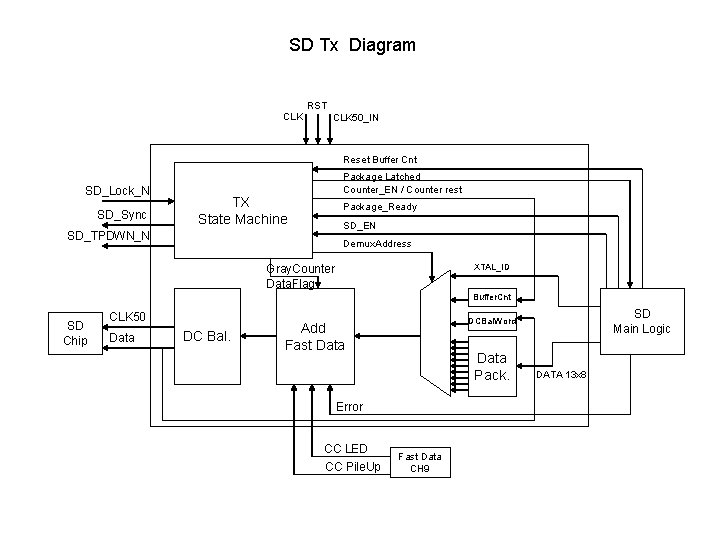

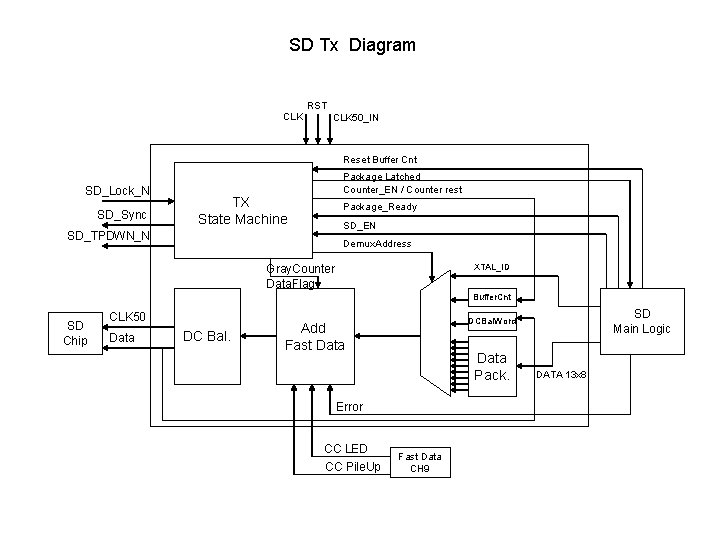

SD Tx Diagram CLK RST CLK 50_IN Reset Buffer Cnt SD_Lock_N SD_Sync Package Latched Counter_EN / Counter rest TX State Machine Package_Ready SD_EN SD_TPDWN_N Demux. Address XTAL_ID Gray. Counter Data. Flag Buffer. Cnt SD Chip CLK 50 Data DC Bal. Add Fast Data Pack. Error CC LED CC Pile. Up SD Main Logic DCBal. Word Fast Data CH 9 DATA 13 x 8

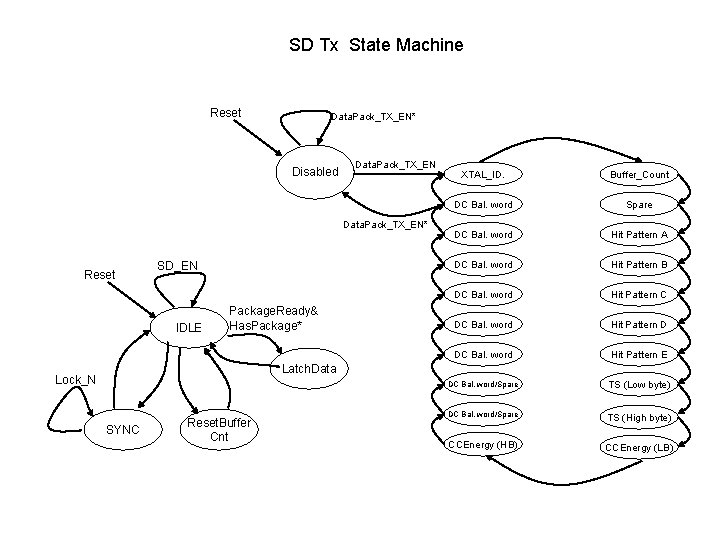

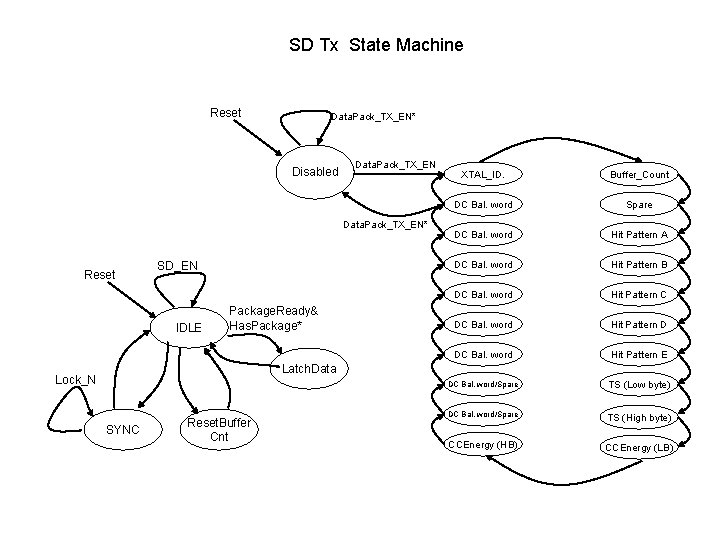

SD Tx State Machine Reset Data. Pack_TX_EN* Disabled Data. Pack_TX_EN* Reset SD_EN IDLE Package. Ready& Has. Package* XTAL_ID. Buffer_Count DC Bal. word Spare DC Bal. word Hit Pattern A DC Bal. word Hit Pattern B DC Bal. word Hit Pattern C DC Bal. word Hit Pattern D DC Bal. word Hit Pattern E DC Bal. word/Spare TS (Low byte) DC Bal. word/Spare TS (High byte) CCEnergy (HB) CCEnergy (LB) Latch. Data Lock_N SYNC Reset. Buffer Cnt

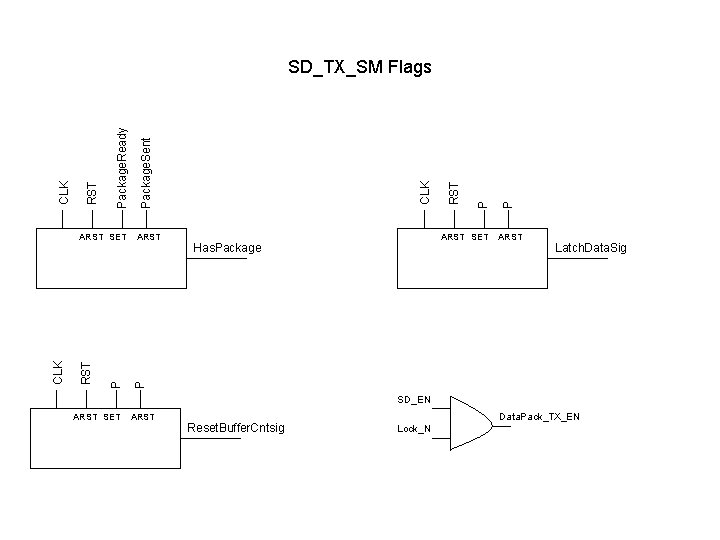

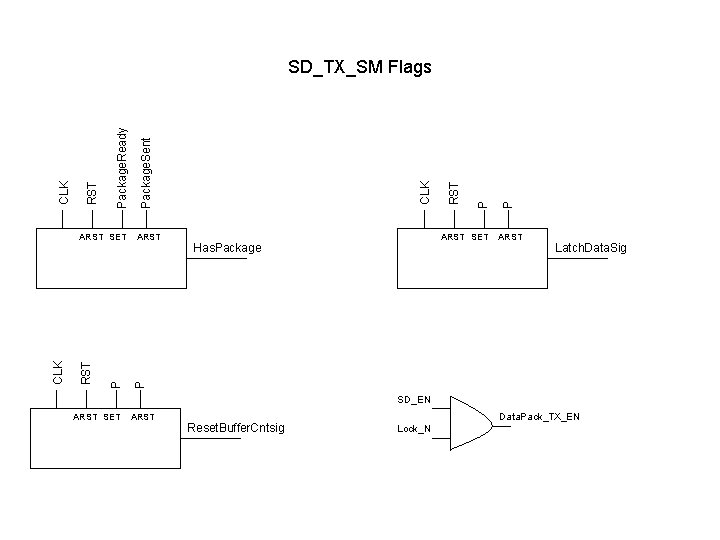

P RST CLK ARST SET Has. Package P P RST CLK Package. Sent ARST Latch. Data. Sig P Package. Ready RST CLK SD_TX_SM Flags SD_EN ARST SET ARST Reset. Buffer. Cntsig Data. Pack_TX_EN Lock_N

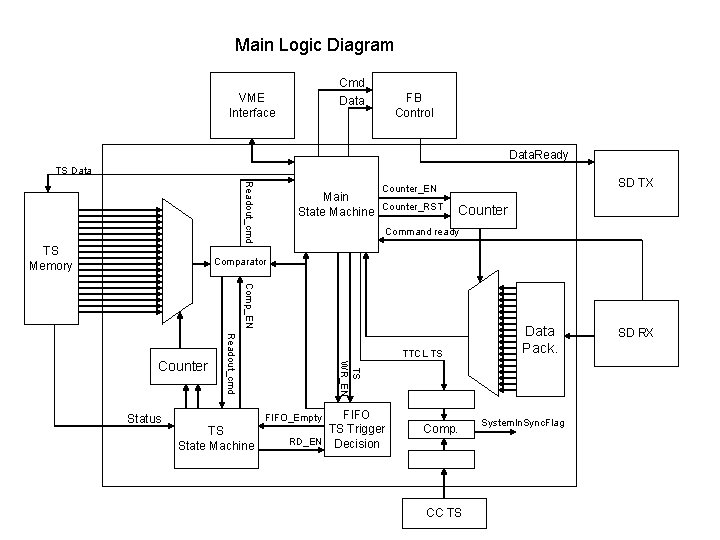

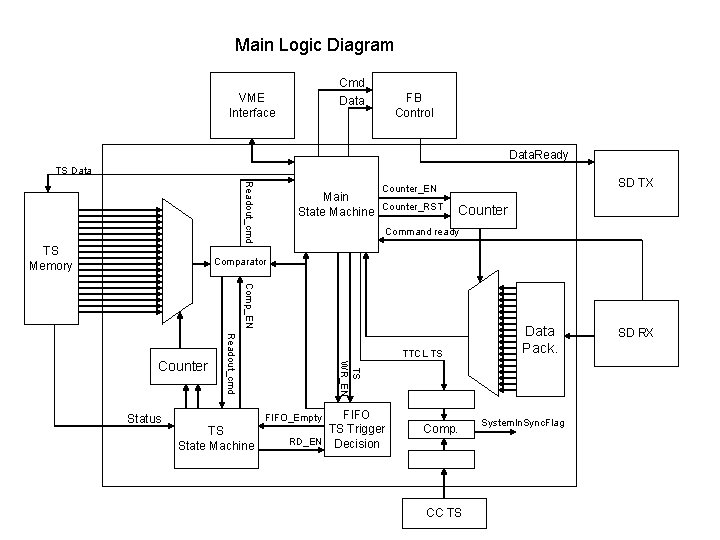

Main Logic Diagram Cmd Data VME Interface FB Control Data. Ready TS Data Readout_cmd TS Memory SD TX Counter_EN Main State Machine Counter_RST Counter Command ready Comparator Comp_EN TTCL TS TS WR_EN Status Readout_cmd Counter FIFO TS Trigger RD_EN Decision FIFO_Empty TS State Machine Data Pack. Comp. CC TS System. In. Sync. Flag SD RX

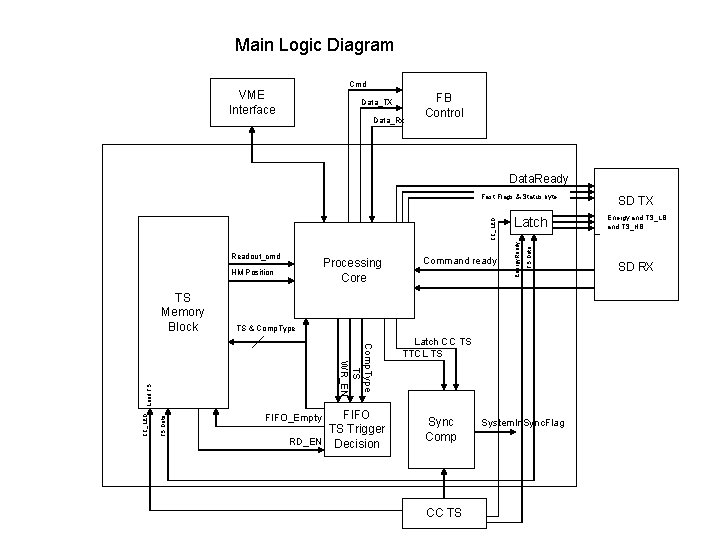

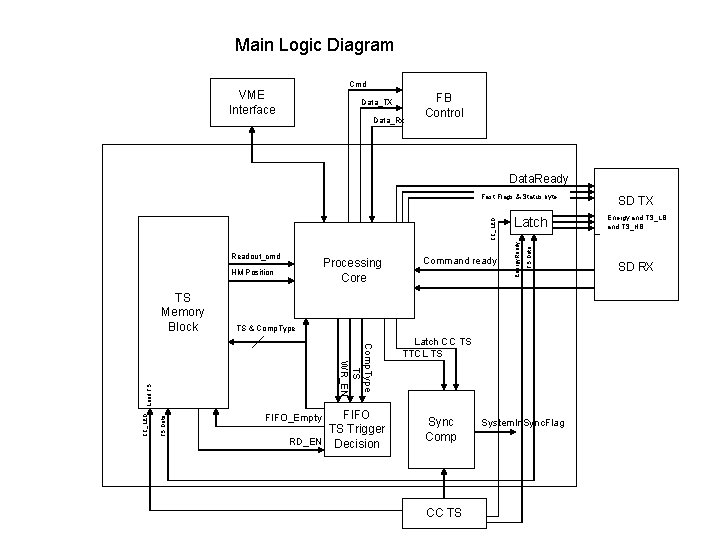

Main Logic Diagram Cmd VME Interface Data_TX Data_Rx FB Control Data. Ready Processing Core HM Position TS Memory Block TS & Comp. Type TS Data Load TS Comp. Type TS WR_EN CC_LED Command ready TS Data Readout_cmd Latch Energy. Ready CC_LED Fast Flags & Status byte FIFO TS Trigger RD_EN Decision FIFO_Empty Latch CC TS TTCL TS Sync Comp CC TS System. In. Sync. Flag SD TX Energy and TS_LB and TS_HB SD RX

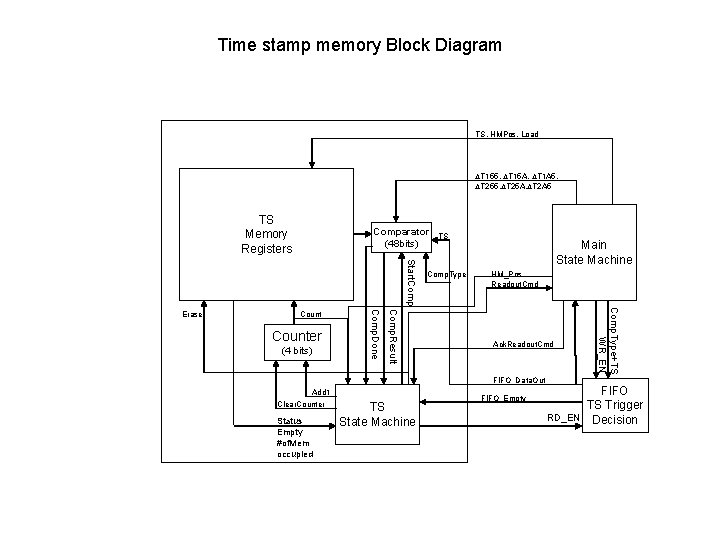

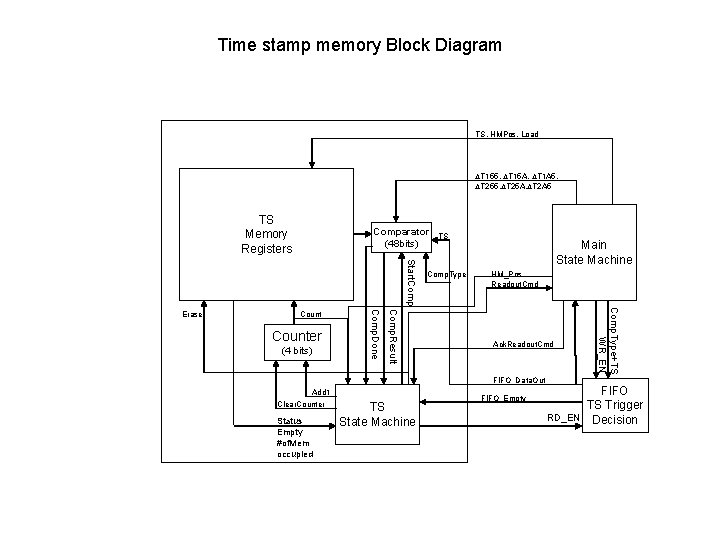

Time stamp memory Block Diagram TS, HMPos, Load T 155, T 15 A, T 1 A 5, T 255, T 25 A, T 2 A 5 TS Memory Registers Comparator (48 bits) Start. Comp (4 bits) Comp. Type Main State Machine HM_Pos Readout. Cmd Ack. Readout. Cmd FIFO_Data. Out Add 1 Clear. Counter Status Empty #of. Mem occupied TS State Machine FIFO_Empty Comp. Type+TS WR_EN Counter Comp. Result Count Comp. Done Erase TS FIFO TS Trigger RD_EN Decision

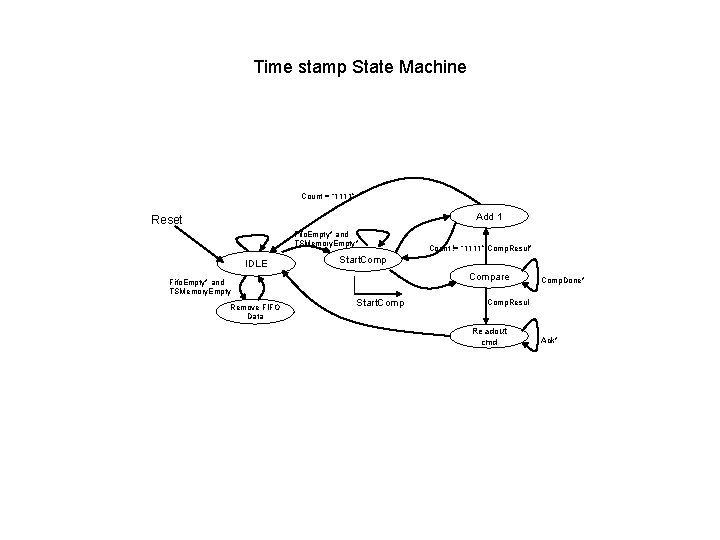

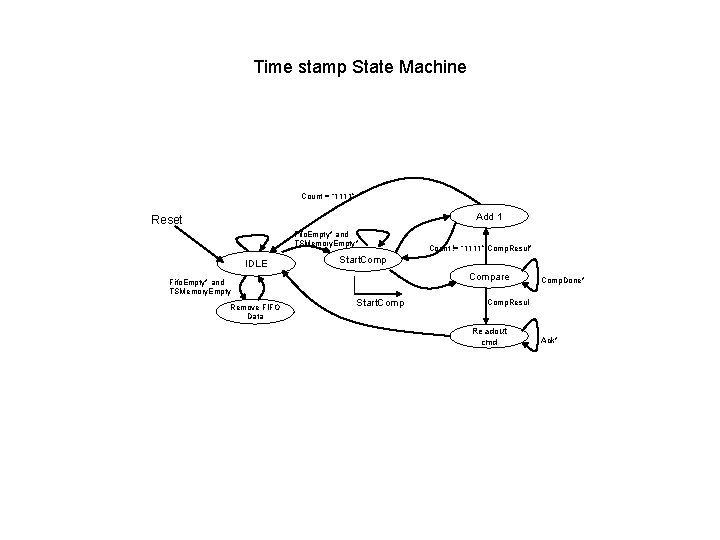

Time stamp State Machine Count = “ 1111” Add 1 Reset Fifo. Empty* and TSMemory. Empty* IDLE Compare Fifo. Empty* and TSMemory. Empty Remove FIFO Data Count != “ 1111” Comp. Resul* Start. Comp. Done* Comp. Resul Readout cmd Ack*

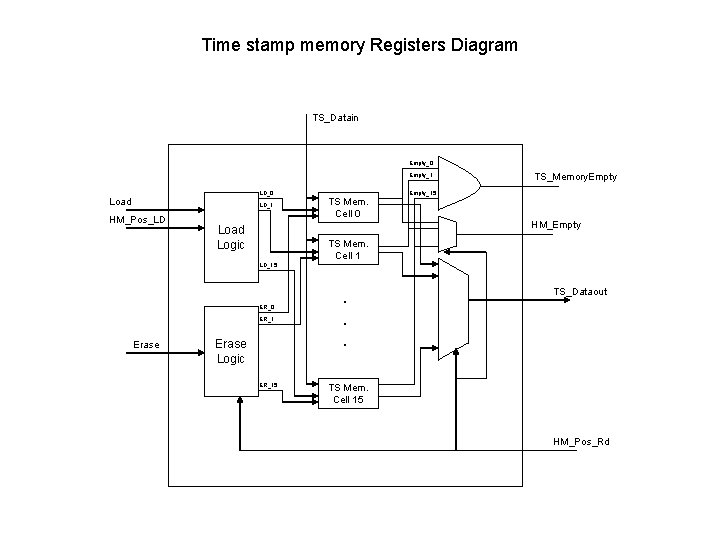

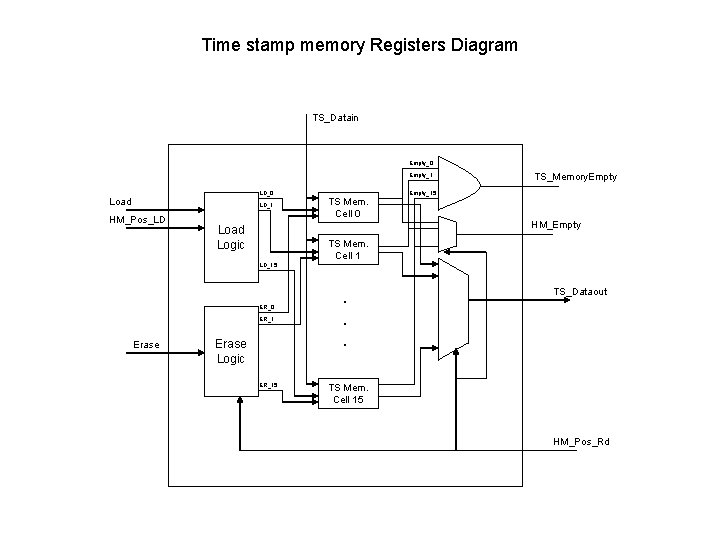

Time stamp memory Registers Diagram TS_Datain Empty_0 Empty_1 LD_0 Load LD_1 HM_Pos_LD TS Mem. Cell 0 TS_Memory. Empty_15 HM_Empty Load Logic TS Mem. Cell 1 LD_15 ER_0 ER_1 Erase Logic ER_15 . . . TS_Dataout TS Mem. Cell 15 HM_Pos_Rd

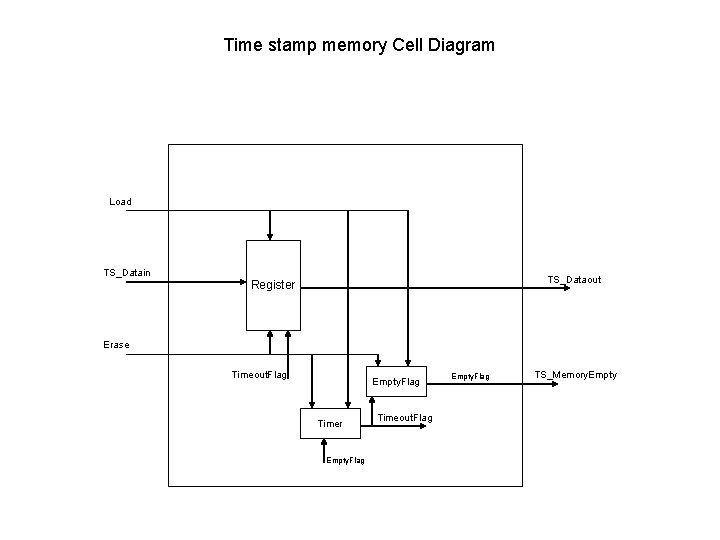

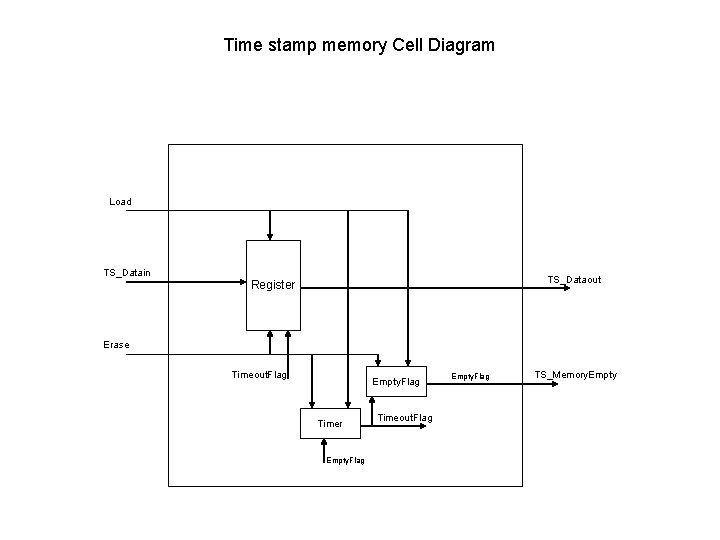

Time stamp memory Cell Diagram Load TS_Datain TS_Dataout Register Erase Timeout. Flag Empty. Flag Timer Empty. Flag Timeout. Flag Empty. Flag TS_Memory. Empty

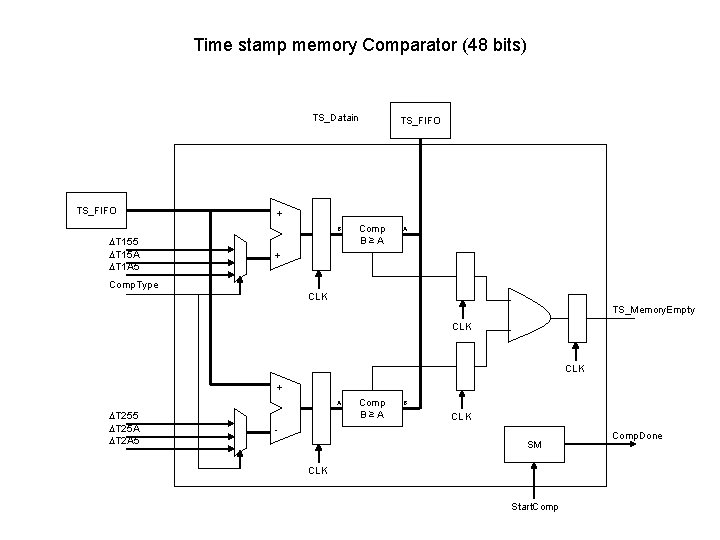

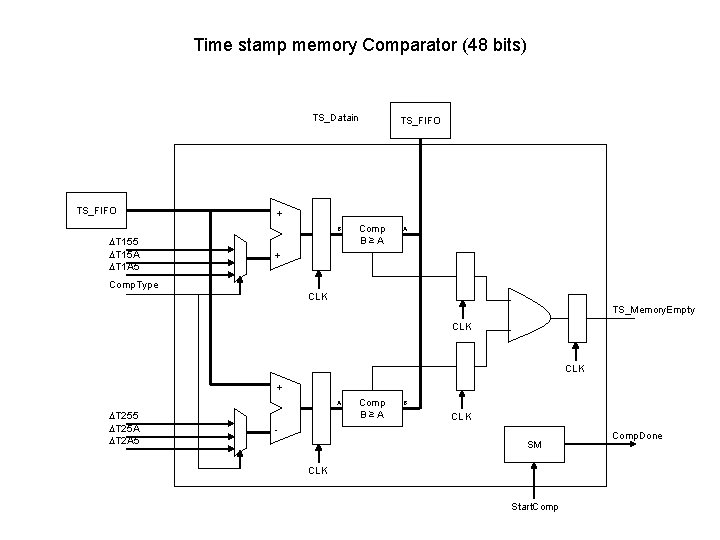

Time stamp memory Comparator (48 bits) TS_Datain TS_FIFO + B T 155 T 15 A T 1 A 5 TS_FIFO Comp B≥A A + Comp. Type CLK TS_Memory. Empty CLK + A T 255 T 25 A T 2 A 5 Comp B≥A B CLK SM CLK Start. Comp. Done

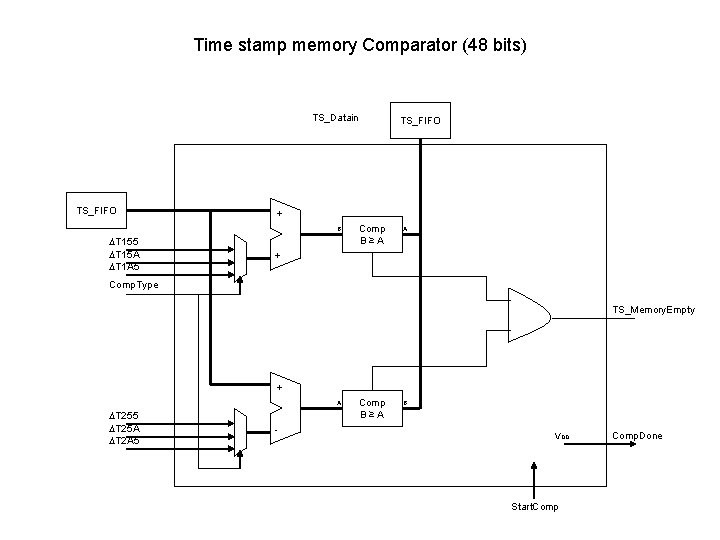

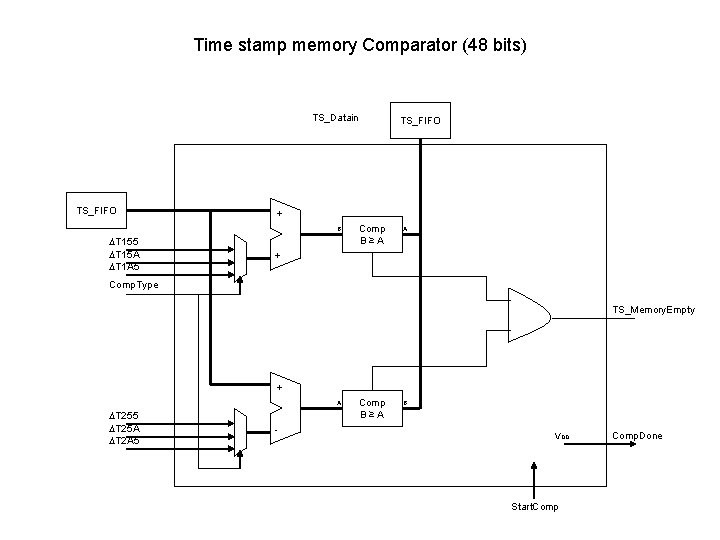

Time stamp memory Comparator (48 bits) TS_Datain TS_FIFO + B T 155 T 15 A T 1 A 5 TS_FIFO Comp B≥A A + Comp. Type TS_Memory. Empty + A T 255 T 25 A T 2 A 5 - Comp B≥A B Vcc Start. Comp. Done

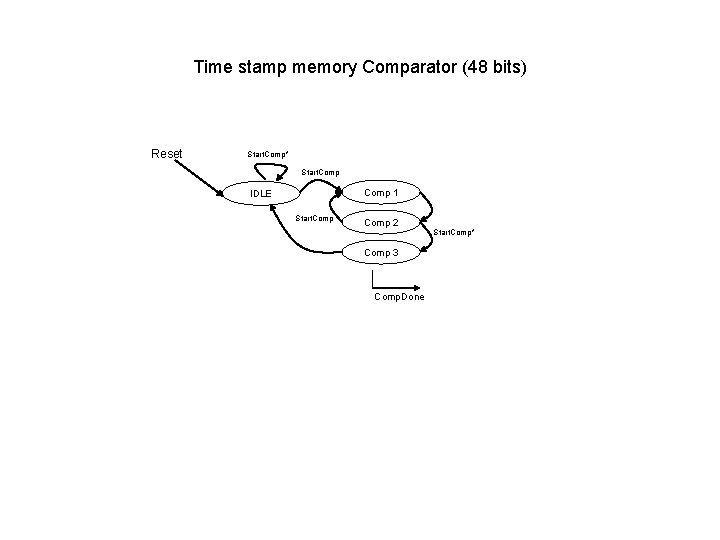

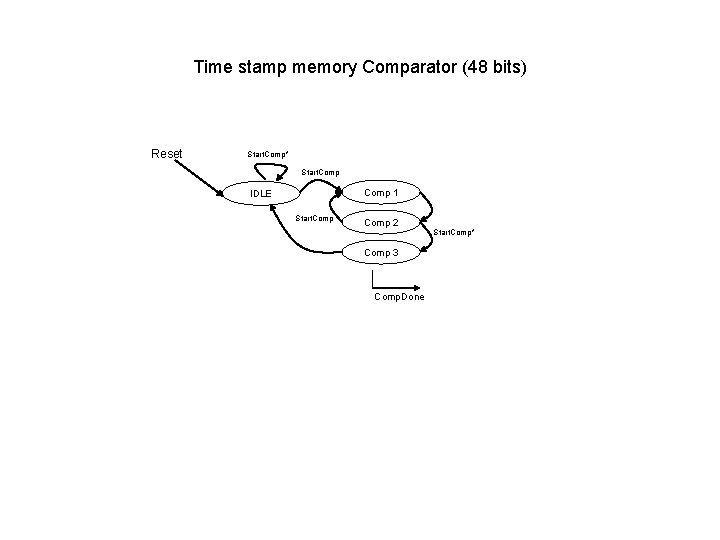

Time stamp memory Comparator (48 bits) Reset Start. Comp* Start. Comp 1 IDLE Start. Comp 2 Comp 3 Comp. Done Start. Comp*

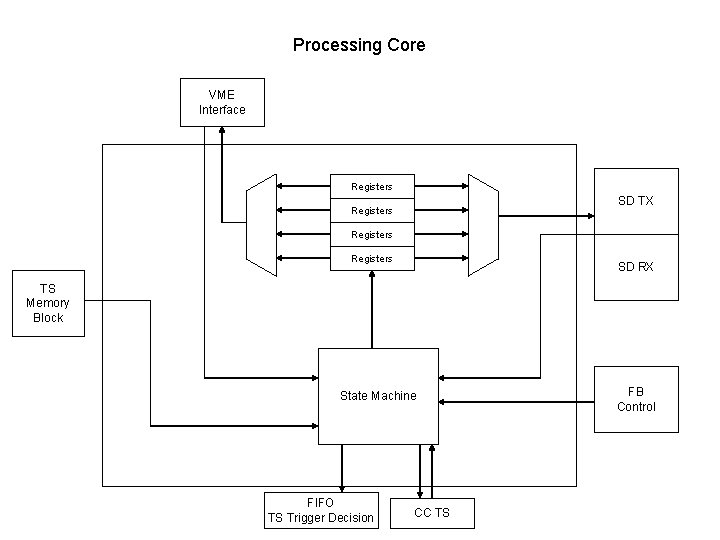

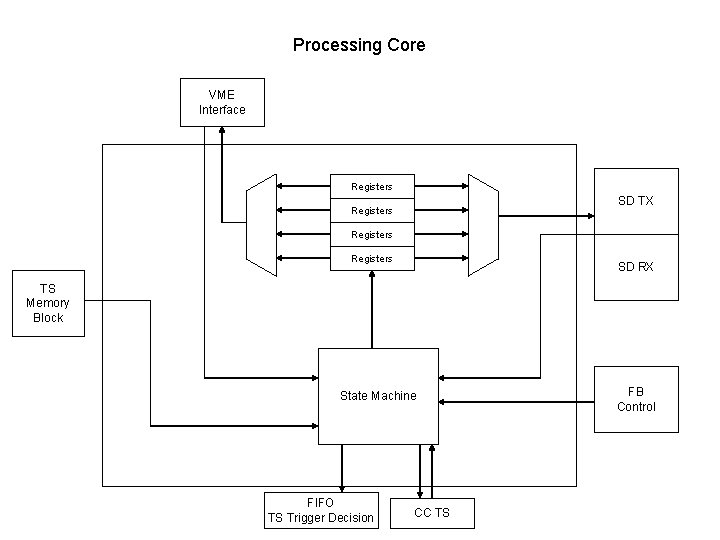

Processing Core VME Interface Registers SD TX Registers SD RX TS Memory Block State Machine FIFO TS Trigger Decision CC TS FB Control

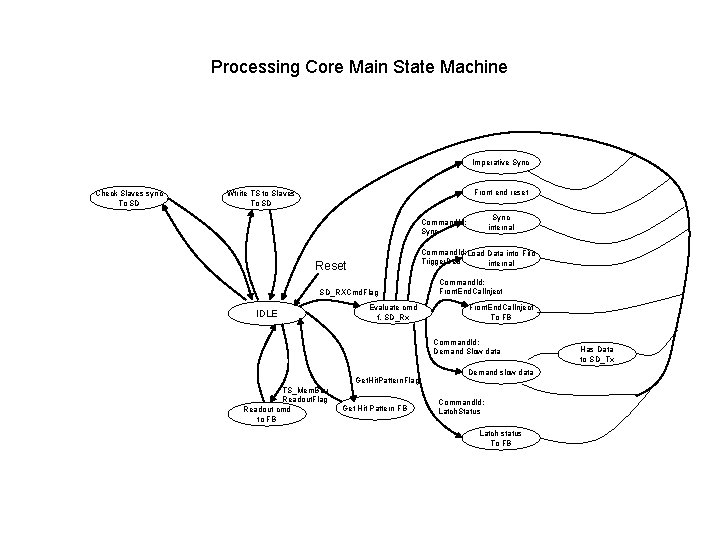

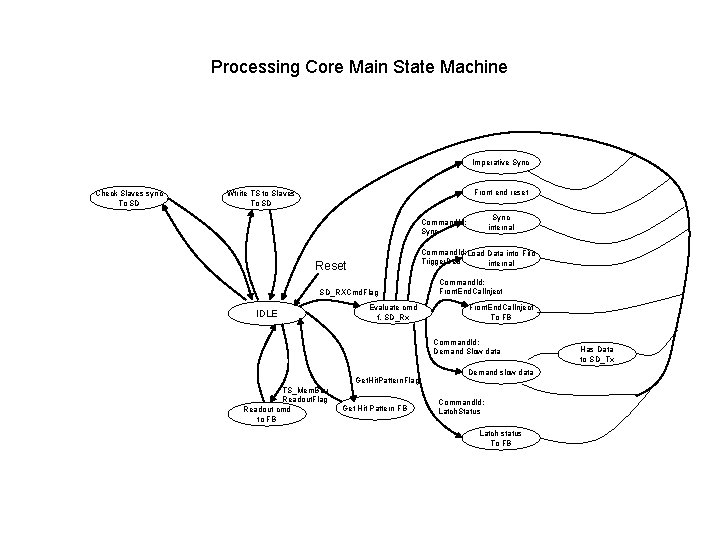

Processing Core Main State Machine Imperative Sync Check Slaves sync To SD Front end reset Wtrite TS to Slaves To SD Sync internal Command. Id: Sync Command. Id: Load Data into Fifo Trigger. Dec internal Reset SD_RXCmd. Flag IDLE Evaluate cmd f. SD_Rx Command. Id: Front. End. Cal. Inject To FB Command. Id: Demand Slow data Get. Hit. Pattern. Flag TS_Mem. Blor Readout. Flag Readout cmd to FB Get Hit Pattern FB Demand slow data Command. Id: Latch. Status Latch status To FB Has Data to SD_Tx

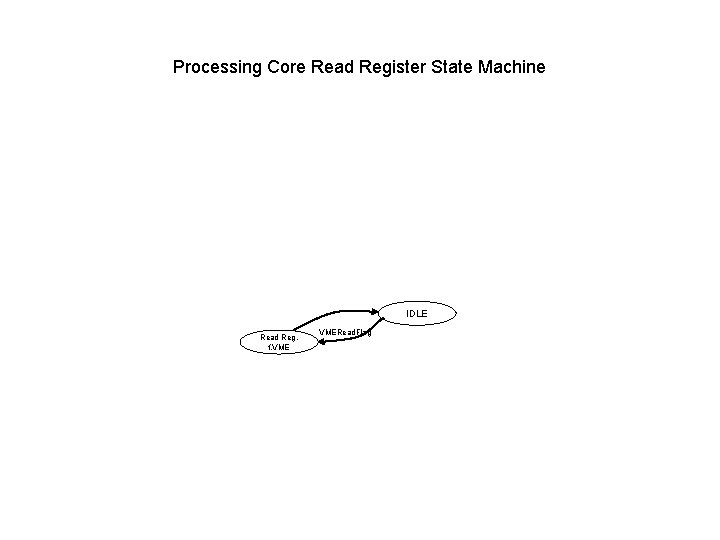

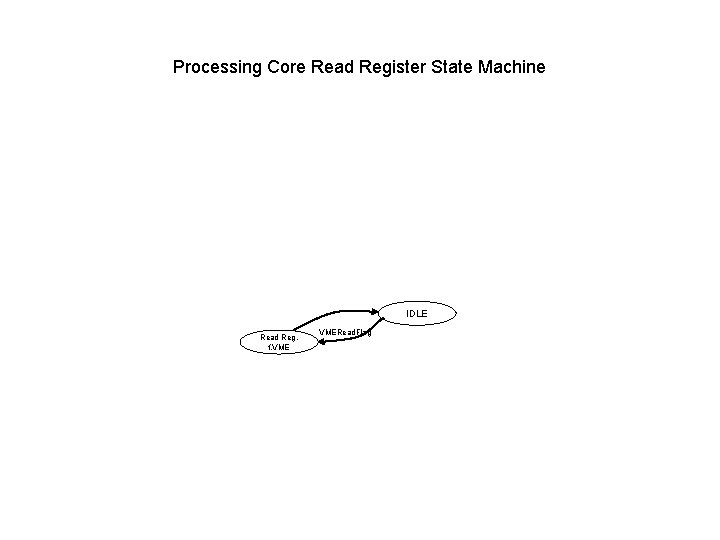

Processing Core Read Register State Machine IDLE Read Reg. f. VMERead. Flag

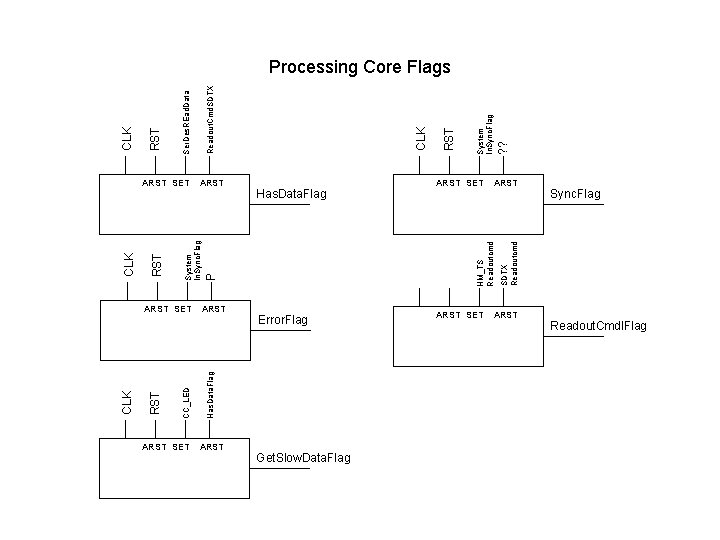

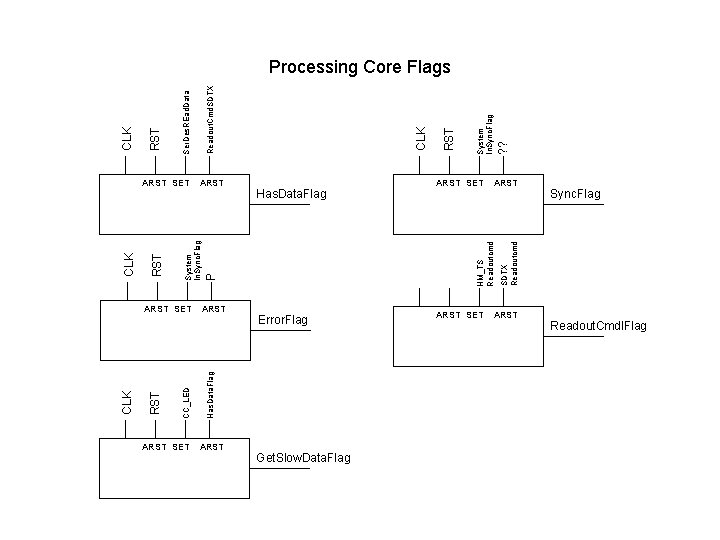

ARST SET ARST Error. Flag Get. Slow. Data. Flag ARST SET ? ? System In. Sync. Flag ARST Sync. Flag SDTX Readoutcmd ARST SET HM_TS Readoutcmd P ARST CLK Has. Data. Flag CC_LED ARST SET RST ARST System In. Sync. Flag RST CLK ARST SET CLK Readout. Cmd. SDTX Ser. Des. REad. Data RST CLK Processing Core Flags ARST Readout. Cmdl. Flag

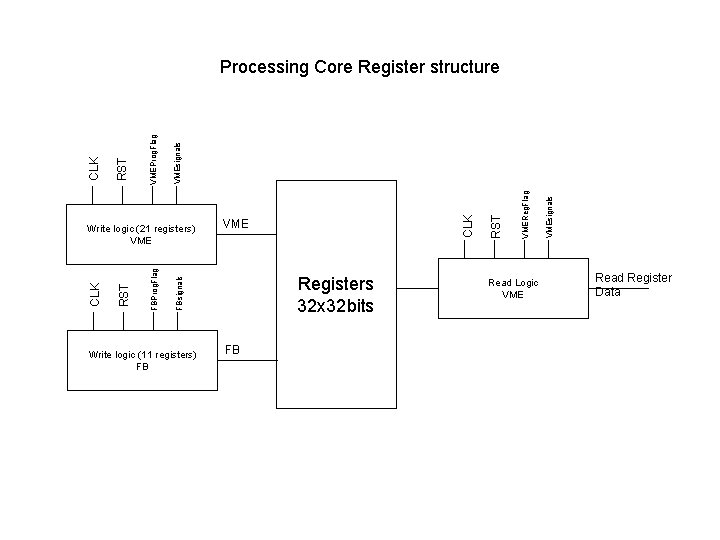

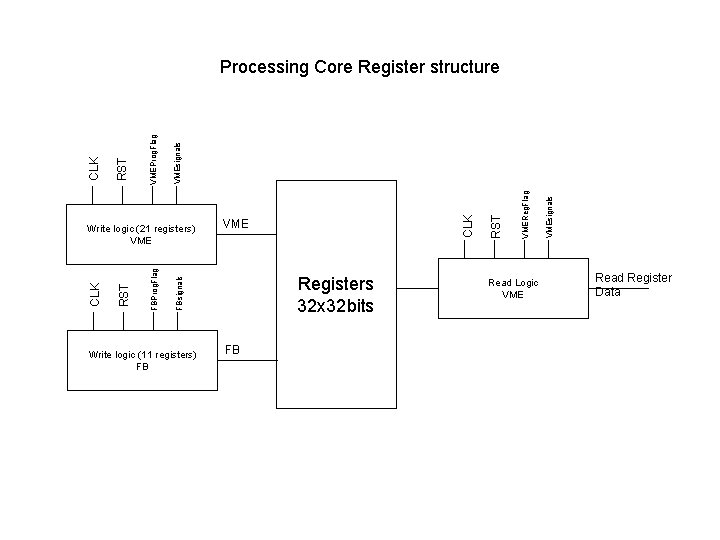

Registers 32 x 32 bits Write logic (11 registers) FB FB Read Logic VMEsignals VMEReg. Flag RST VME FBsignals FBProg. Flag RST CLK Write logic (21 registers) VME CLK VMEsignals VMEProg. Flag RST CLK Processing Core Register structure Read Register Data

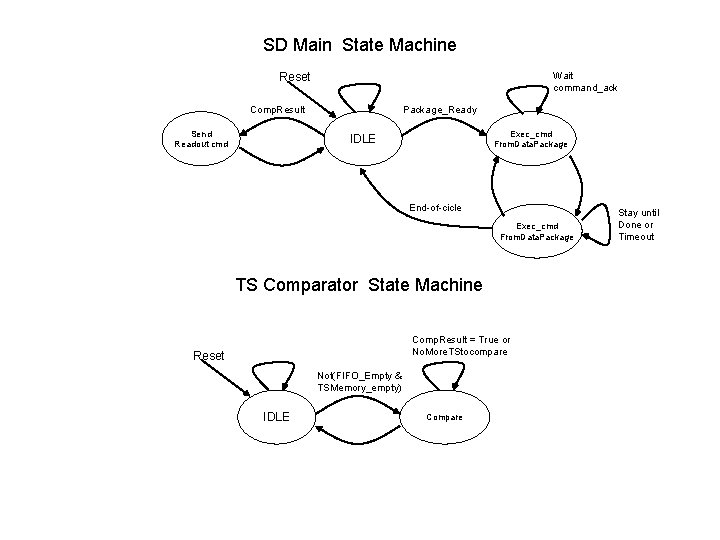

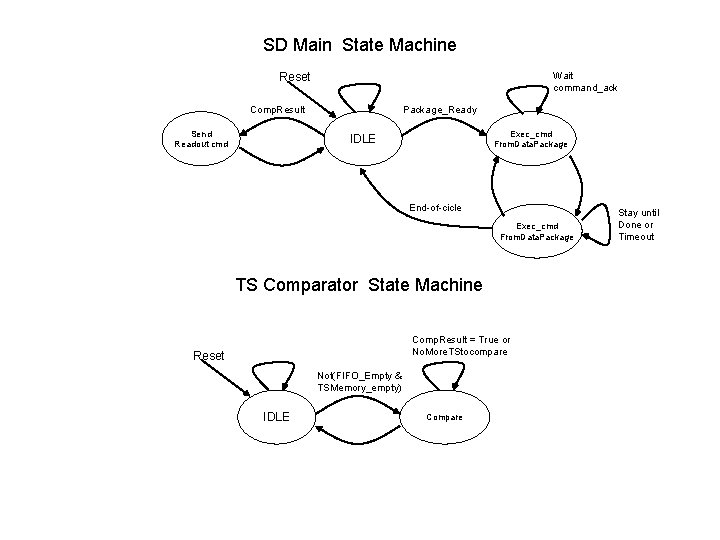

SD Main State Machine Wait command_ack Reset Comp. Result Send Readout cmd Package_Ready Exec_cmd From. Data. Package IDLE End-of-cicle Exec_cmd From. Data. Package TS Comparator State Machine Comp. Result = True or No. More. TStocompare Reset Not(FIFO_Empty & TSMemory_empty) IDLE Compare Stay until Done or Timeout

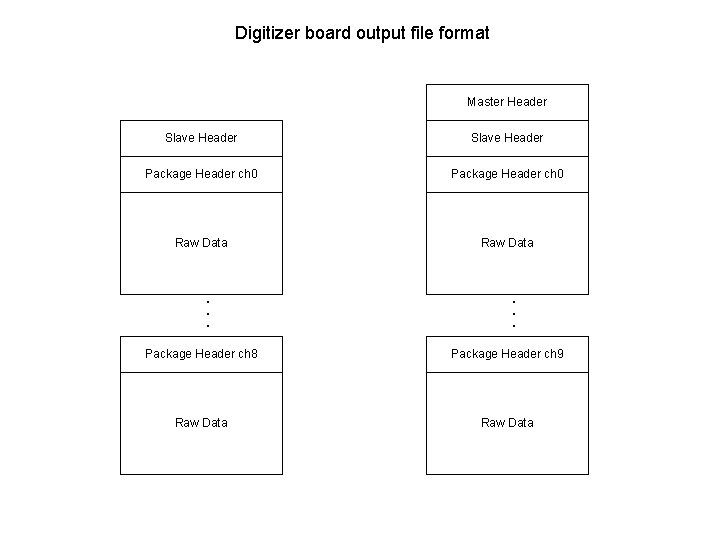

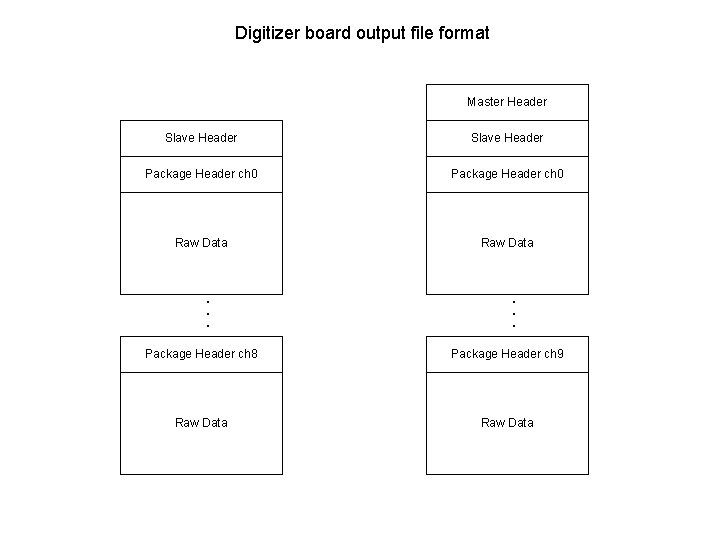

Digitizer board output file format Master Header Slave Header Package Header ch 0 Raw Data . . . Package Header ch 8 Package Header ch 9 Raw Data