R R Q Clk Q S Clk S

![module swap (Data, Resetn, w, Clock, Extern, Rin. Ext, Bus. Wires); input [7: 0] module swap (Data, Resetn, w, Clock, Extern, Rin. Ext, Bus. Wires); input [7: 0]](https://slidetodoc.com/presentation_image_h2/a0a7d52dc58794c0a35f64af45884ac5/image-11.jpg)

![module swapmux(Data, Resetn, w, Clock, Rin. Ext, Bus. Wires); input [7: 0] Data; input module swapmux(Data, Resetn, w, Clock, Rin. Ext, Bus. Wires); input [7: 0] Data; input](https://slidetodoc.com/presentation_image_h2/a0a7d52dc58794c0a35f64af45884ac5/image-12.jpg)

![module swapmux (Data, Resetn, w, Clock, Rin. Ext, Bus. Wires); input [7: 0] Data; module swapmux (Data, Resetn, w, Clock, Rin. Ext, Bus. Wires); input [7: 0] Data;](https://slidetodoc.com/presentation_image_h2/a0a7d52dc58794c0a35f64af45884ac5/image-13.jpg)

![module proc(Data, Reset, w, Clock, F, Rx, Ry, Done, Bus. Wires); input [7: 0] module proc(Data, Reset, w, Clock, F, Rx, Ry, Done, Bus. Wires); input [7: 0]](https://slidetodoc.com/presentation_image_h2/a0a7d52dc58794c0a35f64af45884ac5/image-14.jpg)

![module proc(Data, Reset, w, Clock, F, Rx, Ry, Done, Bus. Wires); input [7: 0] module proc(Data, Reset, w, Clock, F, Rx, Ry, Done, Bus. Wires); input [7: 0]](https://slidetodoc.com/presentation_image_h2/a0a7d52dc58794c0a35f64af45884ac5/image-16.jpg)

![regn reg_0 (Bus. Wires, Rin[0], Clock, R 0); regn reg_1 (Bus. Wires, Rin[1], Clock, regn reg_0 (Bus. Wires, Rin[0], Clock, R 0); regn reg_1 (Bus. Wires, Rin[1], Clock,](https://slidetodoc.com/presentation_image_h2/a0a7d52dc58794c0a35f64af45884ac5/image-18.jpg)

- Slides: 20

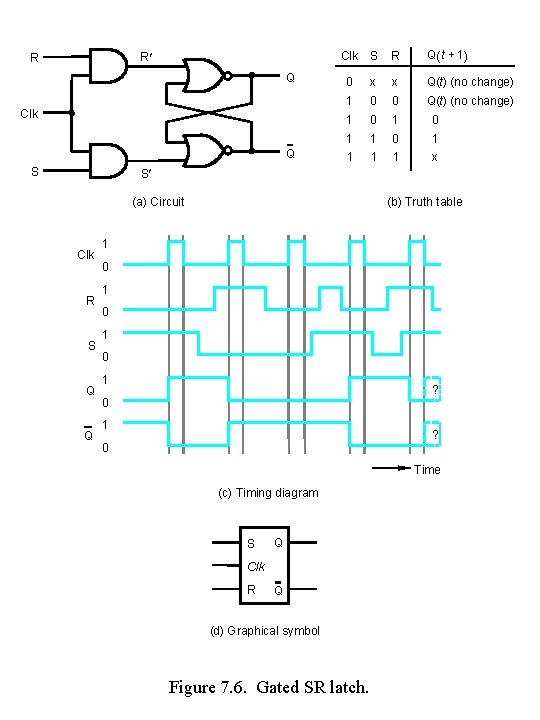

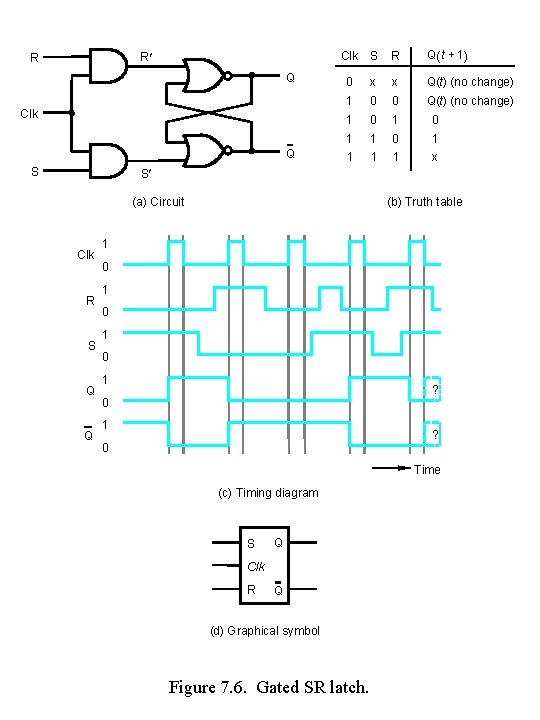

R¢ R Q Clk Q S Clk S R Q( t + 1 ) 0 x x Q(t) (no change) 1 0 0 Q(t) (no change) 1 0 1 1 x S¢ (a) Circuit Clk R S Q Q (b) Truth table 1 0 1 0 1 ? 0 Time (c) Timing diagram S Q Clk R Q (d) Graphical symbol Figure 7. 6. Gated SR latch.

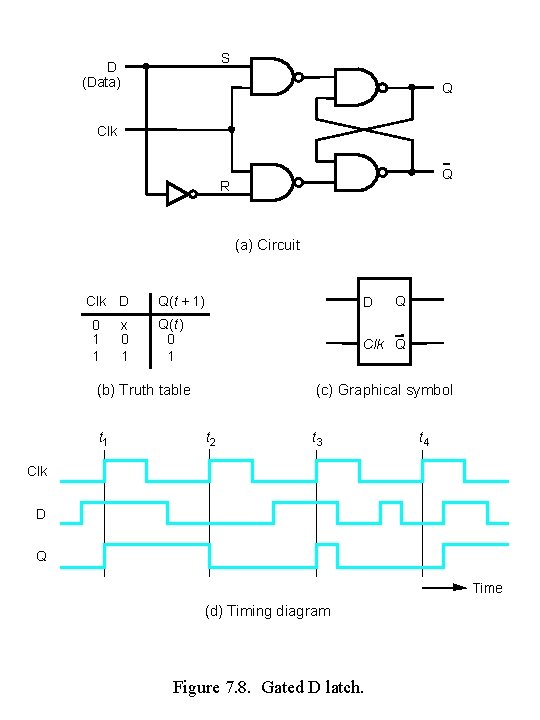

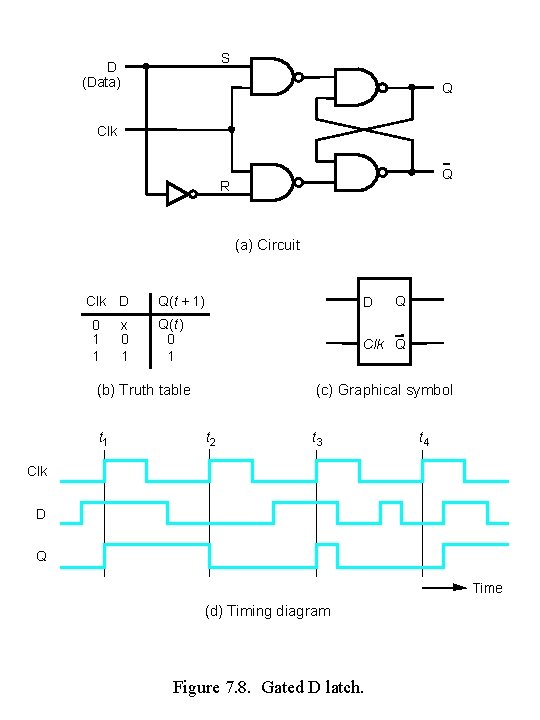

S D (Data) Q Clk Q R (a) Circuit Clk D 0 1 1 x 0 1 Q( t + 1) D Q( t ) 0 1 Clk Q (b) Truth table t 1 Q (c) Graphical symbol t 2 t 3 t 4 Clk D Q Time (d) Timing diagram Figure 7. 8. Gated D latch.

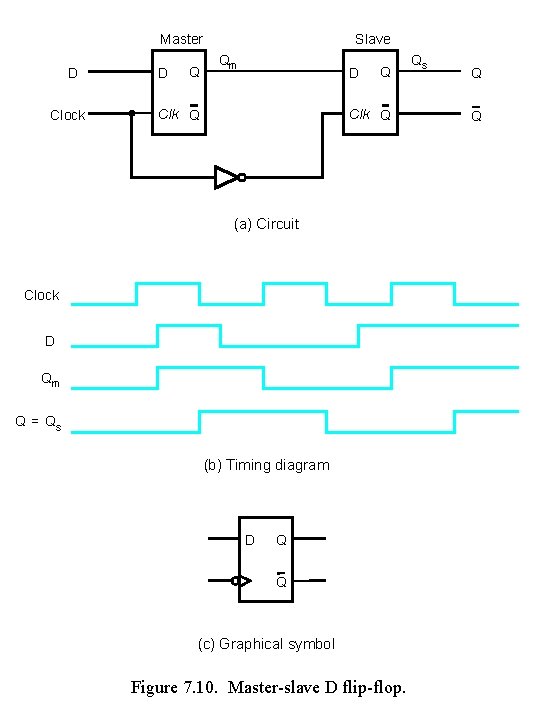

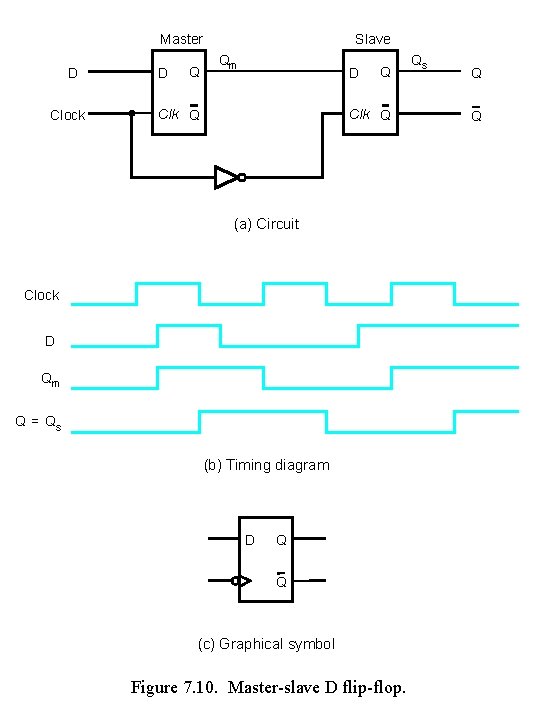

Master D Clock D Q Slave Qm D Clk Q Q Clk Q (a) Circuit Clock D Qm Q = Qs (b) Timing diagram D Q Q (c) Graphical symbol Figure 7. 10. Master-slave D flip-flop. Qs Q Q

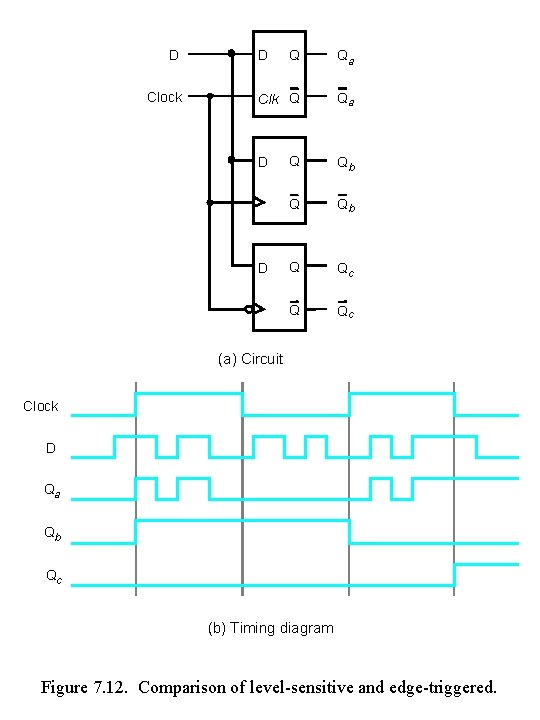

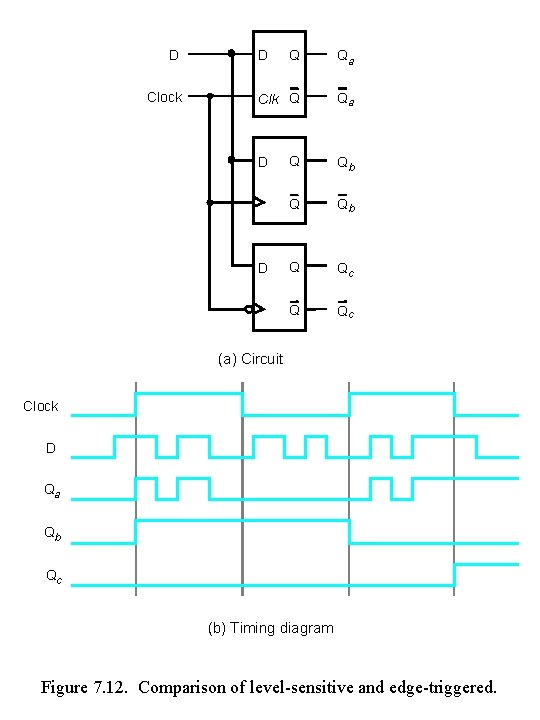

D Clock Q Qa Clk Q Qa Q Qb Q Qc D D D (a) Circuit Clock D Qa Qb Qc (b) Timing diagram Figure 7. 12. Comparison of level-sensitive and edge-triggered.

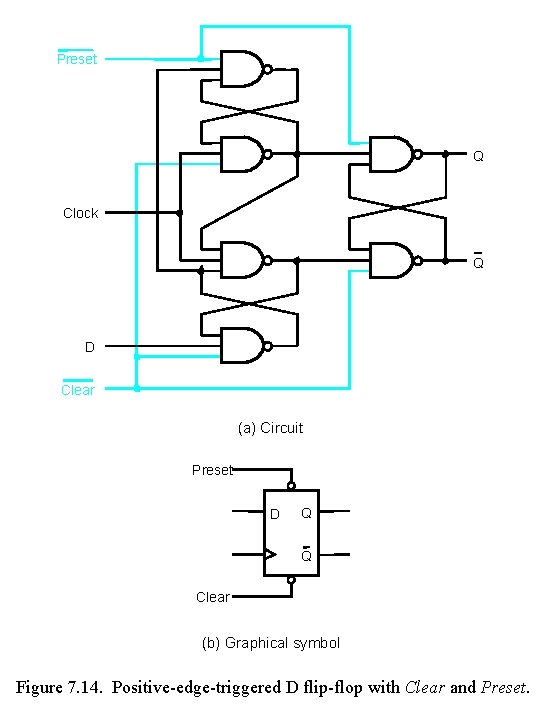

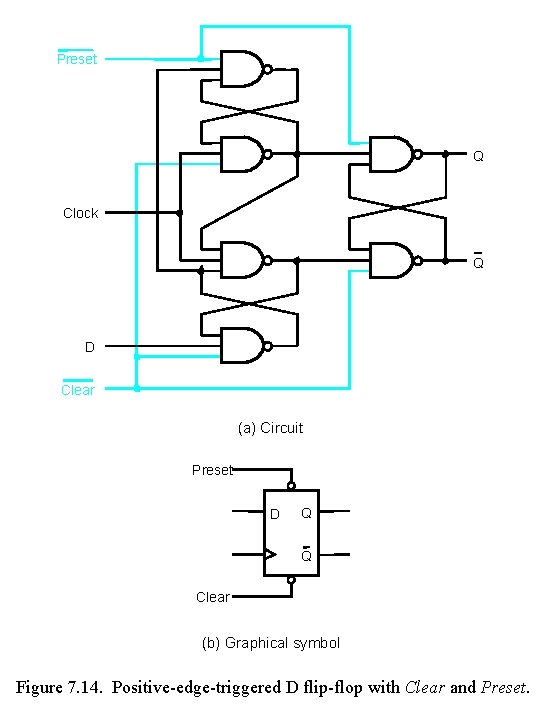

Preset Q Clock Q D Clear (a) Circuit Preset D Q Q Clear (b) Graphical symbol Figure 7. 14. Positive-edge-triggered D flip-flop with Clear and Preset.

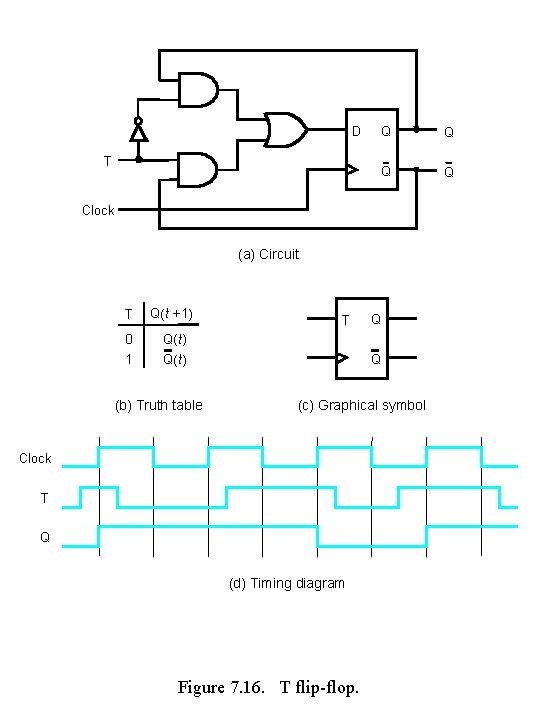

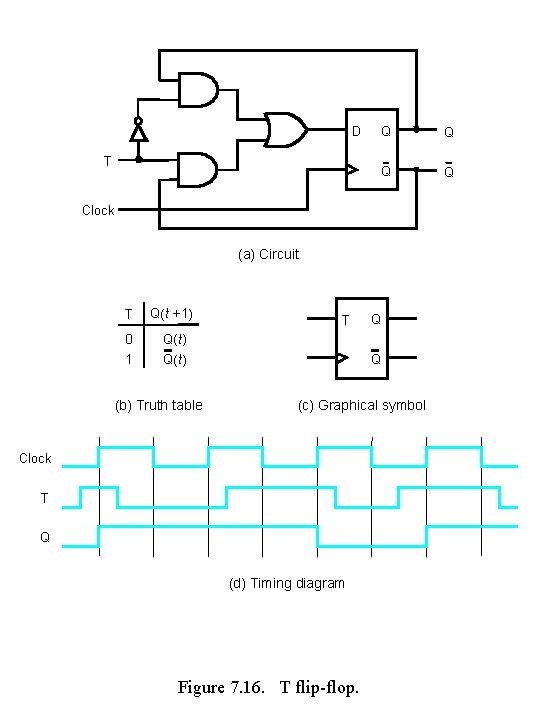

D T Q Q Clock (a) Circuit T Q( t + 1) 0 Q( t ) 1 Q( t ) (b) Truth table T Q Q (c) Graphical symbol Clock T Q (d) Timing diagram Figure 7. 16. T flip-flop.

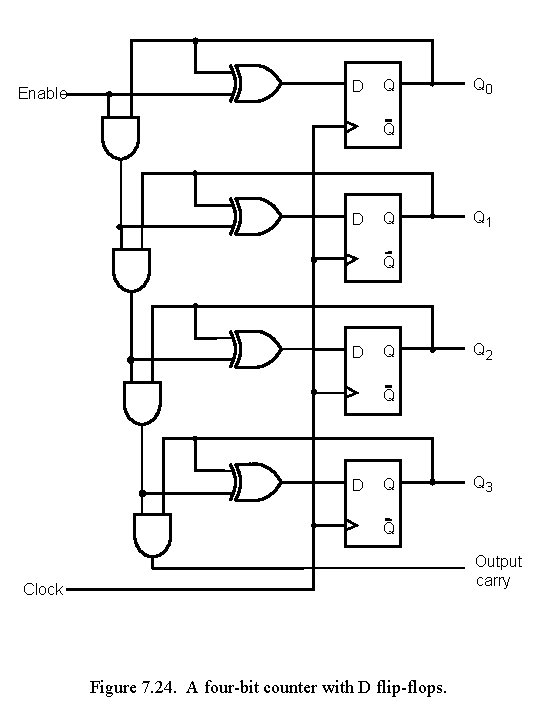

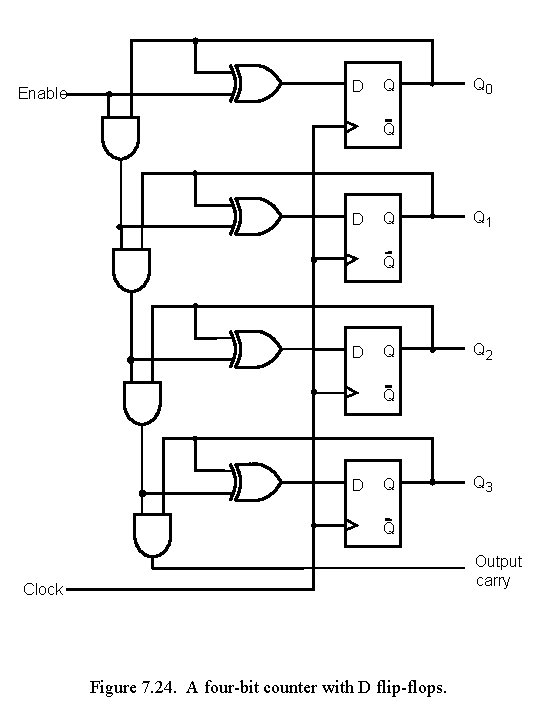

Enable D Q Q 0 Q D Q Q 1 Q D Q Q 2 Q D Q Q 3 Q Output carry Clock Figure 7. 24. A four-bit counter with D flip-flops.

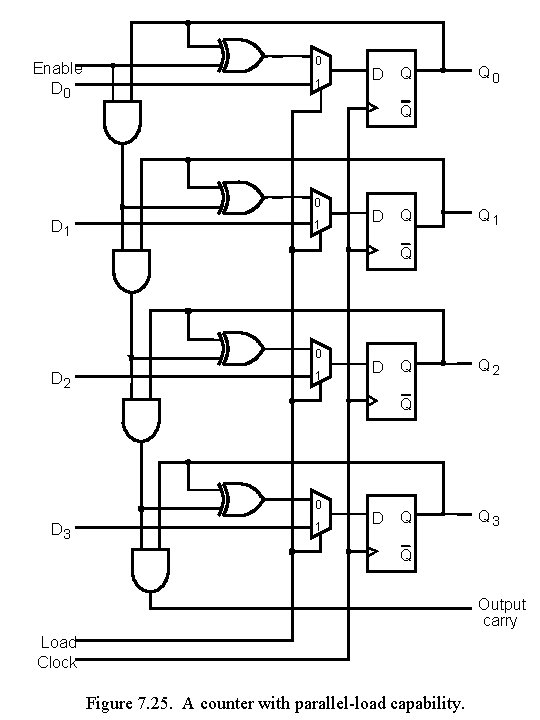

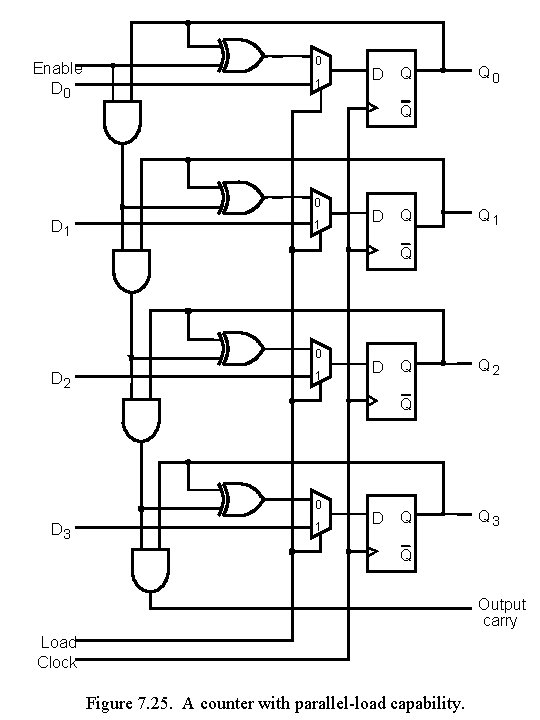

Enable D 0 0 1 D Q Q 0 D 1 1 D Q Q 1 Q 0 D 2 1 D Q Q 2 Q 0 D 3 1 D Q Q 3 Q Output carry Load Clock Figure 7. 25. A counter with parallel-load capability.

Figure 7. 29. Ring counter.

Figure 7. 33. Implementation of a circuit in a CPLD.

![module swap Data Resetn w Clock Extern Rin Ext Bus Wires input 7 0 module swap (Data, Resetn, w, Clock, Extern, Rin. Ext, Bus. Wires); input [7: 0]](https://slidetodoc.com/presentation_image_h2/a0a7d52dc58794c0a35f64af45884ac5/image-11.jpg)

module swap (Data, Resetn, w, Clock, Extern, Rin. Ext, Bus. Wires); input [7: 0] Data; input Resetn, w, Clock, Extern; input [1: 3] Rin. Ext; output [7: 0] Bus. Wires; tri [7: 0] Bus. Wires; wire [1: 3] Rin, Rout, Q; wire [7: 0] R 1, R 2, R 3; shiftr control (Resetn, w, Clock, Q); defparam control. m = 3; assign Rin[1] = Rin. Ext[1] | Q[3]; assign Rin[2] = Rin. Ext[2] | Q[2]; assign Rin[3] = Rin. Ext[3] | Q[1]; assign Rout[1] = Q[2]; assign Rout[2] = Q[1]; assign Rout[3] = Q[3]; regn reg_1 (Bus. Wires, Rin[1], Clock, R 1); regn reg_2 (Bus. Wires, Rin[2], Clock, R 2); regn reg_3 (Bus. Wires, Rin[3], Clock, R 3); trin tri_ext (Data, Extern, Bus. Wires); trin tri_1 (R 1, Rout[1], Bus. Wires); trin tri_2 (R 2, Rout[2], Bus. Wires); trin tri_3 (R 3, Rout[3], Bus. Wires); endmodule Figure 7. 69. A digital system like the one in Figure 7. 60.

![module swapmuxData Resetn w Clock Rin Ext Bus Wires input 7 0 Data input module swapmux(Data, Resetn, w, Clock, Rin. Ext, Bus. Wires); input [7: 0] Data; input](https://slidetodoc.com/presentation_image_h2/a0a7d52dc58794c0a35f64af45884ac5/image-12.jpg)

module swapmux(Data, Resetn, w, Clock, Rin. Ext, Bus. Wires); input [7: 0] Data; input Resetn, w, Clock; input [1: 3] Rin. Ext; output [7: 0] Bus. Wires; reg [7: 0] Bus. Wires; wire [1: 3] Rin, Q; wire [7: 0] R 1, R 2, R 3; reg [1: 0] S; shiftr control (Resetn, w, Clock, Q); defparam control. m = 3; assign Rin[1] = Rin. Ext[1] | Q[3]; assign Rin[2] = Rin. Ext[2] | Q[2]; assign Rin[3] = Rin. Ext[3] | Q[1]; regn reg_1 (Bus. Wires, Rin[1], Clock, R 1); regn reg_2 (Bus. Wires, Rin[2], Clock, R 2); regn reg_3 (Bus. Wires, Rin[3], Clock, R 3); always @(Q or Data or R 1 or R 2 or R 3 or S) begin // Encoder if (Q == 3'b 000) S = 2'b 00; else if (Q == 3'b 100) S = 2'b 10; else if (Q == 3'b 010) S = 2'b 01; else S = 2'b 11; // Multiplexers if (S == 2'b 00) Bus. Wires = Data; else if (S == 2'b 01) Bus. Wires = R 1; else if (S == 2'b 10) Bus. Wires = R 2; else Bus. Wires = R 3; endmodule Figure 7. 70. Using multiplexers to implement a bus.

![module swapmux Data Resetn w Clock Rin Ext Bus Wires input 7 0 Data module swapmux (Data, Resetn, w, Clock, Rin. Ext, Bus. Wires); input [7: 0] Data;](https://slidetodoc.com/presentation_image_h2/a0a7d52dc58794c0a35f64af45884ac5/image-13.jpg)

module swapmux (Data, Resetn, w, Clock, Rin. Ext, Bus. Wires); input [7: 0] Data; input Resetn, w, Clock; input [1: 3] Rin. Ext; output [7: 0] Bus. Wires; reg [7: 0] Bus. Wires; wire [1: 3] Rin, Q; wire [7: 0] R 1, R 2, R 3; shiftr control (Resetn, w, Clock, Q); defparam control. m = 3; assign Rin[1] = Rin. Ext[1] | Q[3]; assign Rin[2] = Rin. Ext[2] | Q[2]; assign Rin[3] = Rin. Ext[3] | Q[1]; regn reg_1 (Bus. Wires, Rin[1], Clock, R 1); regn reg_2 (Bus. Wires, Rin[2], Clock, R 2); regn reg_3 (Bus. Wires, Rin[3], Clock, R 3); always @(Q or Data or R 1 or R 2 or R 3) begin if (Q == 3'b 000) Bus. Wires = Data; else if (Q == 3'b 100) Bus. Wires = R 2; else if (Q == 3'b 010) Bus. Wires = R 1; else Bus. Wires = R 3; endmodule Figure 7. 71. A simplified version of the specification in Figure 7. 70.

![module procData Reset w Clock F Rx Ry Done Bus Wires input 7 0 module proc(Data, Reset, w, Clock, F, Rx, Ry, Done, Bus. Wires); input [7: 0]](https://slidetodoc.com/presentation_image_h2/a0a7d52dc58794c0a35f64af45884ac5/image-14.jpg)

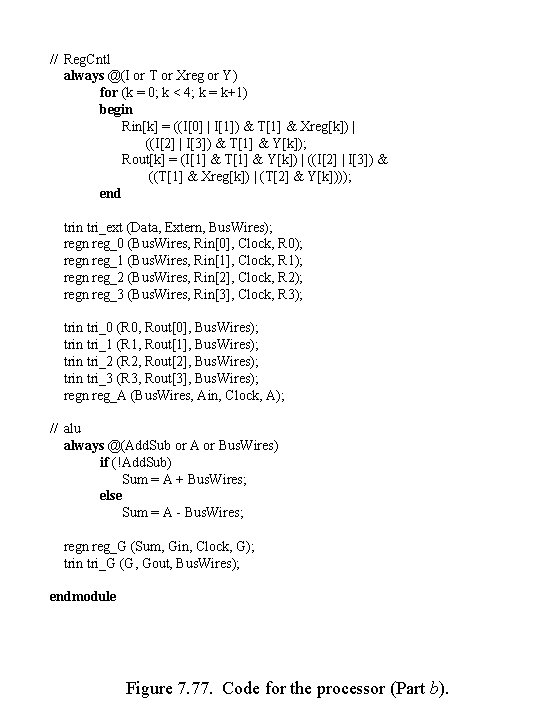

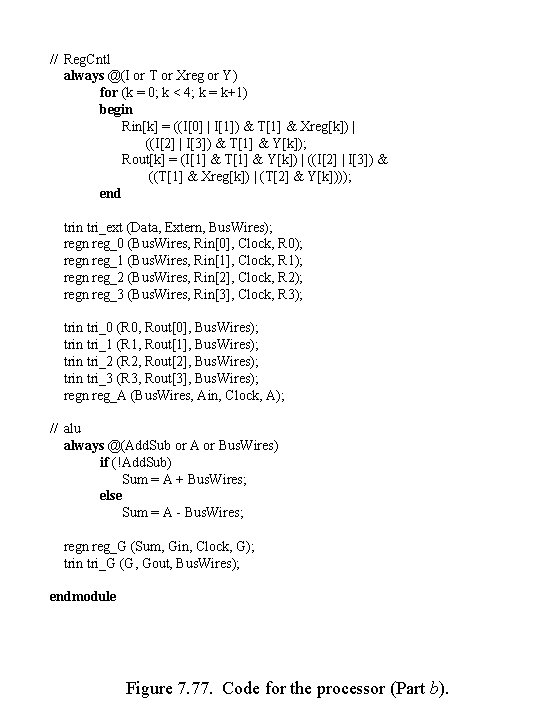

module proc(Data, Reset, w, Clock, F, Rx, Ry, Done, Bus. Wires); input [7: 0] Data; input Reset, w, Clock; input [1: 0] F, Rx, Ry; output [7: 0] Bus. Wires; output Done; wire [7: 0] Bus. Wires; reg [0: 3] Rin, Rout; reg [7: 0] Sum; wire Clear, Add. Sub, Extern, Ain, Gout, FRin; wire [1: 0] Count; wire [0: 3] T, I, Xreg, Y; wire [7: 0] R 0, R 1, R 2, R 3, A, G; wire [1: 6] Func, Func. Reg; integer k; upcounter (Clear, Clock, Count); dec 2 to 4 dec. T (Count, 1, T); assign Clear = Reset | Done | (~w & T[0]); assign Func = {F, Rx, Ry}; assign FRin = w & T[0]; regn functionreg (Func, FRin, Clock, Func. Reg); defparam functionreg. n = 6; dec 2 to 4 dec. I (Func. Reg[1: 2], 1, I); dec 2 to 4 dec. X (Func. Reg[3: 4], 1, Xreg); dec 2 to 4 dec. Y (Func. Reg[5: 6], 1, Y); assign Extern = I[0] & T[1]; assign Done = ((I[0] | I[1]) & T[1]) | ((I[2] | I[3]) & T[3]); assign Ain = (I[2] | I[3]) & T[1]; assign Gin = (I[2] | I[3]) & T[2]; assign Gout = (I[2] | I[3]) & T[3]; assign Add. Sub = I[3]; … continiued in Part b. Figure 7. 77. Code for the processor (Part a).

// Reg. Cntl always @(I or T or Xreg or Y) for (k = 0; k < 4; k = k+1) begin Rin[k] = ((I[0] | I[1]) & T[1] & Xreg[k]) | ((I[2] | I[3]) & T[1] & Y[k]); Rout[k] = (I[1] & T[1] & Y[k]) | ((I[2] | I[3]) & ((T[1] & Xreg[k]) | (T[2] & Y[k]))); end trin tri_ext (Data, Extern, Bus. Wires); regn reg_0 (Bus. Wires, Rin[0], Clock, R 0); regn reg_1 (Bus. Wires, Rin[1], Clock, R 1); regn reg_2 (Bus. Wires, Rin[2], Clock, R 2); regn reg_3 (Bus. Wires, Rin[3], Clock, R 3); trin tri_0 (R 0, Rout[0], Bus. Wires); trin tri_1 (R 1, Rout[1], Bus. Wires); trin tri_2 (R 2, Rout[2], Bus. Wires); trin tri_3 (R 3, Rout[3], Bus. Wires); regn reg_A (Bus. Wires, Ain, Clock, A); // alu always @(Add. Sub or A or Bus. Wires) if (!Add. Sub) Sum = A + Bus. Wires; else Sum = A - Bus. Wires; regn reg_G (Sum, Gin, Clock, G); trin tri_G (G, Gout, Bus. Wires); endmodule Figure 7. 77. Code for the processor (Part b).

![module procData Reset w Clock F Rx Ry Done Bus Wires input 7 0 module proc(Data, Reset, w, Clock, F, Rx, Ry, Done, Bus. Wires); input [7: 0]](https://slidetodoc.com/presentation_image_h2/a0a7d52dc58794c0a35f64af45884ac5/image-16.jpg)

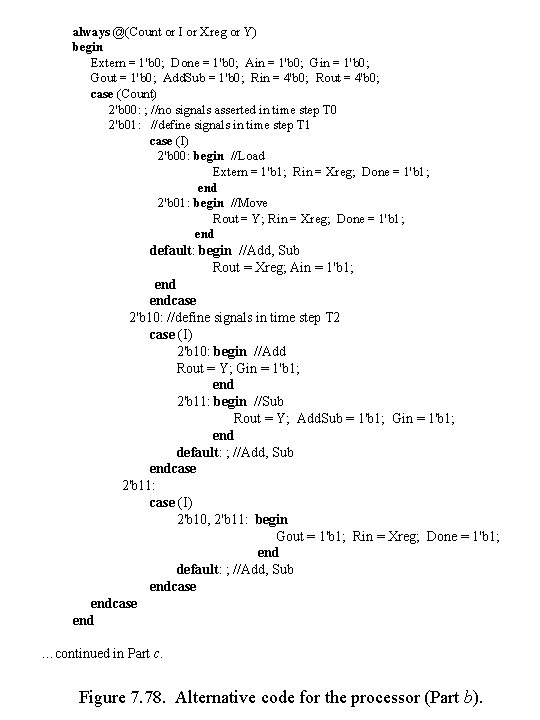

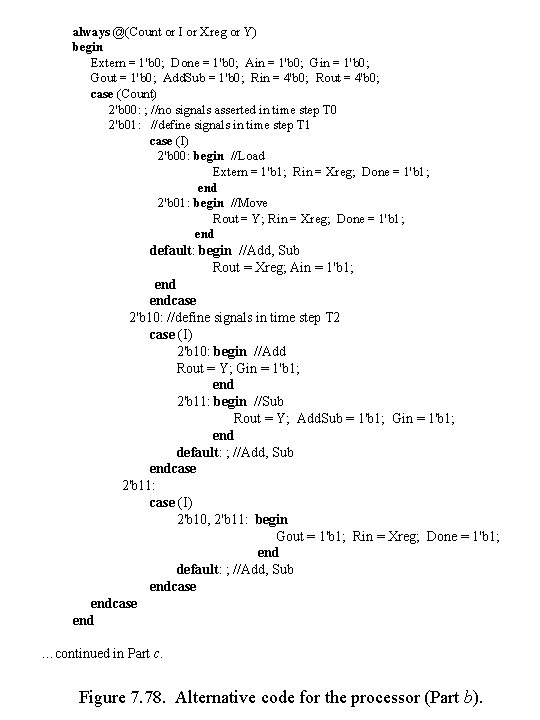

module proc(Data, Reset, w, Clock, F, Rx, Ry, Done, Bus. Wires); input [7: 0] Data; input Reset, w, Clock; input [1: 0] F, Rx, Ry; output [7: 0] Bus. Wires; output Done; reg [7: 0] Bus. Wires, Sum; reg [0: 3] Rin, Rout; reg Extern, Done, Ain, Gout, Add. Sub; wire [1: 0] Count, I; wire [0: 3] Xreg, Y; wire [7: 0] R 0, R 1, R 2, R 3, A, G; wire [1: 6] Func, Func. Reg, Sel; wire Clear = Reset | Done | (~w & ~Count[1] & ~Count[0]); upcounter (Clear, Clock, Count); assign Func = {F, Rx, Ry}; wire FRin = w & ~Count[1] & ~Count[0]; regn functionreg (Func, FRin, Clock, Func. Reg); defparam functionreg. n = 6; assign I = Func. Reg[1: 2]; dec 2 to 4 dec. X (Func. Reg[3: 4], 1, Xreg); dec 2 to 4 dec. Y (Func. Reg[5: 6], 1, Y); … continued in Part b. Figure 7. 78. Alternative code for the processor. (Part a).

always @(Count or I or Xreg or Y) begin Extern = 1'b 0; Done = 1'b 0; Ain = 1'b 0; Gout = 1'b 0; Add. Sub = 1'b 0; Rin = 4'b 0; Rout = 4'b 0; case (Count) 2'b 00: ; //no signals asserted in time step T 0 2'b 01: //define signals in time step T 1 case (I) 2'b 00: begin //Load Extern = 1'b 1; Rin = Xreg; Done = 1'b 1; end 2'b 01: begin //Move Rout = Y; Rin = Xreg; Done = 1'b 1; end default: begin //Add, Sub Rout = Xreg; Ain = 1'b 1; endcase 2'b 10: //define signals in time step T 2 case (I) 2'b 10: begin //Add Rout = Y; Gin = 1'b 1; end 2'b 11: begin //Sub Rout = Y; Add. Sub = 1'b 1; Gin = 1'b 1; end default: ; //Add, Sub endcase 2'b 11: case (I) 2'b 10, 2'b 11: begin Gout = 1'b 1; Rin = Xreg; Done = 1'b 1; end default: ; //Add, Sub endcase end …continued in Part c. Figure 7. 78. Alternative code for the processor (Part b).

![regn reg0 Bus Wires Rin0 Clock R 0 regn reg1 Bus Wires Rin1 Clock regn reg_0 (Bus. Wires, Rin[0], Clock, R 0); regn reg_1 (Bus. Wires, Rin[1], Clock,](https://slidetodoc.com/presentation_image_h2/a0a7d52dc58794c0a35f64af45884ac5/image-18.jpg)

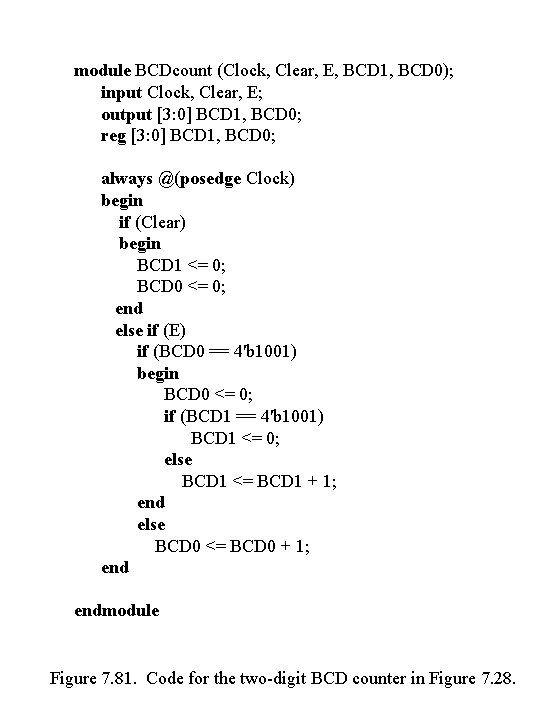

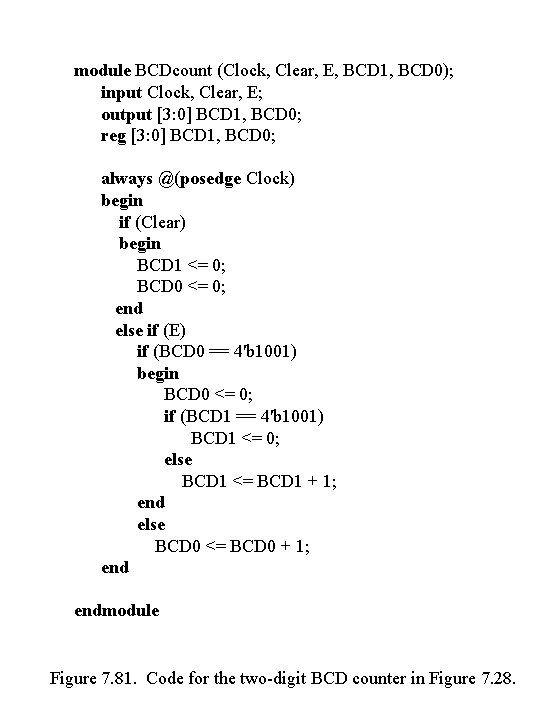

regn reg_0 (Bus. Wires, Rin[0], Clock, R 0); regn reg_1 (Bus. Wires, Rin[1], Clock, R 1); regn reg_2 (Bus. Wires, Rin[2], Clock, R 2); regn reg_3 (Bus. Wires, Rin[3], Clock, R 3); regn reg_A (Bus. Wires, Ain, Clock, A); //alu always @(Add. Sub or A or Bus. Wires) begin if (!Add. Sub) Sum = A + Bus. Wires; else Sum = A - Bus. Wires; end regn reg_G (Sum, Gin, Clock, G); assign Sel = {Rout, Gout, Extern}; always @(Sel or R 0 or R 1 or R 2 or R 3 or G or Data) begin if (Sel == 6'b 100000) Bus. Wires = R 0; else if (Sel == 6'b 010000) Bus. Wires = R 1; else if (Sel == 6'b 001000) Bus. Wires = R 2; else if (Sel == 6'b 000100) Bus. Wires = R 3; else if (Sel == 6'b 000010) Bus. Wires = G; else Bus. Wires = Data; endmodule Figure 7. 78. Alternative code for the processor (Part c).

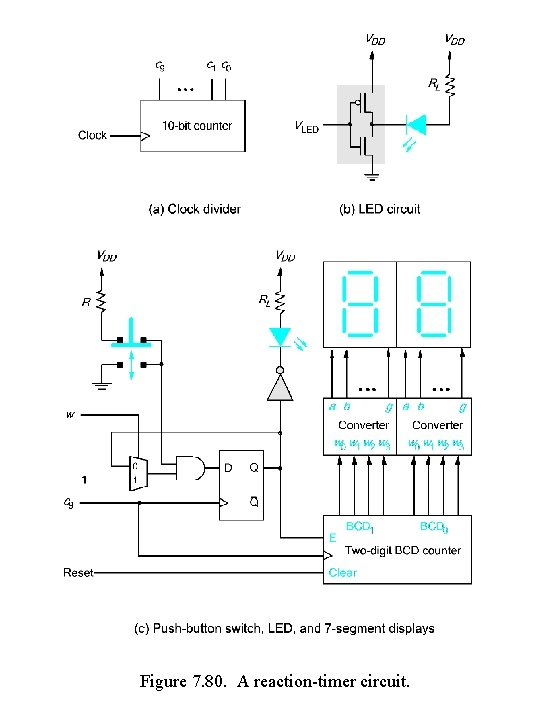

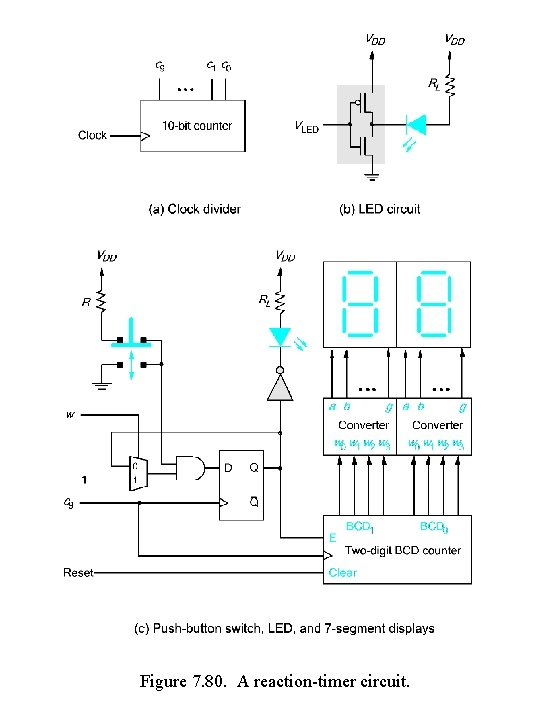

Figure 7. 80. A reaction-timer circuit.

module BCDcount (Clock, Clear, E, BCD 1, BCD 0); input Clock, Clear, E; output [3: 0] BCD 1, BCD 0; reg [3: 0] BCD 1, BCD 0; always @(posedge Clock) begin if (Clear) begin BCD 1 <= 0; BCD 0 <= 0; end else if (E) if (BCD 0 == 4'b 1001) begin BCD 0 <= 0; if (BCD 1 == 4'b 1001) BCD 1 <= 0; else BCD 1 <= BCD 1 + 1; end else BCD 0 <= BCD 0 + 1; endmodule Figure 7. 81. Code for the two-digit BCD counter in Figure 7. 28.