setup if clkevent and clk 1 or clk

- Slides: 51

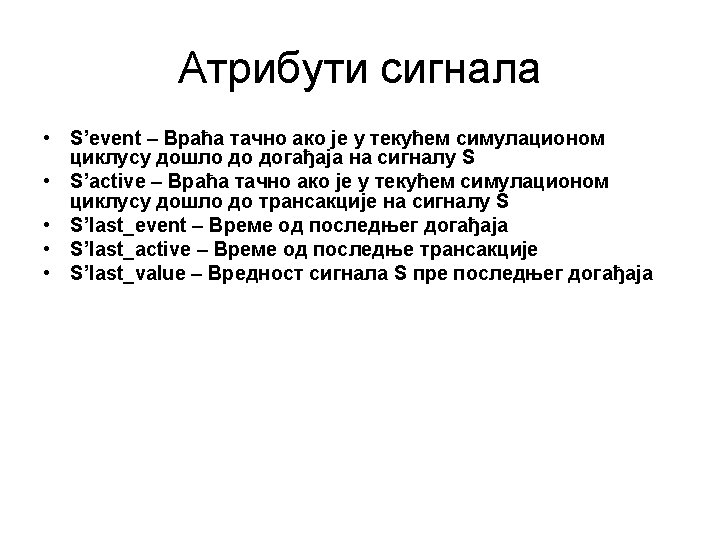

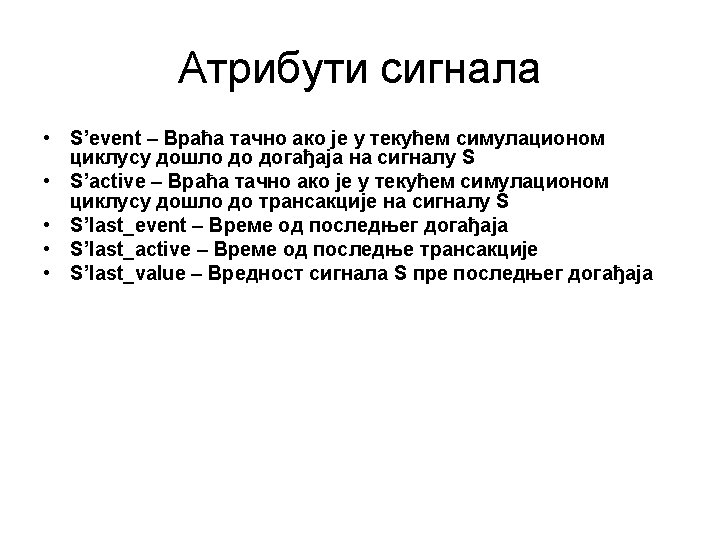

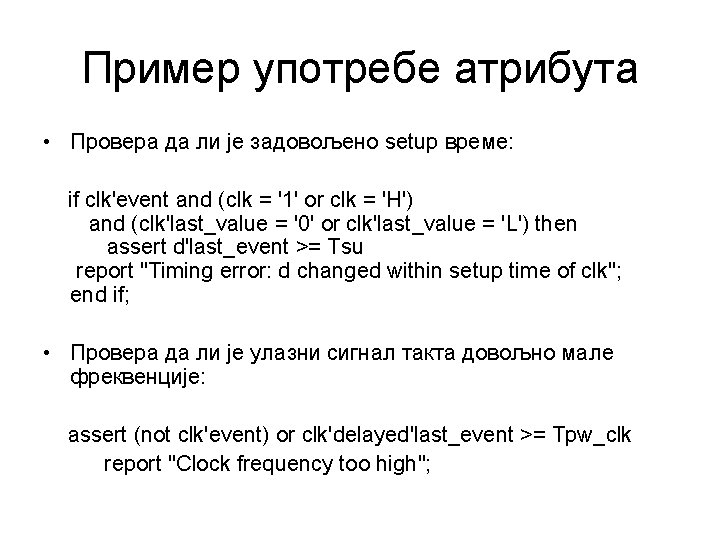

Пример употребе атрибута • Провера да ли је задовољено setup време: if clk'event and (clk = '1' or clk = 'H') and (clk'last_value = '0' or clk'last_value = 'L') then assert d'last_event >= Tsu report "Timing error: d changed within setup time of clk"; end if; • Провера да ли је улазни сигнал такта довољно мале фреквенције: assert (not clk'event) or clk'delayed'last_event >= Tpw_clk report "Clock frequency too high";

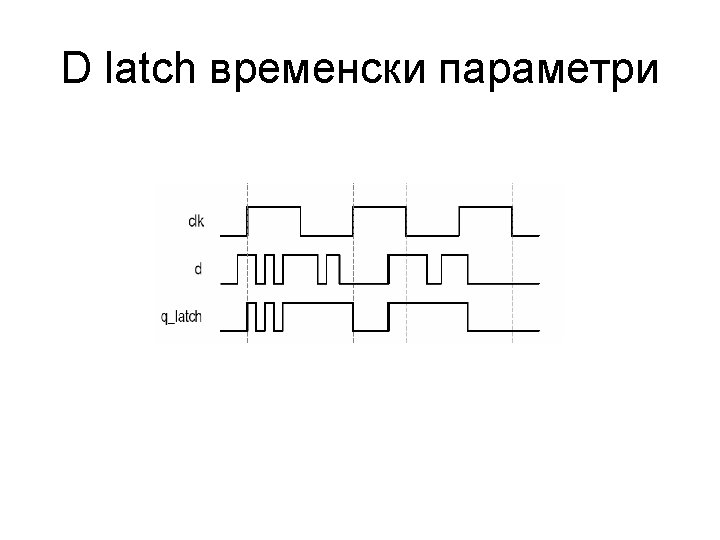

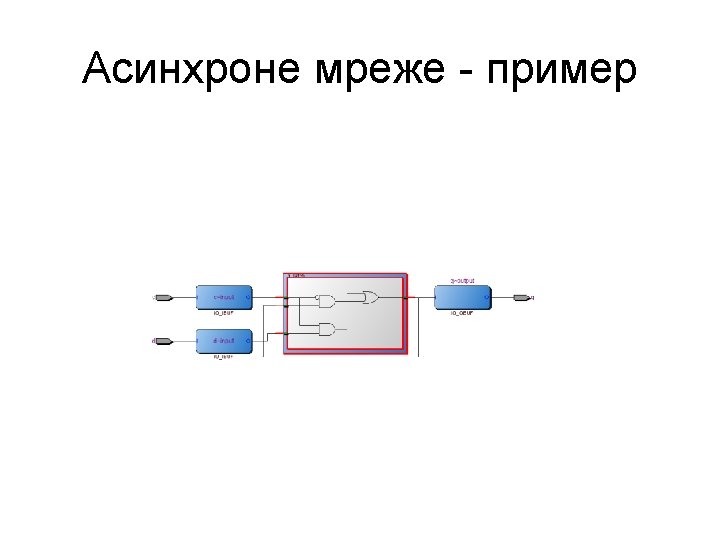

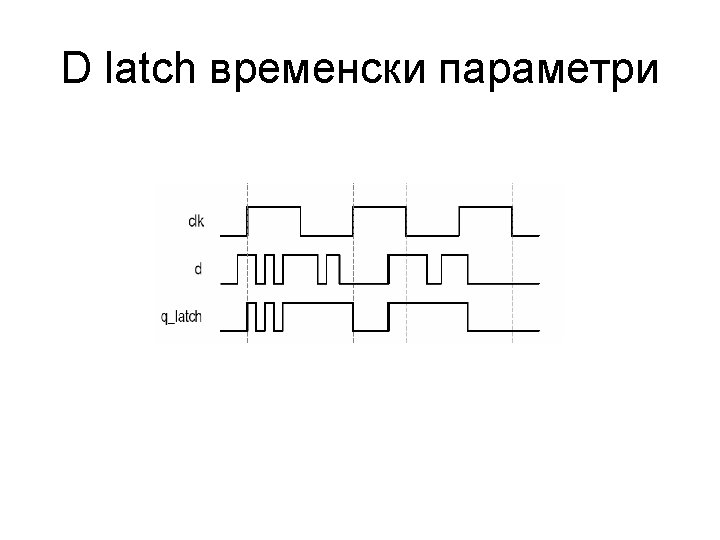

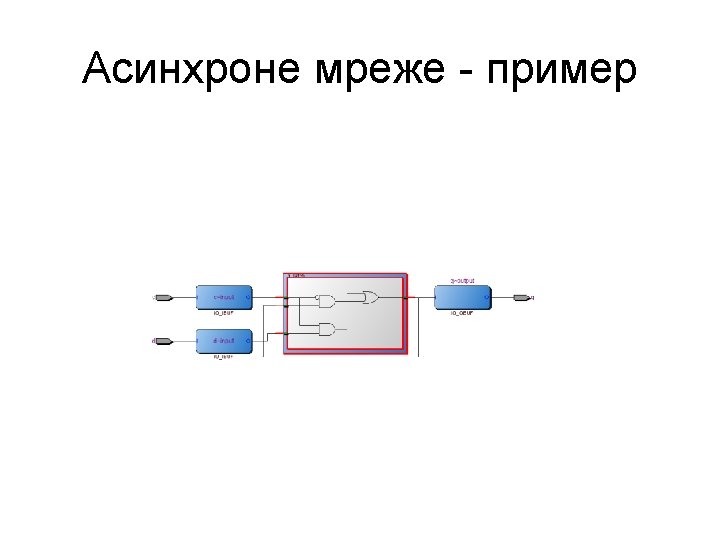

Асинхроне мреже - пример library ieee; use ieee. std_logic_1164. all; entity dlatch is port( c: in std_logic; d: in std_logic; q: out std_logic ); end dlatch;

Асинхроне мреже - пример architecture demo_arch of dlatch is signal q_latch: std_logic; begin process (c, d, q_latch) begin if (c = '1') then q_latch <= d; else q_latch <= q_latch; end if; end process; q <= q_latch; end demo_arch;

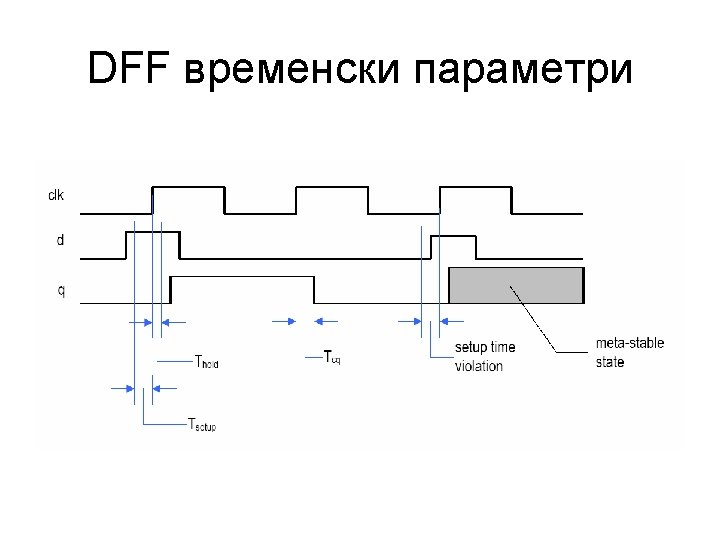

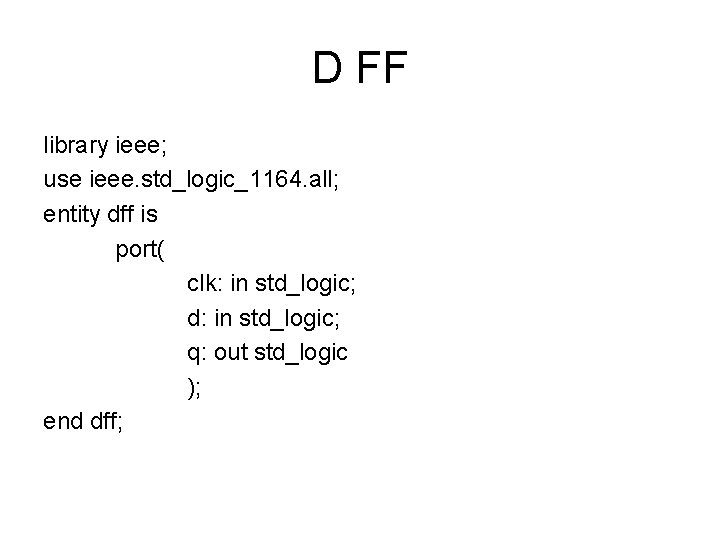

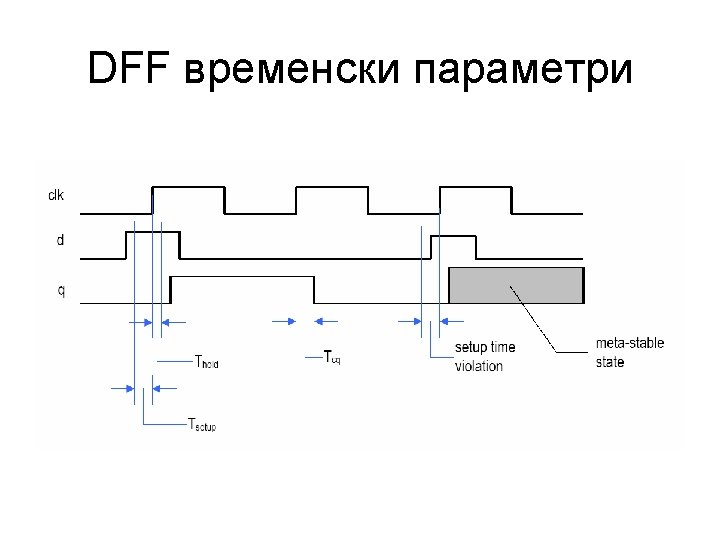

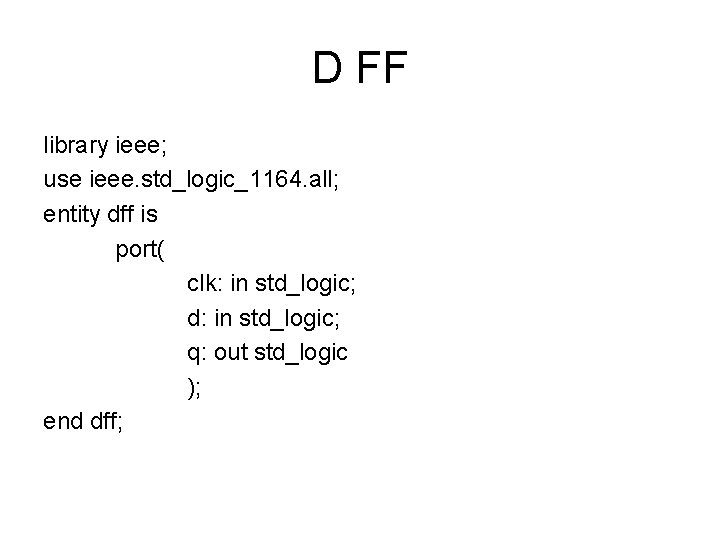

D FF library ieee; use ieee. std_logic_1164. all; entity dff is port( clk: in std_logic; d: in std_logic; q: out std_logic ); end dff;

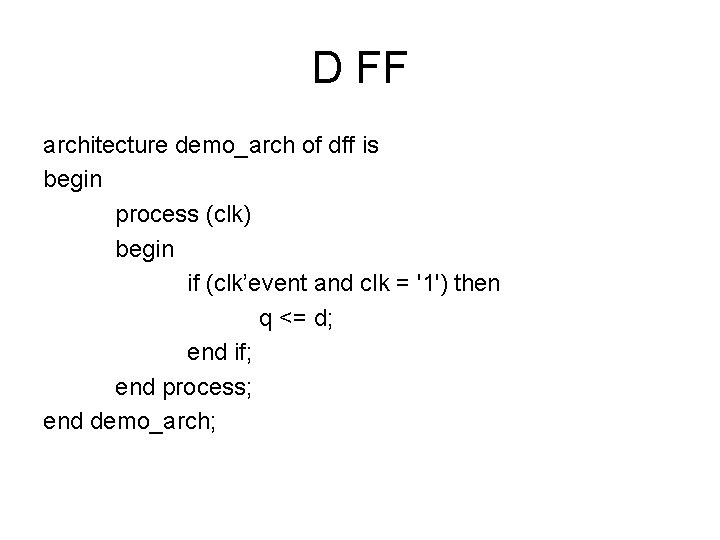

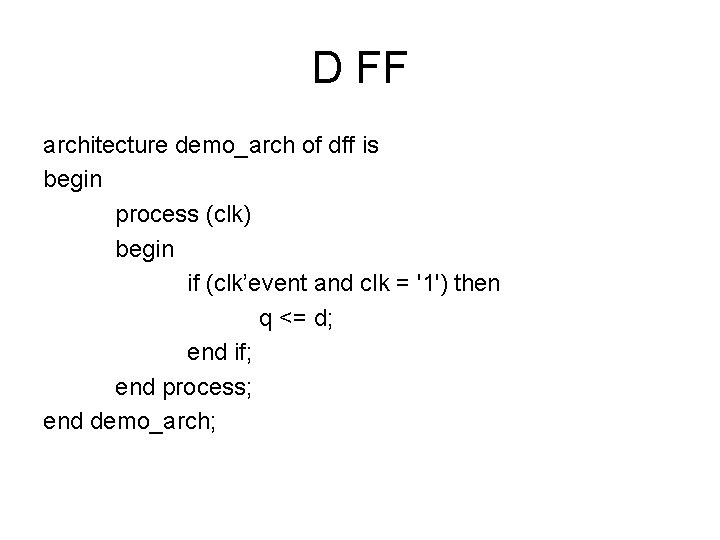

D FF architecture demo_arch of dff is begin process (clk) begin if (clk’event and clk = '1') then q <= d; end if; end process; end demo_arch;

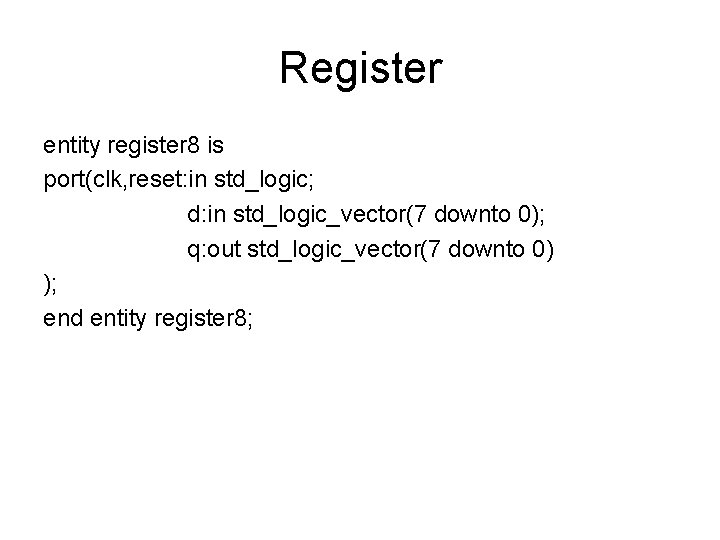

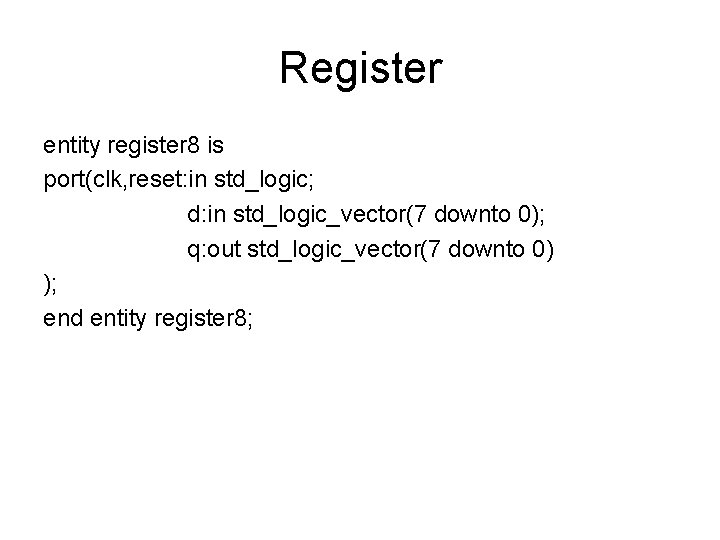

Register entity register 8 is port(clk, reset: in std_logic; d: in std_logic_vector(7 downto 0); q: out std_logic_vector(7 downto 0) ); end entity register 8;

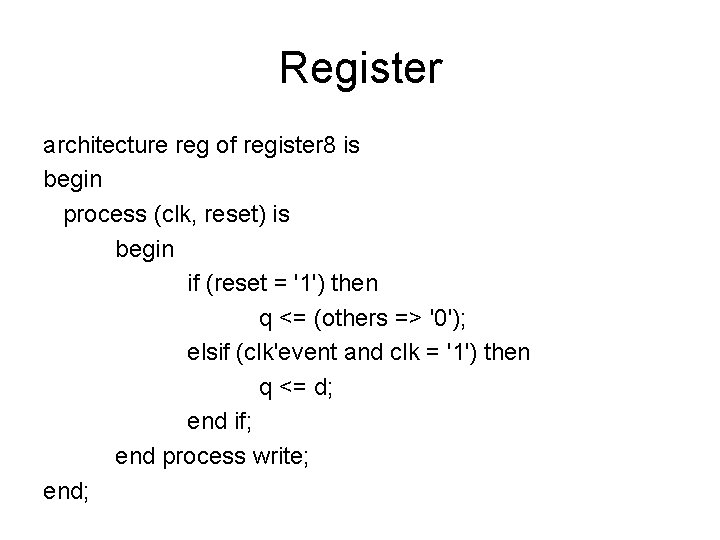

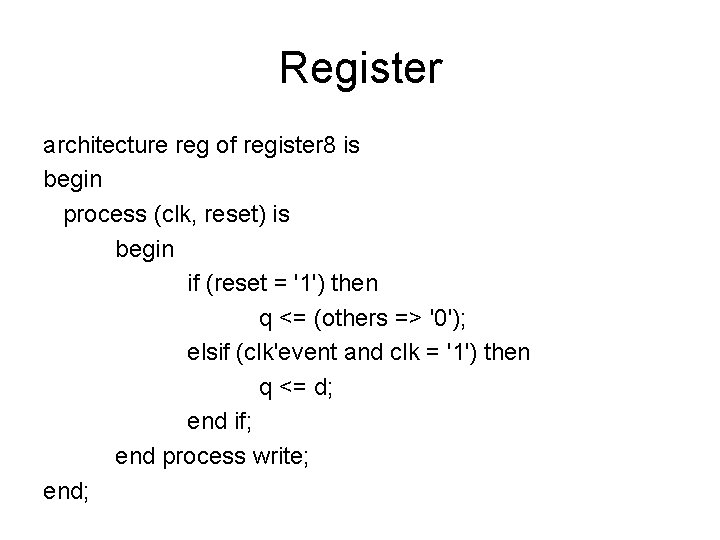

Register architecture reg of register 8 is begin process (clk, reset) is begin if (reset = '1') then q <= (others => '0'); elsif (clk'event and clk = '1') then q <= d; end if; end process write; end;

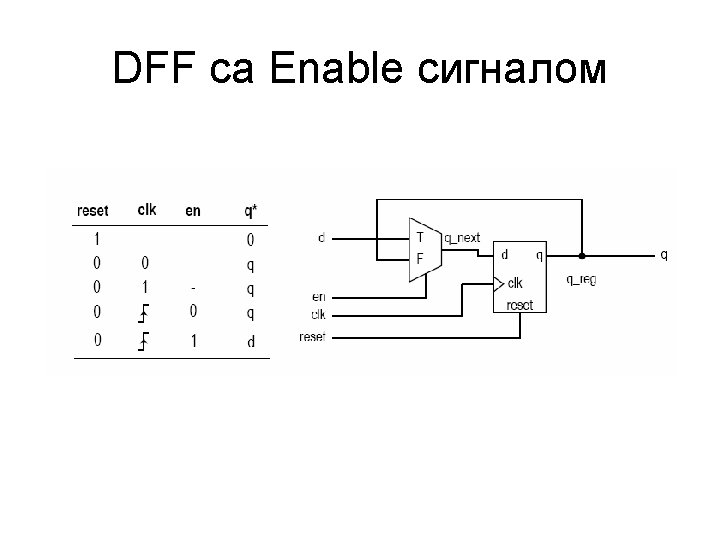

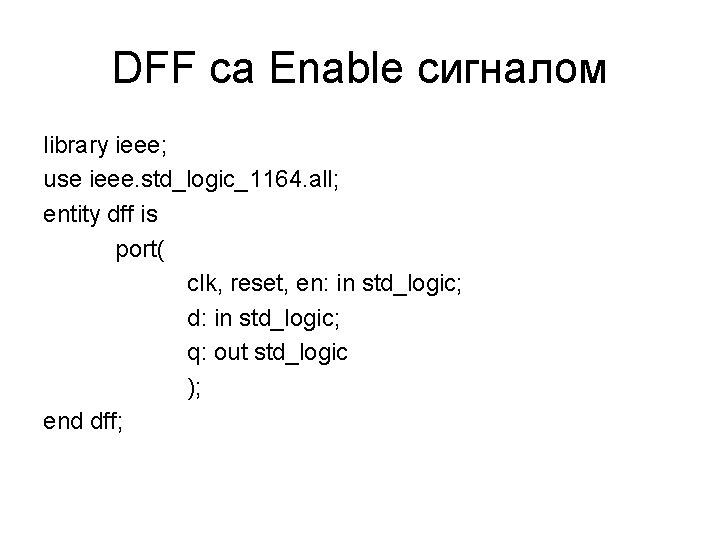

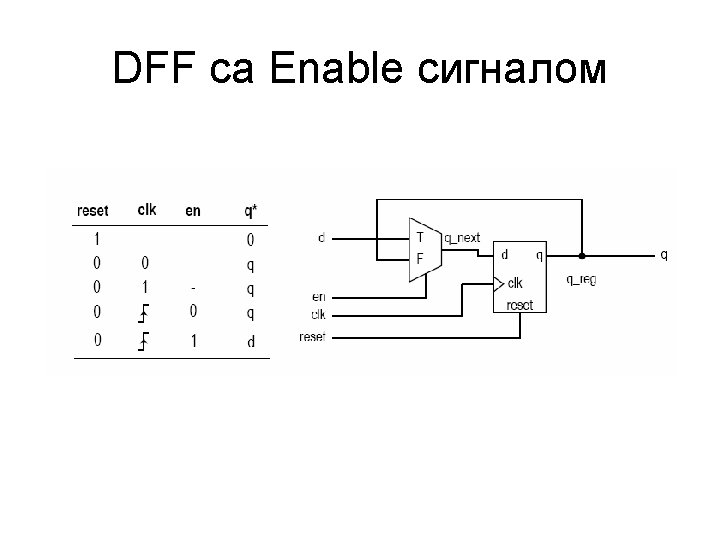

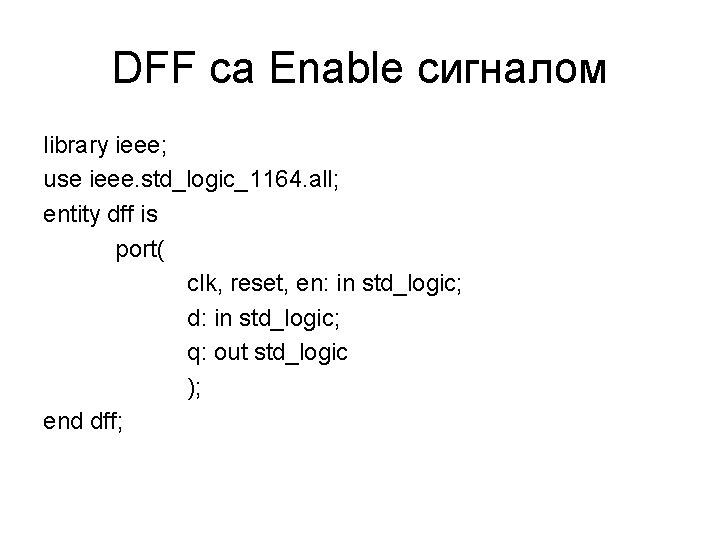

DFF са Enable сигналом library ieee; use ieee. std_logic_1164. all; entity dff is port( clk, reset, en: in std_logic; d: in std_logic; q: out std_logic ); end dff;

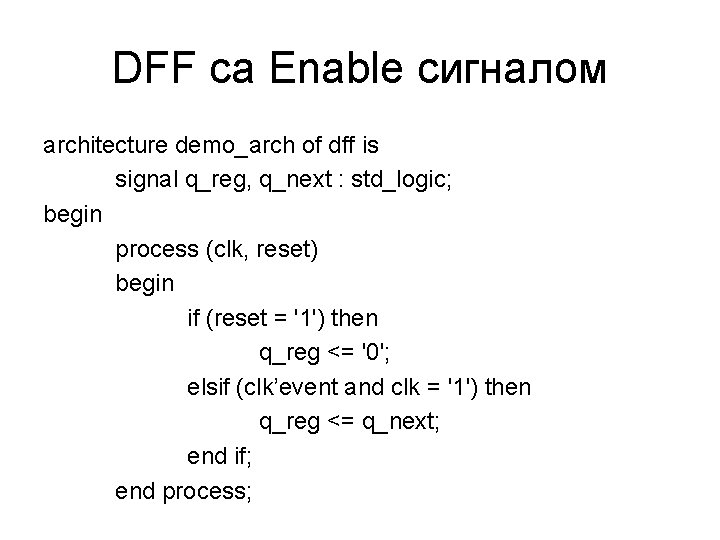

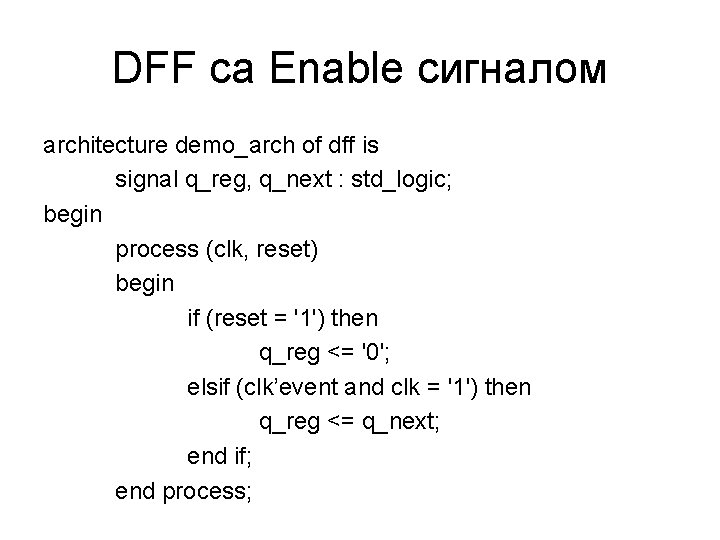

DFF са Enable сигналом architecture demo_arch of dff is signal q_reg, q_next : std_logic; begin process (clk, reset) begin if (reset = '1') then q_reg <= '0'; elsif (clk’event and clk = '1') then q_reg <= q_next; end if; end process;

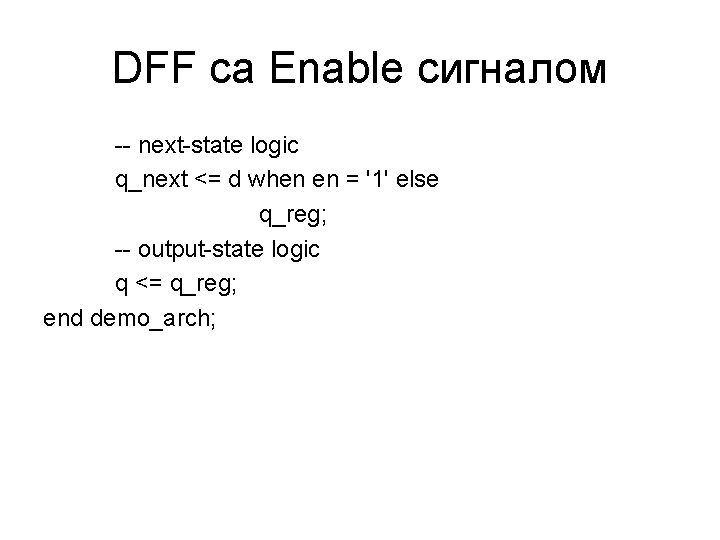

DFF са Enable сигналом -- next-state logic q_next <= d when en = '1' else q_reg; -- output-state logic q <= q_reg; end demo_arch;

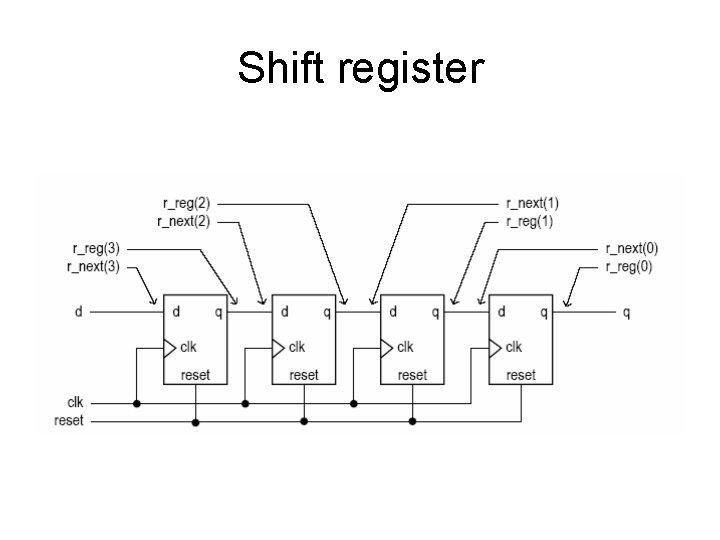

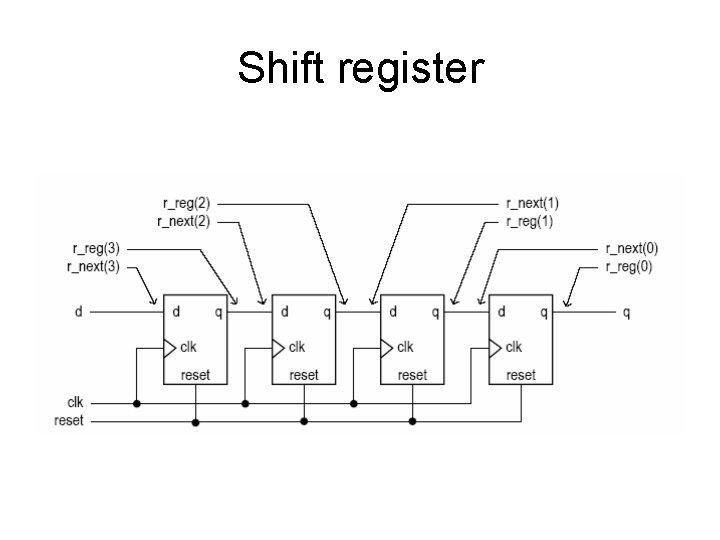

Shift register

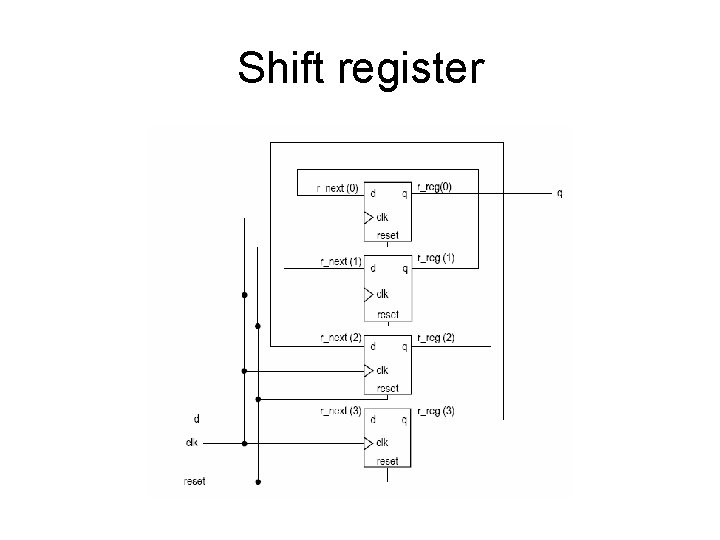

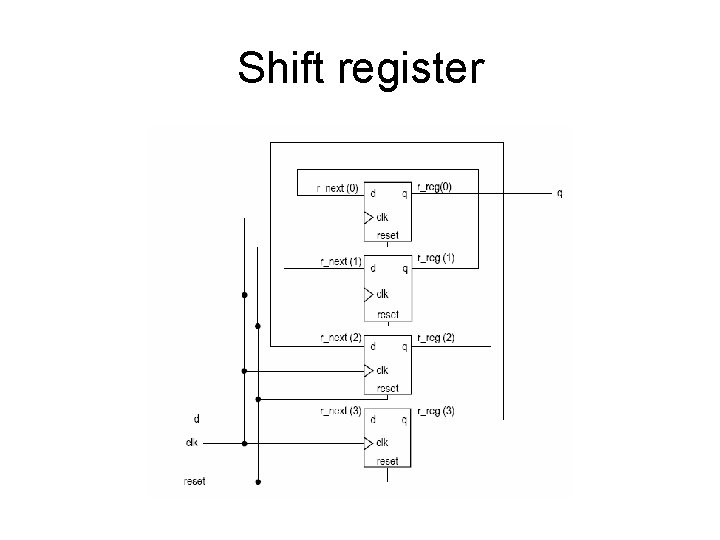

Shift register

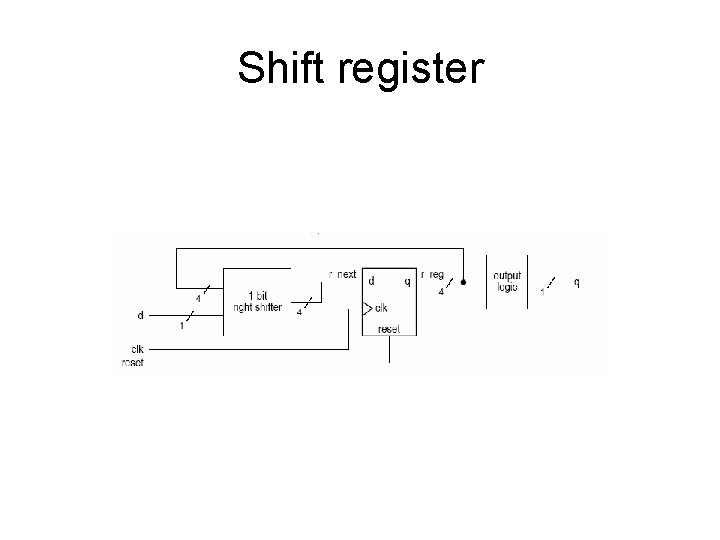

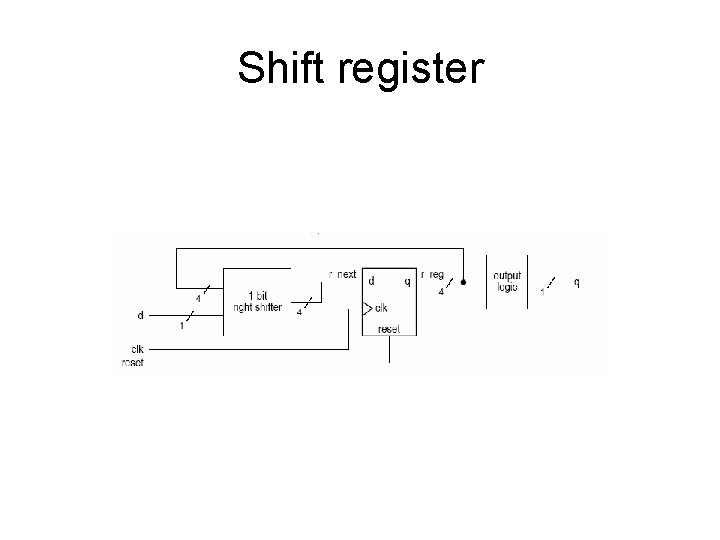

Shift register

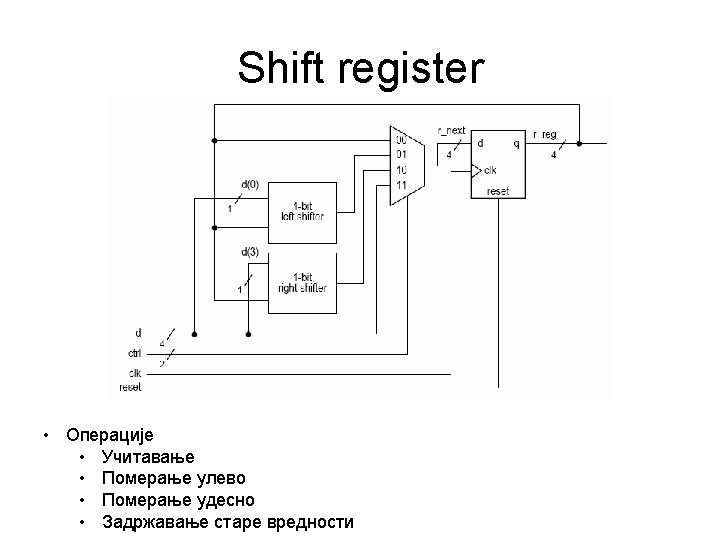

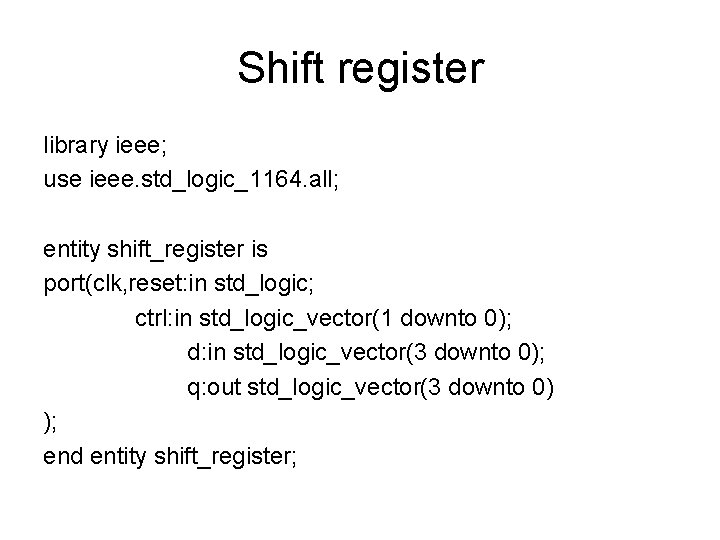

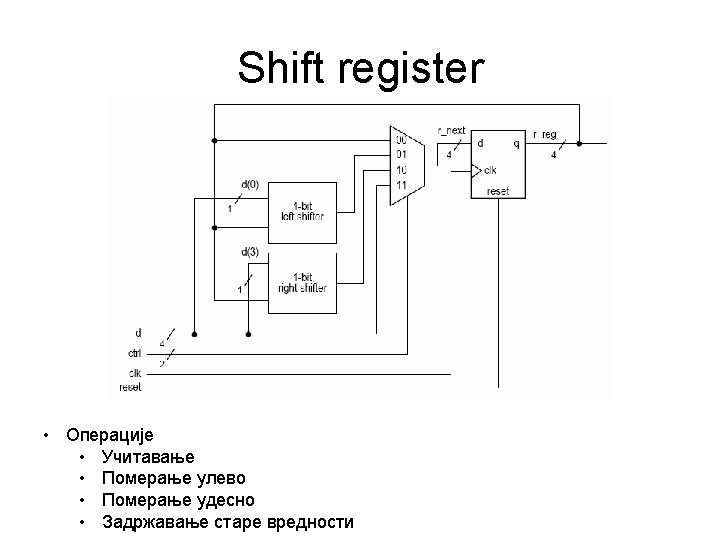

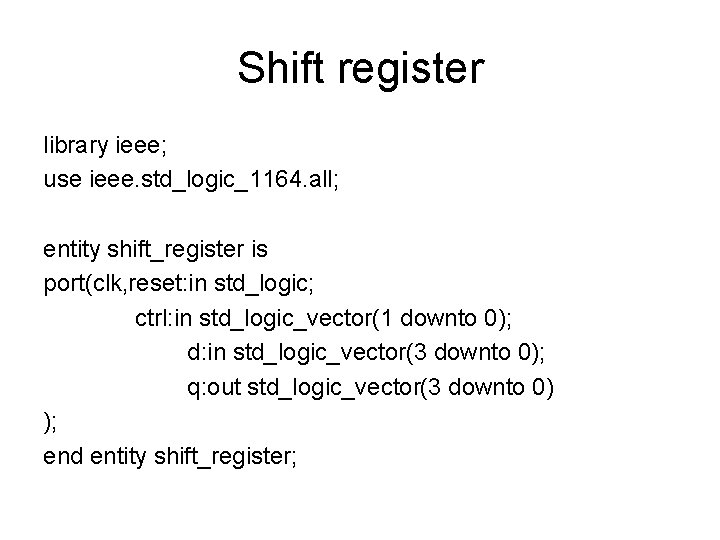

Shift register library ieee; use ieee. std_logic_1164. all; entity shift_register is port(clk, reset: in std_logic; ctrl: in std_logic_vector(1 downto 0); d: in std_logic_vector(3 downto 0); q: out std_logic_vector(3 downto 0) ); end entity shift_register;

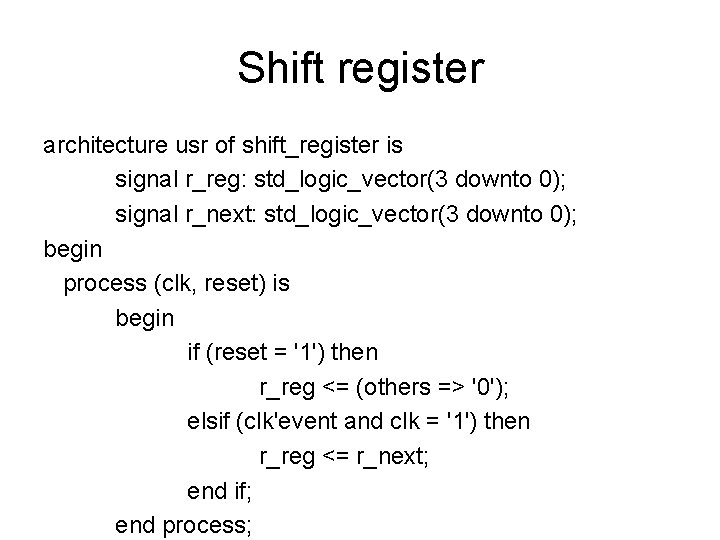

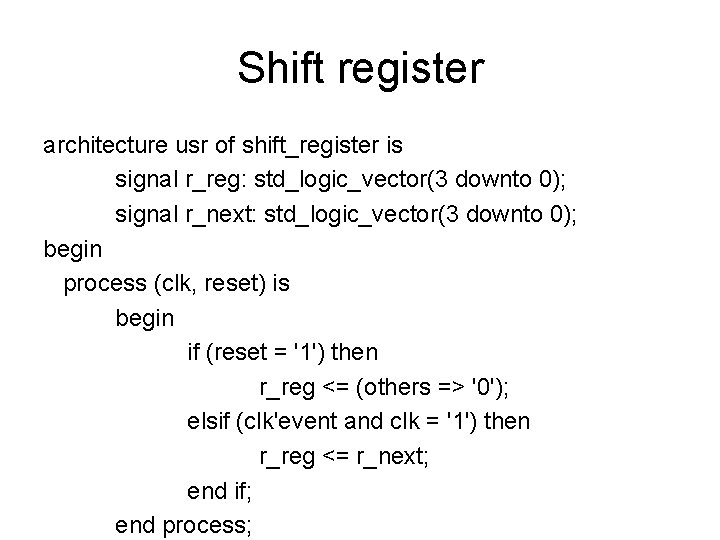

Shift register architecture usr of shift_register is signal r_reg: std_logic_vector(3 downto 0); signal r_next: std_logic_vector(3 downto 0); begin process (clk, reset) is begin if (reset = '1') then r_reg <= (others => '0'); elsif (clk'event and clk = '1') then r_reg <= r_next; end if; end process;

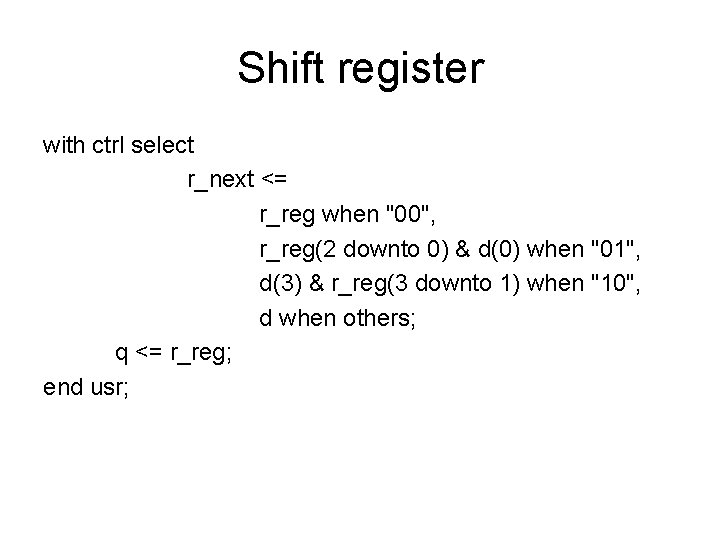

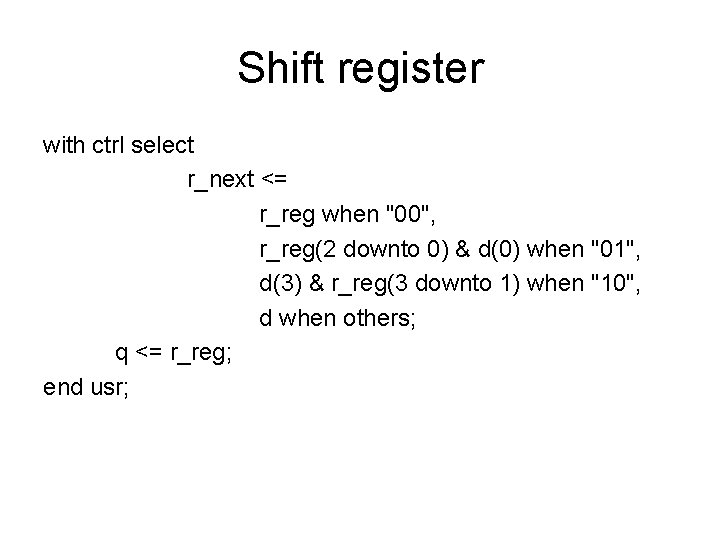

Shift register with ctrl select r_next <= r_reg when "00", r_reg(2 downto 0) & d(0) when "01", d(3) & r_reg(3 downto 1) when "10", d when others; q <= r_reg; end usr;

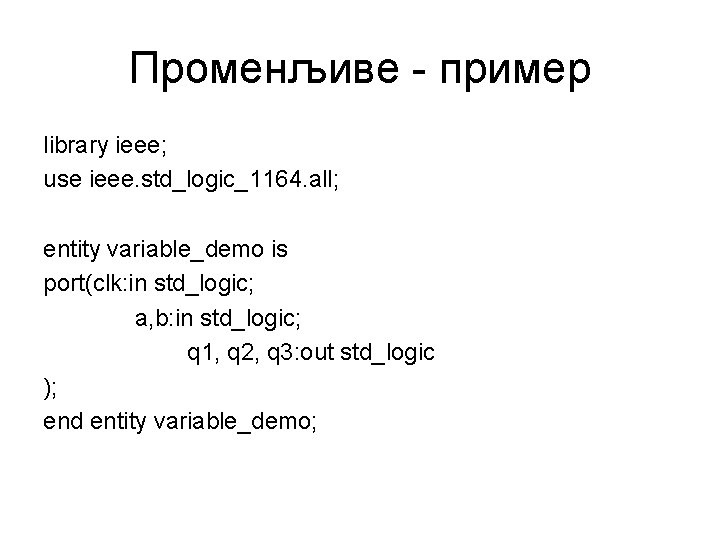

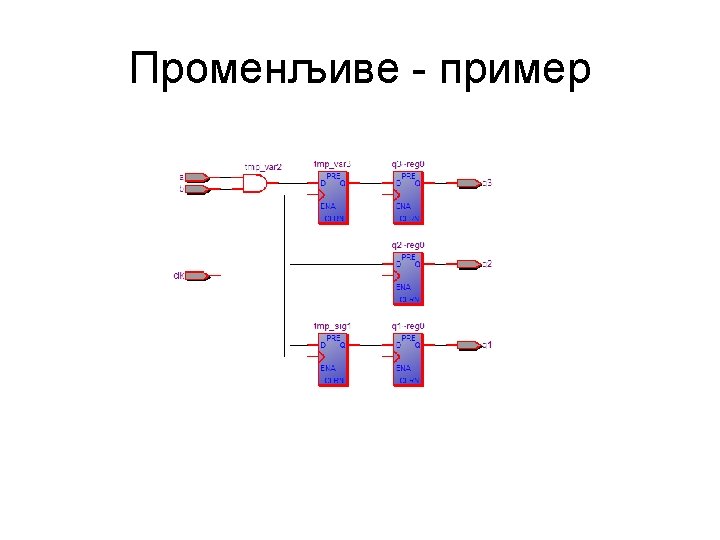

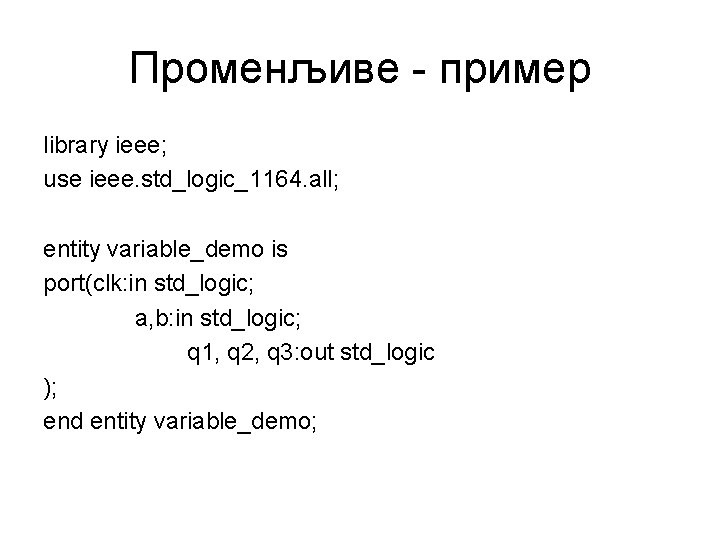

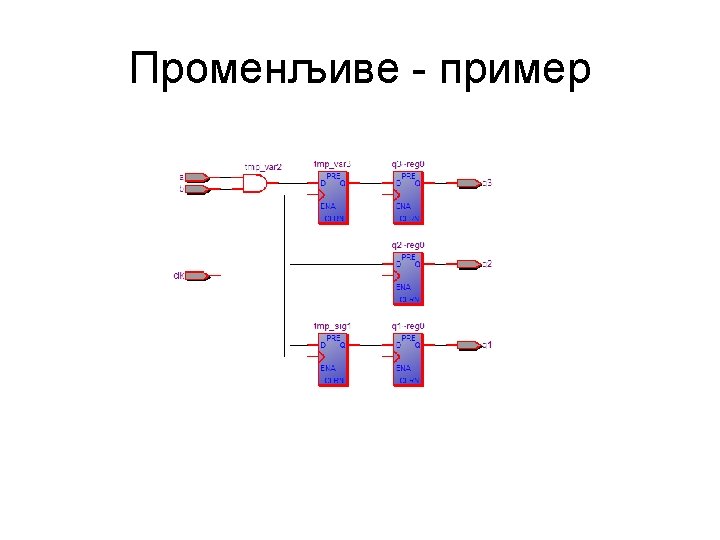

Променљиве - пример library ieee; use ieee. std_logic_1164. all; entity variable_demo is port(clk: in std_logic; a, b: in std_logic; q 1, q 2, q 3: out std_logic ); end entity variable_demo;

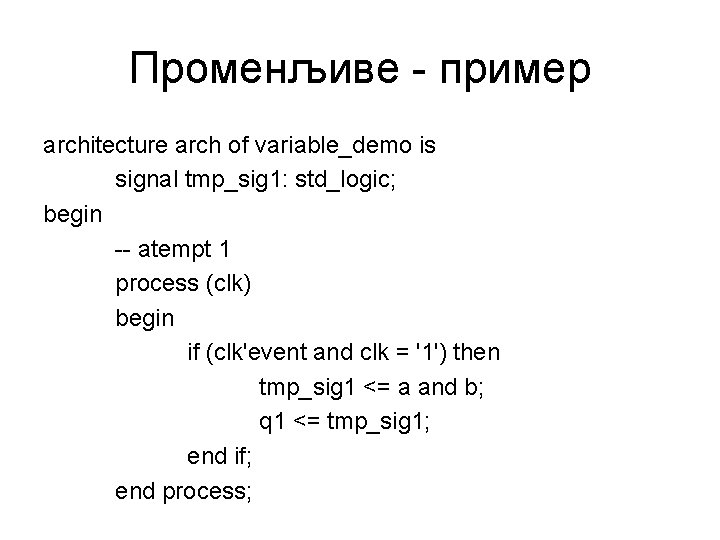

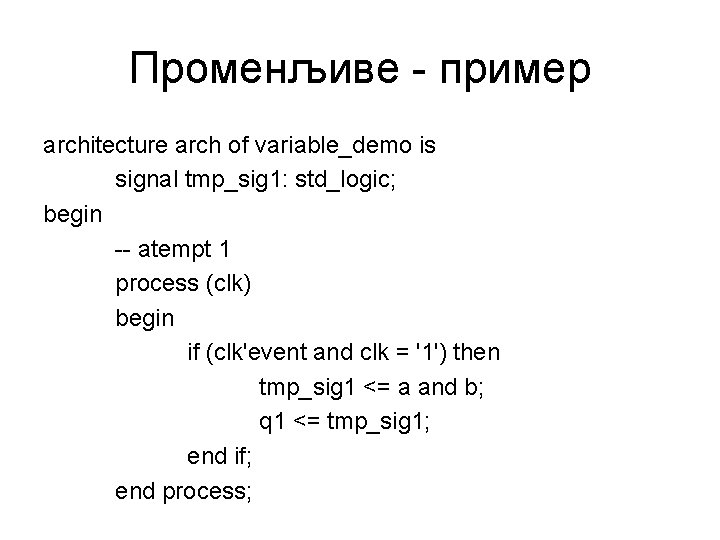

Променљиве - пример architecture arch of variable_demo is signal tmp_sig 1: std_logic; begin -- atempt 1 process (clk) begin if (clk'event and clk = '1') then tmp_sig 1 <= a and b; q 1 <= tmp_sig 1; end if; end process;

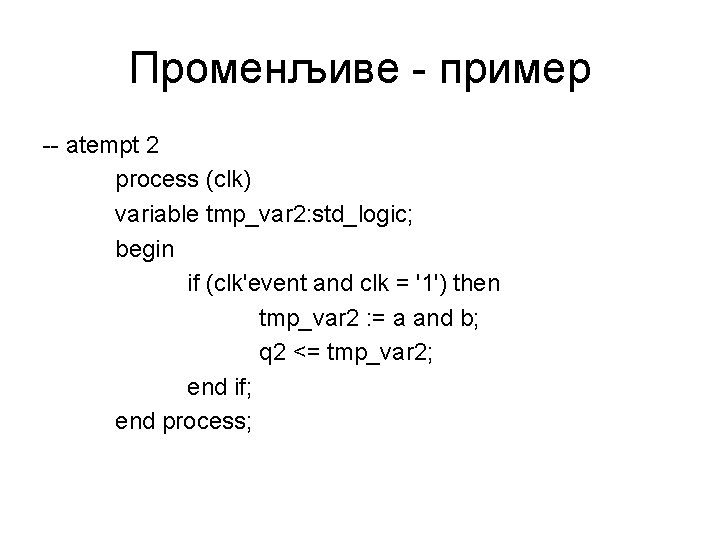

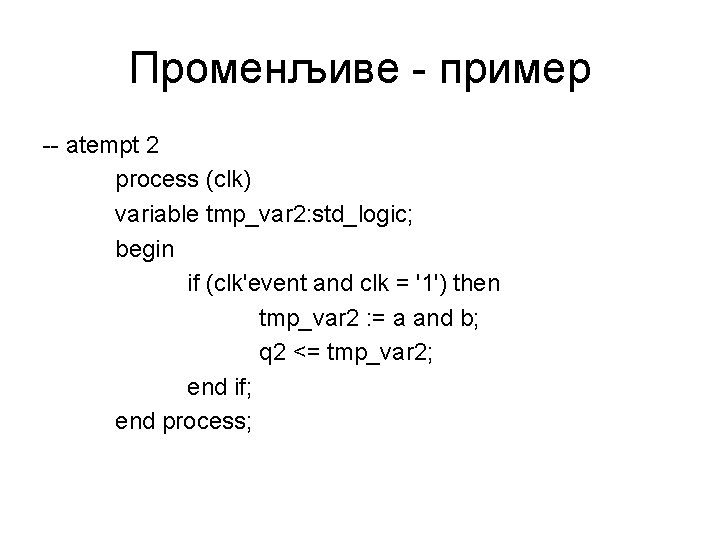

Променљиве - пример -- atempt 2 process (clk) variable tmp_var 2: std_logic; begin if (clk'event and clk = '1') then tmp_var 2 : = a and b; q 2 <= tmp_var 2; end if; end process;

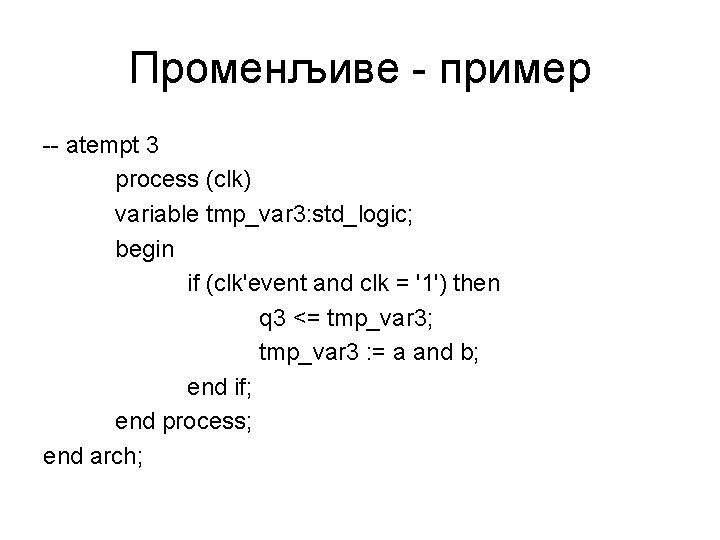

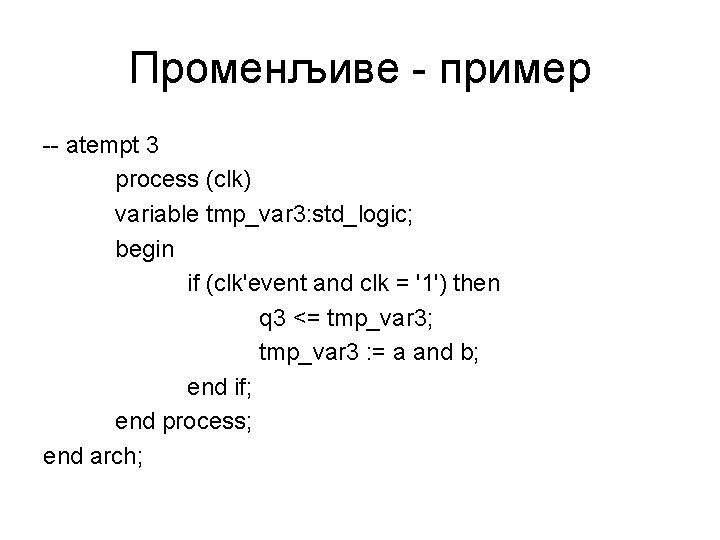

Променљиве - пример -- atempt 3 process (clk) variable tmp_var 3: std_logic; begin if (clk'event and clk = '1') then q 3 <= tmp_var 3; tmp_var 3 : = a and b; end if; end process; end arch;

Dataflow

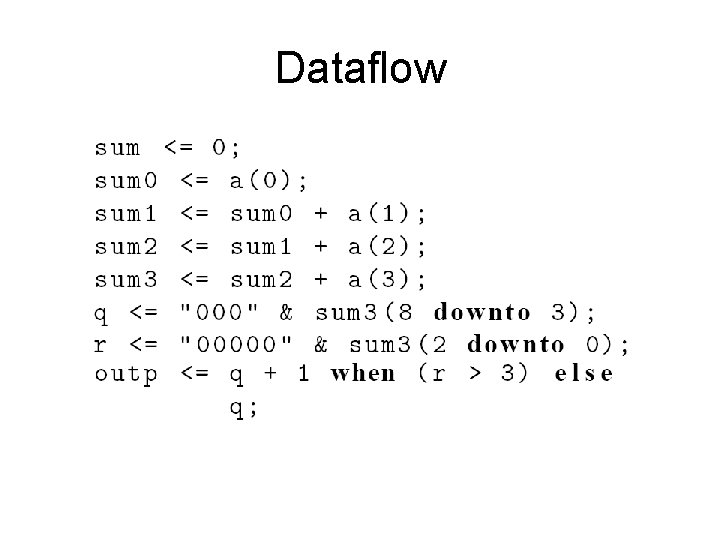

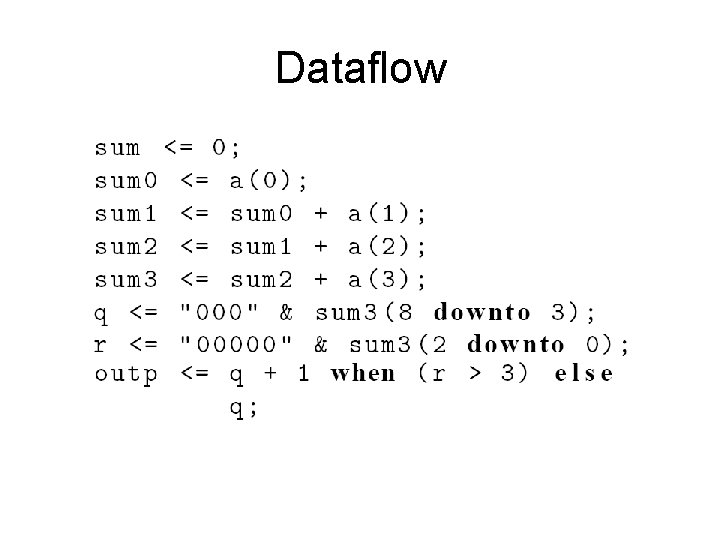

Dataflow

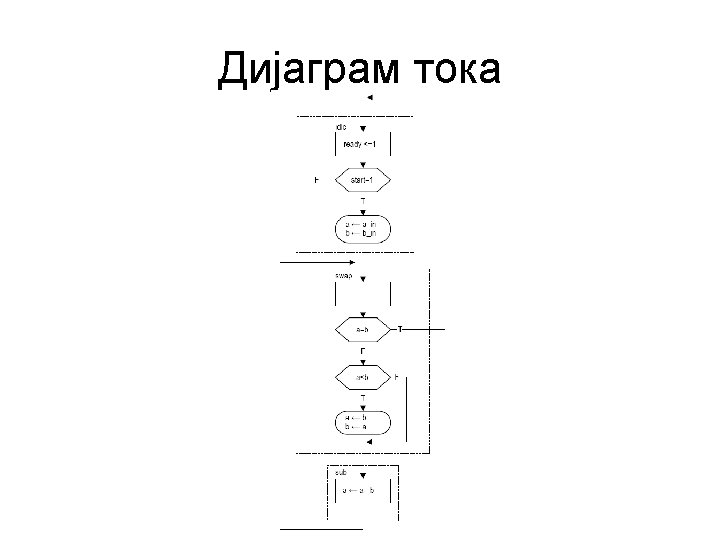

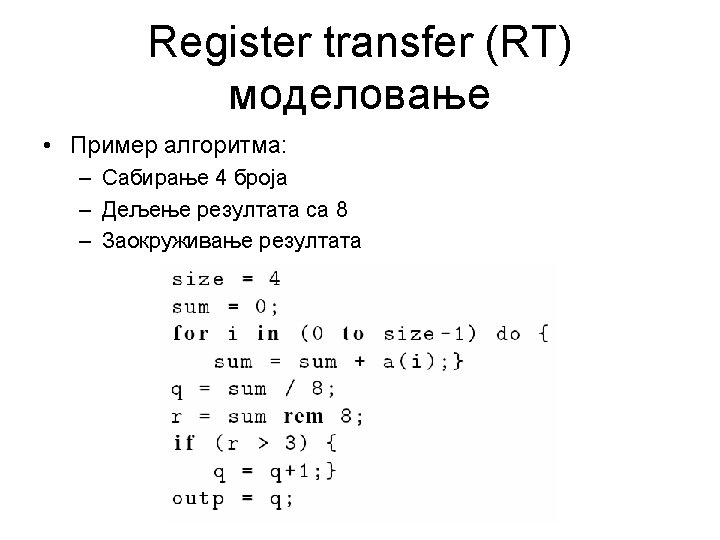

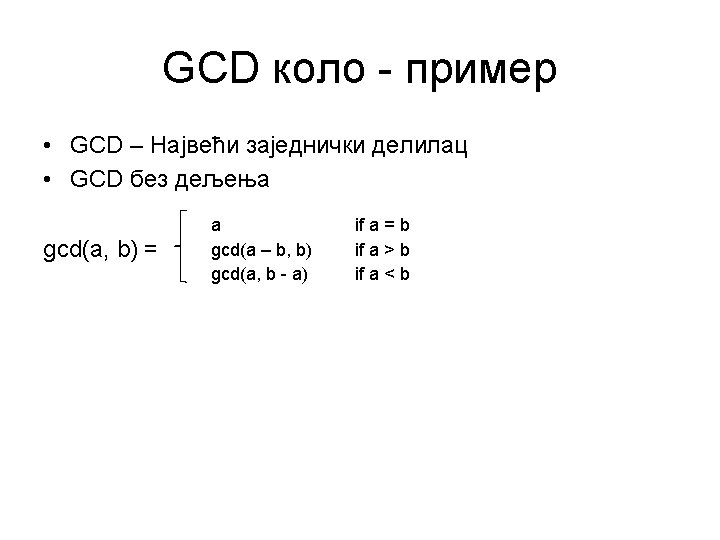

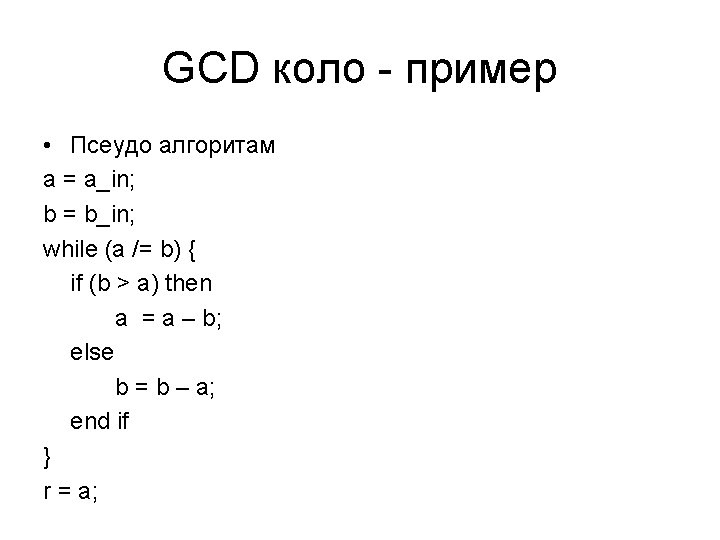

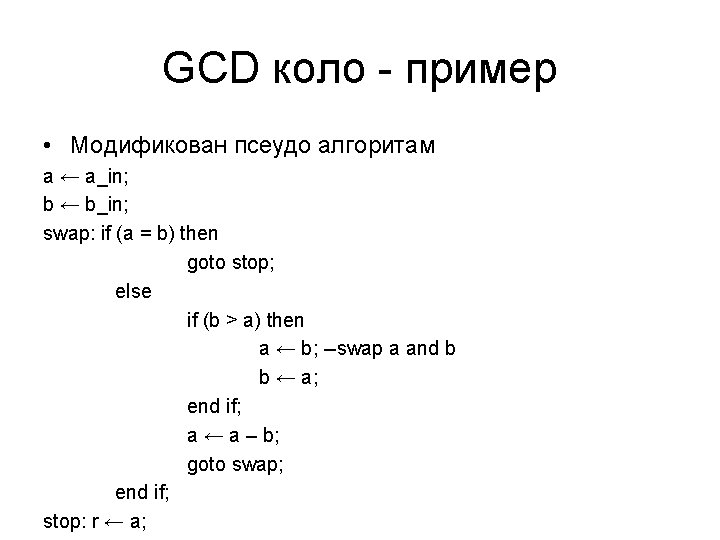

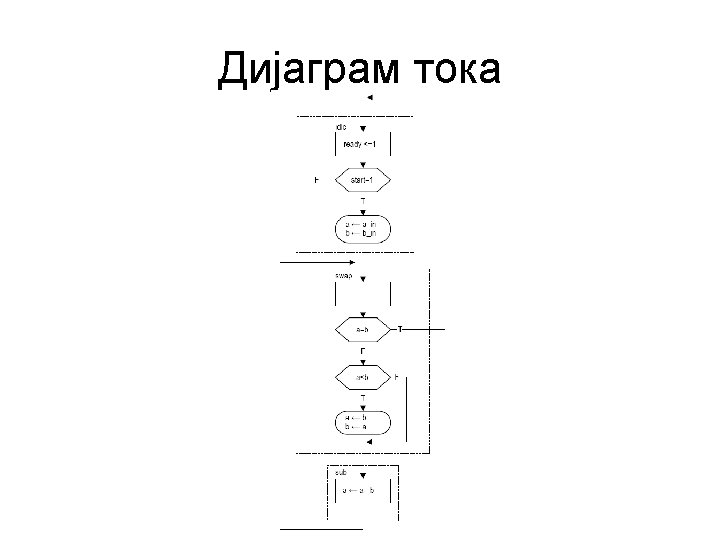

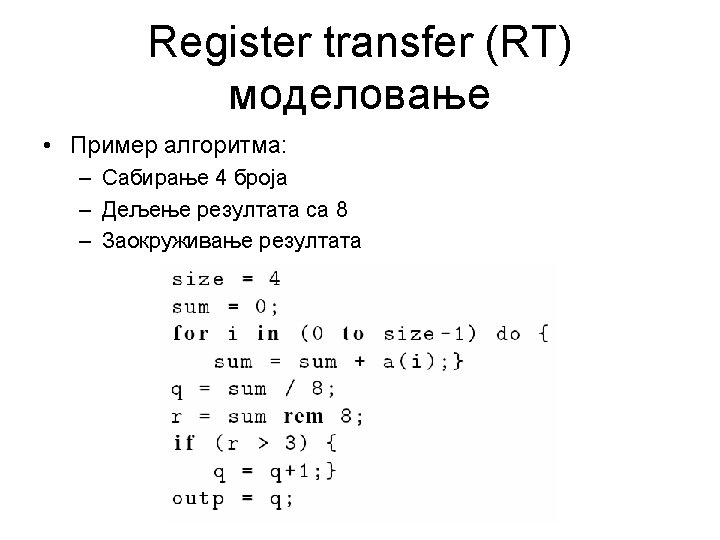

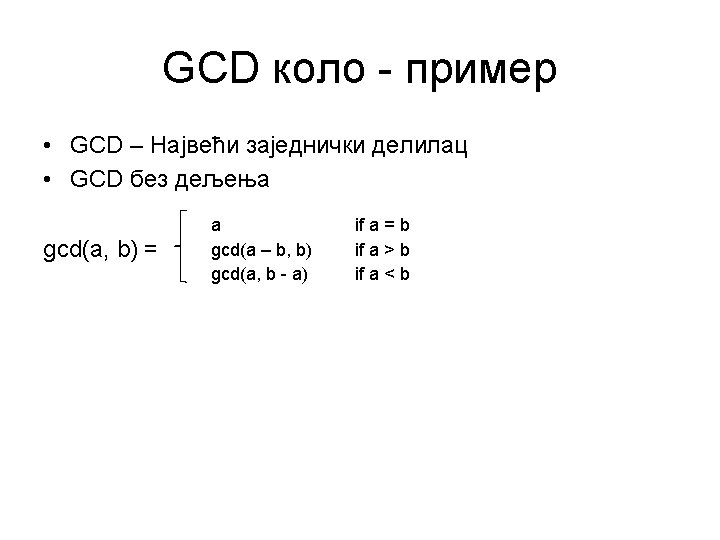

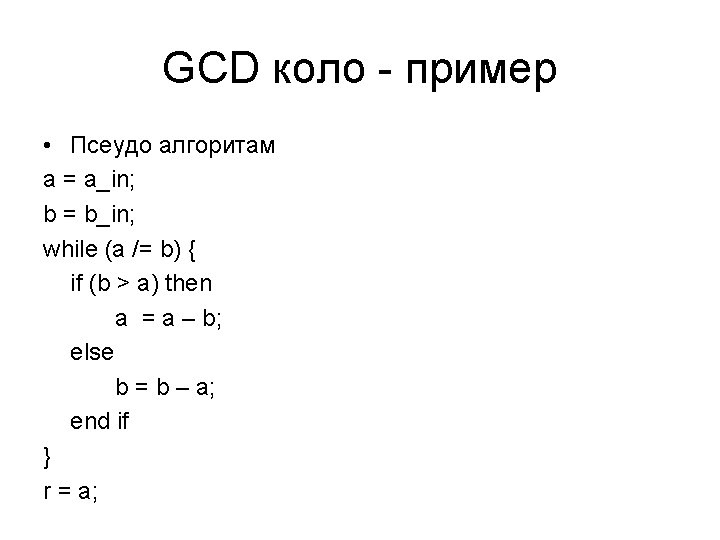

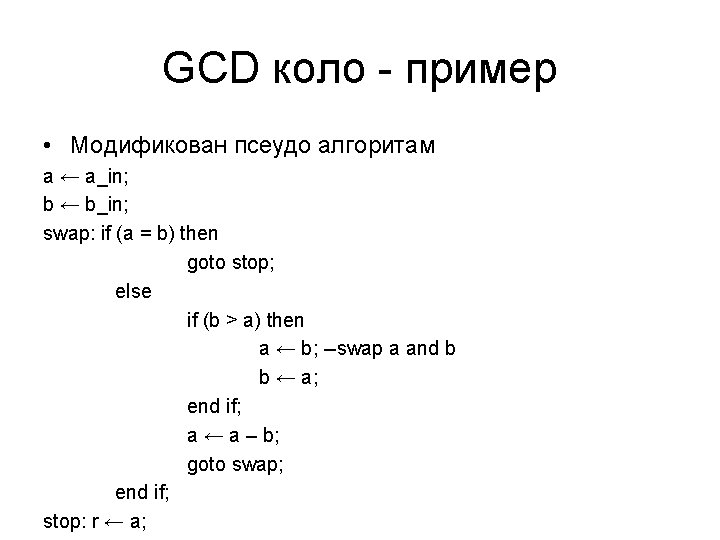

GCD коло - пример • Модификован псеудо алгоритам a ← a_in; b ← b_in; swap: if (a = b) then goto stop; else if (b > a) then a ← b; --swap a and b b ← a; end if; a ← a – b; goto swap; end if; stop: r ← a;