CISC RISC and PostRISC Computers CE 140 A

![CISC versus RISC o Example: n CISC: o n MULT [ADDR 1], [ADDR 2] CISC versus RISC o Example: n CISC: o n MULT [ADDR 1], [ADDR 2]](https://slidetodoc.com/presentation_image_h2/0cdbb1427e0e7cb652435d4794a86135/image-22.jpg)

- Slides: 28

CISC, RISC, and Post-RISC Computers CE 140 A 1/A 2 4 July 2003

Required Reading o RISC vs. CISC: the Post-RISC Era n John “Hannibal” Stokes http: //www. arstechnica. com/cpu/4 q 99/risc-cisc/rvc-1. html

Review: Basic Performance Equation o T = (N x S) / R n n T – program execution time N – number of instructions S – average steps per instruction R – clock rate

Technological Conditions (Late 70’s to Early 80’s) o Storage and memory n o Compilers n o Generally, expensive and slow Long compilation time, unoptimized output VLSI n “low” transistor densities

Solution o Storage and memory n o Compilers n n o More compact code Make HLL ASM translation simpler Code in assembly for optimized program VLSI n Reduce number of required transistors. How?

“Software crisis” o o Hardware costs were falling Software development costs were rising

Solution o o Shift complexity from software to hardware Bridge “semantic gap” between machine capabilities and high-level languages

Complex Instruction Set Computer o o Late 1970 s: experimentation with complex instructions made possible by interpreter (microprogrammed control) CISC generally required use of microprogrammed control

CISC o o Increased use of complex, multistep instructions Lower N, higher S Made the addition of new features to old microprocessors easy Example: 8086 (1978) Pentium (1993) by Intel

CISC o o Complex instructions More steps Larger and more expensive ICs Sometimes lead to reduced performance Less instructions per program less code

CISC o o Powerful instructions More direct implementation of high-level language operations Allows more complex addressing modes

CISC Issues o o o Larger instruction set larger control stores larger microprograms Larger microprograms slower and difficult to test “Semantic gap” “Semantic clash”

CISC Issues o o 80/20 rule – 80% of the instructions use only 20% of the instruction set Need to maintain backward compatibility increased development cost

Reduced Instruction Set Computer o o Reduced Instruction Set Computer Mid-1970 s – John Cocke – IBM 801 1980: Patterson and Séquin – RISC processor SPARC 1981: Hennessy – MIPS processor

Technological Conditions o o Cheaper memory Better compilers

RISC o o “Make the common case fast” Speed up 20% of instruction set n n o o o Simpler instructions Simpler addressing modes Increased performance Higher N, lower S Complexity is moved from hardware to software

RISC o “Even if a RISC machine takes four or five instructions to do what a CISC machine does in one instruction, if the RISC instructions are 10 times as fast, RISC wins”

RISC o o Well-suited to pipelined execution, parallelism Can be used effectively by optimizing compilers Hardwired control faster direct execution Simpler hardware Smaller chip area more space for registers and cache

RISC and Compilers o o Compilers play a more prominent role Need for intelligent, optimizing compilers

RISC Design Principles o All instructions are directly executed by hardware n o o Hardwired Control Maximize the rate at which instructions are issued Instructions should be easy to decode n Regular, fixed-length instructions

RISC Design Principles o o Only Loads and Stores should reference memory Provide plenty of registers

![CISC versus RISC o Example n CISC o n MULT ADDR 1 ADDR 2 CISC versus RISC o Example: n CISC: o n MULT [ADDR 1], [ADDR 2]](https://slidetodoc.com/presentation_image_h2/0cdbb1427e0e7cb652435d4794a86135/image-22.jpg)

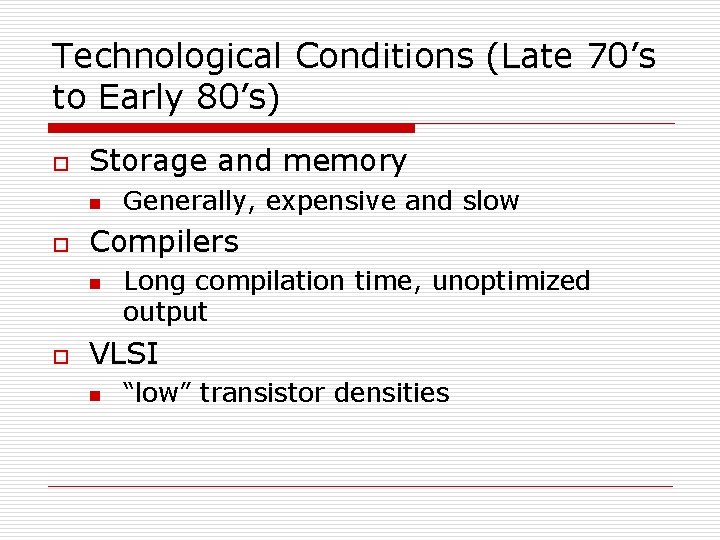

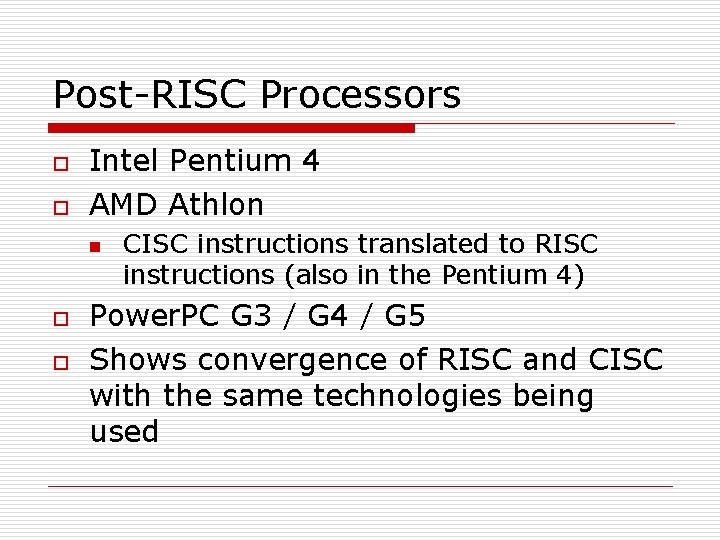

CISC versus RISC o Example: n CISC: o n MULT [ADDR 1], [ADDR 2] RISC o o LOAD A, [ADDR 1] LOAD B, [ADDR 2] MULT A, B STORE [ADDR 1], A

“Why aren’t RISC machines as popular as CISC machines? ” o o o Not a totally valid question Big investment in software for Intelbased machines (primarily CISC) Compatibility Intel-based machines now have a RISC core Common instructions Faster Uncommon instructions Slower

CISC and RISC o o o Now the term RISC refers to any computer with an ISA and CPU organization that is designed for high performance Size of instruction set is now considered relatively unimportant Focus on fast instructions, not number of instructions

The Post-RISC Era o Current Technological Conditions n n n Cheap and fast memory Better compiler features Increased transistor count

The Post-RISC Era o Performance improvements n n n Superscalar execution Branch prediction Hardware Out-of-order execution (OOO) SIMD and FP units Additional fast, simple instructions Software OOO

Post-RISC Processors o o Intel Pentium 4 AMD Athlon n o o CISC instructions translated to RISC instructions (also in the Pentium 4) Power. PC G 3 / G 4 / G 5 Shows convergence of RISC and CISC with the same technologies being used

Post-RISC Era o o o Line between CISC and RISC processors are blurred Different problems and technological conditions different solution, not strictly CISC or RISC Each computer must be evaluated not just on the basis of being CISC or RISC, but as a whole, including hardware and software