INSTRUCTIONAL RISC CISC PIPELINE ARCHITECTURE Kelompok 2 ARSITEKTUR

- Slides: 21

INSTRUCTIONAL, RISC, CISC, &PIPELINE ARCHITECTURE Kelompok 2

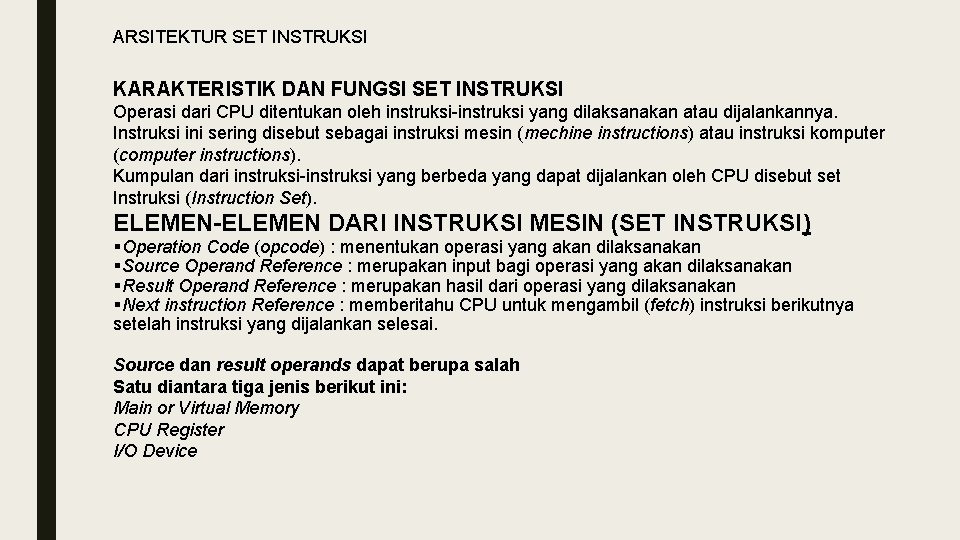

ARSITEKTUR SET INSTRUKSI KARAKTERISTIK DAN FUNGSI SET INSTRUKSI Operasi dari CPU ditentukan oleh instruksi-instruksi yang dilaksanakan atau dijalankannya. Instruksi ini sering disebut sebagai instruksi mesin (mechine instructions) atau instruksi komputer (computer instructions). Kumpulan dari instruksi-instruksi yang berbeda yang dapat dijalankan oleh CPU disebut set Instruksi (Instruction Set). ELEMEN-ELEMEN DARI INSTRUKSI MESIN (SET INSTRUKSI) §Operation Code (opcode) : menentukan operasi yang akan dilaksanakan §Source Operand Reference : merupakan input bagi operasi yang akan dilaksanakan §Result Operand Reference : merupakan hasil dari operasi yang dilaksanakan §Next instruction Reference : memberitahu CPU untuk mengambil (fetch) instruksi berikutnya setelah instruksi yang dijalankan selesai. Source dan result operands dapat berupa salah Satu diantara tiga jenis berikut ini: Main or Virtual Memory CPU Register I/O Device

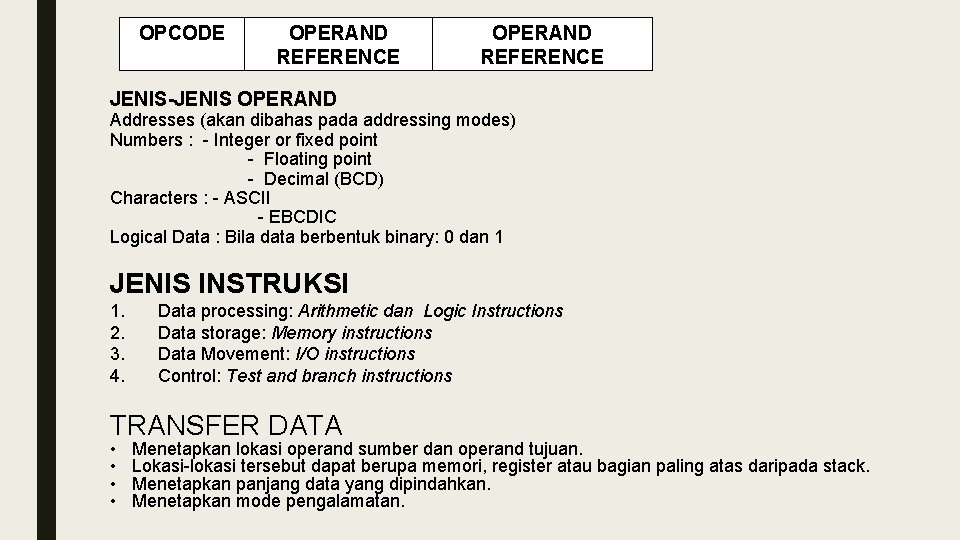

DESAIN SET INSTRUKSI Desain set instruksi merupakan masalah yang sangat komplek yang melibatkan banyak aspek, diantaranya adalah: 1. Kelengkapan set instruksi 2. Ortogonalitas (sifat independensi instruksi) 3. Kompatibilitas : - Source code compatibility - Object code Compatibility Selain ketiga aspek tersebut juga melibatkan hal-hal sebagai berikut: 1. Operation Repertoire: Berapa banyak dan operasi apa saja yang disediakan, dan berapa sulit operasinya 2. Data Types: tipe/jenis data yang dapat olah Instruction Format: panjangnya, banyaknya alamat, dsb. 3. Register: Banyaknya register yang dapat digunakan 4. Addressing: Mode pengalamatan untuk operand FORMAT INSTRUKSI Suatu instruksi terdiri dari beberapa field yang sesuai dengan elemen dalam instruksi tersebut. Layout dari suatu instruksi sering disebut sebagai Format Instruksi (Instruction Format).

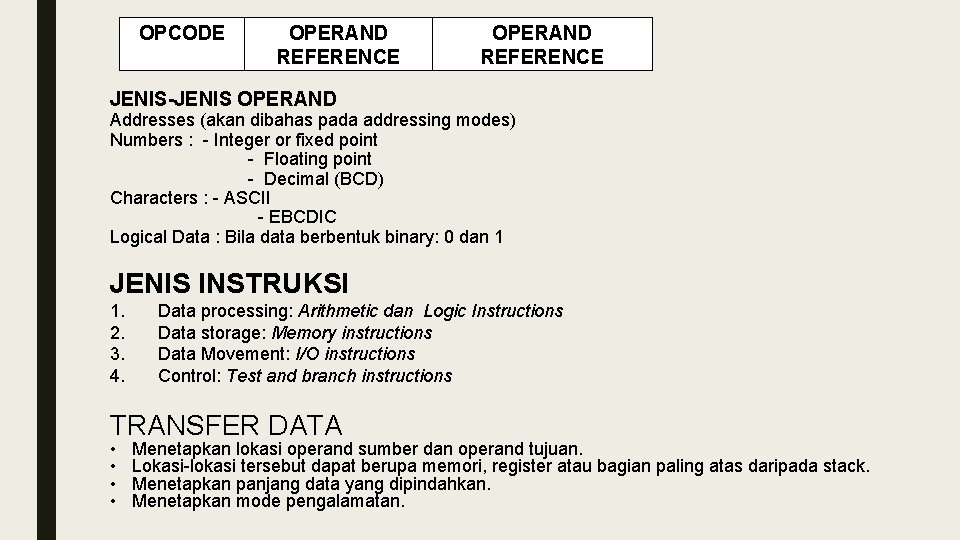

OPCODE OPERAND REFERENCE JENIS-JENIS OPERAND Addresses (akan dibahas pada addressing modes) Numbers : - Integer or fixed point - Floating point - Decimal (BCD) Characters : - ASCII - EBCDIC Logical Data : Bila data berbentuk binary: 0 dan 1 JENIS INSTRUKSI 1. 2. 3. 4. Data processing: Arithmetic dan Logic Instructions Data storage: Memory instructions Data Movement: I/O instructions Control: Test and branch instructions TRANSFER DATA • • Menetapkan lokasi operand sumber dan operand tujuan. Lokasi-lokasi tersebut dapat berupa memori, register atau bagian paling atas daripada stack. Menetapkan panjang data yang dipindahkan. Menetapkan mode pengalamatan.

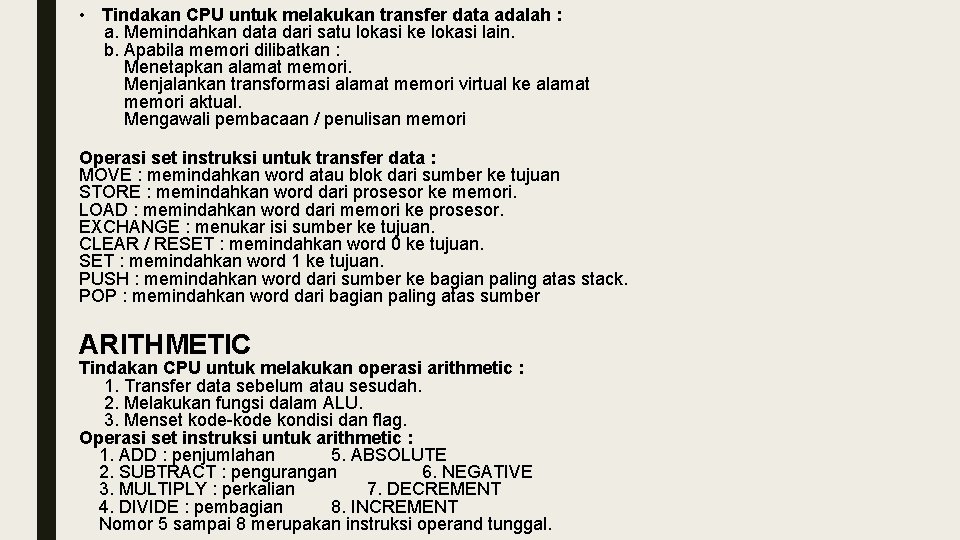

• Tindakan CPU untuk melakukan transfer data adalah : a. Memindahkan data dari satu lokasi ke lokasi lain. b. Apabila memori dilibatkan : Menetapkan alamat memori. Menjalankan transformasi alamat memori virtual ke alamat memori aktual. Mengawali pembacaan / penulisan memori Operasi set instruksi untuk transfer data : MOVE : memindahkan word atau blok dari sumber ke tujuan STORE : memindahkan word dari prosesor ke memori. LOAD : memindahkan word dari memori ke prosesor. EXCHANGE : menukar isi sumber ke tujuan. CLEAR / RESET : memindahkan word 0 ke tujuan. SET : memindahkan word 1 ke tujuan. PUSH : memindahkan word dari sumber ke bagian paling atas stack. POP : memindahkan word dari bagian paling atas sumber ARITHMETIC Tindakan CPU untuk melakukan operasi arithmetic : 1. Transfer data sebelum atau sesudah. 2. Melakukan fungsi dalam ALU. 3. Menset kode-kode kondisi dan flag. Operasi set instruksi untuk arithmetic : 1. ADD : penjumlahan 5. ABSOLUTE 2. SUBTRACT : pengurangan 6. NEGATIVE 3. MULTIPLY : perkalian 7. DECREMENT 4. DIVIDE : pembagian 8. INCREMENT Nomor 5 sampai 8 merupakan instruksi operand tunggal.

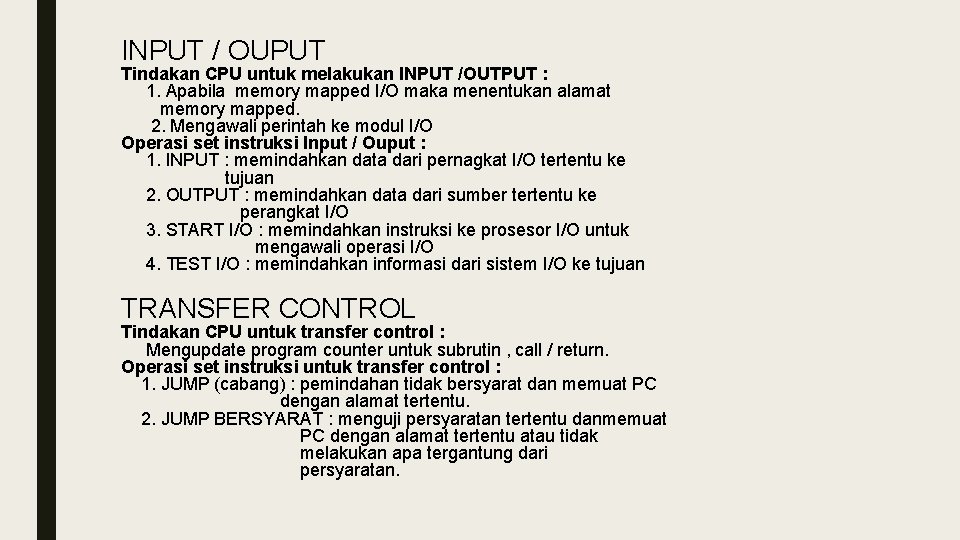

LOGICAL Tindakan CPU sama dengan arithmetic Operasi set instruksi untuk operasi logical : 1. AND, OR, NOT, EXOR 2. COMPARE : melakukan perbandingan logika. 3. TEST : menguji kondisi tertentu. 4. SHIFT : operand menggeser ke kiri atau kanan menyebabkan konstanta pada ujung bit. 5. ROTATE : operand menggeser ke kiri atau ke kanan dengan ujung yang terjalin. CONVERSI Tindakan CPU sama dengan arithmetic dan logical. Instruksi yang mengubah format instruksi yang beroperasi terhadap format data. Misalnya pengubahan bilangan desimal menjadi bilangan biner. Operasi set instruksi untuk conversi : 1. TRANSLATE : menterjemahkan nilai-nilai dalam suatu bagian memori berdasrkan tabel korespodensi. 2. CONVERT : mengkonversi isi suatu word dari suatu bentuk ke bentuk lainnya.

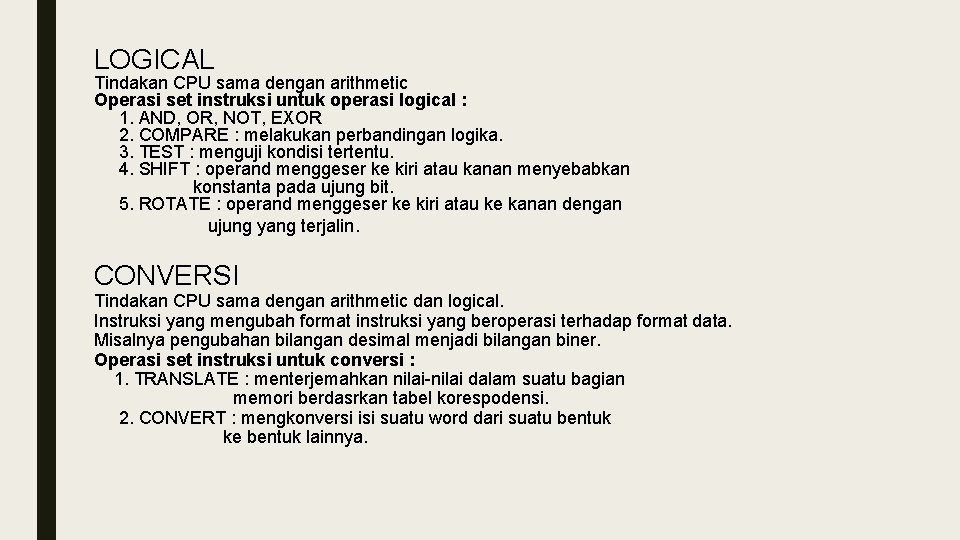

INPUT / OUPUT Tindakan CPU untuk melakukan INPUT /OUTPUT : 1. Apabila memory mapped I/O maka menentukan alamat memory mapped. 2. Mengawali perintah ke modul I/O Operasi set instruksi Input / Ouput : 1. INPUT : memindahkan data dari pernagkat I/O tertentu ke tujuan 2. OUTPUT : memindahkan data dari sumber tertentu ke perangkat I/O 3. START I/O : memindahkan instruksi ke prosesor I/O untuk mengawali operasi I/O 4. TEST I/O : memindahkan informasi dari sistem I/O ke tujuan TRANSFER CONTROL Tindakan CPU untuk transfer control : Mengupdate program counter untuk subrutin , call / return. Operasi set instruksi untuk transfer control : 1. JUMP (cabang) : pemindahan tidak bersyarat dan memuat PC dengan alamat tertentu. 2. JUMP BERSYARAT : menguji persyaratan tertentu danmemuat PC dengan alamat tertentu atau tidak melakukan apa tergantung dari persyaratan.

3. JUMP SUBRUTIN : melompat ke alamat tertentu. 4. RETURN : mengganti isi PC dan register lainnya yang berasal dari lokasi tertentu. 5. EXECUTE : mengambil operand dari lokasi tertentu dan mengeksekusi sebagai instruksi 6. SKIP : menambah PC sehingga melompati instruksi berikutnya. 7. SKIP BERSYARAT : melompat atau tidak melakukan apa-apa berdasarkan pada persyaratan 8. HALT : menghentikan eksekusi program. 9. WAIT (HOLD) : melanjutkan eksekusi pada saat persyaratan dipenuhi. 10. NO OPERATION : tidak ada operasi yang dilakukan. Macam-macam instruksi menurut jumlah operasi yang dispesifikasikan 1. O – Address Instruction 2. 1 – Addreess Instruction. 3. N – Address Instruction 4. M + N – Address Instruction

Macam-macam instruksi menurut sifat akses terhadap memori atau register 1. Memori To Register Instruction 2. Memori To Memori Instruction 3. Register To Register Instruction ADDRESSING MODES Jenis-jenis addressing modes (Teknik Pengalama-tan) yang paling umum: • Immediate • Direct • Indirect • Register Indirect • Displacement • Stack

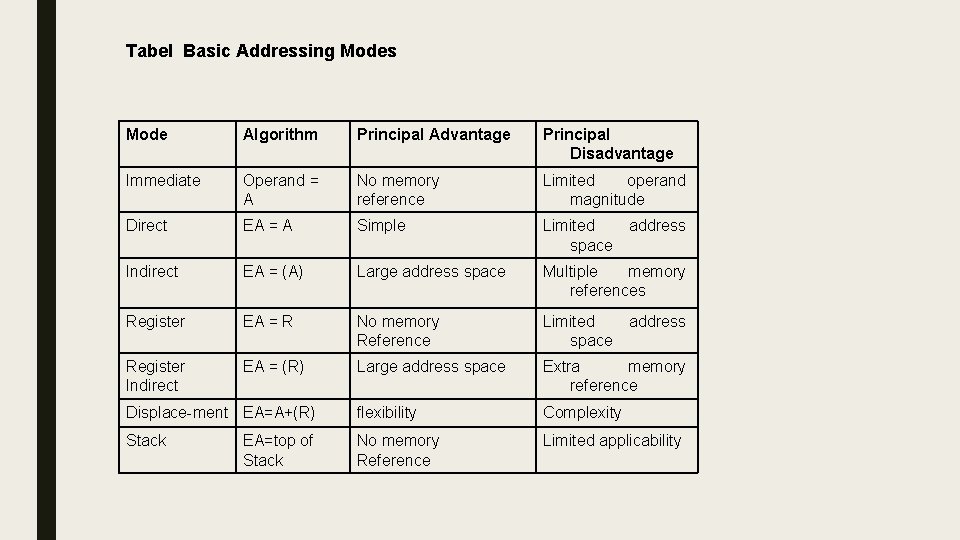

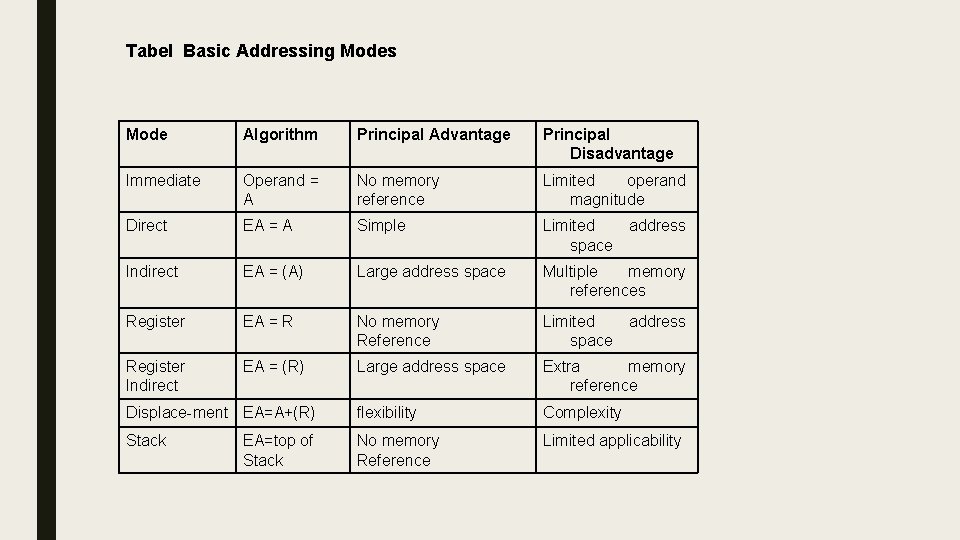

Tabel Basic Addressing Modes Mode Algorithm Principal Advantage Principal Disadvantage Immediate Operand = A No memory reference Limited operand magnitude Direct EA = A Simple Limited space Indirect EA = (A) Large address space Multiple memory references Register EA = R No memory Reference Limited space Register Indirect EA = (R) Large address space Extra memory reference Displace-ment EA=A+(R) flexibility Complexity Stack No memory Reference Limited applicability EA=top of Stack address

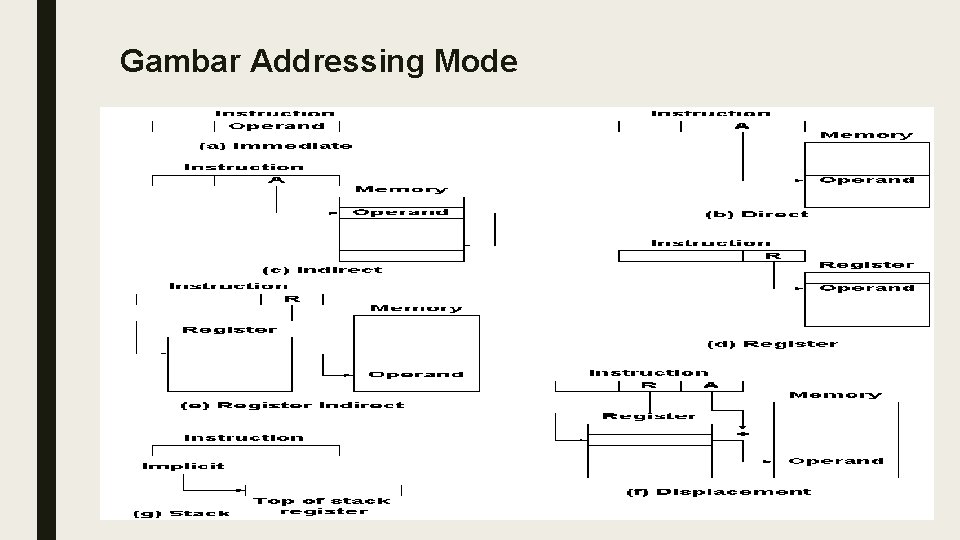

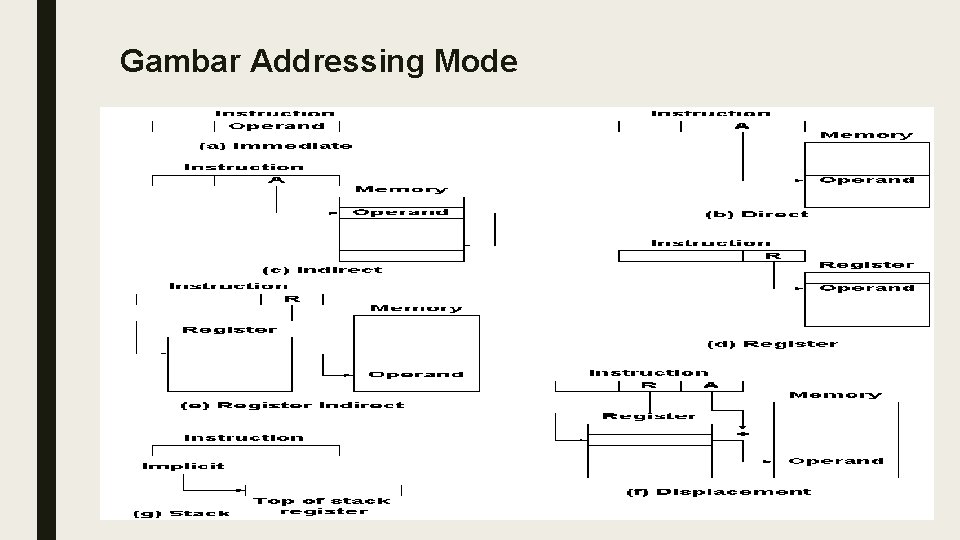

Gambar Addressing Mode

Prosesor RISC dan CISC Pengertian Pada saat ini prosesor saat ini yang dikenal ada 2 yaitu RISC dan CISC adalah singkatan dari Complex Intruction Set Computer dimana prosesor tersebut memiliki set instruksi yang kompleks dan lengkap. RISC adalah singkatan dari Reduced Instruction Set Computer yang artinya prosesor tersebut memiliki set instruksi program yang lebih

CISC sendiri adalah satu bentuk arsitektur yang menjalani beberapa instruksi dengan tingkat yang rendah. Misalnya intruksi tingakt rendah tersebut adalah operasi aritmetika, penyimpananpengambilan dari memory dll. CISC memang memiliki instruksi yang complex dan memang dirasa berpengaruh pada kinerjanya yang lebih lambat. CISC menawarkan set intruksi yang powerful, kuat, tangguh, maka tak heran jika CISC memang hanya mengenal bahasa asembly yang sebenarnya ia tujukan bagi para programmer. Bahasa assembler ini biasanya diambil dari bahasa Inggris dan presentasinya itu disebut dengan Mnemonic. ■ ■ ■ ■ Biner 10110110 B 6 10010111 97 01001010 4 A 10001010 8 A 00100110 26 00000001 01 01111110 7 E Hexa Mnemonic LDAA. . . STAA. . . DECA. . . ORAA. . . BNE. . . NOP. . . JMP. . .

RISC Konsep arsitektur RISC banyak menerapkan proses eksekusi pipeline. Meskipun jumlah perintah tunggal yang diperlukan untuk melakukan pekerjaan yang diberikan mungkin lebih besar, eksekusi secara pipeline memerlukan waktu yang lebih singkat daripada waktu untuk melakukan pekerjaan yang sama dengan menggunakan perintah yang lebih rumit. Mesin RISC memerlukan memori yang lebih besar untuk mengakomodasi program yang lebih besar. IBM 801 adalah prosesor komersial pertama yang menggunakan pendekatan RISC. Lebih lanjut untuk memahami RISC, diawali dengan tinjauan singkat tentang karakteristik eksekusi instruksi. Aspek komputasi yang ditinjau dalam merancang mesin RISC adalah sbb. : >>Operasi-operasi yang dilakukan: Hal ini menentukan fungsi-fungsi yang akan dilakukan oleh CPU dan interaksinya dengan memori. >> Operand-operand yang digunakan: Jenis-jenis operand dan frekuensi pemakaiannya akan menentukan organisasi memori untuk menyimpannya dan mode pengalamatan untuk mengaksesnya. >> Pengurutan eksekusi: Hal ini akan menentukan kontrol dan organisasi pipeline.

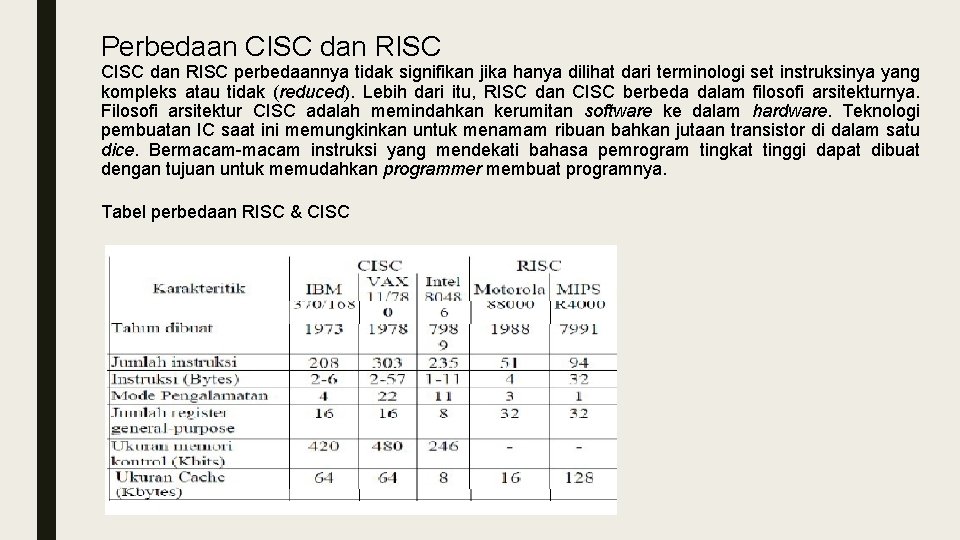

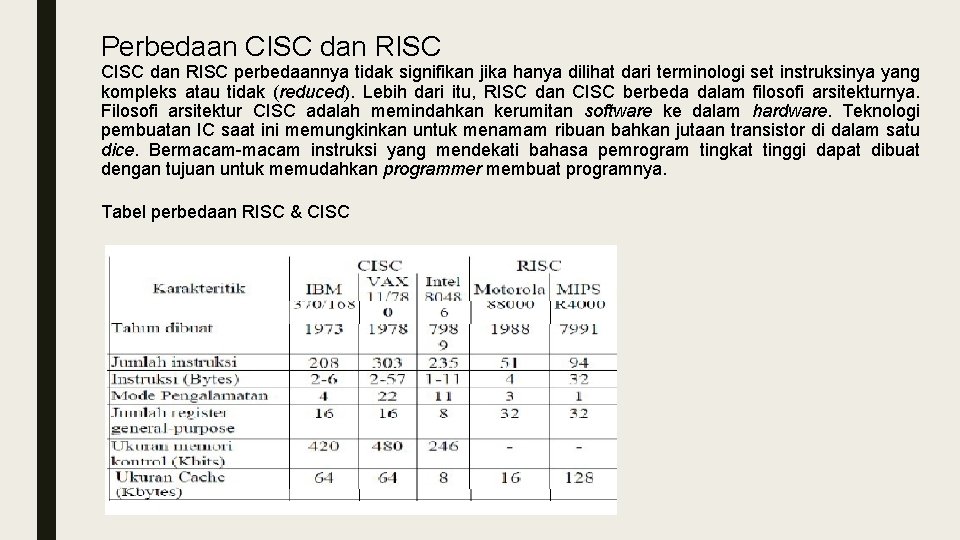

Perbedaan CISC dan RISC perbedaannya tidak signifikan jika hanya dilihat dari terminologi set instruksinya yang kompleks atau tidak (reduced). Lebih dari itu, RISC dan CISC berbeda dalam filosofi arsitekturnya. Filosofi arsitektur CISC adalah memindahkan kerumitan software ke dalam hardware. Teknologi pembuatan IC saat ini memungkinkan untuk menamam ribuan bahkan jutaan transistor di dalam satu dice. Bermacam-macam instruksi yang mendekati bahasa pemrogram tingkat tinggi dapat dibuat dengan tujuan untuk memudahkan programmer membuat programnya. Tabel perbedaan RISC & CISC

Karakteristik CISC dan RISC >> Rancangan RISC dapat memperoleh keuntungan dengan mengambil sejumlah feature CISC dan Rancangan CISC dapat memperoleh keuntungan dengan mengambil sejumlah feature RISC. >> Hasilnya adalah bahwa sejumlah rancangan RISC yang terbaru, yang dikenal sebagai Power. PC, tidak lagi “murni” RISC dan rancangan CISC yang terbaru, yang dikenal sebagai Pentium, memiliki beberapa karakteristik RISC. Ciri-ciri RISC >> Instruksi berukuran tunggal >> Ukuran yang umum adalah 4 byte. >> Jumlah mode pengalamatan data yang sedikit, biasanya kurang dari lima buah. >> Tidak terdapat pengalamatan tak langsung. >> Tidak terdapat operasi yang menggabungkan operasi load/store dengan operasi aritmetika (misalnya, penambahan dari memori, penambahan ke memori). Ciri-Ciri CISC >> Penekanan pada perangkat keras (hardware) >> Termasuk instruksi kompleks multi-clock >> Memori-ke-memori: “LOAD” dan “STORE” saling bekerjasama >> Ukuran kode kecil, kecepatan rendah >> Transistor digunakan untuk menyimpan instruksi-instruksi kompleks

AContoh Aplikasi RISC tmel AVR adalah modifikasi arsitektur Harvard 8 -bit RISC single chip microcontroller yang di kembangkan oleh atmel pada 1996. AVR adalah satu dari keluarga mikrokontroller pertama yang menggunakan memori on-chip flash untuk penyimpanan program, sebagai lawan untuk progammable one time pada ROM, EPROM atau EEPROM digunakan oleh mikrokontroller lain. Atmel AVR Atmega 8

Pipelining Prosesor melakukan suatu kegiatan membagi-bagi proses menjadi beberapa tahapan, dimana semua tahapan komputasi bekerja secara bersama-sama dalam tahapan eksekusi yang berbeda-beda. Komponen Pipelining 1. Latches (register cepat) Register yang menyimpan operand untuk setiap stage/tahapan dan hasil dari proses tahapan/stage sebelumnya. 2. Timer (clock) • Mensinkronkan semua tahapan/stage dalam pipelining dengan tahapan/stage berikutnya. • Memberitahukan latches mengenai kapan membaca hasil dari stage pada saat ini dan membuatnya dapat digunakan pada stage berikutnya. 3. Pipeline Berisikan semua sirkuit untuk tahapan individual, bersama dengan latches yang memisahkan antar tahapan/stage.

Istilah Pipelining 1. Flowtrought Time Waktu yang dibutuhkan oleh pipe untuk menghasilkan result pertamanya. 2. Clock-Cycle Time Waktu yang dibutuhkan oleh pipe untuk menghasilkan result yang berurutan. 3. Branch Penalty Waktu yang dibutuhkan untuk mengisi kembali pipeline setelah branch kondisional berhasil. Unit Pipelining 1. Aritmetik 2. Instruksi generasi alamat instruksi generasi alamat operand fetch instruksi dari memory fetch operand dari memory Menterjemahkan opcode eksekusi instruksi menampilkan result

Event Penghambat Pipelining 1. Unit Fungsional dan Instruksi 2. Ketergantungan Instruksi 3. Kecepatan memory memasok instruksi = proses instruksi 4. Eksekusi logis beberapa instruksi secara urut 5. Perbedaan jumlah tahapan/stage (branch penalty) dengan cycle time

Referensi https: //id. wikipedia. org/wiki/Atmel_AVR