Implementation RISC vs CISC concept Concept of pipeline

- Slides: 28

Implementation RISC vs. CISC concept Concept of pipeline An implementation of Mips Pipeline’s problems Pirouz Bazargan Sabet December 2003

Implementation Objectives Execute each instruction in one cycle Which hardware is required Pirouz Bazargan Sabet December 2003

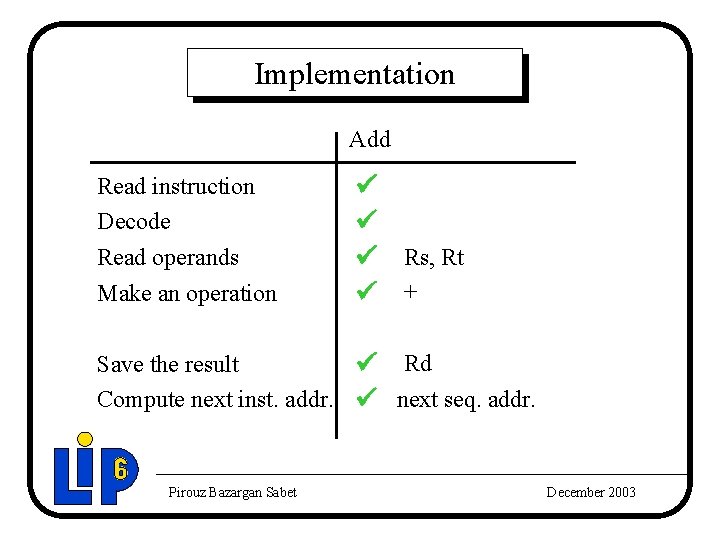

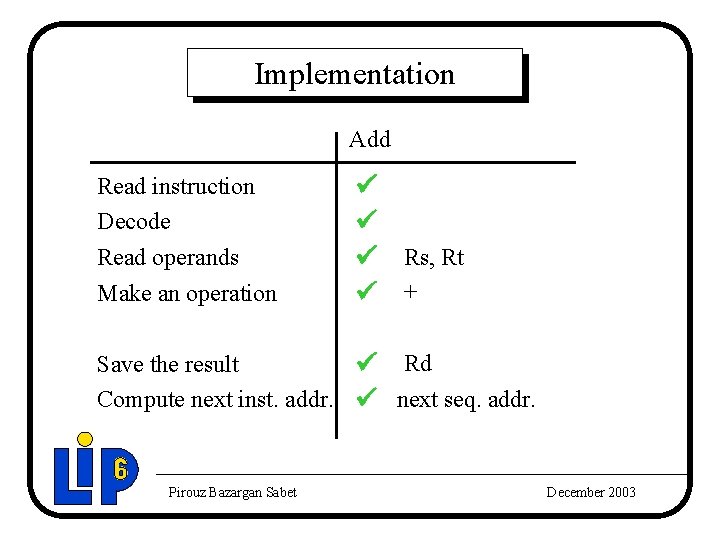

Implementation Add Read instruction Decode Read operands Make an operation ü ü ü Rs, Rt ü + Save the result ü Rd Compute next inst. addr. ü next seq. addr. Pirouz Bazargan Sabet December 2003

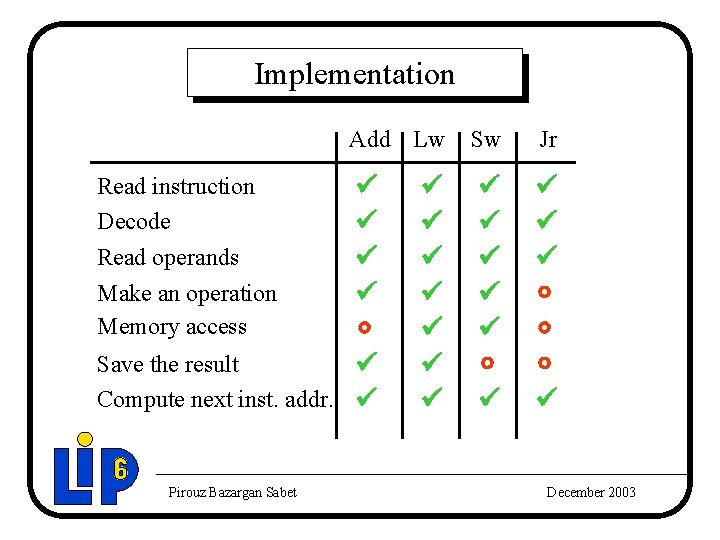

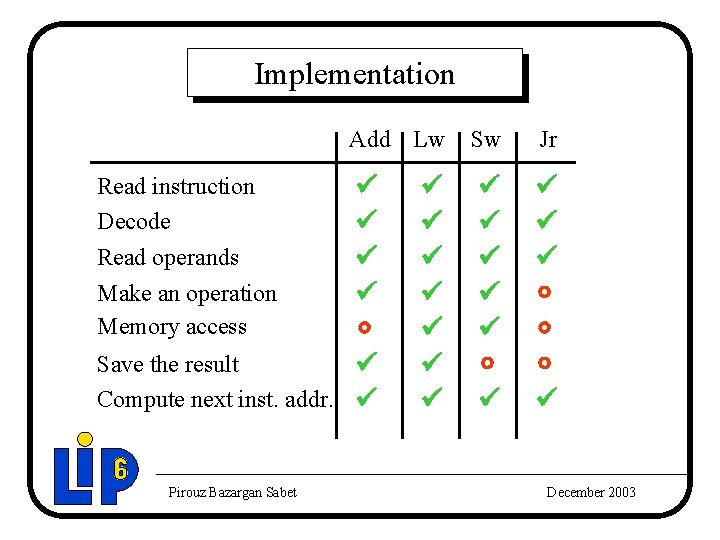

Implementation Add Lw Read instruction Decode Read operands Make an operation Memory access ü ü Save the result ü Compute next inst. addr. ü Pirouz Bazargan Sabet ü ü ü ü Sw Jr ü ü ü ü ü December 2003

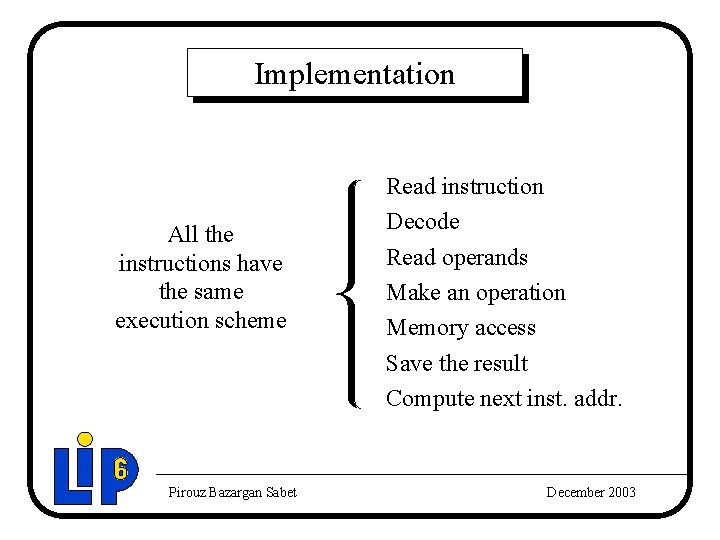

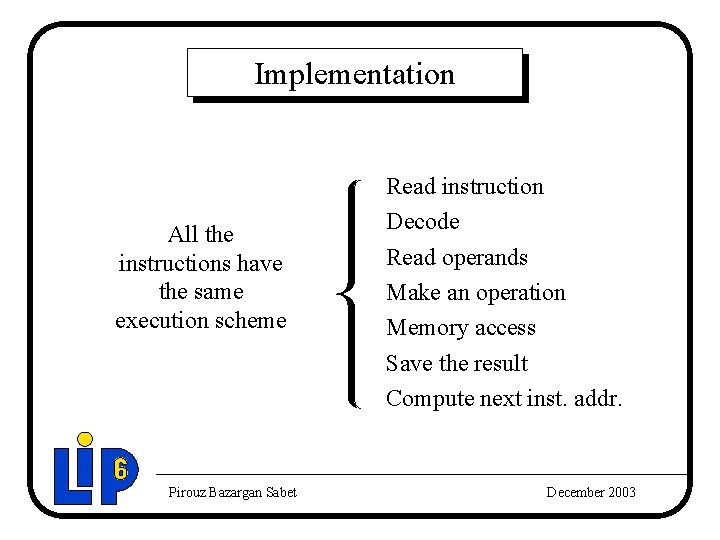

Implementation All the instructions have the same execution scheme Pirouz Bazargan Sabet Read instruction Decode Read operands Make an operation Memory access Save the result Compute next inst. addr. December 2003

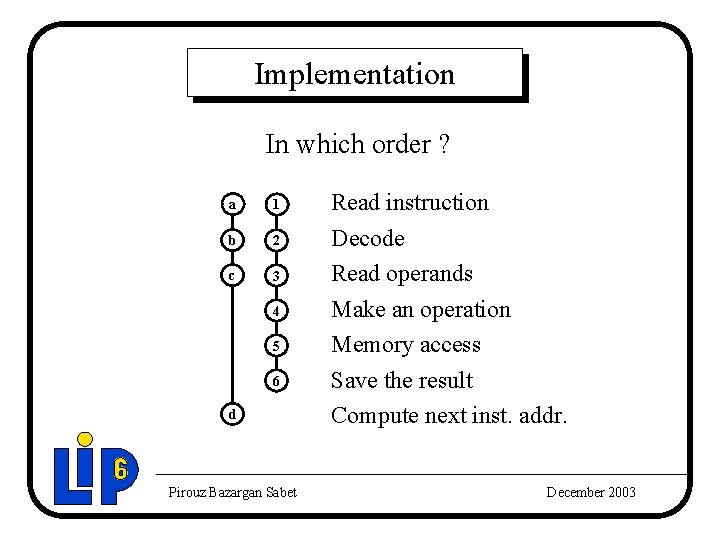

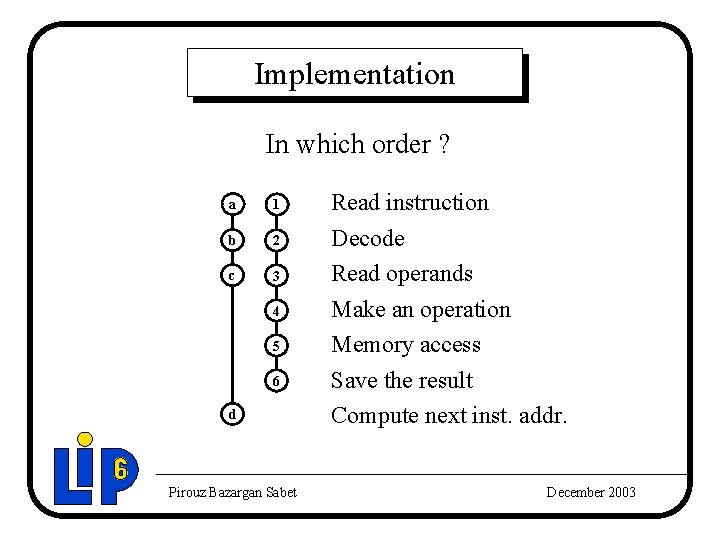

Implementation In which order ? a 1 b 2 c 3 4 5 6 d Pirouz Bazargan Sabet Read instruction Decode Read operands Make an operation Memory access Save the result Compute next inst. addr. December 2003

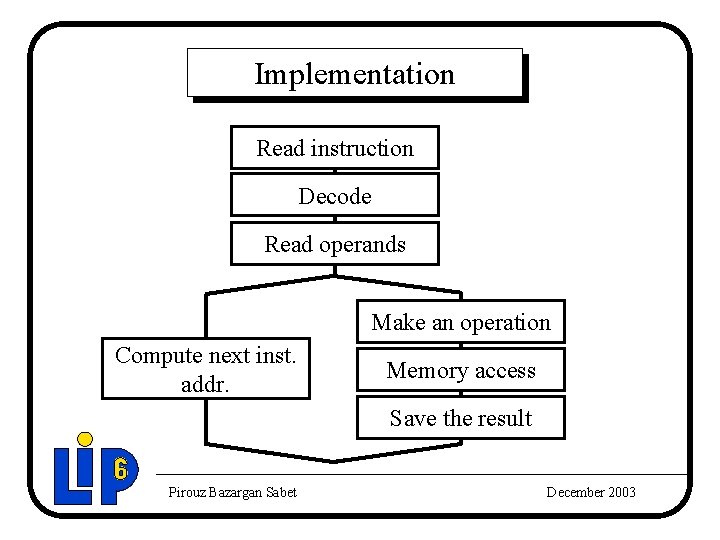

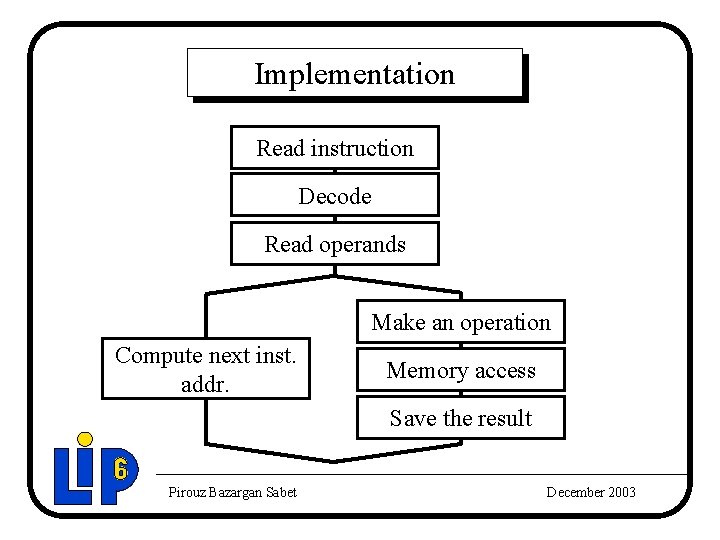

Implementation Read instruction Decode Read operands Make an operation Compute next inst. addr. Memory access Save the result Pirouz Bazargan Sabet December 2003

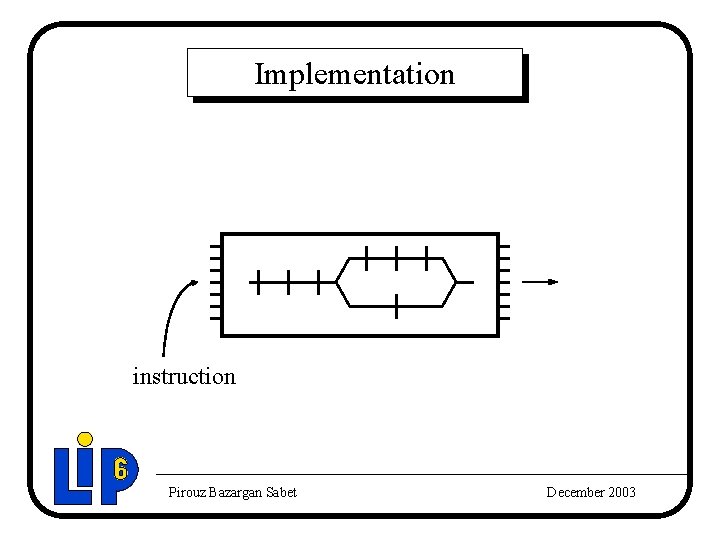

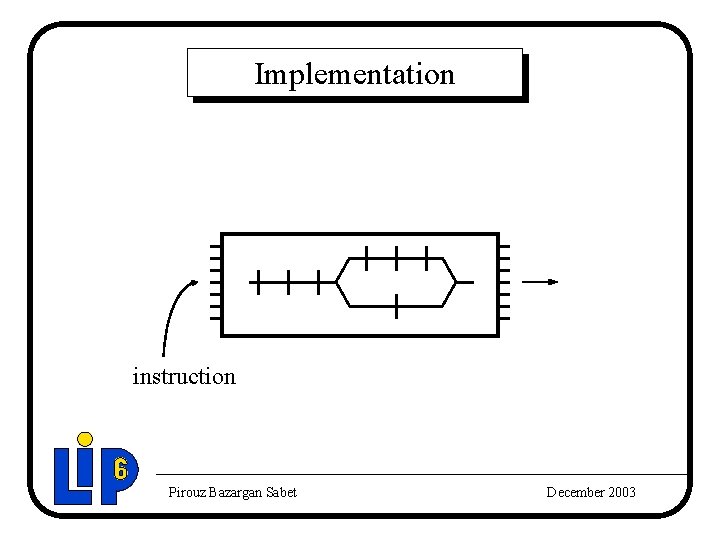

Implementation instruction Pirouz Bazargan Sabet December 2003

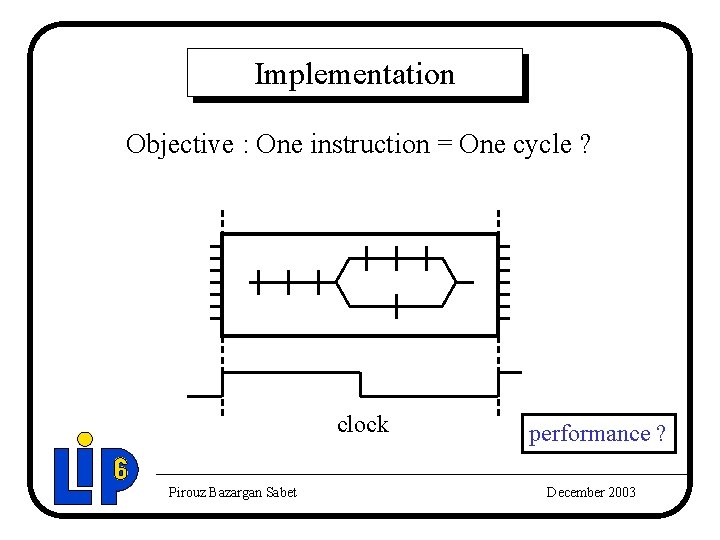

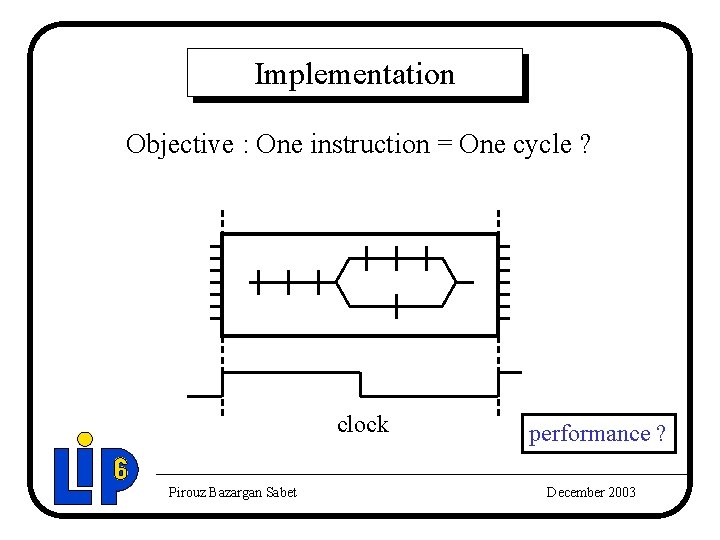

Implementation Objective : One instruction = One cycle ? clock Pirouz Bazargan Sabet performance ? December 2003

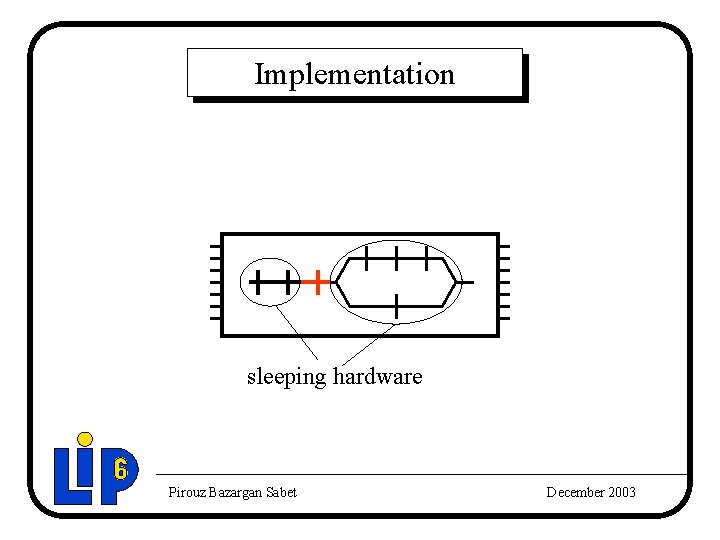

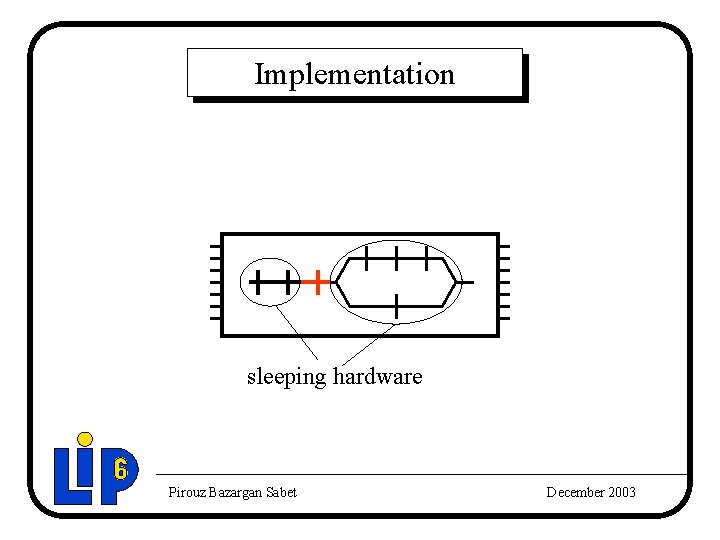

Implementation sleeping hardware Pirouz Bazargan Sabet December 2003

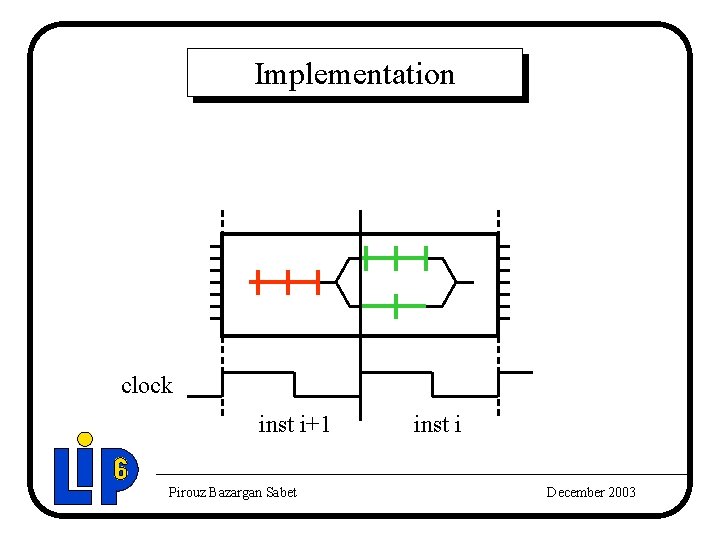

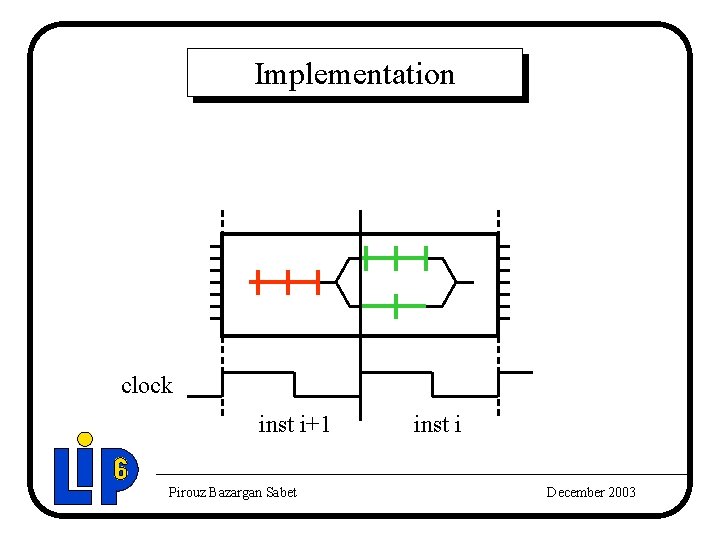

Implementation clock inst i+1 clock Pirouz Bazargan Sabet inst i December 2003

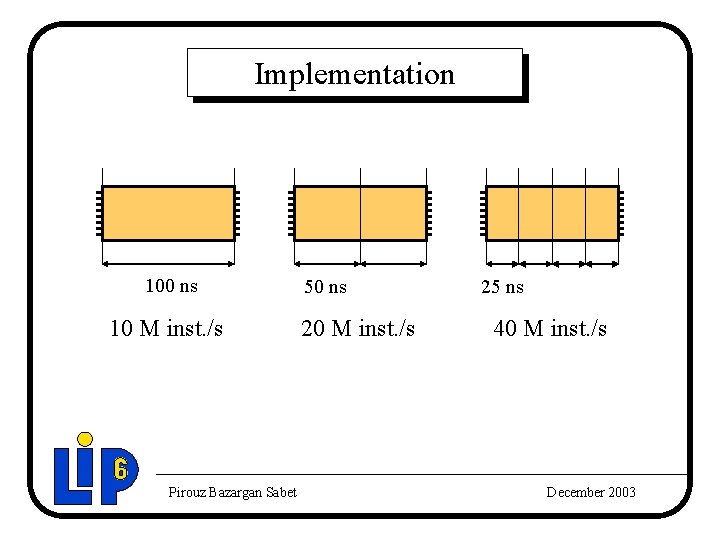

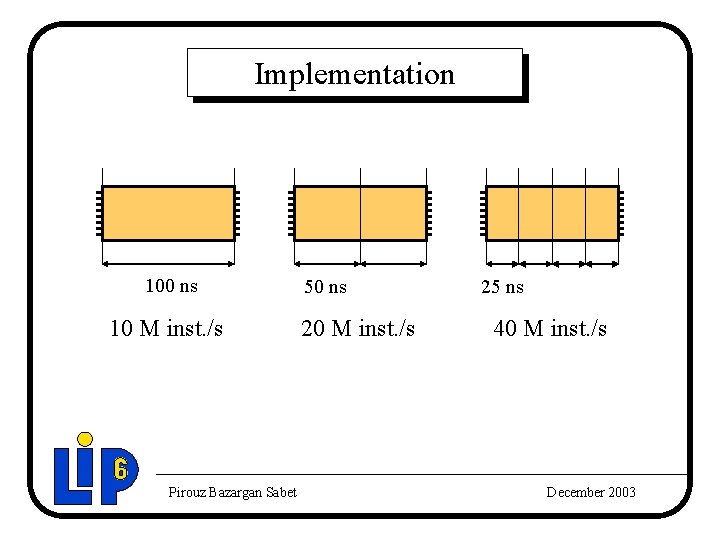

Implementation 100 ns 10 M inst. /s Pirouz Bazargan Sabet 50 ns 20 M inst. /s 25 ns 40 M inst. /s December 2003

Implementation Is there any limitation ? NO ! Pirouz Bazargan Sabet December 2003

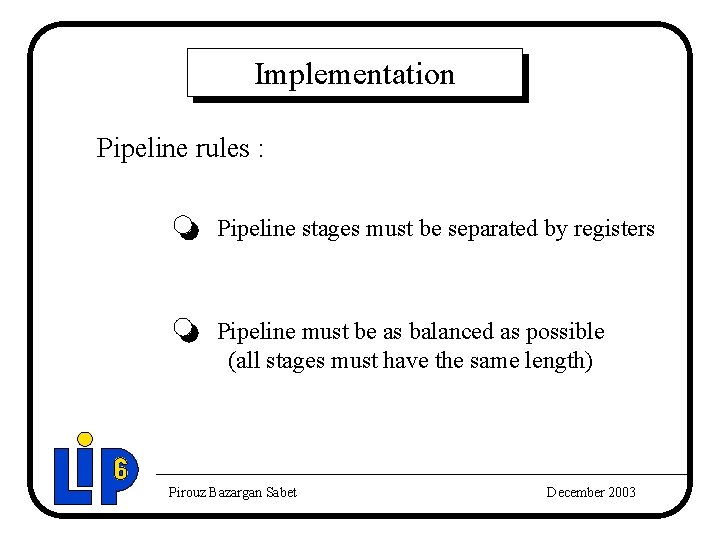

Implementation Pipeline rules : Pipeline stages must be separated by registers Pipeline must be as balanced as possible (all stages must have the same length) Pirouz Bazargan Sabet December 2003

Implementation RISC vs. CISC concept Concept of pipeline An implementation of Mips Pipeline’s problems Pirouz Bazargan Sabet December 2003

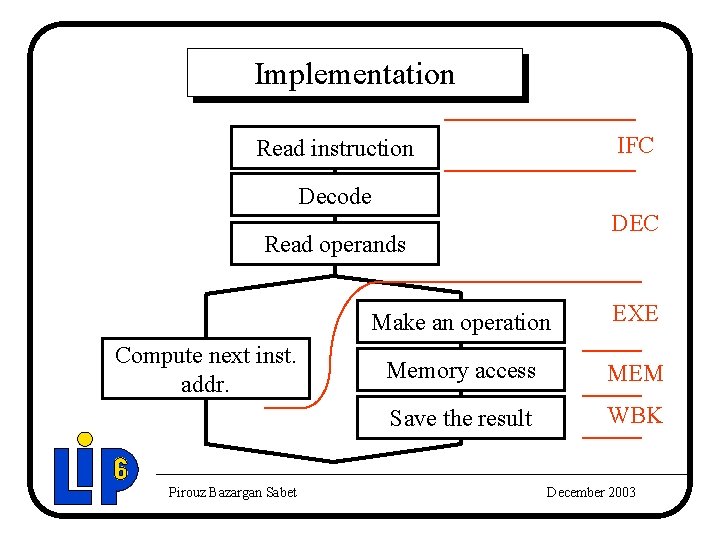

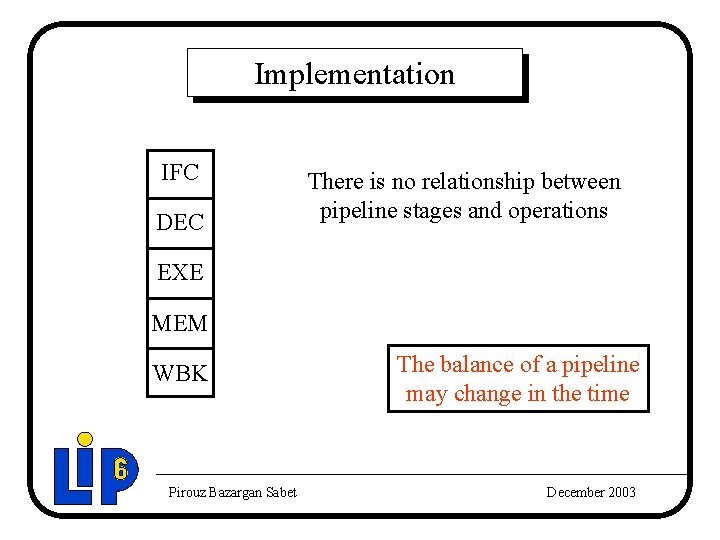

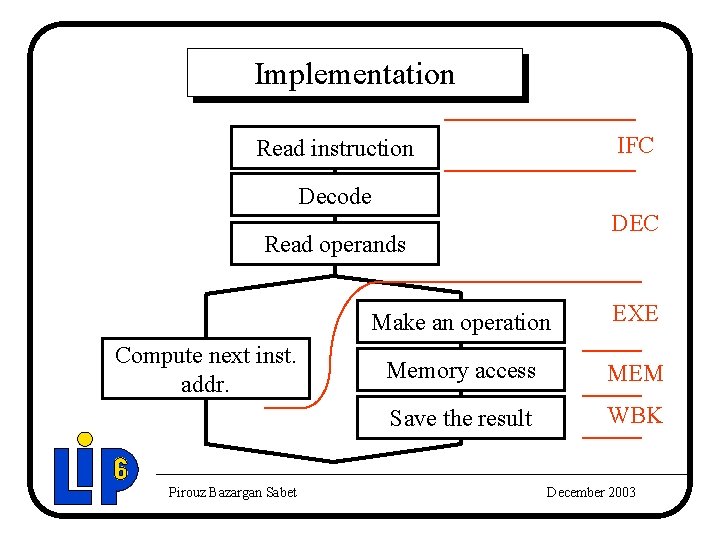

Implementation IFC Read instruction Decode DEC Read operands Compute next inst. addr. Pirouz Bazargan Sabet Make an operation EXE Memory access MEM Save the result WBK December 2003

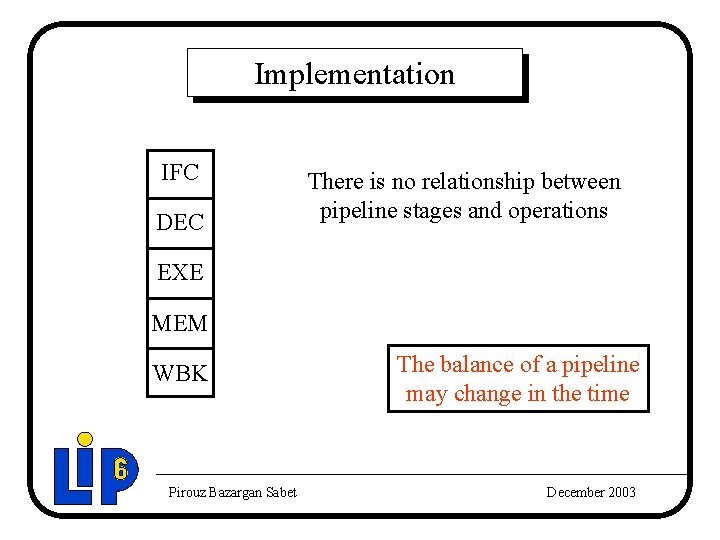

Implementation IFC DEC There is no relationship between pipeline stages and operations EXE MEM WBK Pirouz Bazargan Sabet The balance of a pipeline may change in the time December 2003

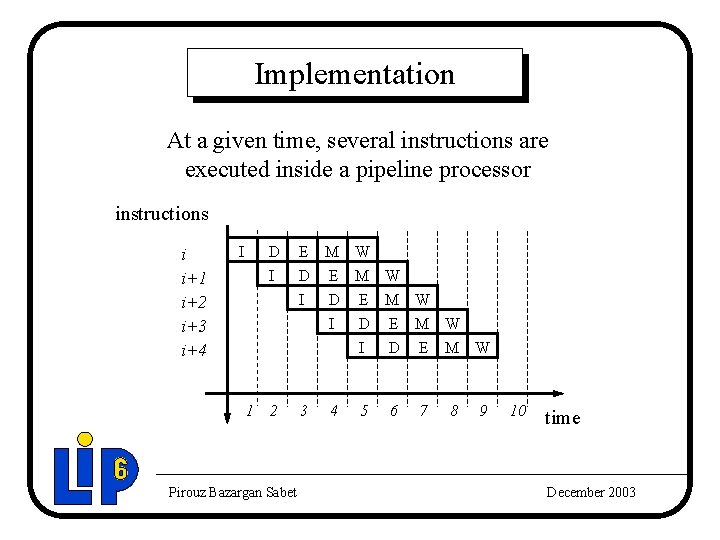

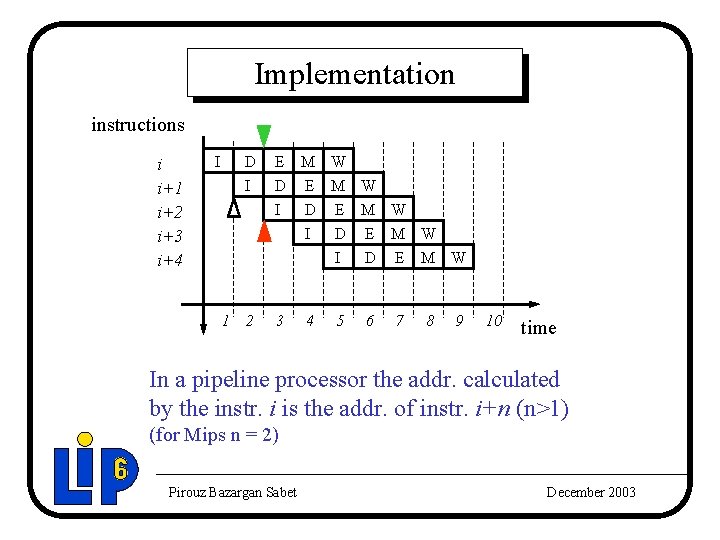

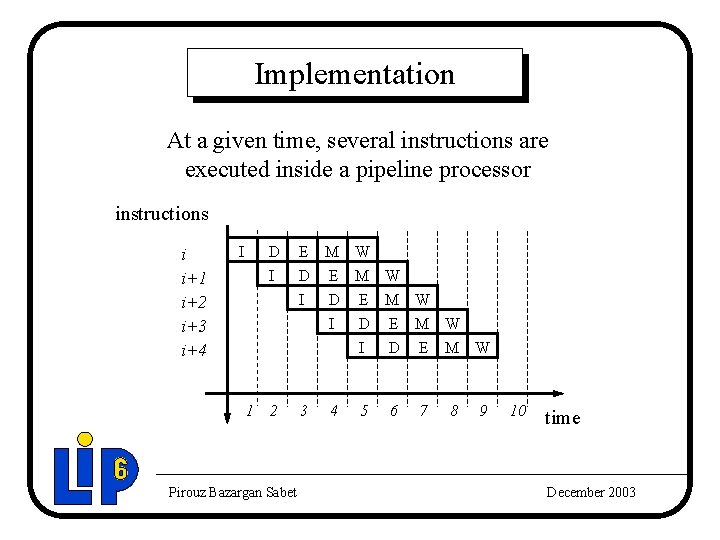

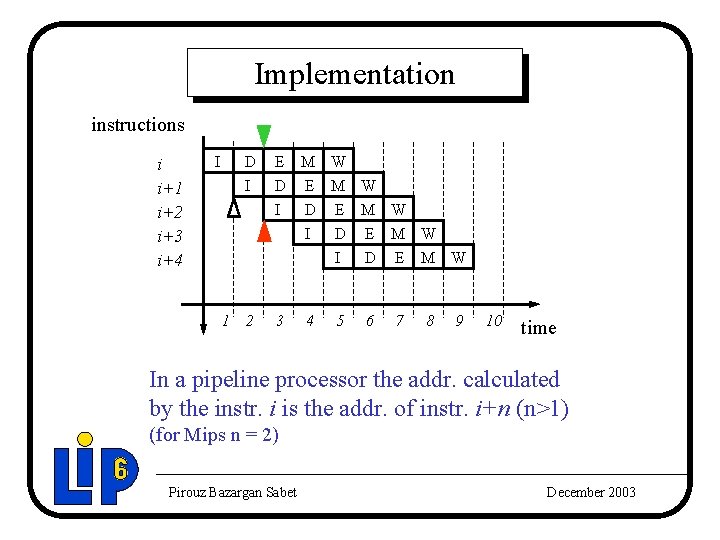

Implementation At a given time, several instructions are executed inside a pipeline processor instructions i i+1 i+2 i+3 i+4 I 1 D I E M W D E M W I D E M W 2 3 Pirouz Bazargan Sabet 4 5 6 7 8 9 10 time December 2003

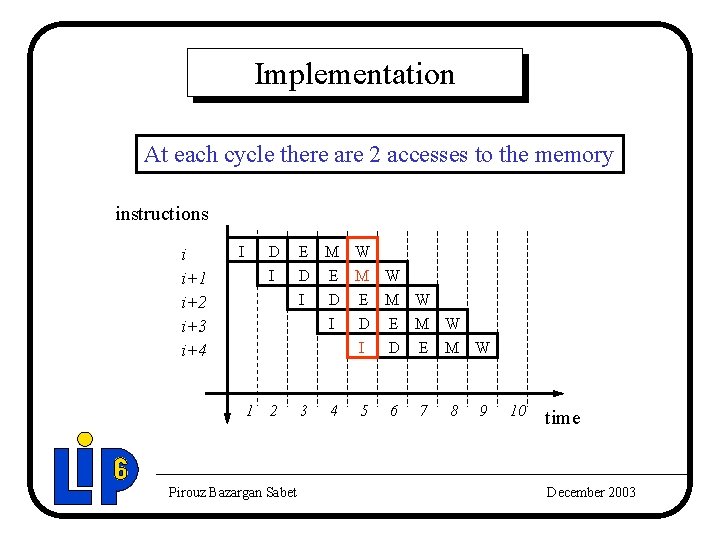

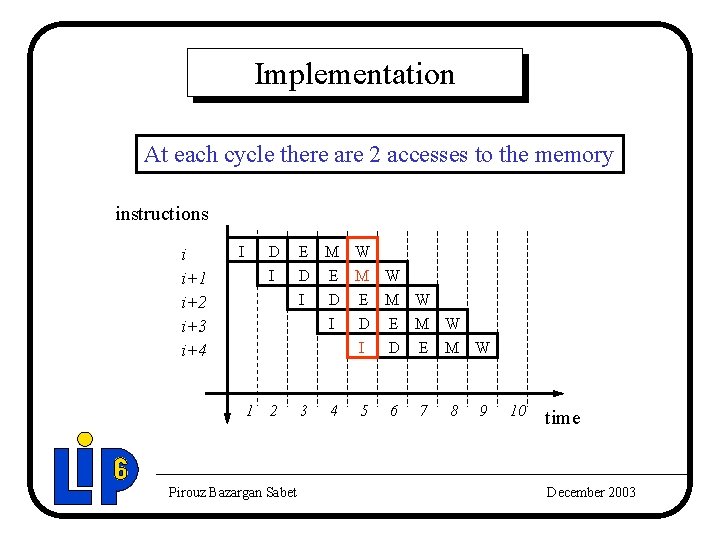

Implementation At each cycle there are 2 accesses to the memory instructions i i+1 i+2 i+3 i+4 I 1 D I E M W D E M W I D E M W 2 3 Pirouz Bazargan Sabet 4 5 6 7 8 9 10 time December 2003

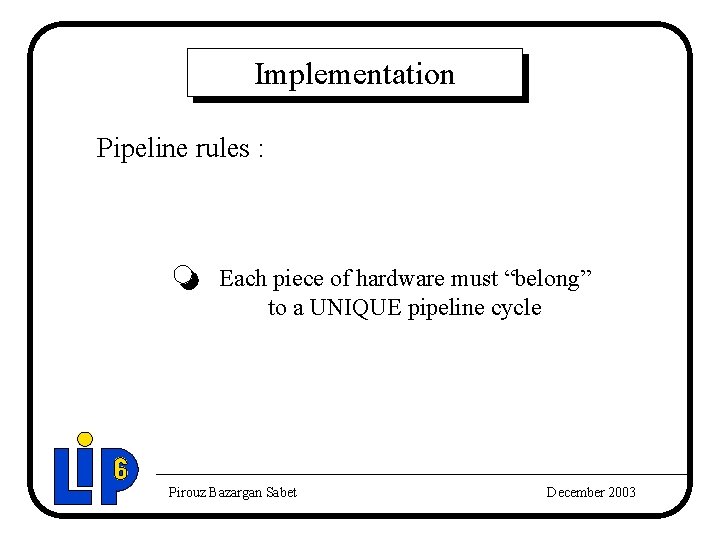

Implementation Pipeline rules : Each piece of hardware must “belong” to a UNIQUE pipeline cycle Pirouz Bazargan Sabet December 2003

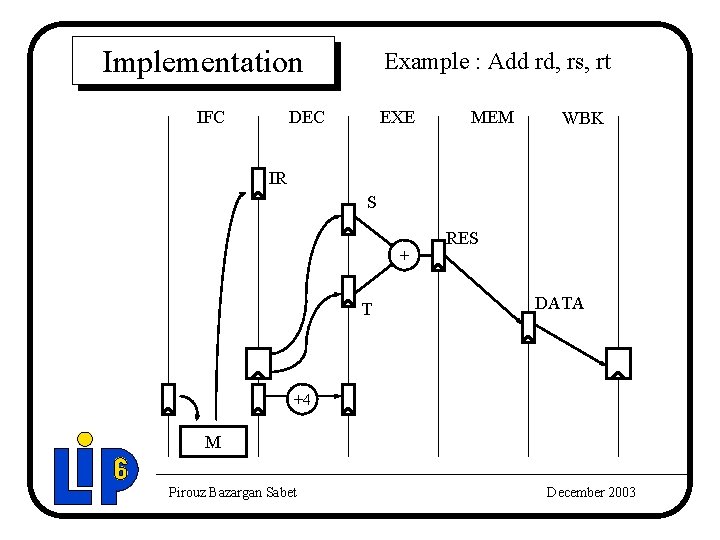

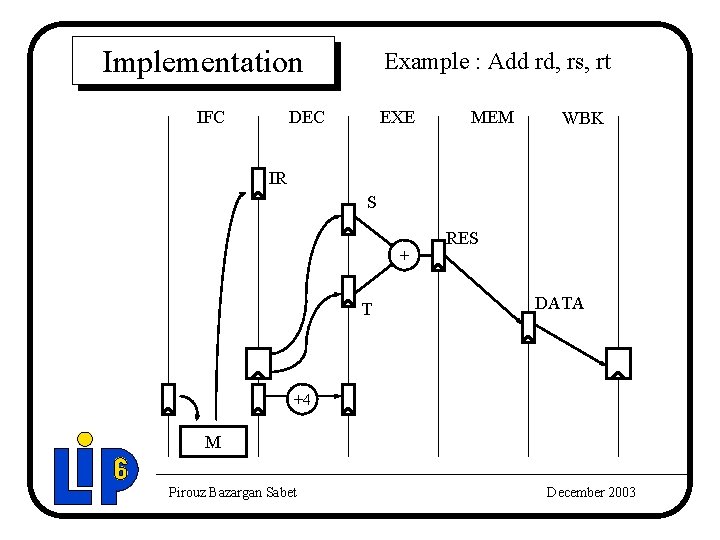

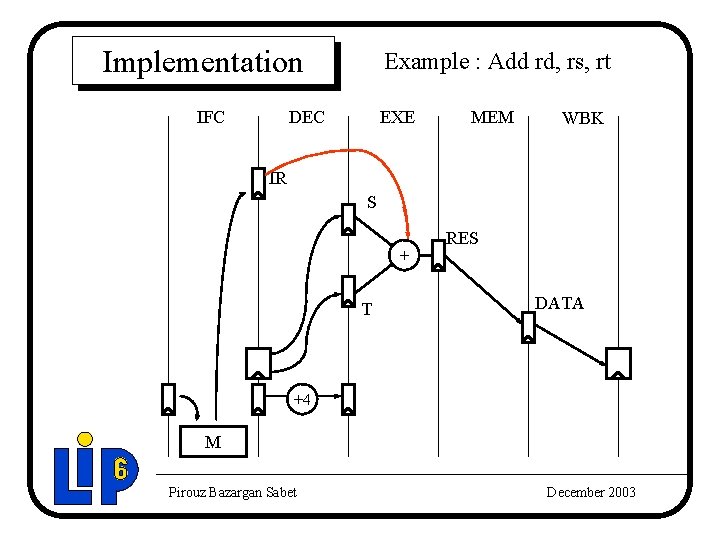

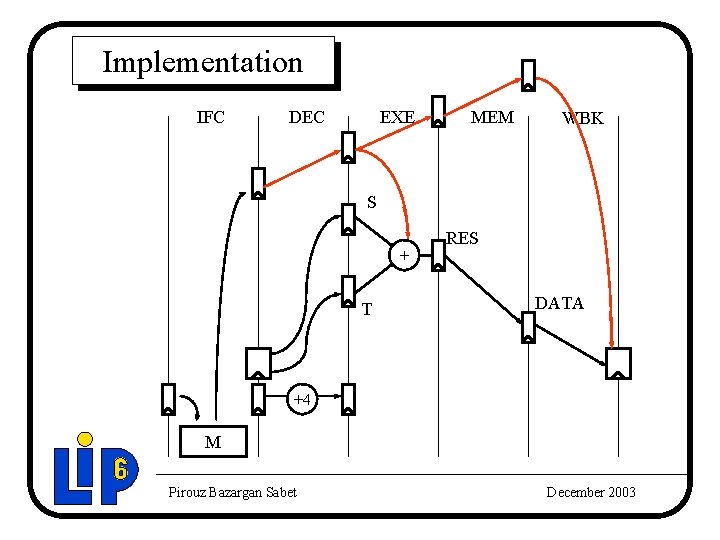

Implementation IFC Example : Add rd, rs, rt DEC EXE MEM WBK IR S + T RES DATA +4 M Pirouz Bazargan Sabet December 2003

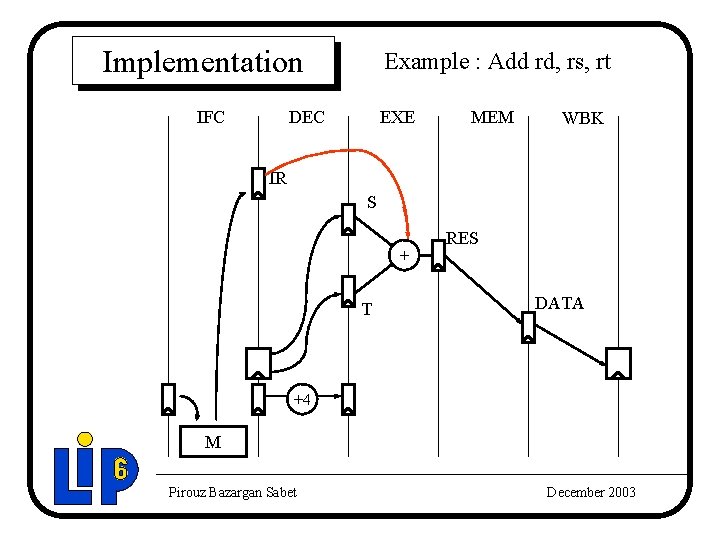

Implementation IFC Example : Add rd, rs, rt DEC EXE MEM WBK IR S + T RES DATA +4 M Pirouz Bazargan Sabet December 2003

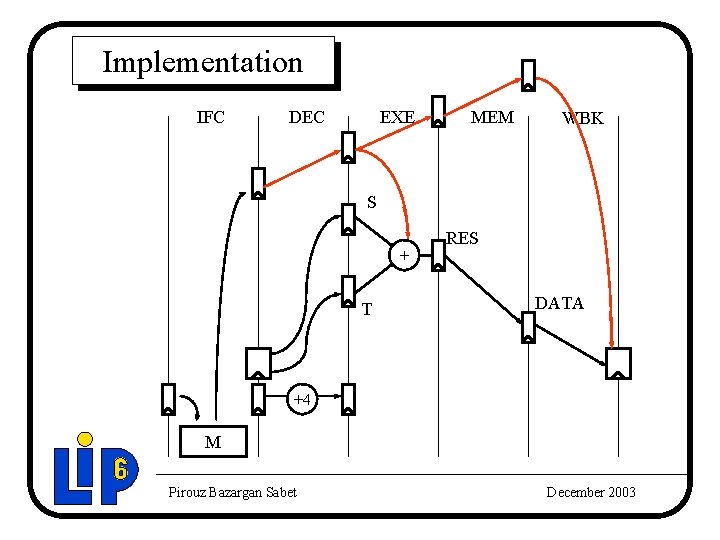

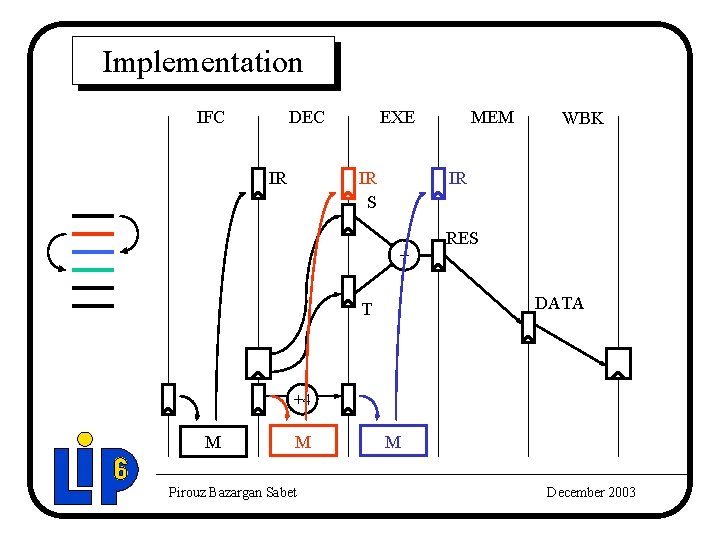

Implementation IFC DEC EXE MEM WBK IR S + T RES DATA +4 M Pirouz Bazargan Sabet December 2003

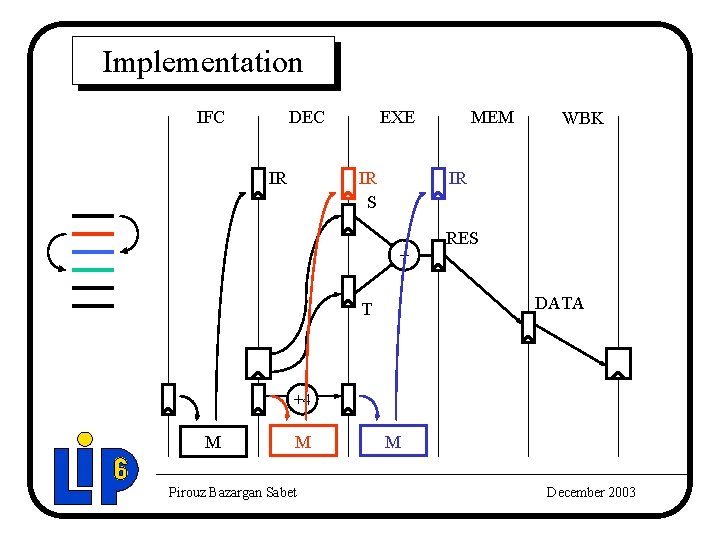

Implementation IFC DEC IR EXE IR S MEM WBK IR + RES DATA T +4 M M Pirouz Bazargan Sabet M December 2003

Implementation instructions i i+1 i+2 i+3 i+4 I D I 1 2 E M W D E M W I D E M W 3 I D I E M W D E M W 4 5 6 7 8 9 10 time In a pipeline processor the addr. calculated by the instr. i is the addr. of instr. i+n (n>1) (for Mips n = 2) Pirouz Bazargan Sabet December 2003

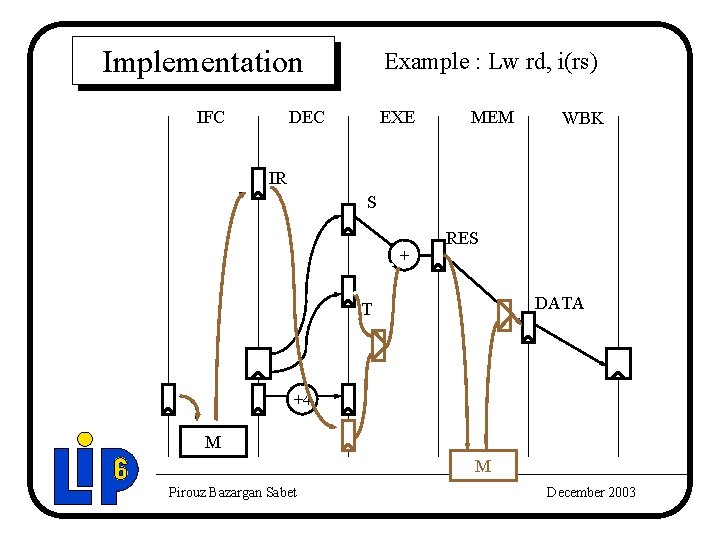

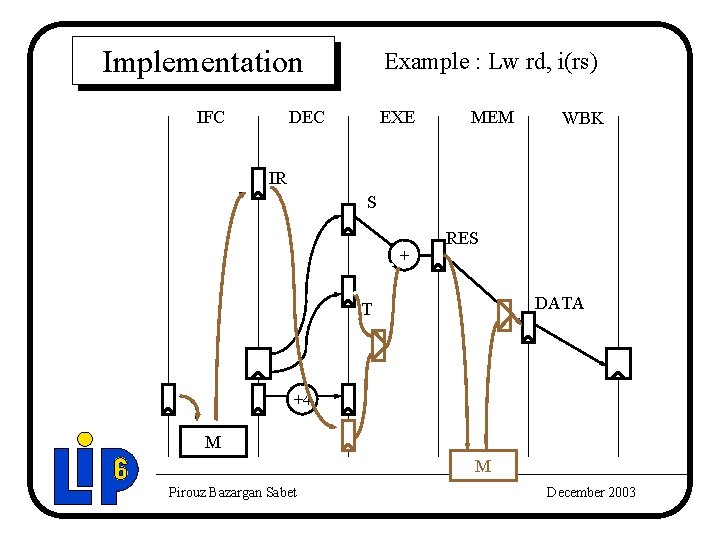

Implementation IFC Example : Lw rd, i(rs) DEC EXE MEM WBK IR S + RES DATA T +4 M M Pirouz Bazargan Sabet December 2003

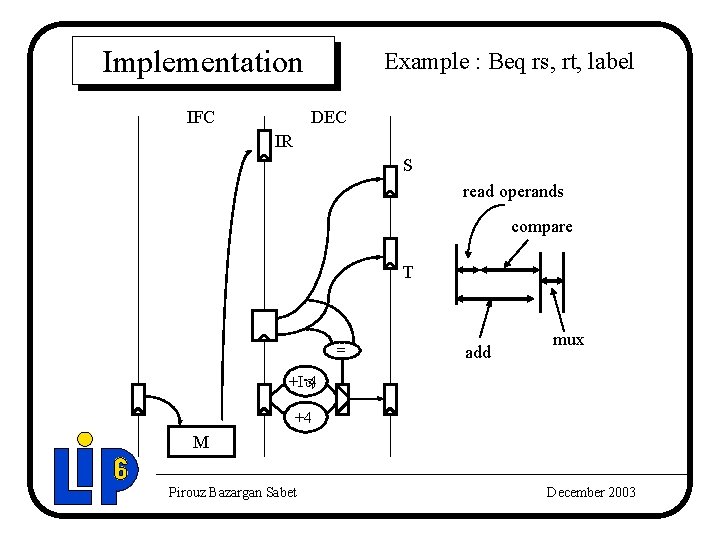

Implementation IFC Example : Beq rs, rt, label DEC IR S read operands add T compare = 4 IÎ4 M Pirouz Bazargan Sabet mux + too long ! December 2003

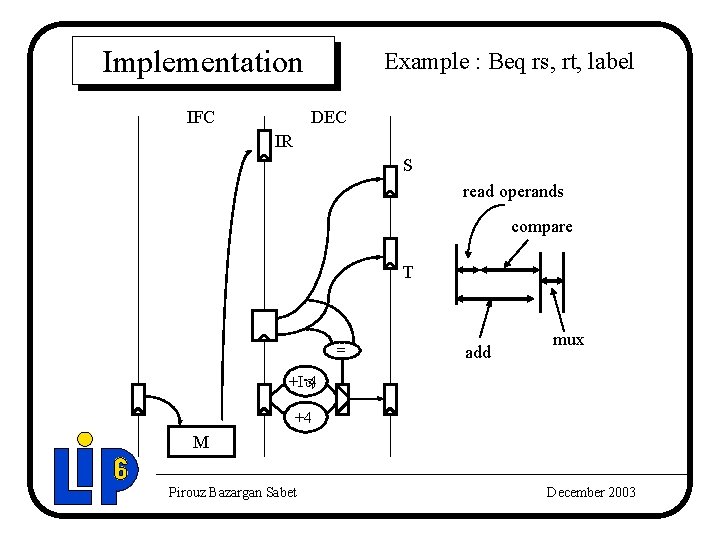

Implementation IFC Example : Beq rs, rt, label DEC IR S read operands compare T = add mux +IÎ4 +4 M Pirouz Bazargan Sabet December 2003