RISC vs CISC Introduo RISC CISC instrues simples

![RISC vs. CISC Comparação : programação Exemplo main () { int a[100]; soma (a, RISC vs. CISC Comparação : programação Exemplo main () { int a[100]; soma (a,](https://slidetodoc.com/presentation_image_h2/5f03234dbae69c40e75b7e7f33c4eeae/image-11.jpg)

- Slides: 12

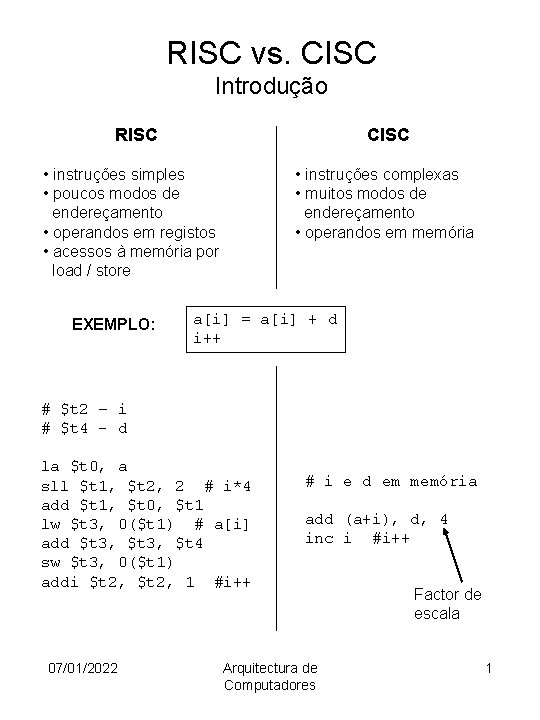

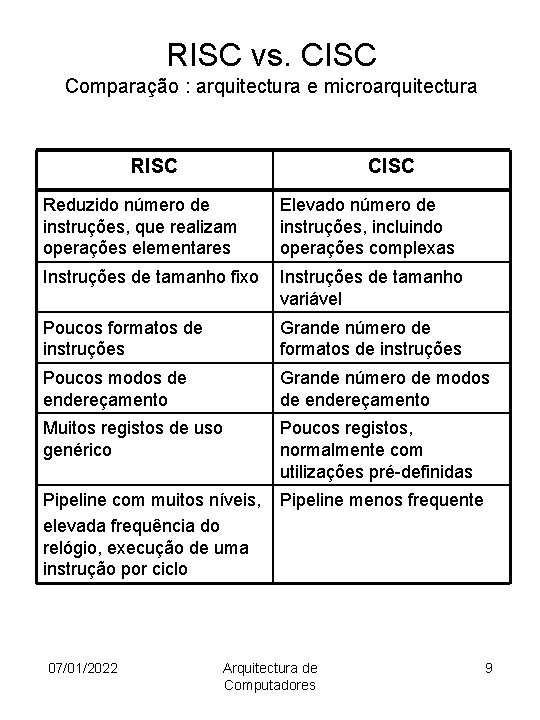

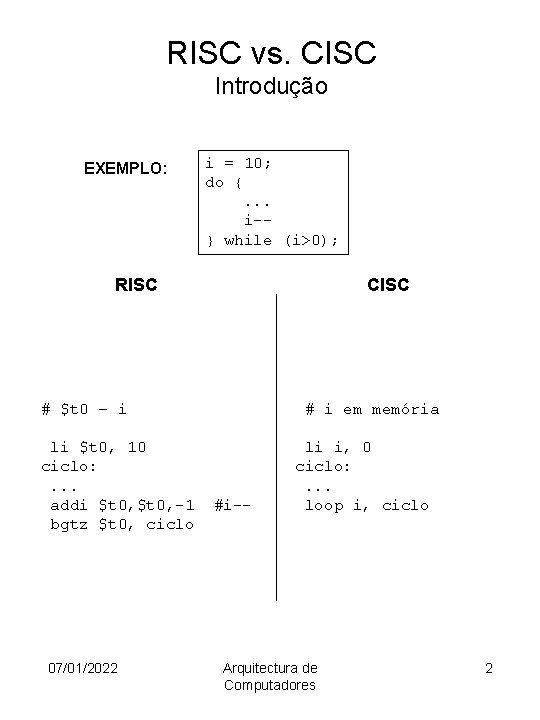

RISC vs. CISC Introdução RISC CISC • instruções simples • poucos modos de endereçamento • operandos em registos • acessos à memória por load / store EXEMPLO: • instruções complexas • muitos modos de endereçamento • operandos em memória a[i] = a[i] + d i++ # $t 2 – i # $t 4 - d la $t 0, a sll $t 1, $t 2, 2 # i*4 add $t 1, $t 0, $t 1 lw $t 3, 0($t 1) # a[i] add $t 3, $t 4 sw $t 3, 0($t 1) addi $t 2, 1 #i++ 07/01/2022 # i e d em memória add (a+i), d, 4 inc i #i++ Arquitectura de Computadores Factor de escala 1

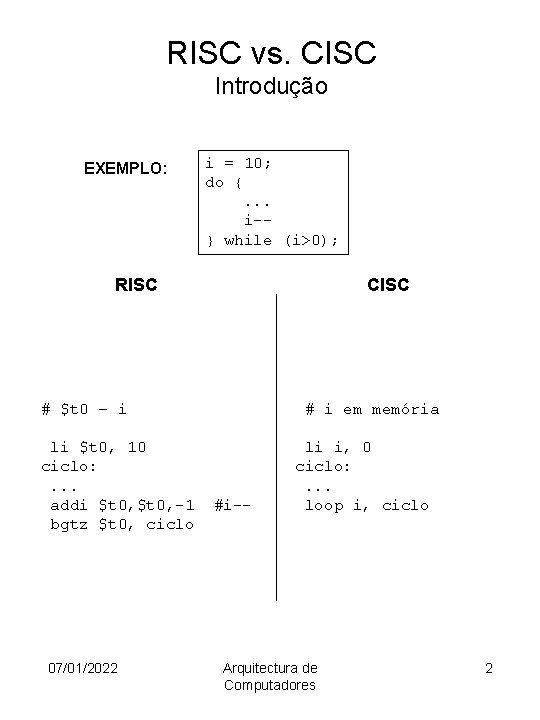

RISC vs. CISC Introdução EXEMPLO: i = 10; do {. . . i-} while (i>0); RISC CISC # $t 0 – i li $t 0, 10 ciclo: . . . addi $t 0, -1 bgtz $t 0, ciclo 07/01/2022 # i em memória #i-- li i, 0 ciclo: . . . loop i, ciclo Arquitectura de Computadores 2

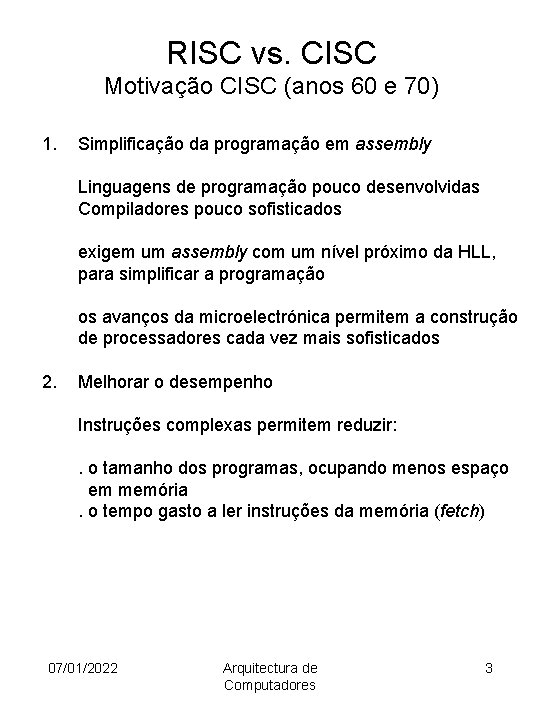

RISC vs. CISC Motivação CISC (anos 60 e 70) 1. Simplificação da programação em assembly Linguagens de programação pouco desenvolvidas Compiladores pouco sofisticados exigem um assembly com um nível próximo da HLL, para simplificar a programação os avanços da microelectrónica permitem a construção de processadores cada vez mais sofisticados 2. Melhorar o desempenho Instruções complexas permitem reduzir: . o tamanho dos programas, ocupando menos espaço em memória. o tempo gasto a ler instruções da memória (fetch) 07/01/2022 Arquitectura de Computadores 3

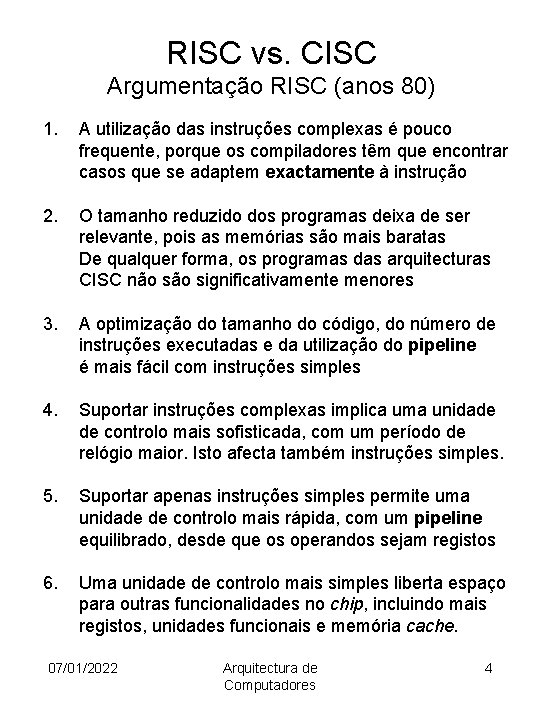

RISC vs. CISC Argumentação RISC (anos 80) 1. A utilização das instruções complexas é pouco frequente, porque os compiladores têm que encontrar casos que se adaptem exactamente à instrução 2. O tamanho reduzido dos programas deixa de ser relevante, pois as memórias são mais baratas De qualquer forma, os programas das arquitecturas CISC não significativamente menores 3. A optimização do tamanho do código, do número de instruções executadas e da utilização do pipeline é mais fácil com instruções simples 4. Suportar instruções complexas implica uma unidade de controlo mais sofisticada, com um período de relógio maior. Isto afecta também instruções simples. 5. Suportar apenas instruções simples permite uma unidade de controlo mais rápida, com um pipeline equilibrado, desde que os operandos sejam registos 6. Uma unidade de controlo mais simples liberta espaço para outras funcionalidades no chip, incluindo mais registos, unidades funcionais e memória cache. 07/01/2022 Arquitectura de Computadores 4

Pipeline Sobreposição da execução de diferentes fases de diferentes instruções. A execução de uma instrução pode ser, geralmente, dividida em 5 fases: 1. Leitura da instrução – fetch (Fe) 2. Descodificação e leitura de registos (ID) 3. Execução da operação ou cálculo do endereço (Ex) 4. Acesso à memória (Mem) 5. Escrita do resultado num registo (WB) Processador sem pipeline : Só quando todas as fases de uma instrução terminam, começa a próxima instrução O ciclo do relógio deve ser tão longo quanto a instrução mais lenta Processador com pipeline : A execução das diferentes fases das várias instruções podem ser encadeadas no tempo. O ciclo do relógio deve ser tão longo quanto a fase mais longa 07/01/2022 Arquitectura de Computadores 5

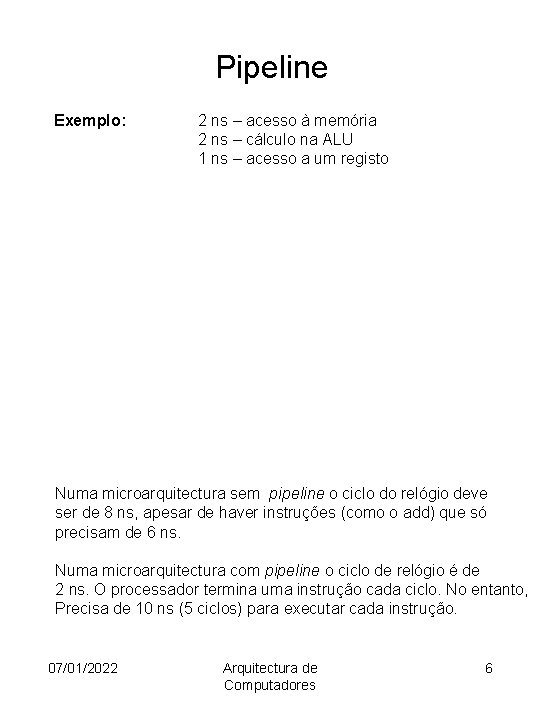

Pipeline Exemplo: 2 ns – acesso à memória 2 ns – cálculo na ALU 1 ns – acesso a um registo Numa microarquitectura sem pipeline o ciclo do relógio deve ser de 8 ns, apesar de haver instruções (como o add) que só precisam de 6 ns. Numa microarquitectura com pipeline o ciclo de relógio é de 2 ns. O processador termina uma instrução cada ciclo. No entanto, Precisa de 10 ns (5 ciclos) para executar cada instrução. 07/01/2022 Arquitectura de Computadores 6

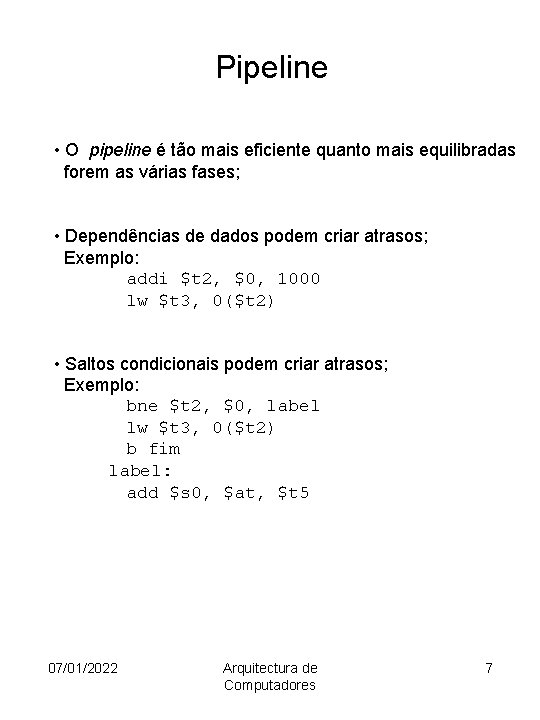

Pipeline • O pipeline é tão mais eficiente quanto mais equilibradas forem as várias fases; • Dependências de dados podem criar atrasos; Exemplo: addi $t 2, $0, 1000 lw $t 3, 0($t 2) • Saltos condicionais podem criar atrasos; Exemplo: bne $t 2, $0, label lw $t 3, 0($t 2) b fim label: add $s 0, $at, $t 5 07/01/2022 Arquitectura de Computadores 7

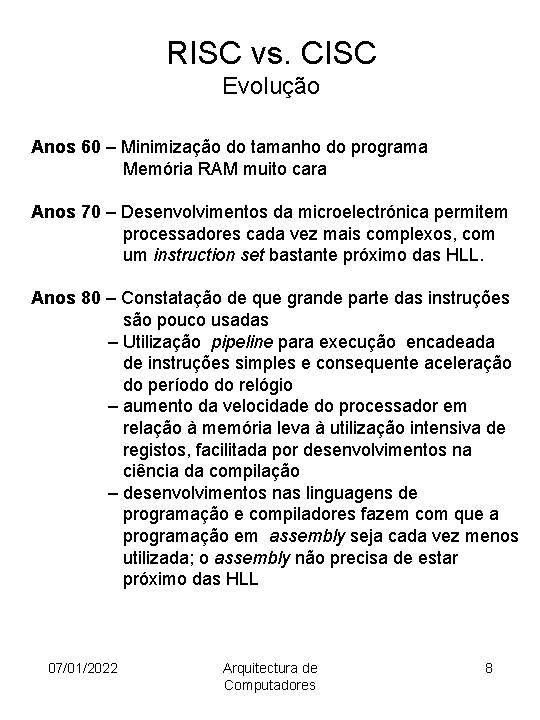

RISC vs. CISC Evolução Anos 60 – Minimização do tamanho do programa Memória RAM muito cara Anos 70 – Desenvolvimentos da microelectrónica permitem processadores cada vez mais complexos, com um instruction set bastante próximo das HLL. Anos 80 – Constatação de que grande parte das instruções são pouco usadas – Utilização pipeline para execução encadeada de instruções simples e consequente aceleração do período do relógio – aumento da velocidade do processador em relação à memória leva à utilização intensiva de registos, facilitada por desenvolvimentos na ciência da compilação – desenvolvimentos nas linguagens de programação e compiladores fazem com que a programação em assembly seja cada vez menos utilizada; o assembly não precisa de estar próximo das HLL 07/01/2022 Arquitectura de Computadores 8

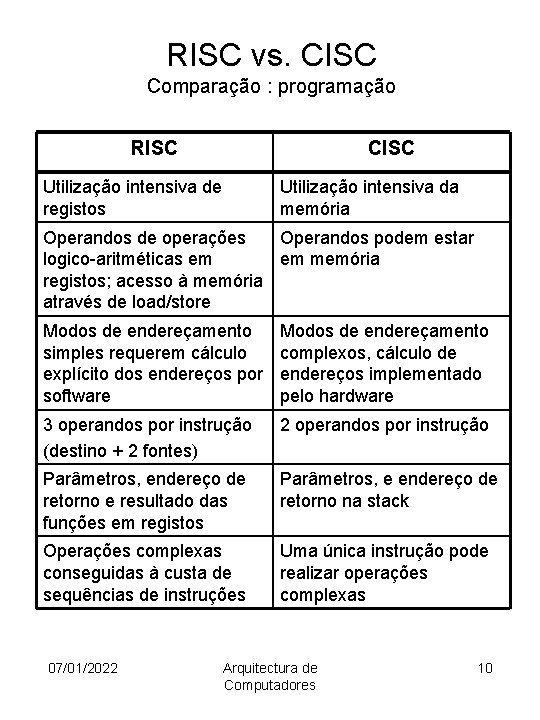

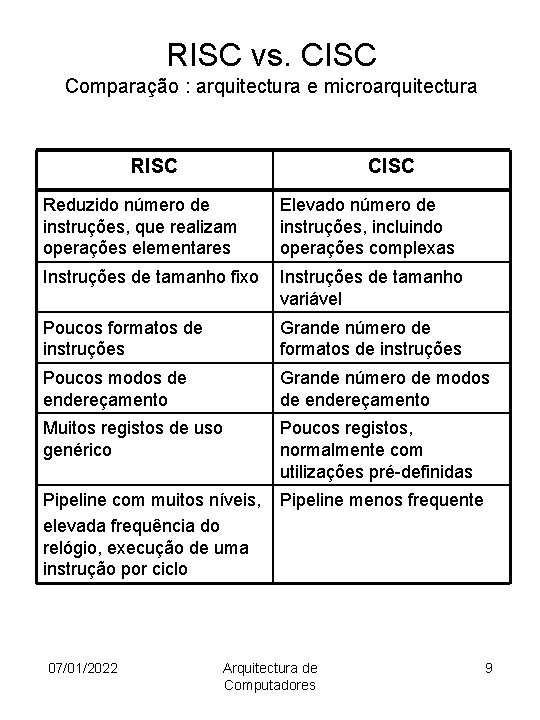

RISC vs. CISC Comparação : arquitectura e microarquitectura RISC CISC Reduzido número de instruções, que realizam operações elementares Elevado número de instruções, incluindo operações complexas Instruções de tamanho fixo Instruções de tamanho variável Poucos formatos de instruções Grande número de formatos de instruções Poucos modos de endereçamento Grande número de modos de endereçamento Muitos registos de uso genérico Poucos registos, normalmente com utilizações pré-definidas Pipeline com muitos níveis, elevada frequência do relógio, execução de uma instrução por ciclo Pipeline menos frequente 07/01/2022 Arquitectura de Computadores 9

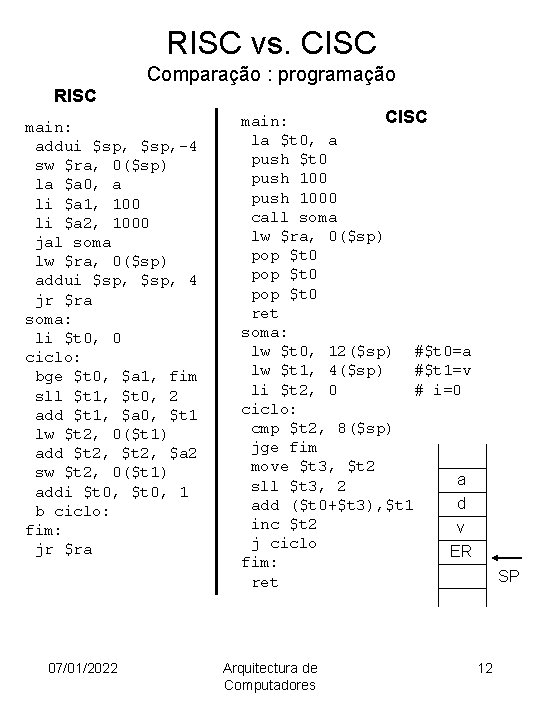

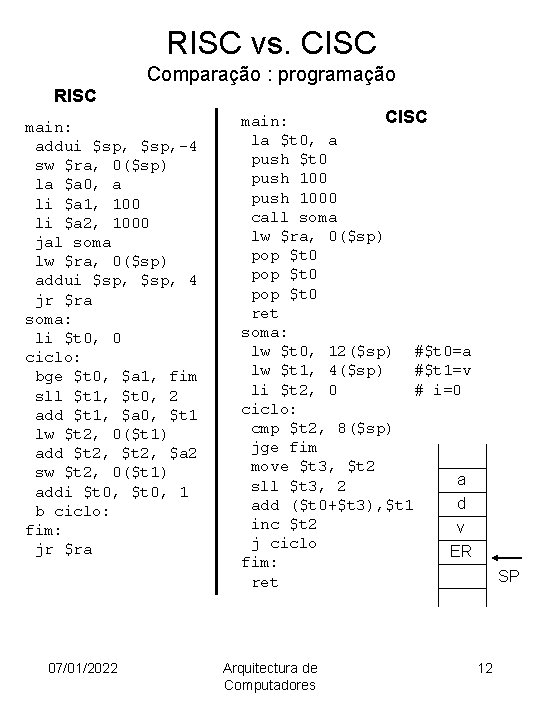

RISC vs. CISC Comparação : programação RISC CISC Utilização intensiva de registos Utilização intensiva da memória Operandos de operações Operandos podem estar logico-aritméticas em em memória registos; acesso à memória através de load/store Modos de endereçamento simples requerem cálculo explícito dos endereços por software Modos de endereçamento complexos, cálculo de endereços implementado pelo hardware 3 operandos por instrução (destino + 2 fontes) 2 operandos por instrução Parâmetros, endereço de retorno e resultado das funções em registos Parâmetros, e endereço de retorno na stack Operações complexas conseguidas à custa de sequências de instruções Uma única instrução pode realizar operações complexas 07/01/2022 Arquitectura de Computadores 10

![RISC vs CISC Comparação programação Exemplo main int a100 soma a RISC vs. CISC Comparação : programação Exemplo main () { int a[100]; soma (a,](https://slidetodoc.com/presentation_image_h2/5f03234dbae69c40e75b7e7f33c4eeae/image-11.jpg)

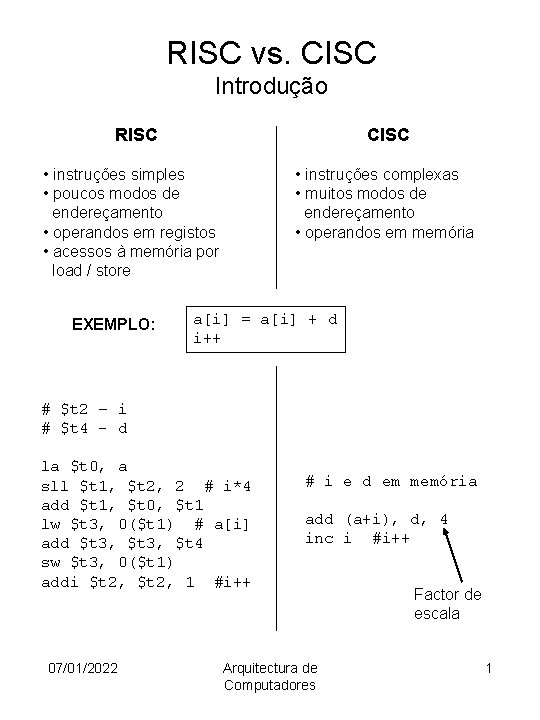

RISC vs. CISC Comparação : programação Exemplo main () { int a[100]; soma (a, 1000); } void soma (int *a, int d, int v) { int i; for (i=0 ; i<d ; i++) a[i] = a[i] + v; } Codificar em assembly duma máquina CISC com as seguintes características: • Apenas 2 operandos por instrução • Um dos operandos pode estar em memória • Apenas 7 registos: $t 0. . $t 5 , $sp • Passagem de parâmetros e endereço de retorno na stack • Modos de endereçamento adicionais: Mem[$reg 1 + $reg 2] 07/01/2022 Arquitectura de Computadores 11

RISC vs. CISC Comparação : programação RISC main: addui $sp, -4 sw $ra, 0($sp) la $a 0, a li $a 1, 100 li $a 2, 1000 jal soma lw $ra, 0($sp) addui $sp, 4 jr $ra soma: li $t 0, 0 ciclo: bge $t 0, $a 1, fim sll $t 1, $t 0, 2 add $t 1, $a 0, $t 1 lw $t 2, 0($t 1) add $t 2, $a 2 sw $t 2, 0($t 1) addi $t 0, 1 b ciclo: fim: jr $ra 07/01/2022 CISC main: la $t 0, a push $t 0 push 1000 call soma lw $ra, 0($sp) pop $t 0 ret soma: lw $t 0, 12($sp) #$t 0=a lw $t 1, 4($sp) #$t 1=v li $t 2, 0 # i=0 ciclo: cmp $t 2, 8($sp) jge fim move $t 3, $t 2 a sll $t 3, 2 d add ($t 0+$t 3), $t 1 inc $t 2 v j ciclo ER fim: ret Arquitectura de Computadores SP 12