Arquitetura de Computadores 1 Prof Larissa Natlia V

- Slides: 57

Arquitetura de Computadores 1 Profª. Larissa Natália V. Carneiro https: //sites. google. com/site/proflarissacarneiro TANENBAUM, Andrew S. Organização Estruturada de computadores 4 a Edição. Rio de Janeiro: Printice-Hall do Brasil, 2001 Arquitetura de Computadores 1 2009

Processador n É responsável pela atividade fim do sistema: q q q n Computar; Calcular; Processar. São projetados para que em um único invólucro tenha todos os elementos necessários. Arquitetura de Computadores 1 2009

Processador n Todo processador é construído para realizar as seguintes operações: q q n Somar, subtrair, multiplicar ou dividir números (operações aritméticas); And, or, xor, nand (operações lógicas); Mover um dado de um local para outro (operação de movimento de dados); Transferir um valor para um dispositivo de saída ou vice-versa (Operação de E/S). Essas operações e a localização tem que estar representadas por sinais elétricos. Arquitetura de Computadores 1 2009

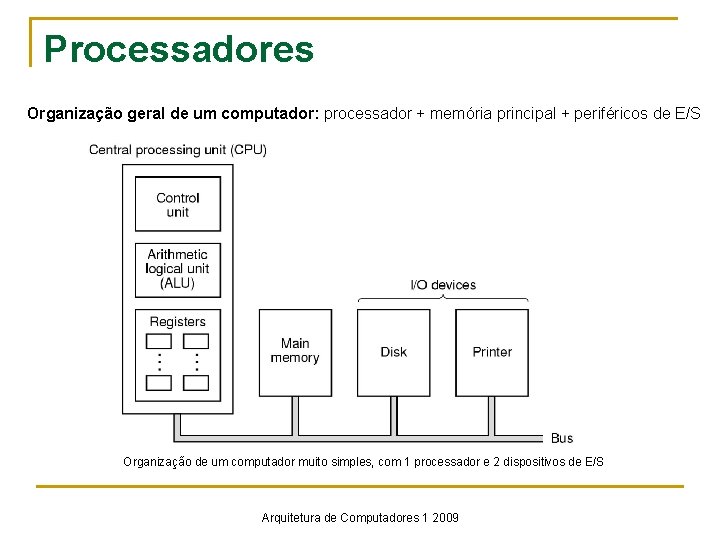

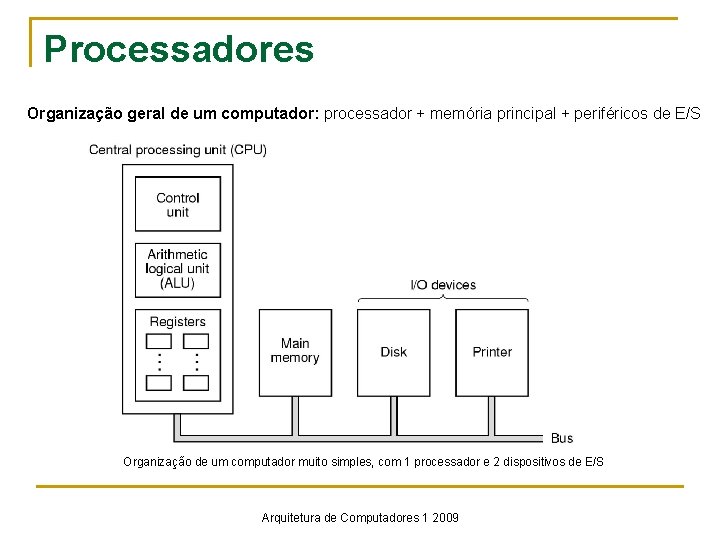

Processadores Organização geral de um computador: processador + memória principal + periféricos de E/S Organização de um computador muito simples, com 1 processador e 2 dispositivos de E/S Arquitetura de Computadores 1 2009

Processadores n O processador é o "cérebro" do computador. q q Sua função é executar os programas armazenados na memória principal. O processador busca cada instrução na memória, examina-a e executa uma após outra. Arquitetura de Computadores 1 2009

Processadores n É composto por: q q q Unidade de controle – responsável por buscar instruções na memória principal e determinar seu tipo; Unidade Aritmética e Lógica(ULA) – dispositivo principal que realiza as operações primitivas; Barramento interno – interligação entre estes componentes. Arquitetura de Computadores 1 2009

Processadores n É composto por: q q Registradores de controle – armazenam bits com funções específicas decorrentes das operações aritméticas realizadas; Registradores de dados – armazenam dados utilizados pela ULA ou resultados parciais das operações; Arquitetura de Computadores 1 2009

Processadores n O Registrador mais importante é o Contador de programa (PC – Program Counter) que indica a próxima instrução a ser buscada para execução. n n O nome é enganoso por ele não ter nada a ver com contar. Outro importante é o registrado de instrução – contém a instrução que está sendo executada no momento em questão. Arquitetura de Computadores 1 2009

Componentes de um processador n Unidade Lógica Aritmética (ULA): q q n Realiza as operações necessárias a execução das instruções; Possui duas entradas de dados; Entradas conectam a saída pelos barramentos; Recebe sinais de controle que determinam a operação. Unidade de Controle: q busca e define o tipo de cada instrução. Arquitetura de Computadores 1 2009

Componentes de um processador n Registradores: q q q memória pequena de alta velocidade; em geral todos de tamanhos iguais (16, 32, 64 ou 128 bits – depende do tamanho da palavra); Program Counter (PC): armazena o endereço da próxima instrução; Registrador de Instruções (IR): armazena instrução que está sendo executada; Outros registradores de propósito geral ou específico. Arquitetura de Computadores 1 2009

(Influência do tamanho da palavra) n n n Significa que suas áreas funcionais só armazenam, processam e transferem dados com X bits de tamanho. Um tamanho maior ou menor da palavra acarreta diferenças acentuadas de desempenho do processador. Hoje, os processadores (e seus registradores) são fabricados com 32 bits ou 64 bits. Arquitetura de Computadores 1 2009

(Influência do tamanho da palavra) n Nos processadores antigos o barramento de dados externo tinha uma largura igual ao da palavra. n Atualmente o barramento tem largura maior que a palavra (cache L 1 e L 2). n Existem barramentos com 128 bits. Arquitetura de Computadores 1 2009

Barramentos n Interligam os componentes: q q conjunto de “fios” (canais de comunicação) paralelos que permitem a transmissão de dados, endereços, sinais de controle e instruções; existem barramentos internos e externos ao processador. Arquitetura de Computadores 1 2009

Barramentos n Barramentos Internos: q n Ligam a CPU aos equipamentos internos ao Gabinete Barramentos Externos: q Ligam a CPU aos equipamentos externos ao Gabinete Arquitetura de Computadores 1 2009

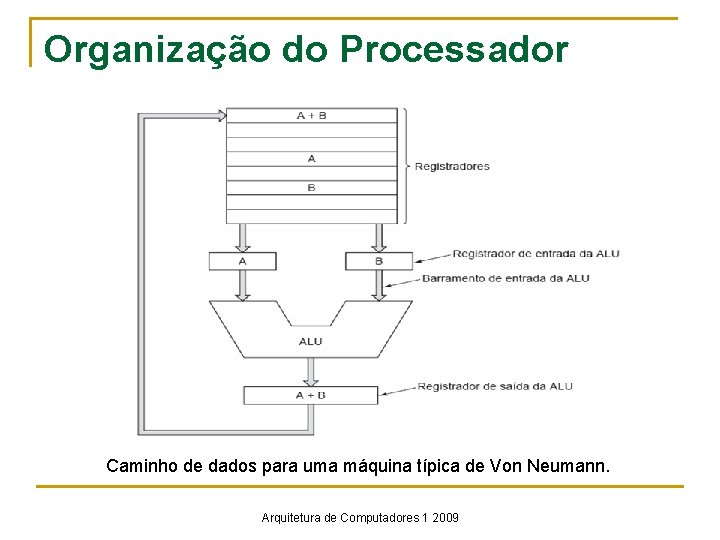

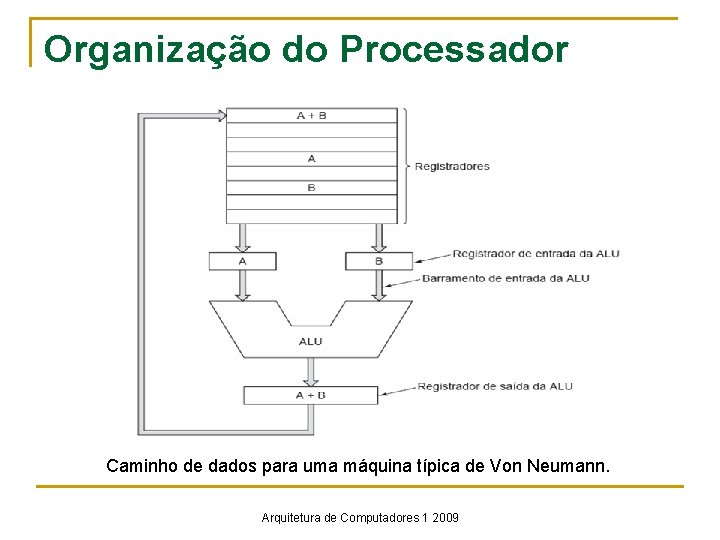

Organização do Processador Caminho de dados para uma máquina típica de Von Neumann. Arquitetura de Computadores 1 2009

Função de controle n Dispositivos da área funcional de controle: q q q q Unidade de controle – UC; Relógio ou clock; Registrador de instrução - RI ou IR; Contador de instrução - CI ou PC ou IP; Decodificador de instrução; Registrador de dados da memória – RDM; Registrador de endereço de memória – REM. Arquitetura de Computadores 1 2009

Unidade de controle n Ciclo de busca da instrução: q q q Busca a instrução que será executada; Armazena no registrador apropriado; Interpretação das ações a serem desencadeadas. Arquitetura de Computadores 1 2009

Unidade de controle n Ciclo de execução da instrução: q q Geração de sinais de controle apropriados; Sinais de controle enviados aos componentes do sistema (internos/externo); Arquitetura de Computadores 1 2009

Unidade de controle n n n É o dispositivo mais complexo. Possui a lógica para realizar a movimentação de dados e de instruções. Emite sinais de controle em instantes determinados conforme a programação. Arquitetura de Computadores 1 2009

Relógio n n n Dispositivo com a finalidade de sincronização da mudança de estado (0, 1). Gerador de pulsos cuja duração é chamada de ciclo. A frequência é a quantidade de ciclos por segundo de um relógio e é medida em Hertz: q q 1 Hz = 1 ciclo/s 1. 000 Hz = 1 KHz 1. 000 k. Hz = 1. 000 = 1 MHz 1. 000 MHz = 1. 000 = 1 GHz Arquitetura de Computadores 1 2009

Registrador de instrução Armazena a instrução a ser executada Arquitetura de Computadores 1 2009

Contador de instruções n Registrador que armazena o endereço da próxima função a ser executada. n Assim que a instrução é buscada na memória, o sistema automaticamente efetiva a modificação do conteúdo da CI para armazenar o endereço da próxima instrução. Arquitetura de Computadores 1 2009

Decodificador de instruções Dispositivo utilizado para identificar a operação a ser realizada, correlacionada à instrução cujo o código de operação foi decodificado. Arquitetura de Computadores 1 2009

Registrador de dados de memória e registrador de endereços de n RDM: memória q q n Utilizados pelo processador e memória para comunicação e transferência de informações; Possui o tamanho igual ao barramento de dados (32, 64 ou 128 bits). REM: q Possui tamanho igual ao dos endereços de memória (consequentemente dos barramentos de endereços) Arquitetura de Computadores 1 2009

Organização do Processador n Caminho de dados: q q q Parte do processador com registradores (1 a 32), ULA e barramentos Dois registradores armazenam as duas entradas (A e B) da ULA A saída da ULA é conectada a 1 dos registradores Importante: A velocidade do caminho de dados determina a velocidade do computador Arquitetura de Computadores 1 2009

Execução de Instruções (pelo processador) n A CPU executa cada instrução em uma série de pequenas etapas. (Ciclo Buscar-Decodificar-Executar 1 instrução) 1. Busca próxima instrução na memória e armazena no IR. 2. Atualiza Contador de instrução PC para apontar para a próxima instrução. 3. Determina tipo de instrução armazenada no IR 4. Se a instrução usar uma palavra na memória, determinar onde essa palavra está. 5. Trazer a palavra para dentro de outro registrador da CPU, se necessário. 6. Executa instrução 7. Volta ao passo 1 para iniciar a execução da instrução seguinte Arquitetura de Computadores 1 2009

Execução de Instruções (pelo processador) n n É fundamental para operação de todos os computadores. É possível escrever um programa que imite o ciclo buscar-decodificar-executar. Um programa que busca, examina e executa as instruções de outro programa é denominado interpretador. Permite que uma família de computadores com a mesma arquitetura, mas com muitas implementações diferentes que poderiam executar o mesmo programa sendo diferente apenas em preço e velocidade. Arquitetura de Computadores 1 2009

Execução de instrução n Outras vantagens da interpretação: q q q Capacidade de corrigir em campo instruções implementadas incorretamente ou até compensar deficiências de projeto no hardware básico; Oportunidade de acrescentar novas instruções a custo mínimo, mesmo após a entrega da máquina; Projeto estruturado que permite desenvolvimento, teste e documentação eficientes de instruções complexas. Arquitetura de Computadores 1 2009

RISC versus CISC n RISC - Reduced Instruction Set Computer (Computadores com instruções reduzidas) q q Nova tecnologia para máquinas de alta performance (não havia preocupação compatibilidade) Máquina com conjunto reduzido de instruções básicas em hardware (~50 instruções) q q Uso de chips processadores VLSI (Very Large Scale Integration “integração em larga escala”) sem interpretação Demais instruções eram geradas por combinação das instruções básicas de hardware Arquitetura de Computadores 1 2009

RISC versus CISC - Complex Instruction Set Computer (Computador com Instruções Complexas) n q q q Tecnologia mais antiga e usada para famílias de computadores compatíveis a nível de software. Número maior de instruções (~ 200 a 300 instruções). Uso extensivo de interpretação. Arquitetura de Computadores 1 2009

RISC versus CISC n Argumento: q Mesmo que uma máquina RISC precisasse de 4 ou 5 instruções para fazer o que uma máquina CISC faria com apenas 1 instrução, se a instrução RISC fosse 10 vezes mais rápida (só hardware) a máquina RISC vencia. Arquitetura de Computadores 1 2009

RISC versus CISC n Questão: Porque então a tecnologia RISC não suplantou a CISC ? q q Problemas de compatibilidade com máquinas antigas com softwares já desenvolvidos Aparecimento de soluções híbridas: Por exemplo, a INTEL usa RISC para instruções de uso mais freqüentes (Núcleo RISC) e interpretação para instruções mais complexas e de uso menos freqüentes. Arquitetura de Computadores 1 2009

Princípios de Projeto para Computadores Modernos n Todas as instruções são diretamente executadas por hardware: q q q Não existe o nível de microinstrução (eliminação da microprogramação); Eliminar um nível de interpretação da alta velocidade à maioria das instruções Para máquina com filosofia CISC as instruções, em geral menos freqüentes, que não existem em hardware, são interpretadas; Arquitetura de Computadores 1 2009

Princípios de Projeto para Computadores Modernos n Maximizar a Taxa à qual as instruções são executadas: q q q Iniciar o máximo possível de instruções por segundo; Uso de paralelismo: execução de várias instruções lentas ao mesmo tempo; Embora as instruções sejam encontradas em ordem no programa, nem sempre são executadas dessa forma. Arquitetura de Computadores 1 2009

Princípios de Projeto para Computadores Modernos n As instruções precisam ser facilmente decodificadas q q n decodificação influencia na velocidade de execução das instruções decodificação determina os recursos a serem usados na execução das instruções Somente as Instruções de Load (leitura) e Store (Armazenamento) devem referenciar a Memória q q Acesso a memória é mais lento Instruções que acessam a memória podem ser intercaladas com outras instruções Arquitetura de Computadores 1 2009

Princípios de Projeto para Computadores Modernos n Projetar uma máquina com muitos registradores (>= 32) q q n Palavras de memória devem permanecer nos registradores o maior tempo possível; Falta de registradores pode obrigar a buscar varias vezes a mesma palavra da memória. Solução para aumentar a velocidade do processador: Uso de paralelismo. q q a nível de instrução: 1 único processador deve executar mais instruções por segundo; a nível de processadores: vários processadores trabalhando juntos na solução do mesmo problema. Arquitetura de Computadores 1 2009

Paralelismo ao Nível de Instruções Maior gargalo para a velocidade de execução de instruções é o acesso a memória n Execução em Pipeline O processamento em pipeline divide a execução de instruções em várias partes, cada uma das quais tratada por um hardware dedicado exclusivamente a ela. Arquitetura de Computadores 1 2009

Paralelismo ao Nível de Instruções n Funcionamento de um pipeline de 5 estágios q q q O estágio 1 busca a instrução da memória e armazena num buffer até chegar a hora de executa-la; No estágio 2 ocorre a decodificação da instrução, determinando tipo e operando; No estágio 3 ocorre a busca dos operados na memória ou nos registradores; No estágio 4 temos a execução - passagem pelo caminho de dados; No estágio 5 o resultado do processamento é escrito num registrador. Arquitetura de Computadores 1 2009

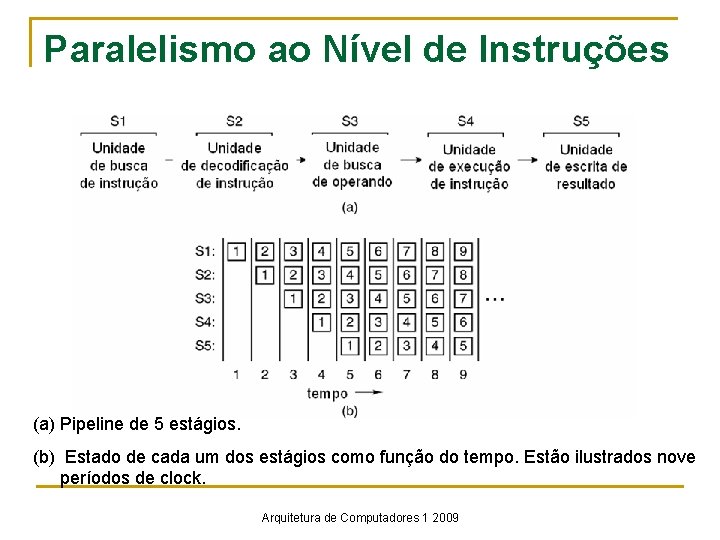

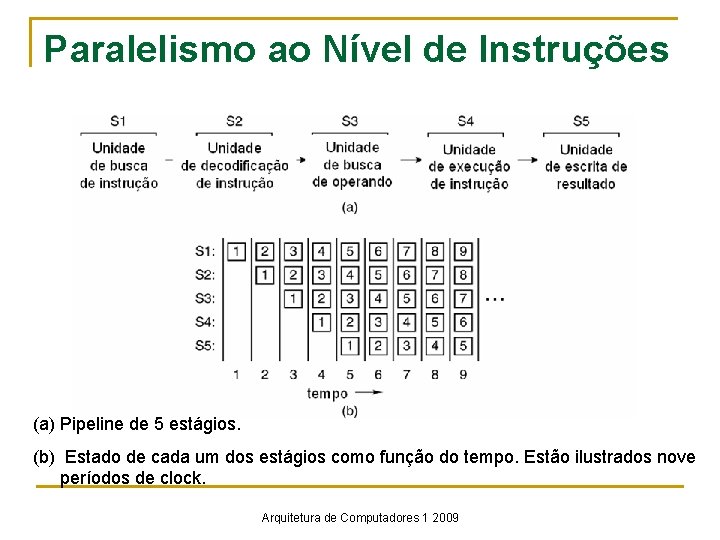

Paralelismo ao Nível de Instruções (a) Pipeline de 5 estágios. (b) Estado de cada um dos estágios como função do tempo. Estão ilustrados nove períodos de clock. Arquitetura de Computadores 1 2009

Paralelismo ao Nível de Instruções n A idéia básica do pipeline é a mesma de uma linha de produção em série. Vários processamentos estão sendo executados ao mesmo tempo. n Obs. : Quando uma instrução leva mais tempo em um estágio do que o normal, dar- se o nome de Quebra de Pipeline. Arquitetura de Computadores 1 2009

Paralelismo ao Nível de Instruções n Tempo de execução de uma instrução q n Tempo Total de uma execução de Pipeline q n É o tempo referente ao inicio do primeiro estágio de uma instrução até o término do último estágio desta instrução. É o tempo referente ao inicio do primeiro estágio de uma instrução até o término do último estágio de todas as instruções. Atraso do Pipeline q É a diferença entre o Pipeline com quebra e o mesmo Pipeline sem quebra. Arquitetura de Computadores 1 2009

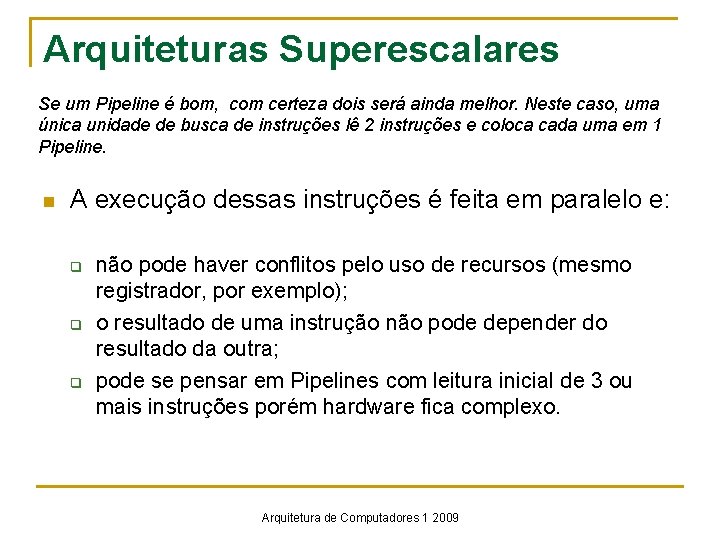

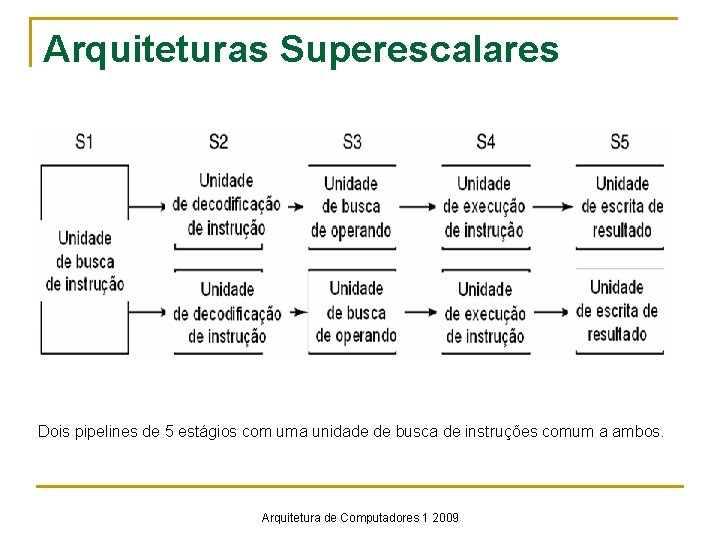

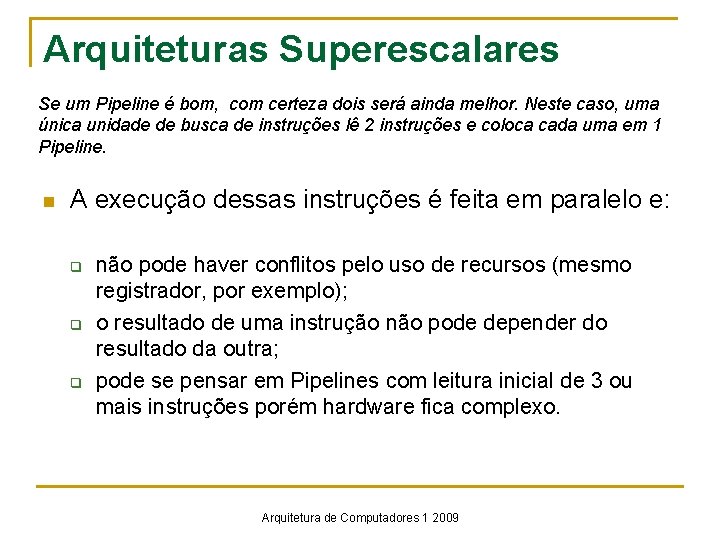

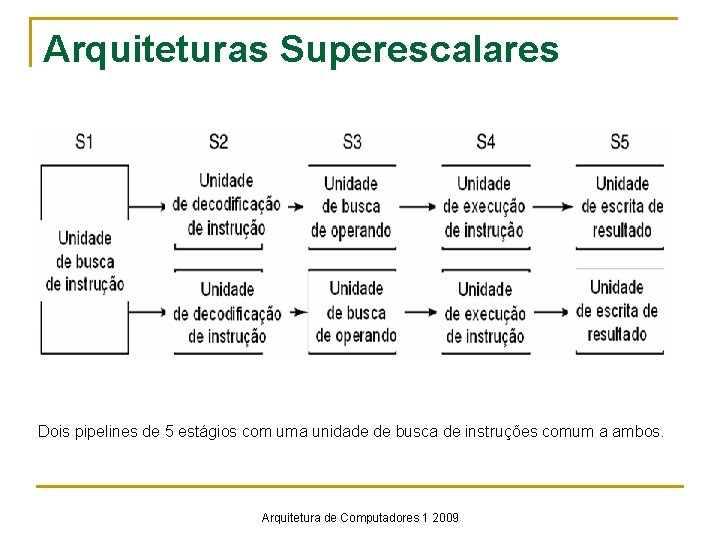

Arquiteturas Superescalares Se um Pipeline é bom, com certeza dois será ainda melhor. Neste caso, uma única unidade de busca de instruções lê 2 instruções e coloca cada uma em 1 Pipeline. n A execução dessas instruções é feita em paralelo e: q q q não pode haver conflitos pelo uso de recursos (mesmo registrador, por exemplo); o resultado de uma instrução não pode depender do resultado da outra; pode se pensar em Pipelines com leitura inicial de 3 ou mais instruções porém hardware fica complexo. Arquitetura de Computadores 1 2009

Arquiteturas Superescalares Dois pipelines de 5 estágios com uma unidade de busca de instruções comum a ambos. Arquitetura de Computadores 1 2009

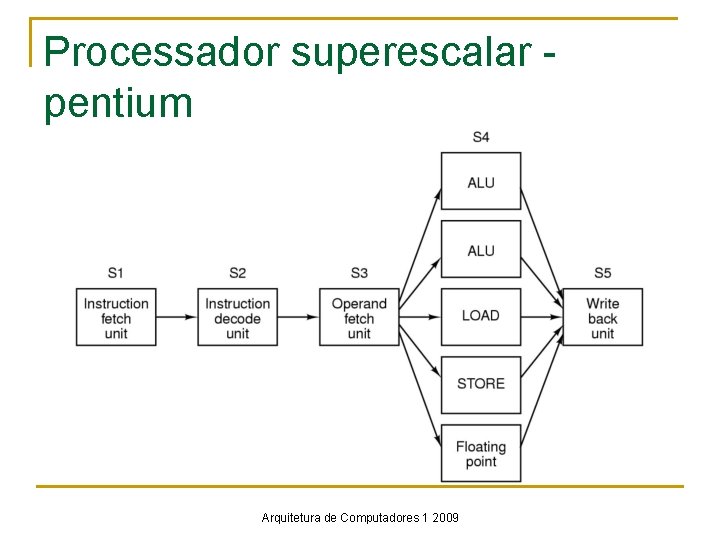

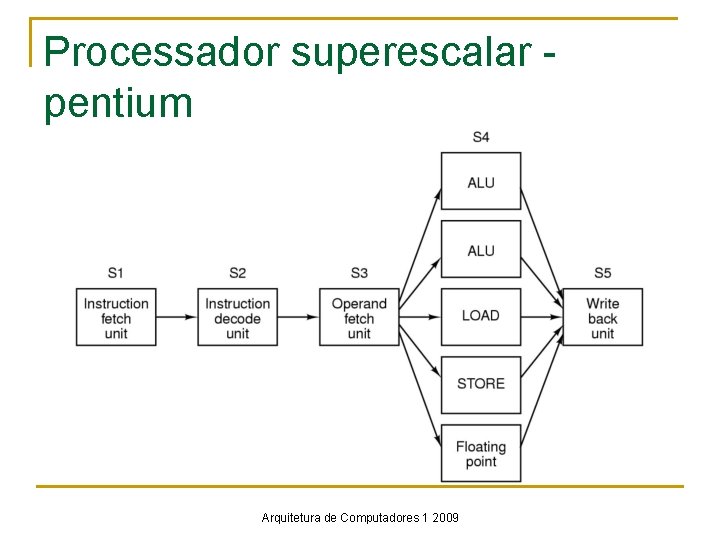

Processador superescalar - pentium Arquitetura de Computadores 1 2009

Arquiteturas Superescalares n A definição superescalar agora é usada para descrever processadores que executam múltiplas instruções e um único ciclo do relógio. Arquitetura de Computadores 1 2009

Paralelismo ao Nível do Processador n A medida que os processadores vão ficando mais rápido: q q Aparecem limitações de ordem física (velocidade nos “fios” (canais de comunicação)); Maior produção de calor pelo chip (problema para dissipar essa energia). Arquitetura de Computadores 1 2009

Paralelismo ao Nível do Processador n Operação do processador em pipeline ou em superescalar possibilita ganhos de 5 a ~10 vezes. n Para ganhos maiores, 50 -100 ou mais vezes, deve-se projetar computador com mais de 1 processador. Arquitetura de Computadores 1 2009

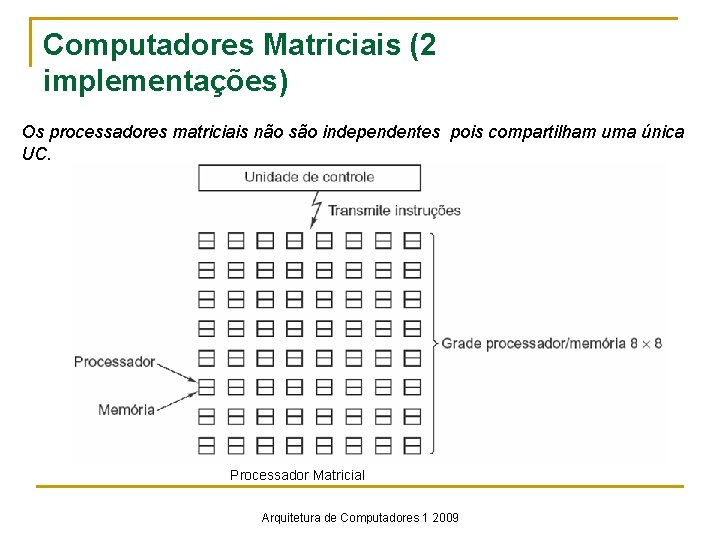

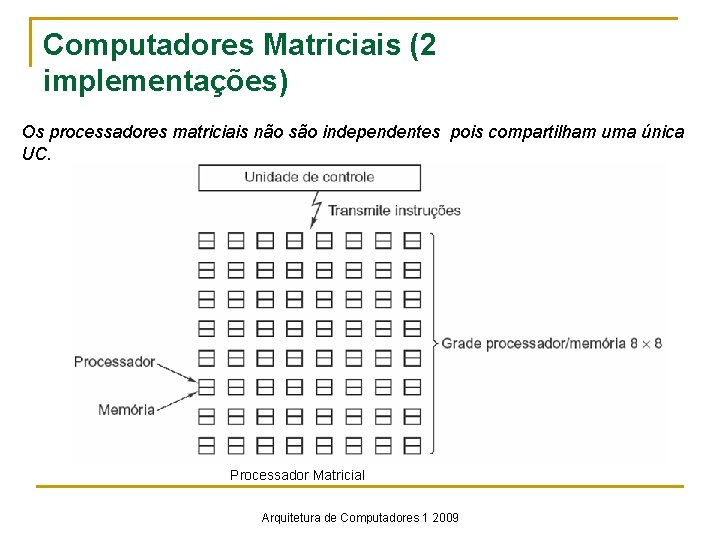

Computadores Matriciais (2 implementações) n Processador matricial: q q composto de grande número de processadores idênticos; cada processador executa a mesma seqüência de instruções sobre diferentes conjuntos de dados; tem uma única unidade de controle; tem uma ULA para cada processador. Arquitetura de Computadores 1 2009

Computadores Matriciais (2 implementações) Os processadores matriciais não são independentes pois compartilham uma única UC. Processador Matricial Arquitetura de Computadores 1 2009

Computadores Matriciais (2 implementações) n Processador vetorial: q q q muito parecido com processador matricial; operações aritméticas são executadas numa única ULA, que opera em paralelo; operandos são colocados em um registro vetorial para serem processados na ULA. Arquitetura de Computadores 1 2009

Computadores Matriciais (2 implementações) n Processador matricial x vetorial q q programação para o matricial voltada ao paralelismo (+difícil); processador matricial é, em geral, mais rápido (principalmente para repetição de um mesmo processamento em vários "pedaços" dos dados); processador vetorial se adapta a processamentos paralelos e não paralelos; hardware do matricial é mais caro (muitas ULAs). Arquitetura de Computadores 1 2009

Multiprocessadores n n n É composto de vários processadores independentes. compartilham uma mesma memória por um Barramento principal (a). ou compartilham uma memória e tem memórias locais (b). q q q executam processamentos locais; liberam trafego do barramento principal; é necessário gerenciar conflitos; Arquitetura de Computadores 1 2009

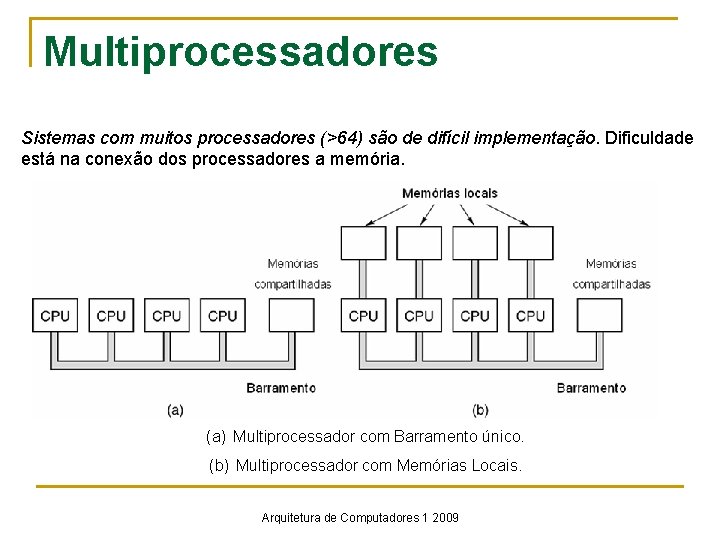

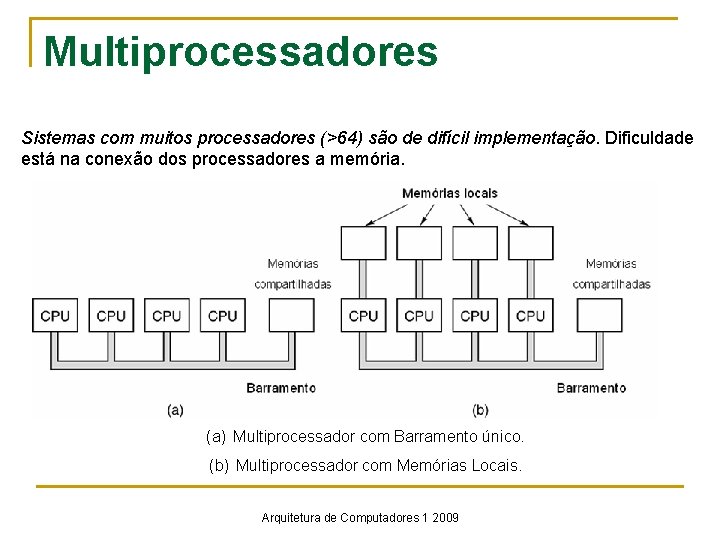

Multiprocessadores Sistemas com muitos processadores (>64) são de difícil implementação. Dificuldade está na conexão dos processadores a memória. (a) Multiprocessador com Barramento único. (b) Multiprocessador com Memórias Locais. Arquitetura de Computadores 1 2009

Multi(computadores) n n n Sistemas com um grande número de computadores interconectados. Não existe nenhum tipo de memória comum sendo compartilhada. Comunicação entre computadores é feita através de troca de mensagens a uma velocidade bem alta. Arquitetura de Computadores 1 2009

Multi(computadores) n n n Computador pode não precisar estar ligados diretamente com todos os outros (uso de topologias em árvore, anéis, etc. . ). Mensagens são roteadas do computador fonte para o destino (usando computadores intermediários). Existem em operação sistemas multicomputadores com cerca de 10000 computadores. Arquitetura de Computadores 1 2009

Multi(computadores) n Importante: q q Como sistemas multiprocessadores são mais fáceis de programar e sistemas multicomputadores são mais fáceis de construir, existem sistemas híbridos. Tais computadores dão a ilusão de compartilhamento de memória, sem arcar com o ônus de implementá-la diretamente. Arquitetura de Computadores 1 2009

Exercício!!! n Faça uma leitura e esboce uma idéia a respeito das seguintes tecnologias envolvendo processadores: q Tecnologia Dual Core n n n Core 2 Duo Core 2 Quad Core 2 Solo (portáteis) Core 2 Extreme Core i 3, i 5 e i 7 Arquitetura de Computadores 1 2009