Alapvet digitlis logikai ramkrk Integrlt ramkr IC Integrated

- Slides: 37

Alapvető digitális logikai áramkörök Integrált áramkör (IC, Integrated Circuit, chip, lapka) 5 x 5 mm 2 szilícium darab kerámia vagy műanyag lapon (tokban), lábakkal (pins). Négy alaptípus: • SSI (Small Scale Integrated 1 -10 kapu), • MSI (Medium Scale. . . , 10 -100 kapu), • LSI (Large Scale. . . , 100 -100 000 kapu), • VLSI (Very Large Scale. . . , > 100 000 kapu). Máté: Architektúrák 3. előadás 1

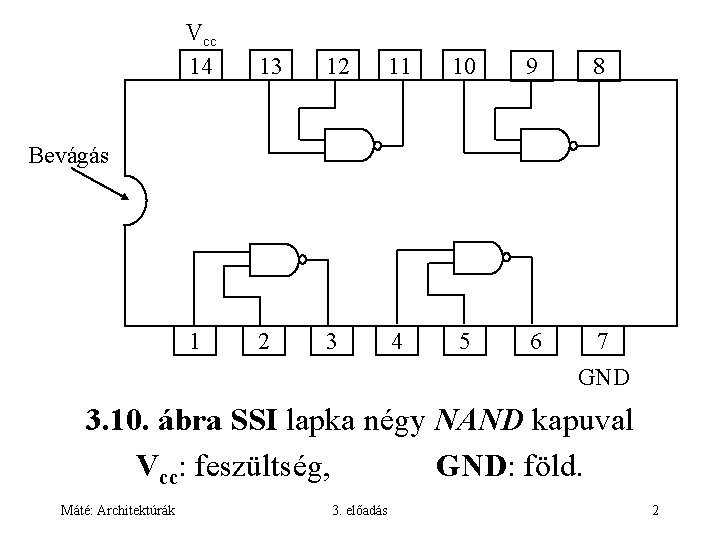

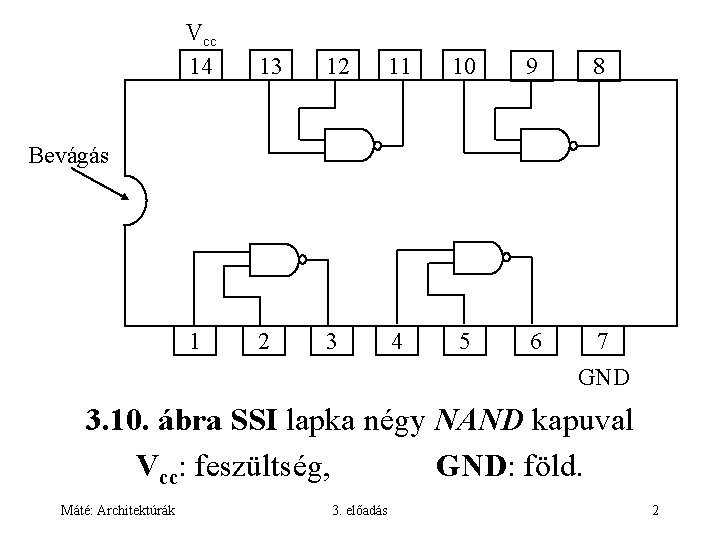

Vcc 14 13 12 11 10 9 8 1 2 3 4 5 6 7 GND Bevágás 3. 10. ábra SSI lapka négy NAND kapuval Vcc: feszültség, GND: föld. Máté: Architektúrák 3. előadás 2

Kívánalom: sok kapu – kevés láb Kombinációs áramkörök Definíció: A kimeneteket egyértelműen meghatározzák a pillanatnyi bemenetek. Máté: Architektúrák 3. előadás 3

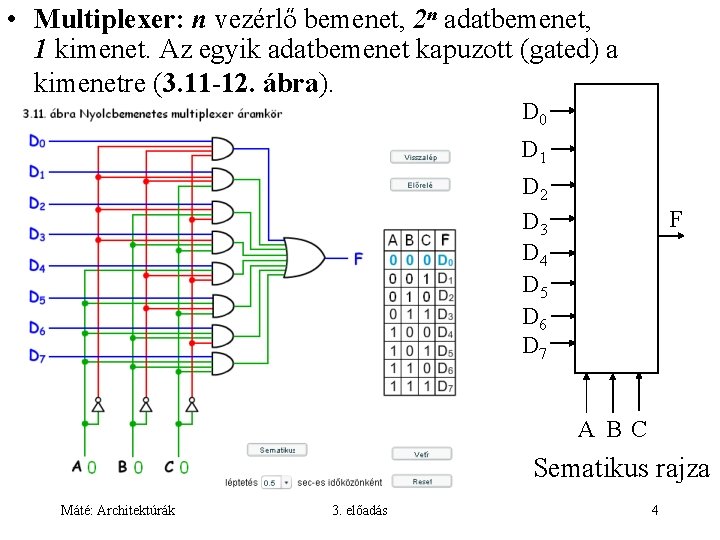

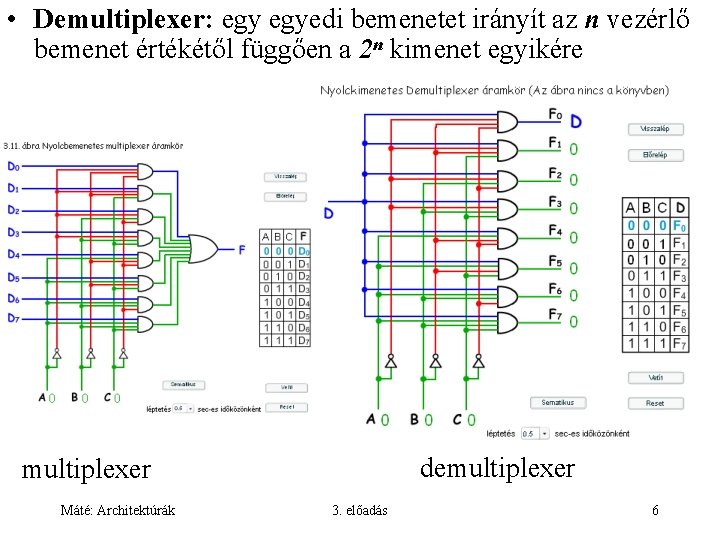

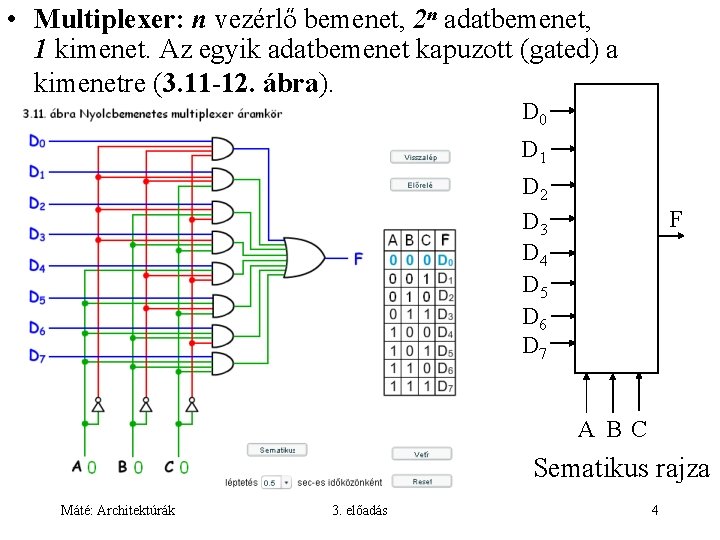

• Multiplexer: n vezérlő bemenet, 2 n adatbemenet, 1 kimenet. Az egyik adatbemenet kapuzott (gated) a kimenetre (3. 11 -12. ábra). D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 F A BC Sematikus rajza Máté: Architektúrák 3. előadás 4

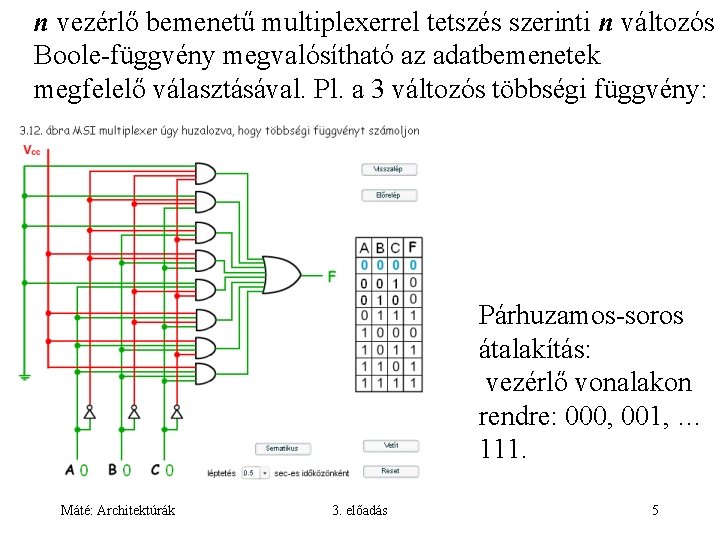

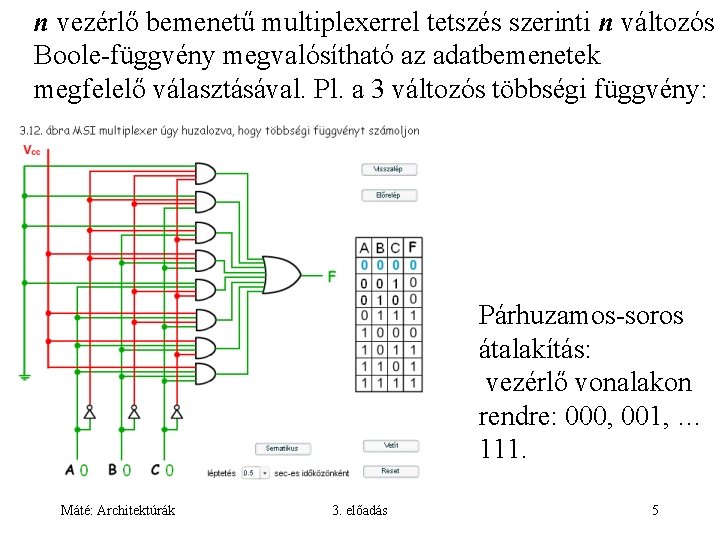

n vezérlő bemenetű multiplexerrel tetszés szerinti n változós Boole-függvény megvalósítható az adatbemenetek megfelelő választásával. Pl. a 3 változós többségi függvény: Párhuzamos-soros átalakítás: vezérlő vonalakon rendre: 000, 001, … 111. Máté: Architektúrák 3. előadás 5

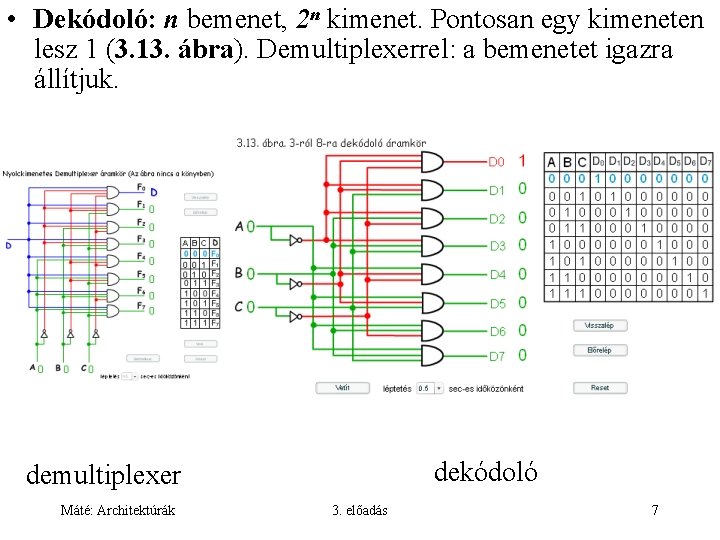

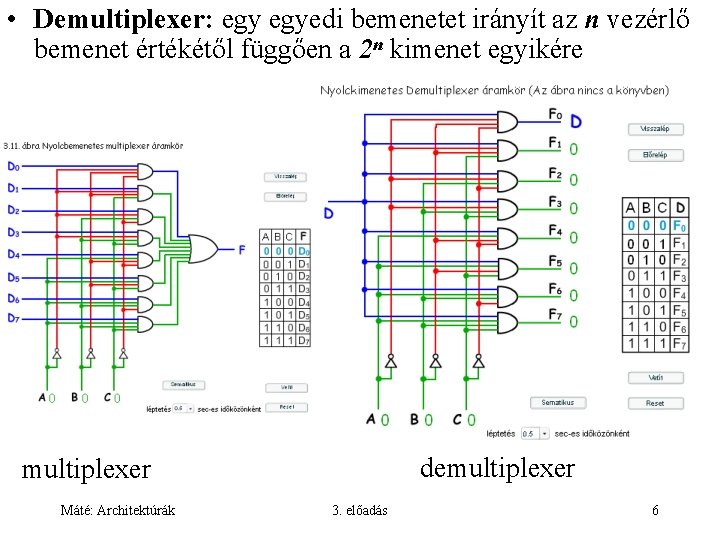

• Demultiplexer: egyedi bemenetet irányít az n vezérlő bemenet értékétől függően a 2 n kimenet egyikére demultiplexer Máté: Architektúrák 3. előadás 6

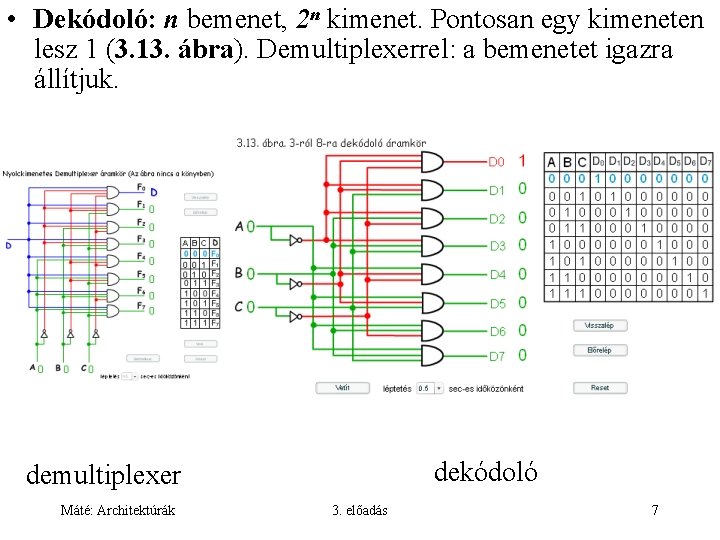

• Dekódoló: n bemenet, 2 n kimenet. Pontosan egy kimeneten lesz 1 (3. 13. ábra). Demultiplexerrel: a bemenetet igazra állítjuk. dekódoló demultiplexer Máté: Architektúrák 3. előadás 7

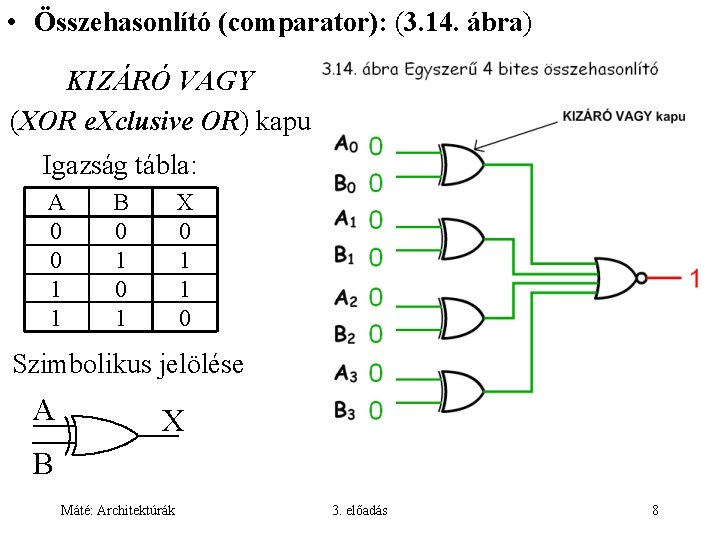

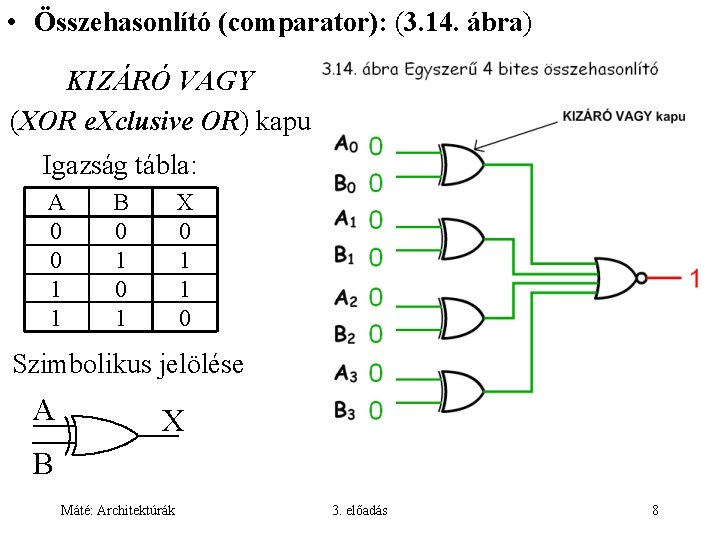

• Összehasonlító (comparator): (3. 14. ábra) KIZÁRÓ VAGY (XOR e. Xclusive OR) kapu Igazság tábla: A 0 0 1 1 B 0 1 X 0 1 1 0 Szimbolikus jelölése A X B Máté: Architektúrák 3. előadás 8

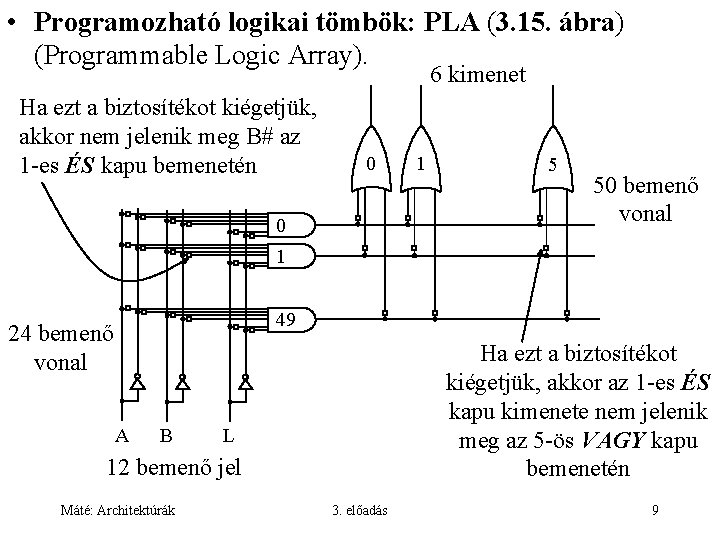

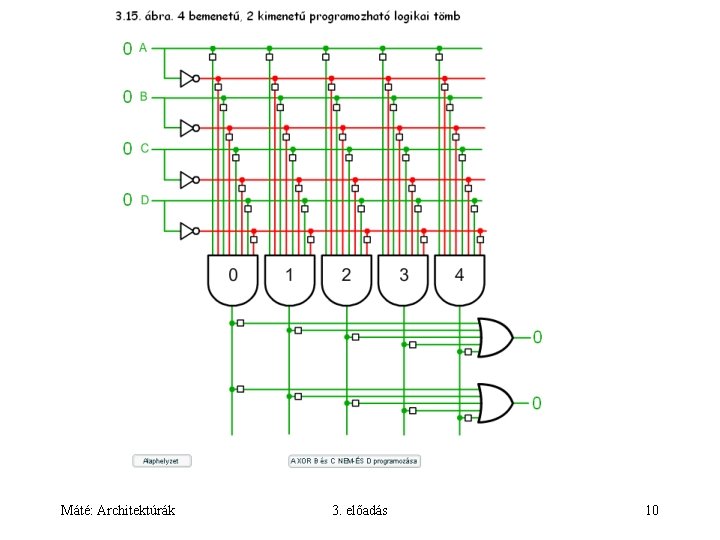

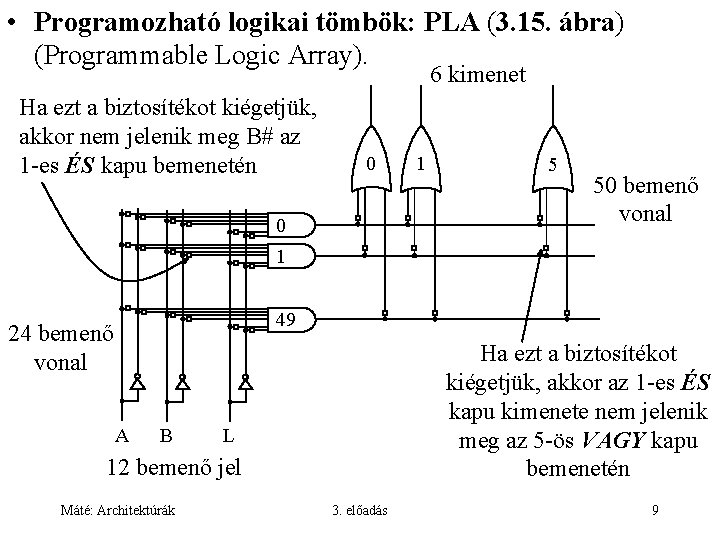

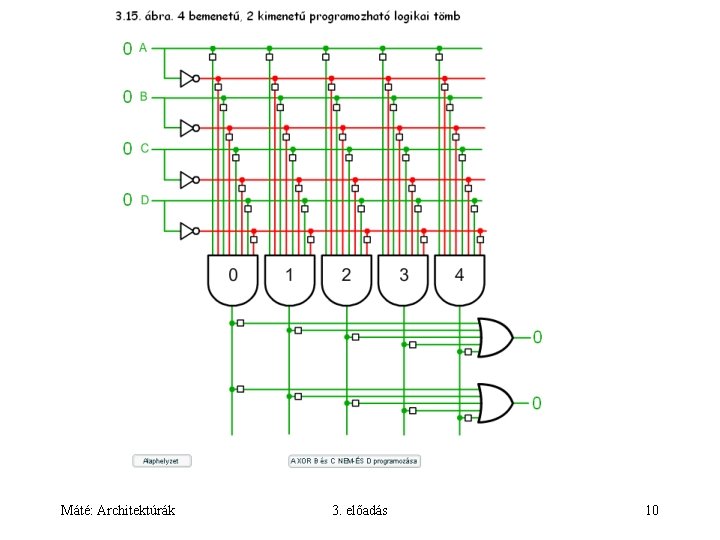

• Programozható logikai tömbök: PLA (3. 15. ábra) (Programmable Logic Array). 6 kimenet Ha ezt a biztosítékot kiégetjük, akkor nem jelenik meg B# az 1 -es ÉS kapu bemenetén 0 0 1 5 50 bemenő vonal 1 49 24 bemenő vonal A B Ha ezt a biztosítékot kiégetjük, akkor az 1 -es ÉS kapu kimenete nem jelenik meg az 5 -ös VAGY kapu bemenetén L 12 bemenő jel Máté: Architektúrák 3. előadás 9

Máté: Architektúrák 3. előadás 10

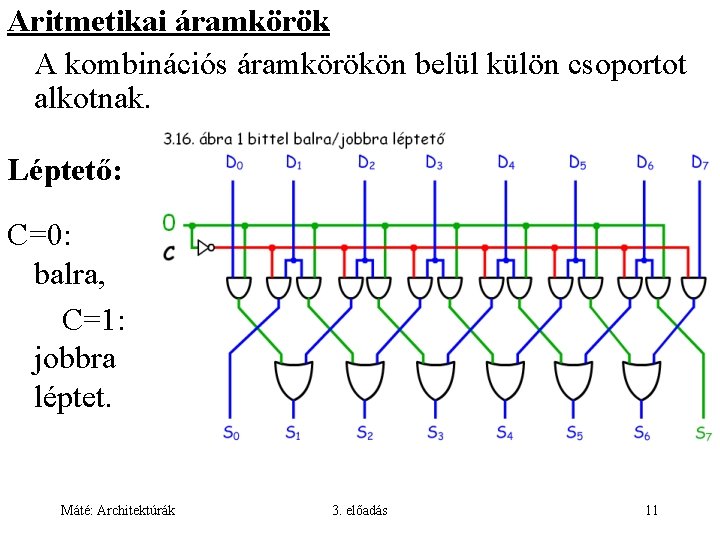

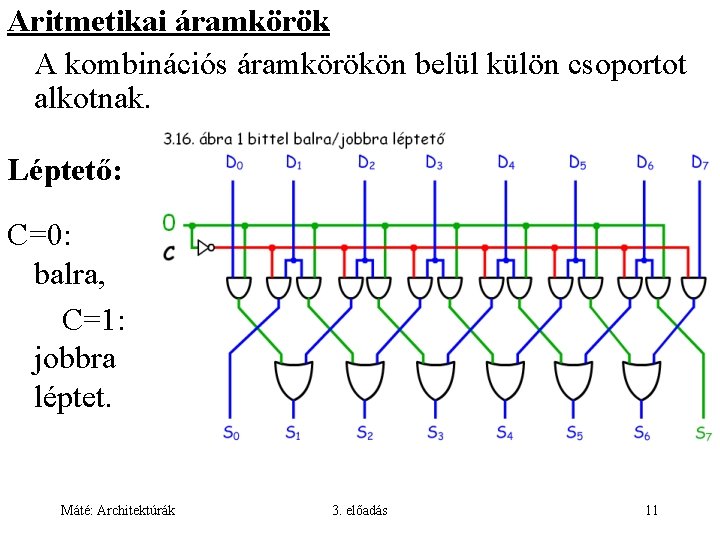

Aritmetikai áramkörök A kombinációs áramkörökön belül külön csoportot alkotnak. Léptető: C=0: balra, C=1: jobbra léptet. Máté: Architektúrák 3. előadás 11

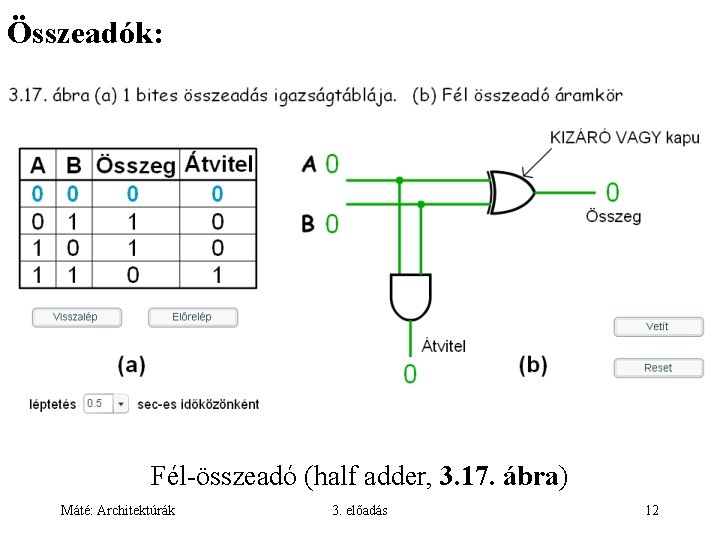

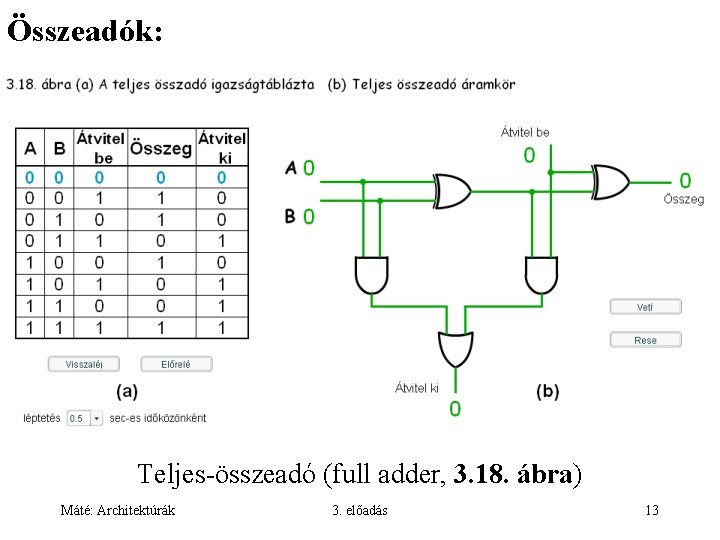

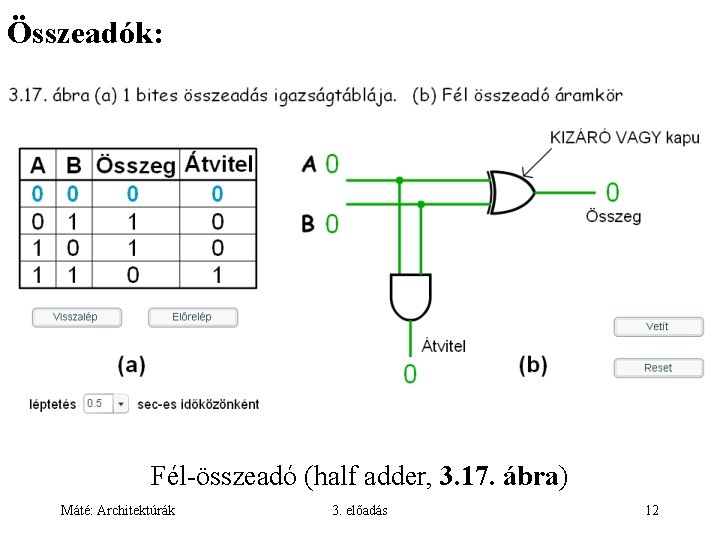

Összeadók: Fél-összeadó (half adder, 3. 17. ábra) Máté: Architektúrák 3. előadás 12

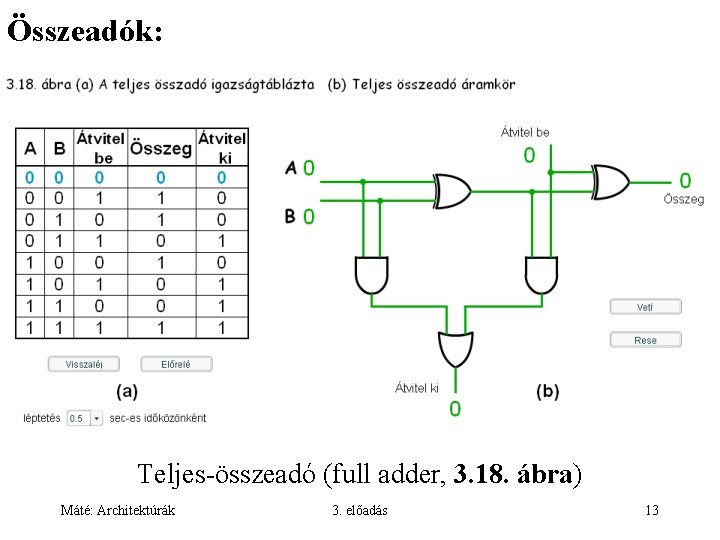

Összeadók: Teljes-összeadó (full adder, 3. 18. ábra) Máté: Architektúrák 3. előadás 13

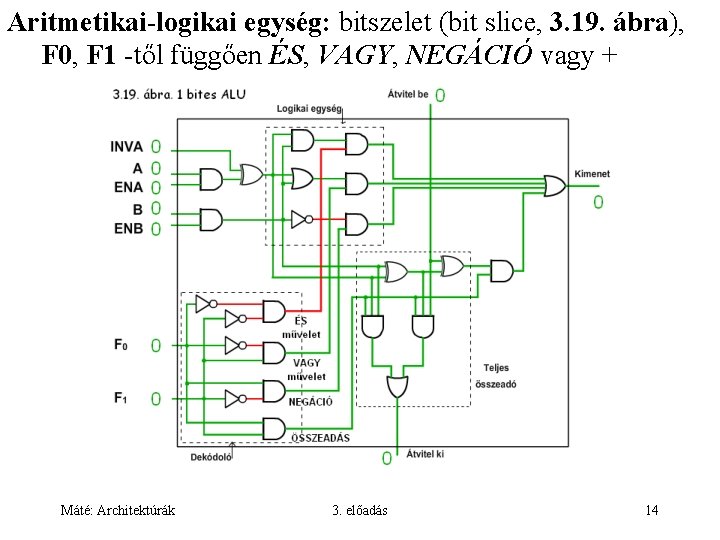

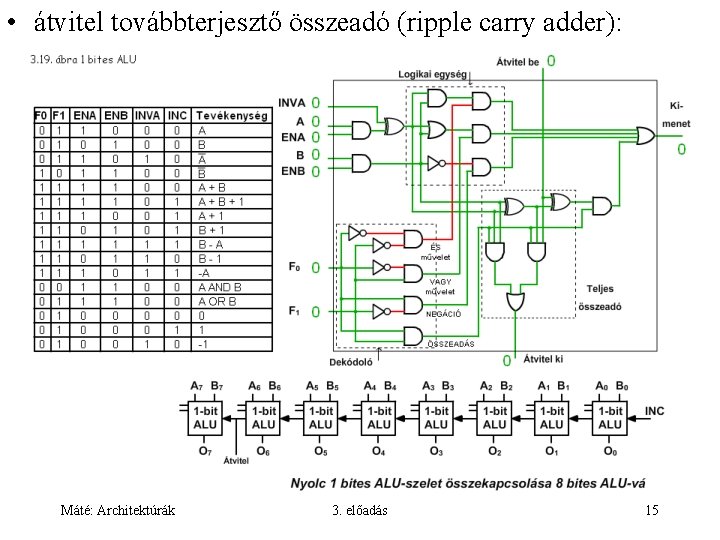

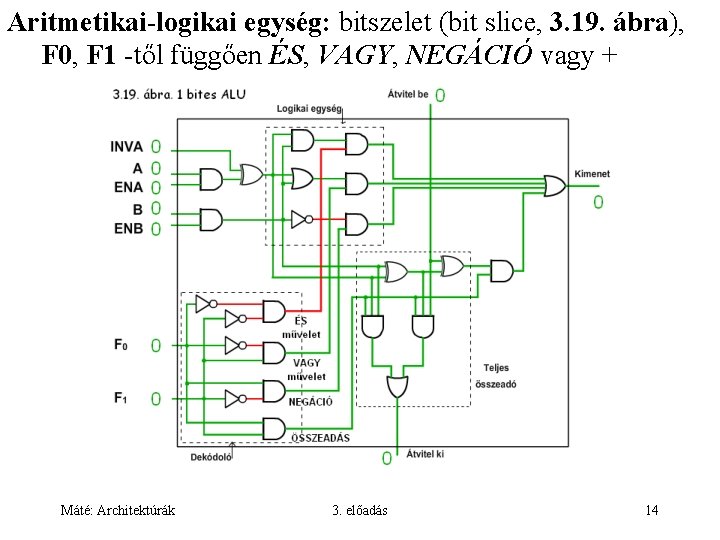

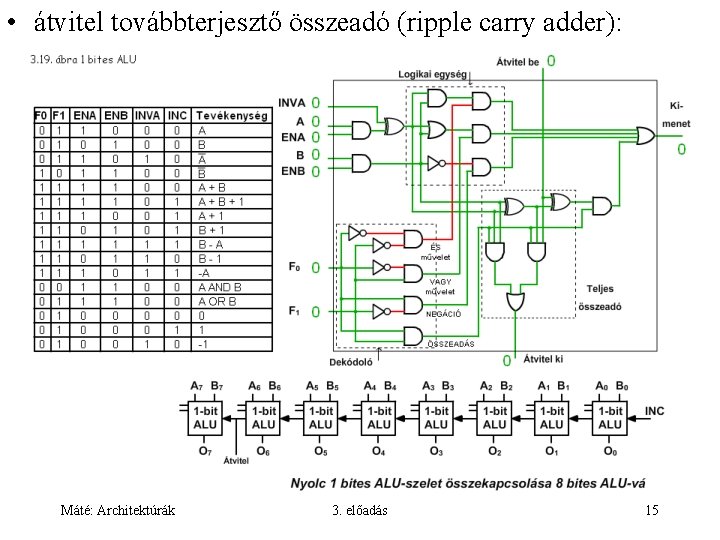

Aritmetikai-logikai egység: bitszelet (bit slice, 3. 19. ábra), F 0, F 1 -től függően ÉS, VAGY, NEGÁCIÓ vagy + Máté: Architektúrák 3. előadás 14

• átvitel továbbterjesztő összeadó (ripple carry adder): Máté: Architektúrák 3. előadás 15

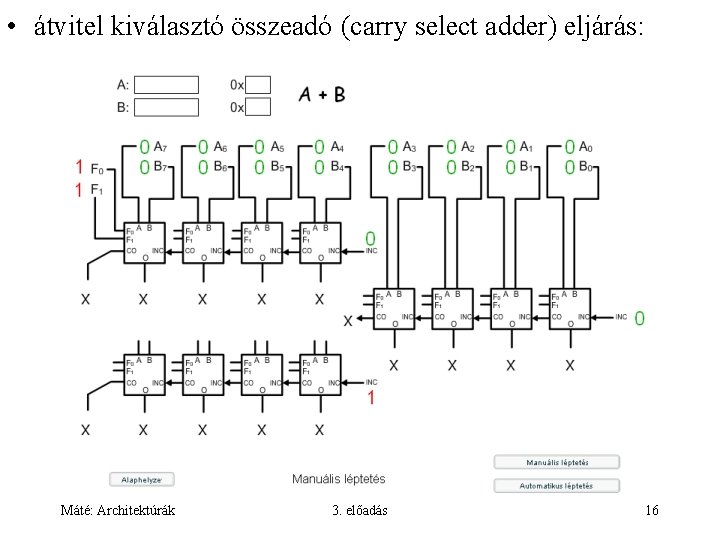

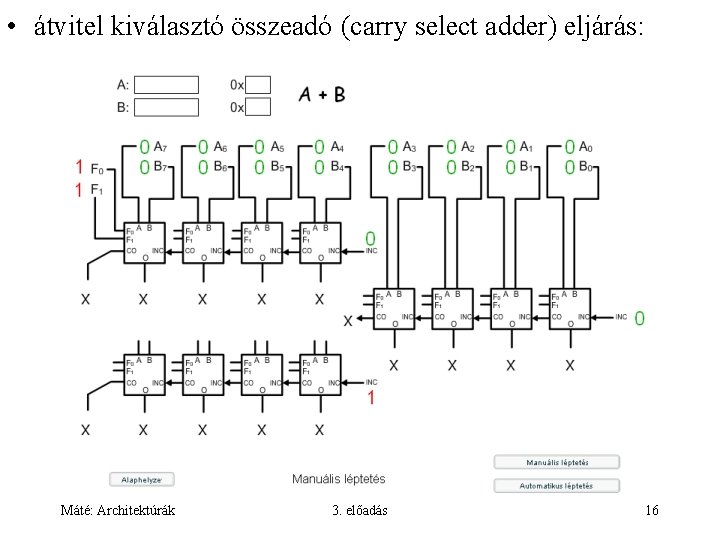

• átvitel kiválasztó összeadó (carry select adder) eljárás: Máté: Architektúrák 3. előadás 16

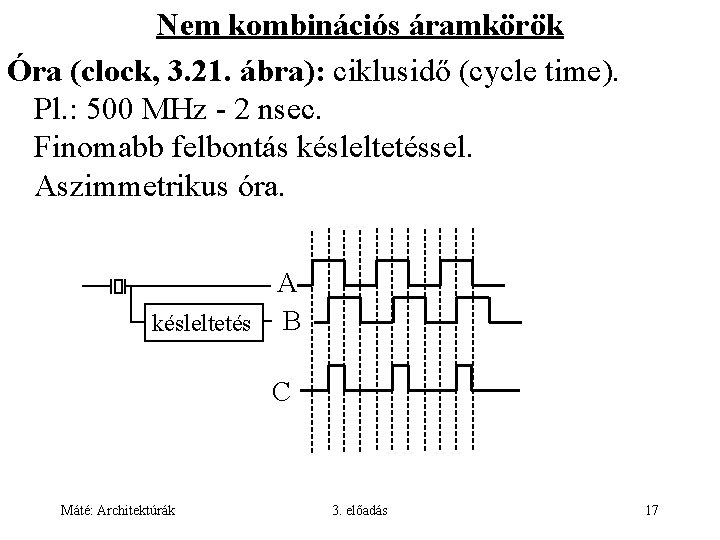

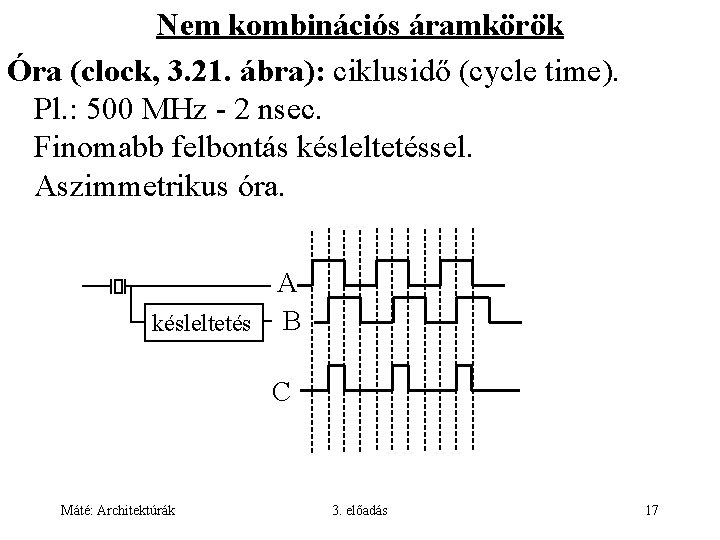

Nem kombinációs áramkörök Óra (clock, 3. 21. ábra): ciklusidő (cycle time). Pl. : 500 MHz - 2 nsec. Finomabb felbontás késleltetéssel. Aszimmetrikus óra. A késleltetés B C Máté: Architektúrák 3. előadás 17

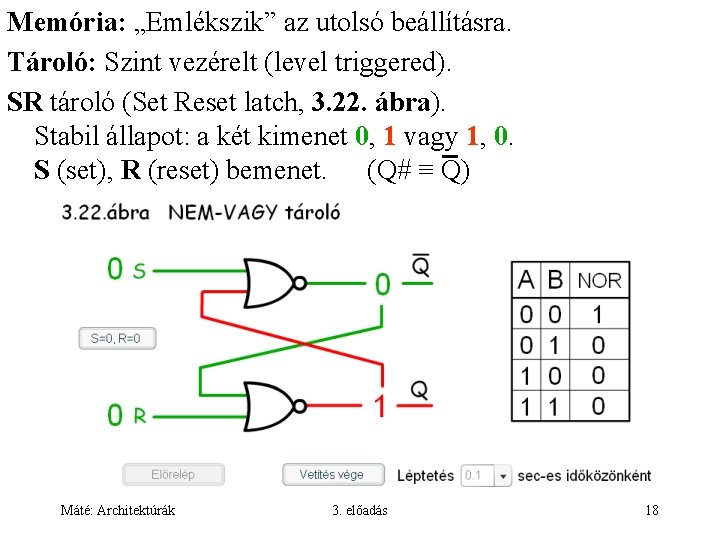

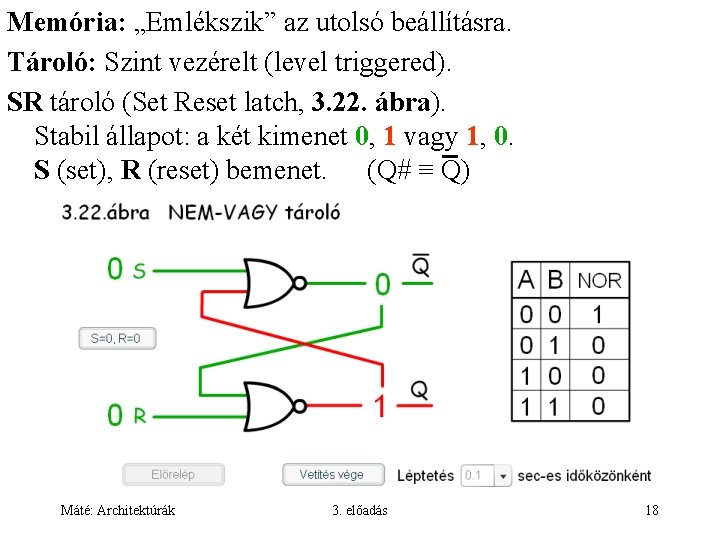

Memória: „Emlékszik” az utolsó beállításra. Tároló: Szint vezérelt (level triggered). SR tároló (Set Reset latch, 3. 22. ábra). Stabil állapot: a két kimenet 0, 1 vagy 1, 0. S (set), R (reset) bemenet. (Q# ≡ Q) Máté: Architektúrák 3. előadás 18

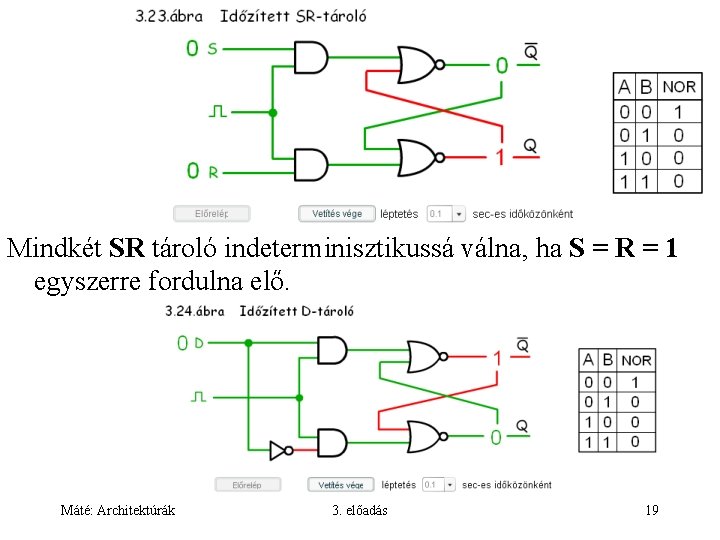

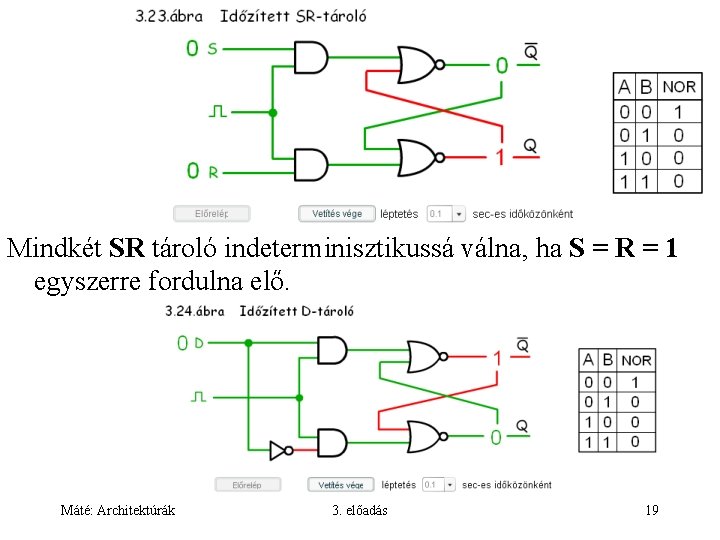

Mindkét SR tároló indeterminisztikussá válna, ha S = R = 1 egyszerre fordulna elő. Máté: Architektúrák 3. előadás 19

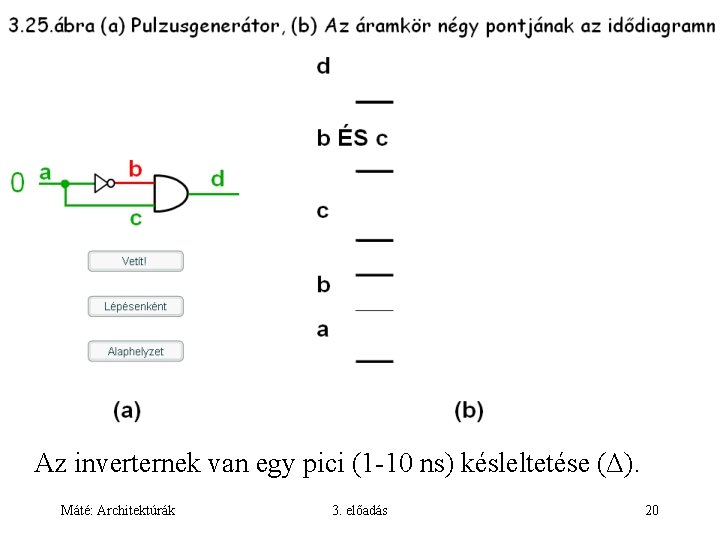

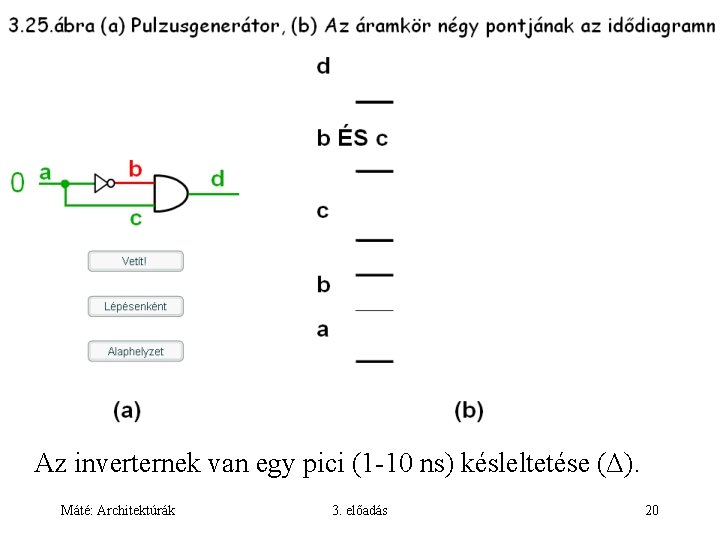

Az inverternek van egy pici (1 -10 ns) késleltetése (Δ). Máté: Architektúrák 3. előadás 20

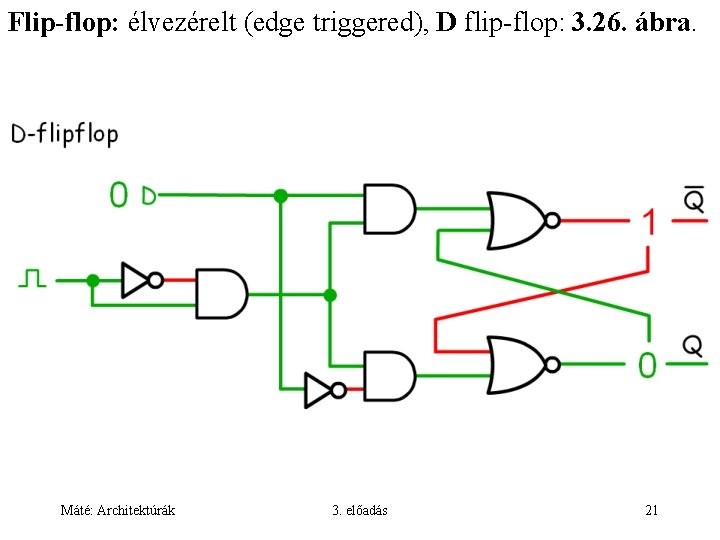

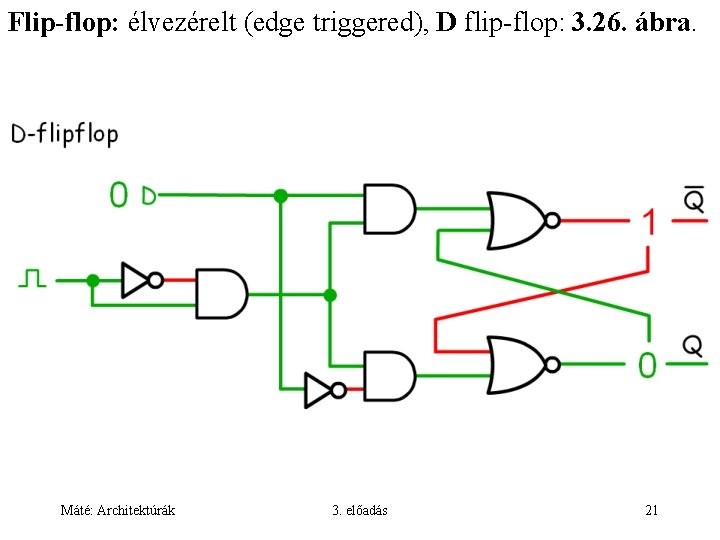

Flip-flop: élvezérelt (edge triggered), D flip-flop: 3. 26. ábra. Máté: Architektúrák 3. előadás 21

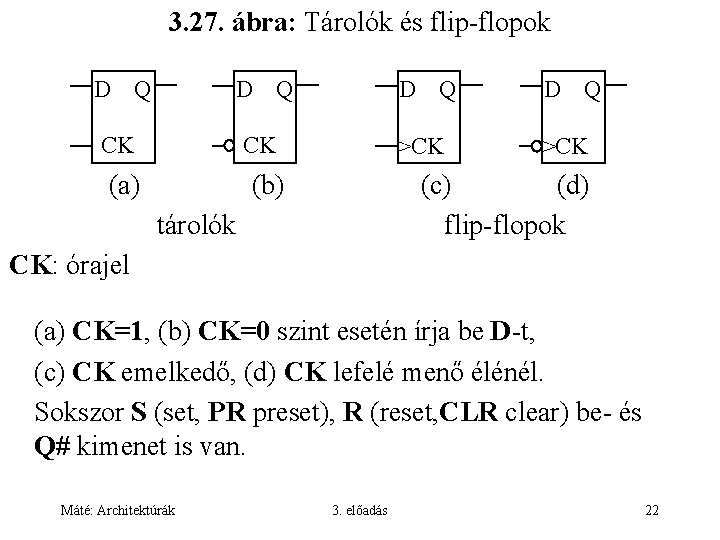

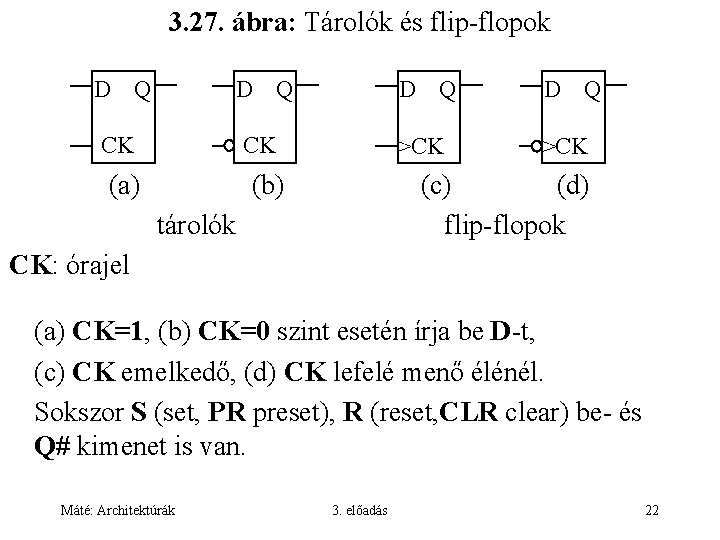

3. 27. ábra: Tárolók és flip-flopok D Q D Q CK CK >CK (a) (b) (c) (d) flip-flopok tárolók CK: órajel (a) CK=1, (b) CK=0 szint esetén írja be D-t, (c) CK emelkedő, (d) CK lefelé menő élénél. Sokszor S (set, PR preset), R (reset, CLR clear) be- és Q# kimenet is van. Máté: Architektúrák 3. előadás 22

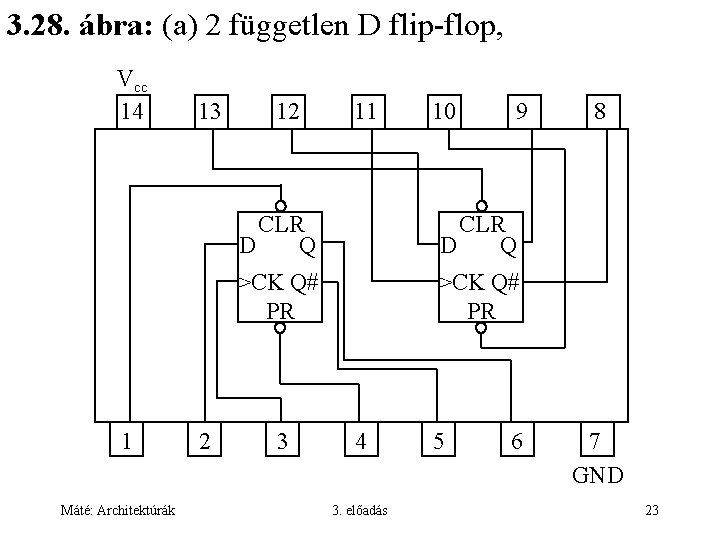

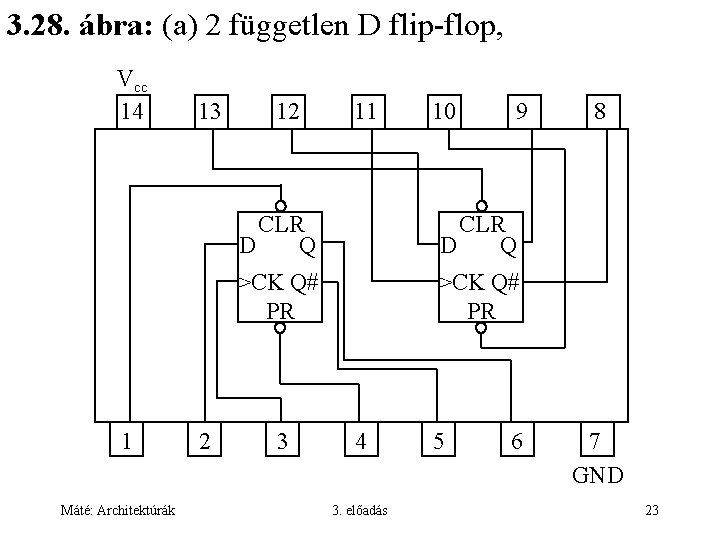

3. 28. ábra: (a) 2 független D flip-flop, Vcc 14 1 Máté: Architektúrák 13 2 12 11 10 9 CLR D Q >CK Q# PR 3 4 3. előadás 5 6 8 7 GND 23

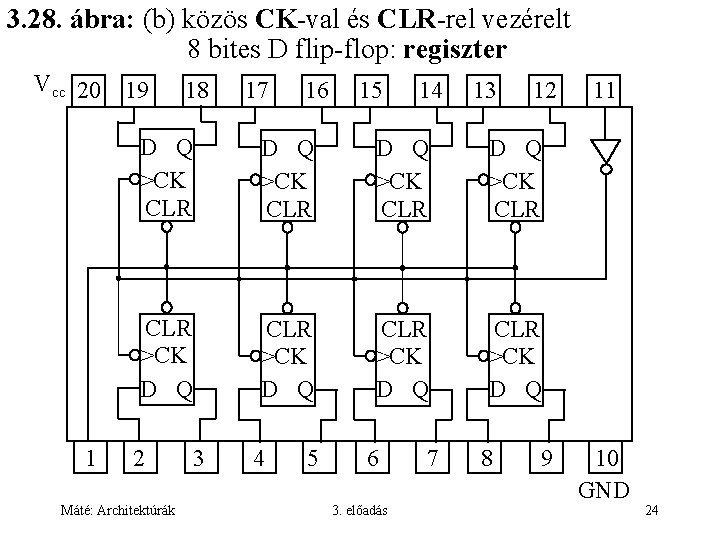

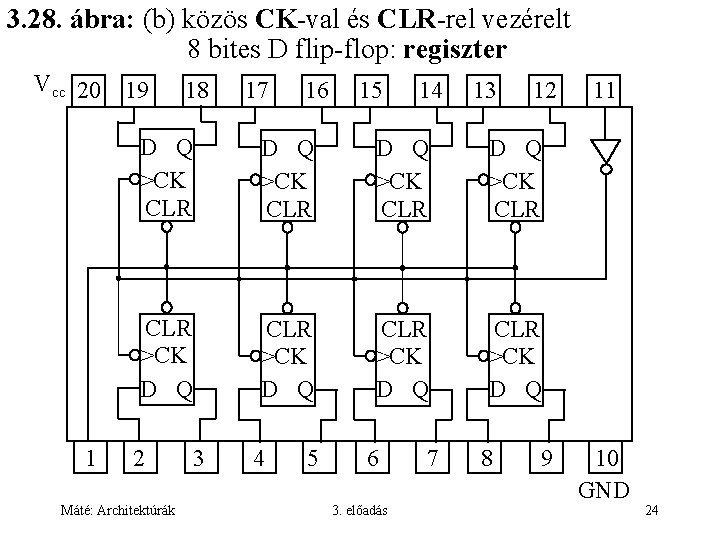

3. 28. ábra: (b) közös CK-val és CLR-rel vezérelt 8 bites D flip-flop: regiszter Vcc 20 1 19 18 17 16 15 14 13 12 D Q >CK CLR CLR >CK D Q 2 Máté: Architektúrák 3 4 5 6 3. előadás 7 8 9 11 10 GND 24

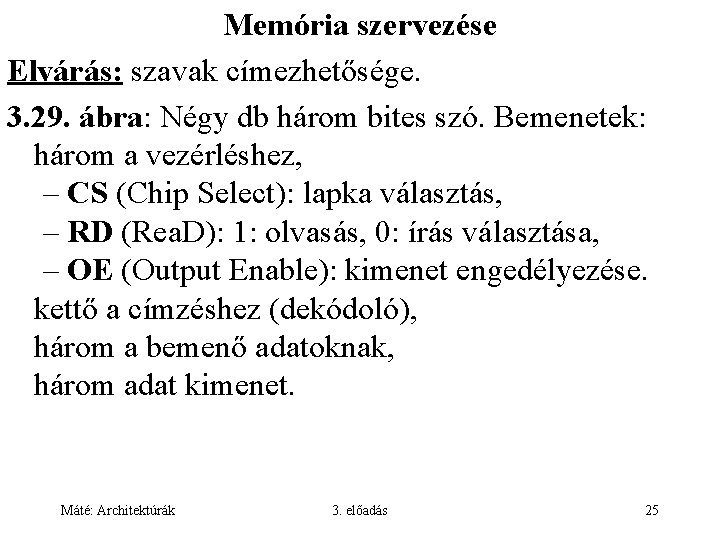

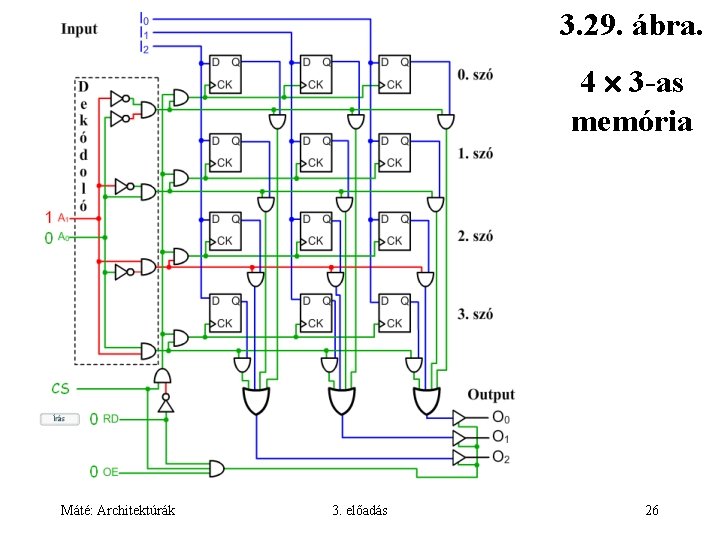

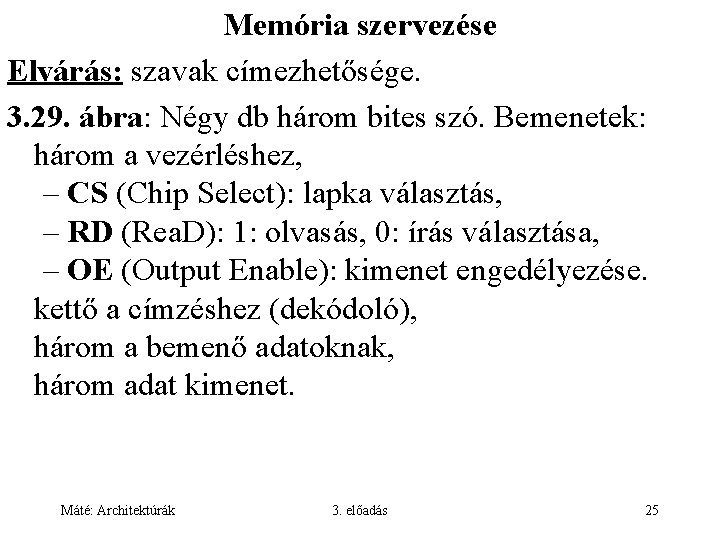

Memória szervezése Elvárás: szavak címezhetősége. 3. 29. ábra: Négy db három bites szó. Bemenetek: három a vezérléshez, – CS (Chip Select): lapka választás, – RD (Rea. D): 1: olvasás, 0: írás választása, – OE (Output Enable): kimenet engedélyezése. kettő a címzéshez (dekódoló), három a bemenő adatoknak, három adat kimenet. Máté: Architektúrák 3. előadás 25

3. 29. ábra. 4 3 -as memória Máté: Architektúrák 3. előadás 26

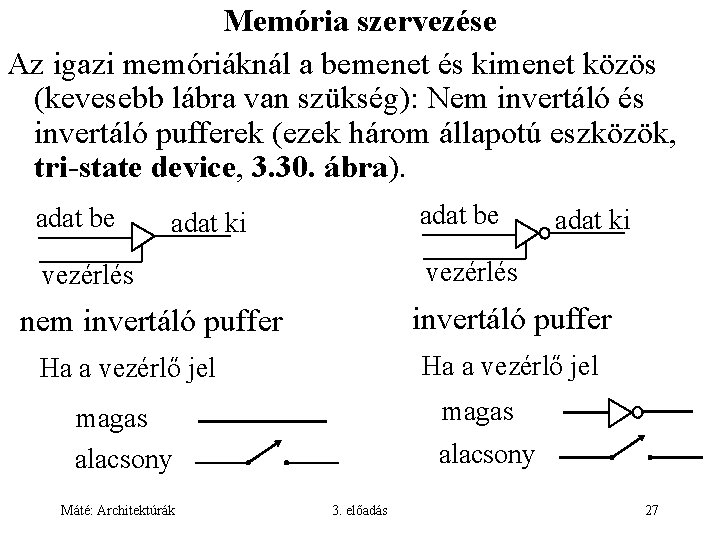

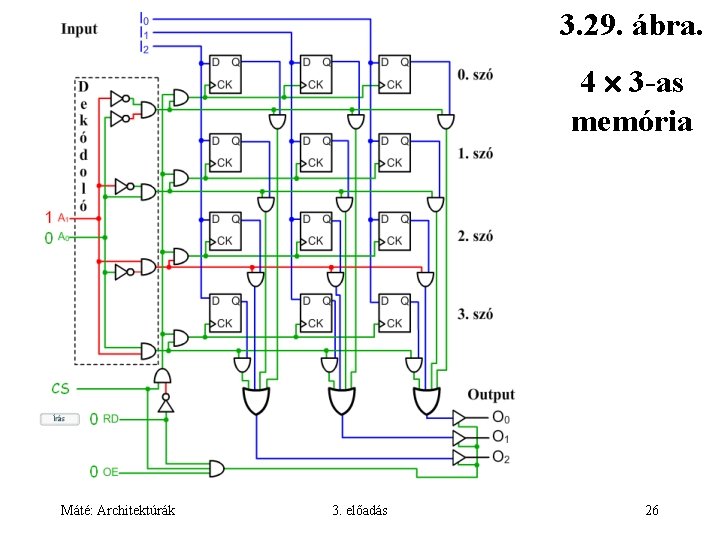

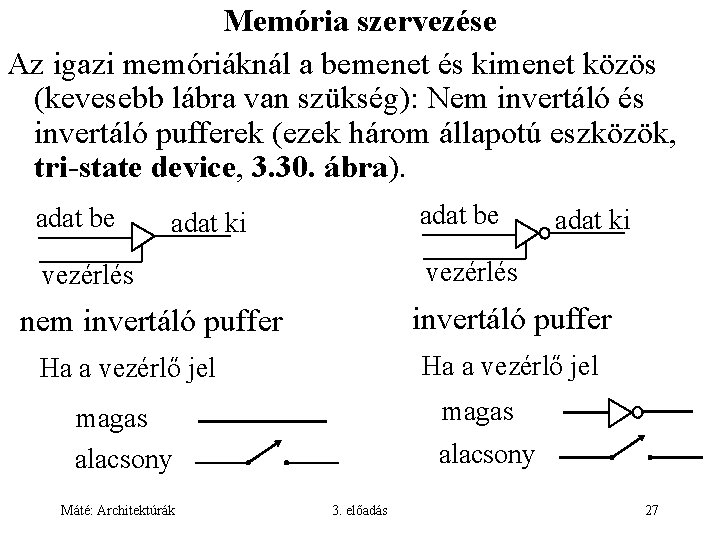

Memória szervezése Az igazi memóriáknál a bemenet és kimenet közös (kevesebb lábra van szükség): Nem invertáló és invertáló pufferek (ezek három állapotú eszközök, tri-state device, 3. 30. ábra). adat be adat ki vezérlés invertáló puffer nem invertáló puffer Ha a vezérlő jel magas alacsony Máté: Architektúrák adat ki alacsony 3. előadás 27

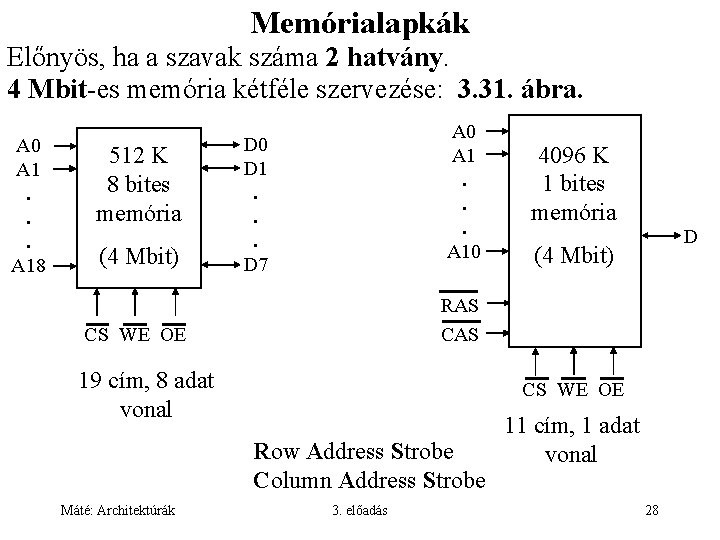

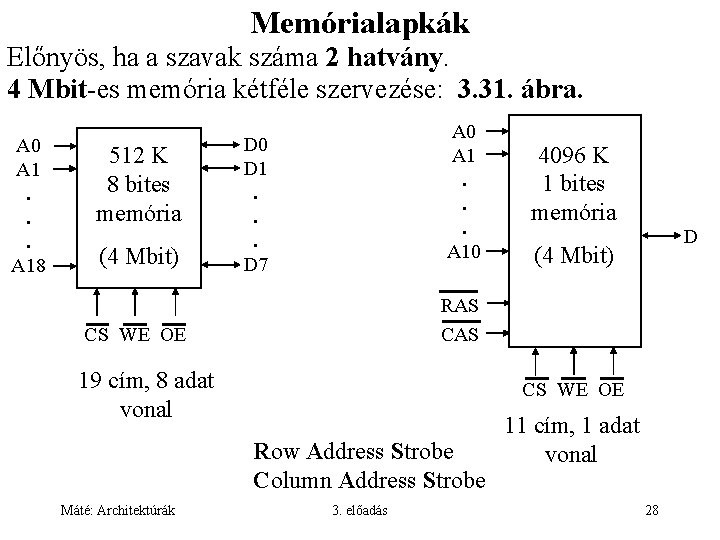

Memórialapkák Előnyös, ha a szavak száma 2 hatvány. 4 Mbit-es memória kétféle szervezése: 3. 31. ábra. A 0 A 1. . . A 18 512 K 8 bites memória (4 Mbit) A 0 A 1. . . A 10 D 1. . . D 7 D (4 Mbit) RAS CS WE OE 19 cím, 8 adat vonal CS WE OE Row Address Strobe Column Address Strobe Máté: Architektúrák 4096 K 1 bites memória 3. előadás 11 cím, 1 adat vonal 28

Memórialapkák A jel (bemenet) beállított (asserted) vagy negált. CS beállított: 1, de CS# beállított: 0 a) 512 K bájtos elrendezés: 19 cím, 8 adat vonal. b) 2048*2048 bites elrendezés: 11 cím, 1 adat vonal: Bit kiválasztás sor- (RAS: Row Address Strobe) és oszlopindex CAS (Column. . . ) segítségével. Gyakran alkalmazzák nagyobb memóriáknál, bár a két cím megadása lassíthat. Nagyobb memóriáknál 1, 4, 8, 16 bites kimeneteket is használnak. Máté: Architektúrák 3. előadás 29

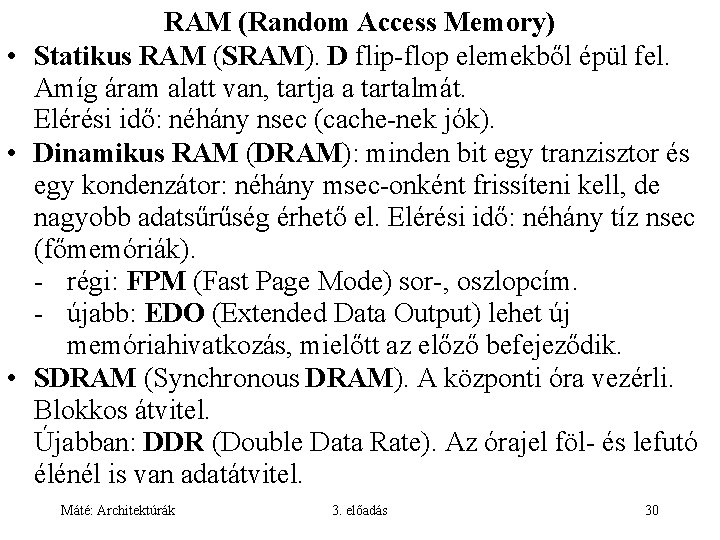

RAM (Random Access Memory) • Statikus RAM (SRAM). D flip-flop elemekből épül fel. Amíg áram alatt van, tartja a tartalmát. Elérési idő: néhány nsec (cache-nek jók). • Dinamikus RAM (DRAM): minden bit egy tranzisztor és egy kondenzátor: néhány msec-onként frissíteni kell, de nagyobb adatsűrűség érhető el. Elérési idő: néhány tíz nsec (főmemóriák). - régi: FPM (Fast Page Mode) sor-, oszlopcím. - újabb: EDO (Extended Data Output) lehet új memóriahivatkozás, mielőtt az előző befejeződik. • SDRAM (Synchronous DRAM). A központi óra vezérli. Blokkos átvitel. Újabban: DDR (Double Data Rate). Az órajel föl- és lefutó élénél is van adatátvitel. Máté: Architektúrák 3. előadás 30

ROM (Read-Only Memory) ROM: gyárilag kialakított tartalom. PROM (Programmable ROM): a tartalom biztosítékok kiégetésével alakul ki (a PLA-khoz hasonlóan, 3. 15. ábra). EPROM (Erasable PROM): a biztosítékok speciális fénnyel kiolvaszthatók és „kijavíthatók”. EEPROM: elektromos impulzusokkal. Flash memória: törlés és újraírás csak blokkonként. Kb. 100 000 használat után „elkopnak”. Ilyen van a legtöbb MP 3 lejátszóban, digitális fényképezőgépben … Máté: Architektúrák 3. előadás 31

512 MB-os flash memória Máté: Architektúrák 3. előadás 32

Feladatok Mit nevezünk kombinációs áramkörnek? Milyen kombinációs áramköröket ismer? Milyen be- és kimenetei vannak a multiplexernek, a dekódolónak? Mire használható a multiplexer, és hogyan? Mire használható a PLA, és hogyan? Milyen aritmetikai áramköröket ismer? Hogy működik a léptető? Hogy működik a „fél összeadó”? Mi indokolja a „fél összeadó” elnevezést? Máté: Architektúrák 3. előadás 33

Feladatok Hogy épül fel a teljes összeadó? Milyen részei vannak az ALU-nak? Milyen be- és kimenetei vannak az 1 bites ALU-nak? Milyen műveletek végezhetők el az ALU-val? Hogy működik az átvitel továbbterjesztő/kiválasztó összeadó? Máté: Architektúrák 3. előadás 34

Feladatok Hogy érhetünk el az órajelnél finomabb időzítést? Milyen nem kombinációs áramköröket ismer? Kombinációs áramkör-e az ALU? Hogyan csökkenthető az összeadásnál az átvitelekből származó idő? Hány stabil állapota van az SR tárolónak? Mi a különbség az SR és az időzített SR tároló között? Mi a különbség az SR és D tároló között? Mi a pulzusgenerátor, és mi a működési elve? Mi a különbség a tároló és a flip-flop között? Máté: Architektúrák 3. előadás 35

Feladatok Hogy működik az invertáló és a nem invertáló puffer? Miért használnak a memóriáknál invertáló vagy nem invertáló puffert? Hogy címezhető meg n címlábon 2 n nél nagyobb memória? Mit jelent, hogy a CS/CS# bemenet beállított/negált? Mi a RAM? Milyen elemekből épül fel a SRAM? Milyen elemekből épül fel a DRAM? Hogy működik a DRAM? Máté: Architektúrák 3. előadás 36

Feladatok Hogy működik az SDRAM? Mit jelent az FPM rövidítés? Mit jelent az EDO rövidítés? Hogy működik a DDR? Mit jelent a ROM rövidítés? Hogy működik az EPROM? Hogy működik az EEPROM? Milyen memória van a legtöbb fényképezőgépben? Máté: Architektúrák 3. előadás 37