VLSI Signal Processing CORDIC Coordinate rotation digital computer

- Slides: 25

VLSI Signal Processing CORDIC (Coordinate rotation digital computer) For VLSI Signal Processing Course Ref: Y. H. Hu, “CORDIC based VLSI architecture for digital signal processing, ” IEEE Signal Processing Mag. , pp. 16 -35, July 1992. 2001/4/30 1 台大電機吳安宇

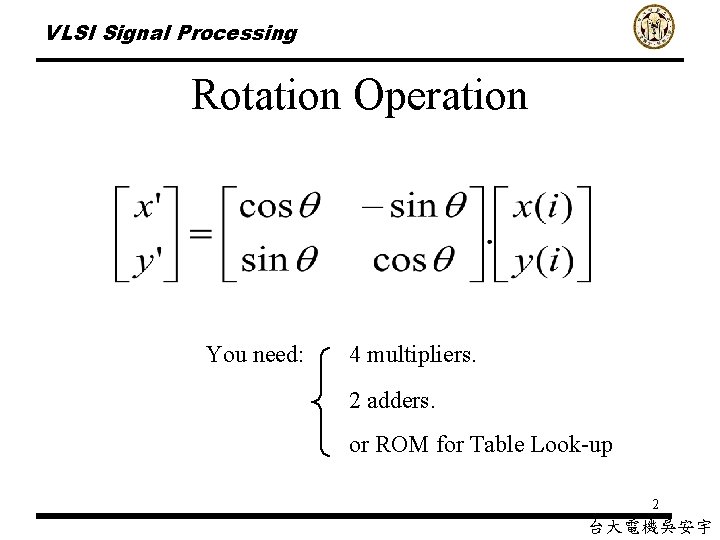

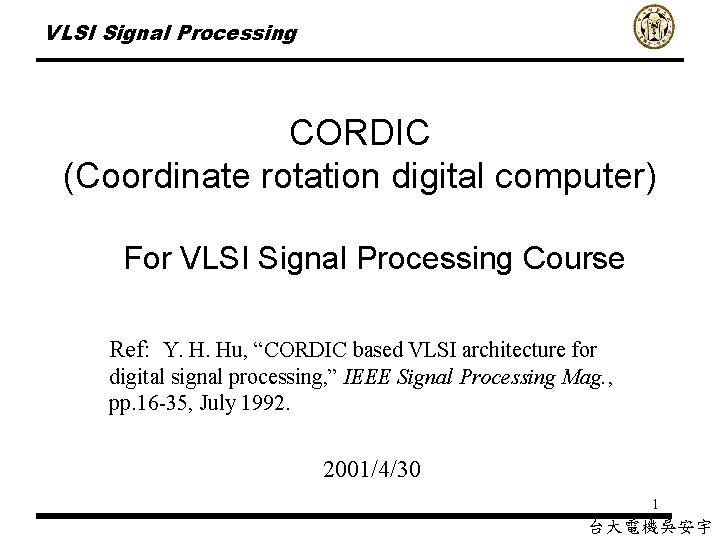

VLSI Signal Processing Rotation Operation You need: 4 multipliers. 2 adders. or ROM for Table Look-up 2 台大電機吳安宇

VLSI Signal Processing • What is “CORDIC” ? –COordinate Rotation DIgital Computer • Why do we use “CORDIC” ? –MAC dominates the implementational cost in some DSP functions. –The DSP approach, CORDIC, helps to save the hardware cost. 3 台大電機吳安宇

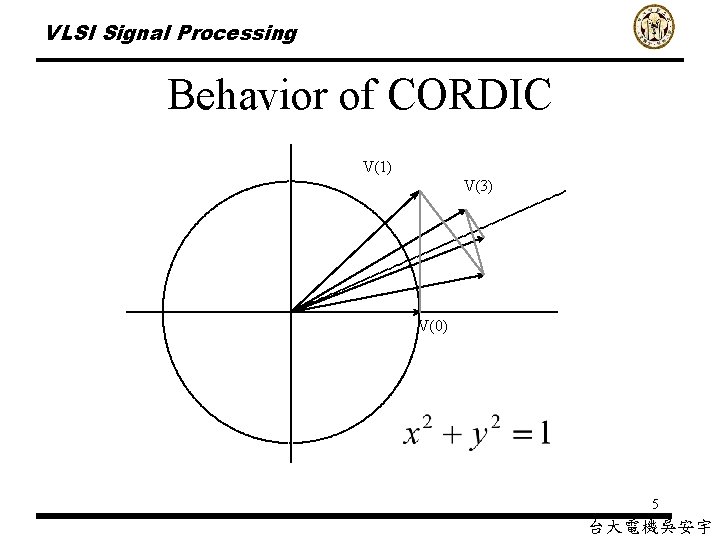

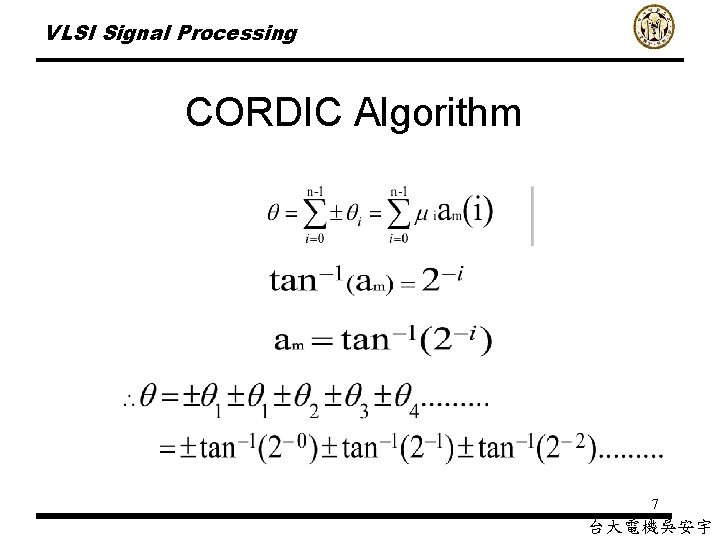

VLSI Signal Processing Basic Concept of The CORDIC • To decompose the desired rotation angle (θ) into the weighted sum of a set of predefined elementary rotation angles (am(i)) • Such that the rotation through each of them can be accomplished with simple shift-andadd operation. 4 台大電機吳安宇

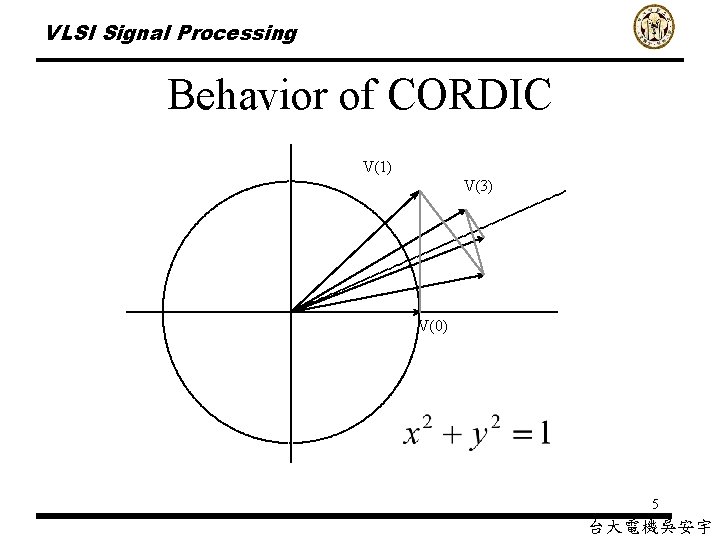

VLSI Signal Processing Behavior of CORDIC V(1) V(3) V(0) 5 台大電機吳安宇

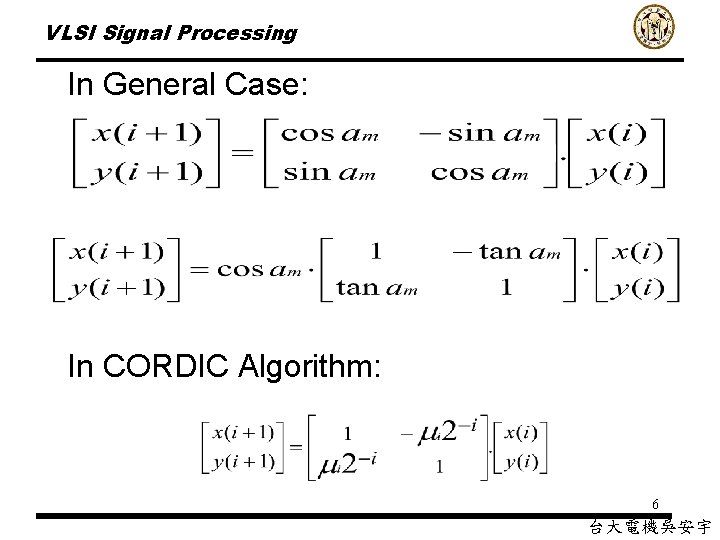

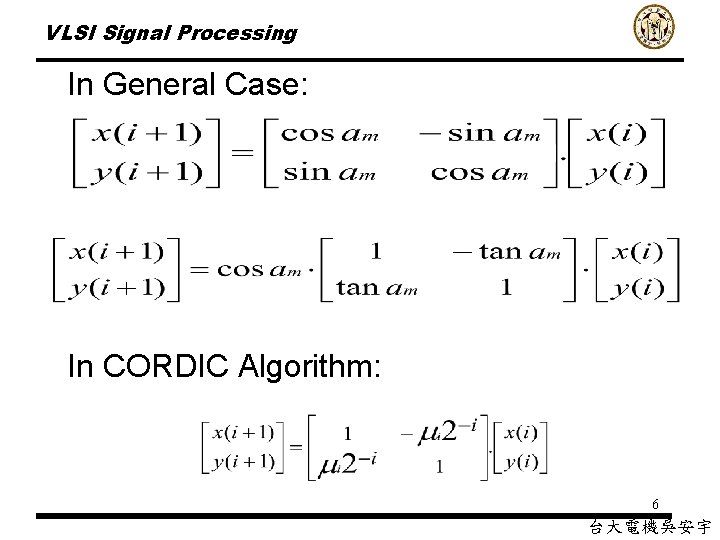

VLSI Signal Processing In General Case: In CORDIC Algorithm: 6 台大電機吳安宇

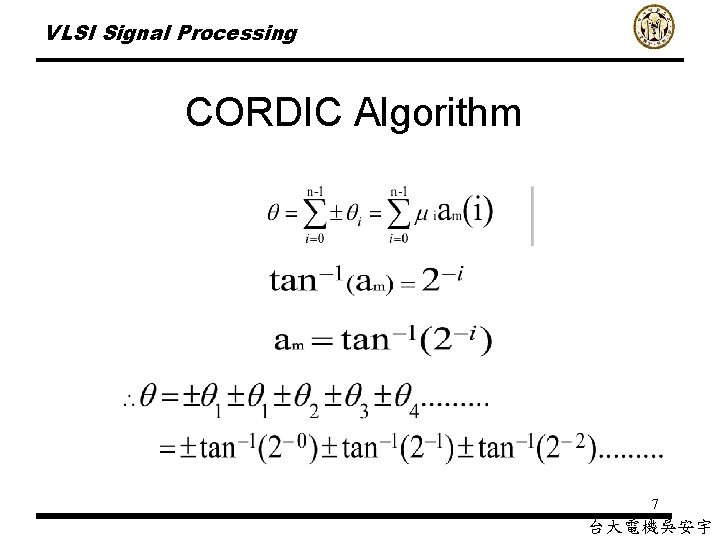

VLSI Signal Processing CORDIC Algorithm 7 台大電機吳安宇

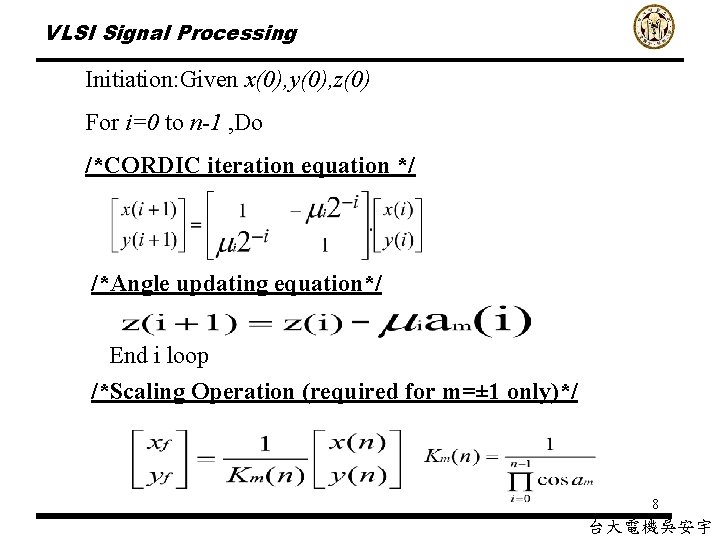

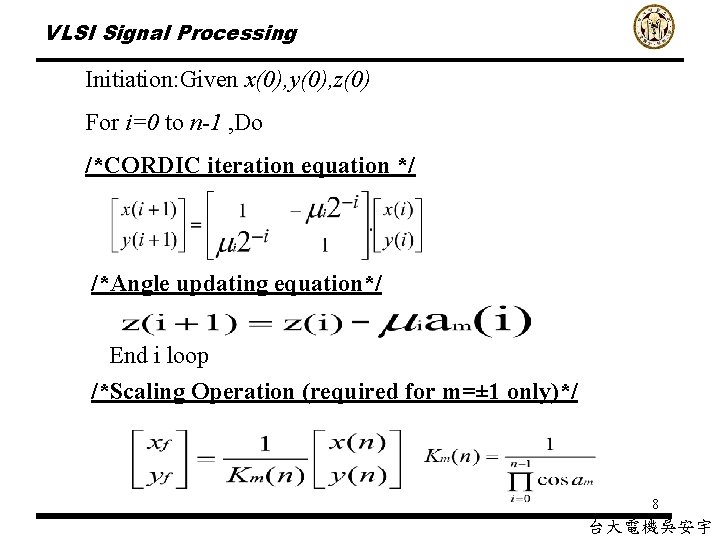

VLSI Signal Processing Initiation: Given x(0), y(0), z(0) For i=0 to n-1 , Do /*CORDIC iteration equation */ /*Angle updating equation*/ End i loop /*Scaling Operation (required for m=± 1 only)*/ 8 台大電機吳安宇

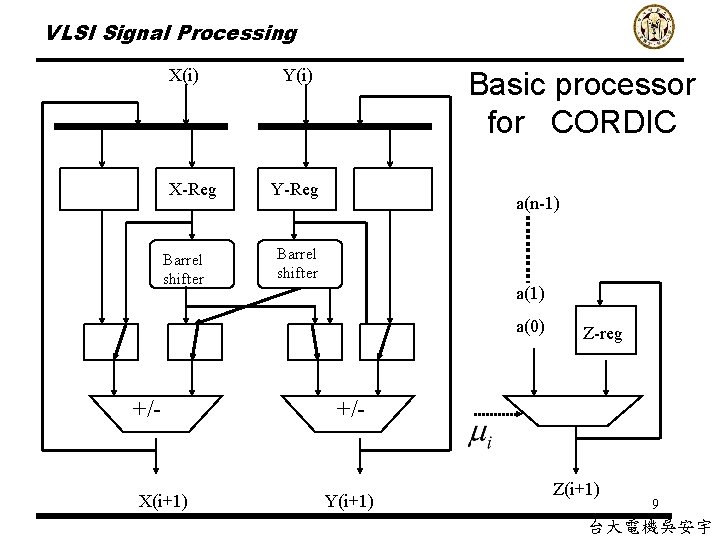

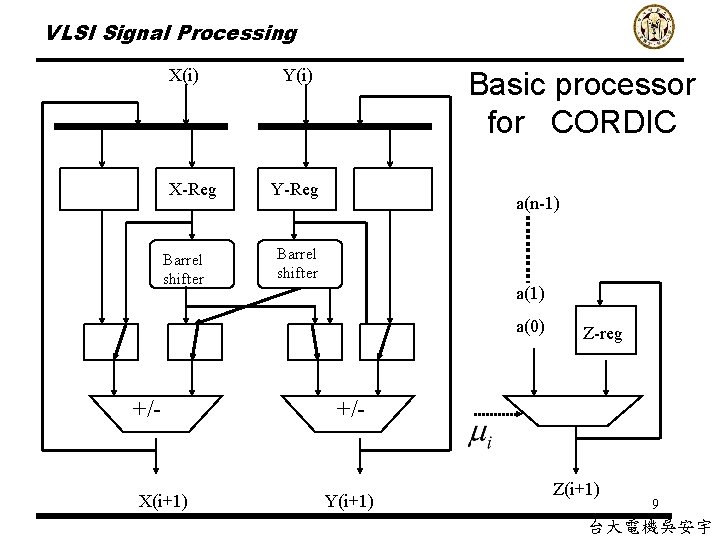

VLSI Signal Processing X(i) X-Reg Barrel shifter Y(i) Basic processor for CORDIC Y-Reg a(n-1) Barrel shifter a(1) a(0) +/- X(i+1) Z-reg +/- Y(i+1) Z(i+1) 9 台大電機吳安宇

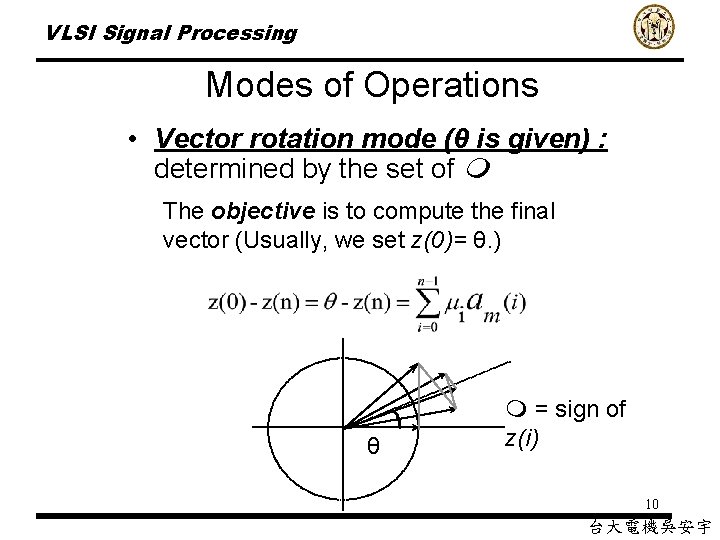

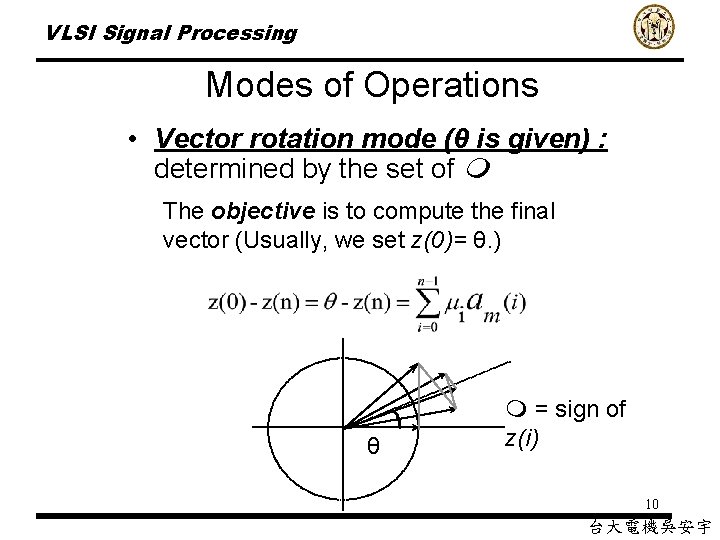

VLSI Signal Processing Modes of Operations • Vector rotation mode (θ is given) : determined by the set of The objective is to compute the final vector (Usually, we set z(0)= θ. ) θ = sign of z(i) 10 台大電機吳安宇

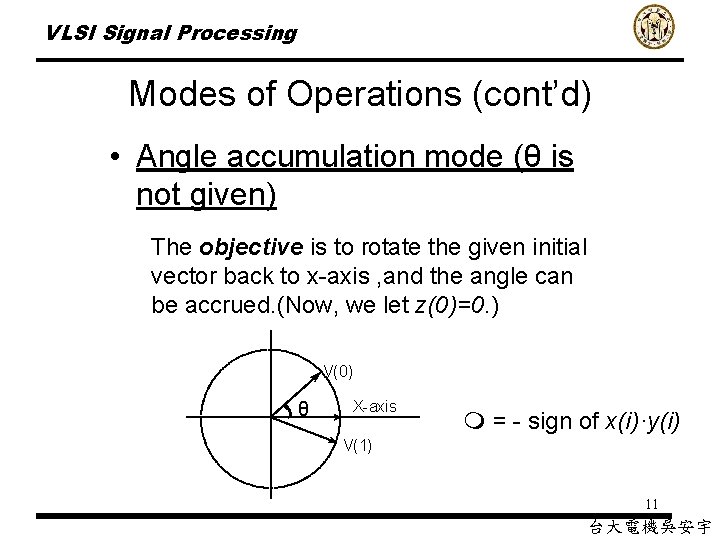

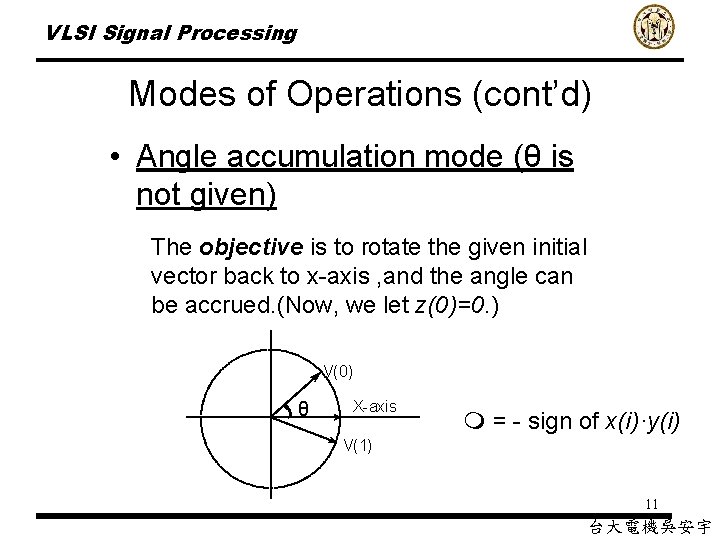

VLSI Signal Processing Modes of Operations (cont’d) • Angle accumulation mode (θ is not given) The objective is to rotate the given initial vector back to x-axis , and the angle can be accrued. (Now, we let z(0)=0. ) V(0) θ X-axis = - sign of x(i)·y(i) V(1) 11 台大電機吳安宇

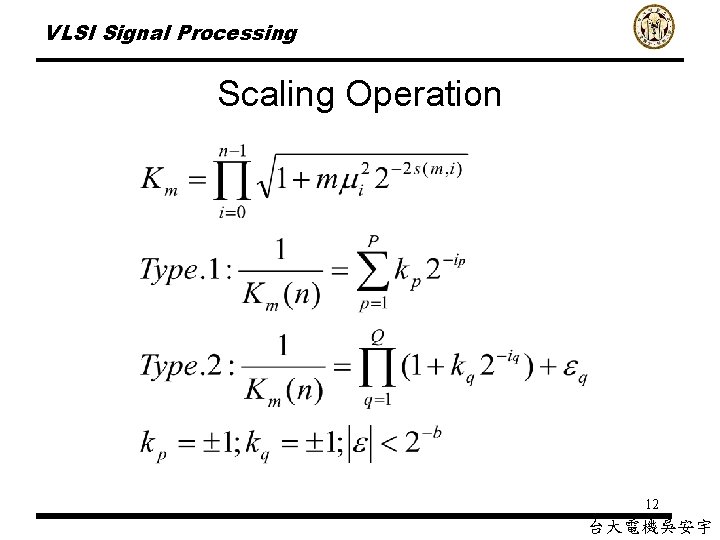

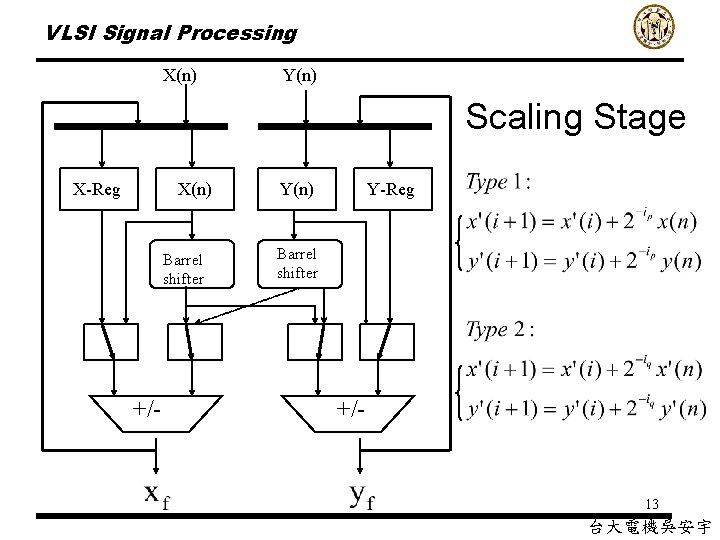

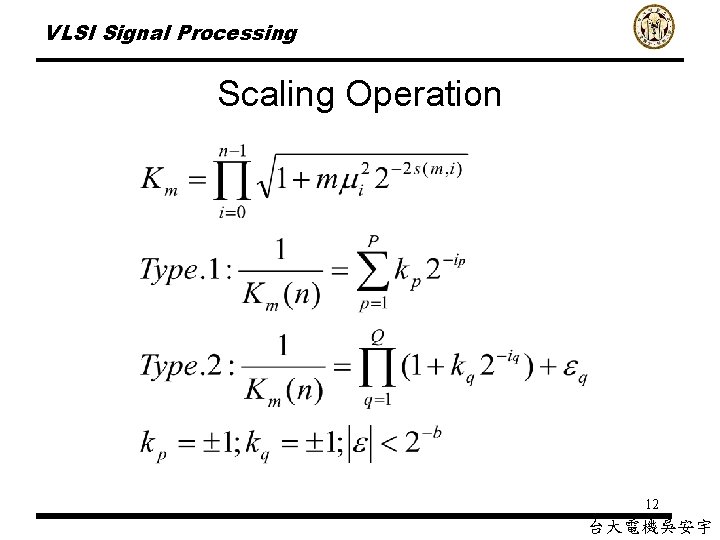

VLSI Signal Processing Scaling Operation 12 台大電機吳安宇

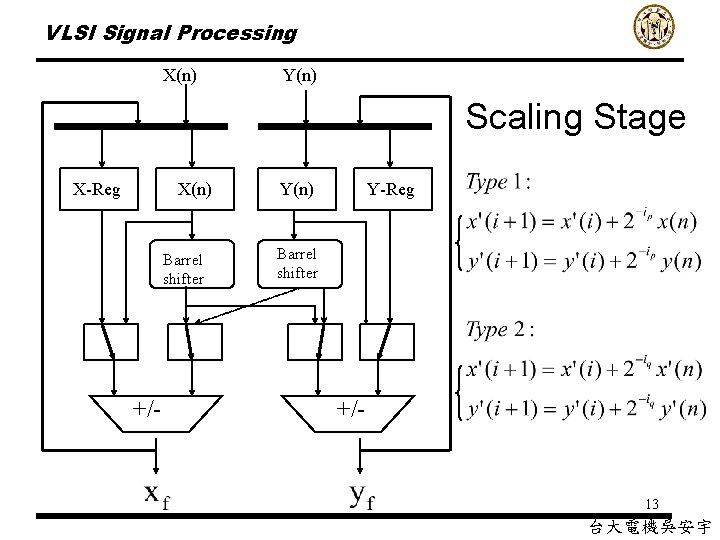

VLSI Signal Processing X(n) Y(n) Scaling Stage X-Reg X(n) Barrel shifter +/- Y(n) Y-Reg Barrel shifter +/- 13 台大電機吳安宇

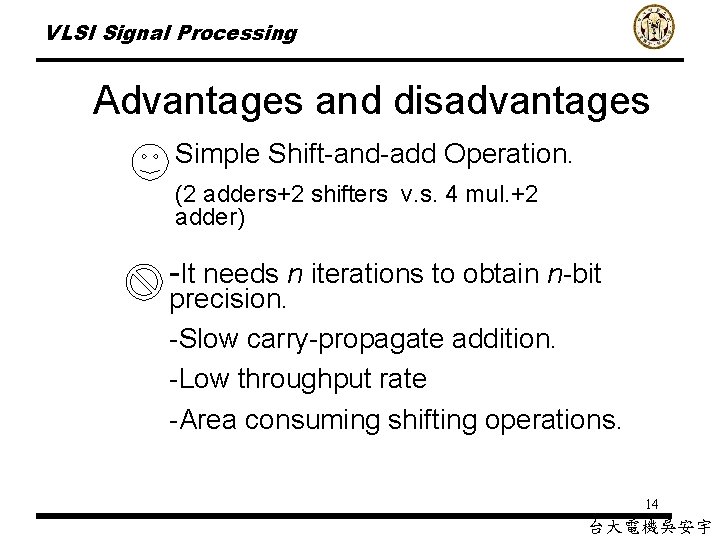

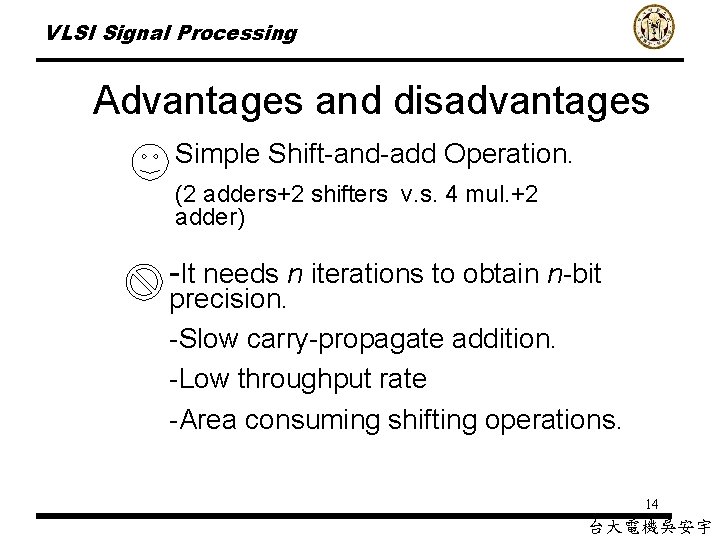

VLSI Signal Processing Advantages and disadvantages Simple Shift-and-add Operation. (2 adders+2 shifters v. s. 4 mul. +2 adder) -It needs n iterations to obtain n-bit precision. -Slow carry-propagate addition. -Low throughput rate -Area consuming shifting operations. 14 台大電機吳安宇

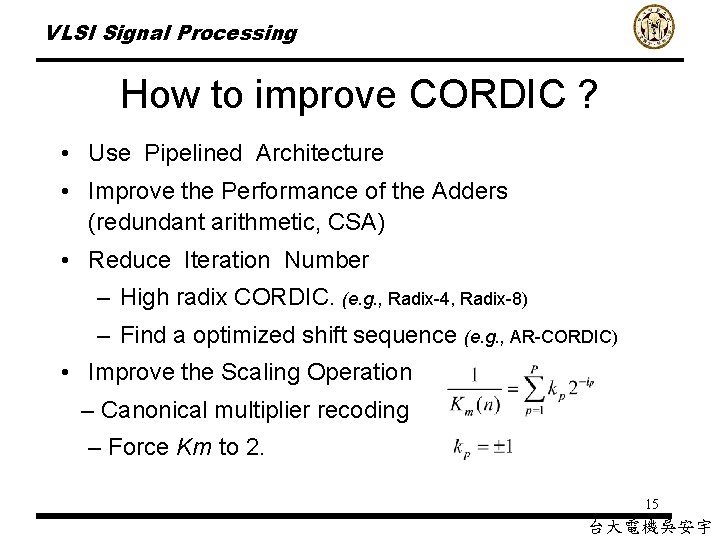

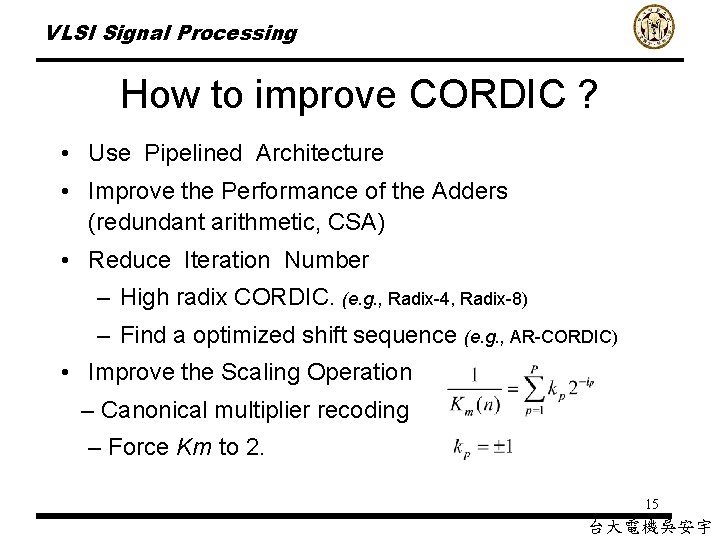

VLSI Signal Processing How to improve CORDIC ? • Use Pipelined Architecture • Improve the Performance of the Adders (redundant arithmetic, CSA) • Reduce Iteration Number – High radix CORDIC. (e. g. , Radix-4, Radix-8) – Find a optimized shift sequence (e. g. , AR-CORDIC) • Improve the Scaling Operation – Canonical multiplier recoding – Force Km to 2. 15 台大電機吳安宇

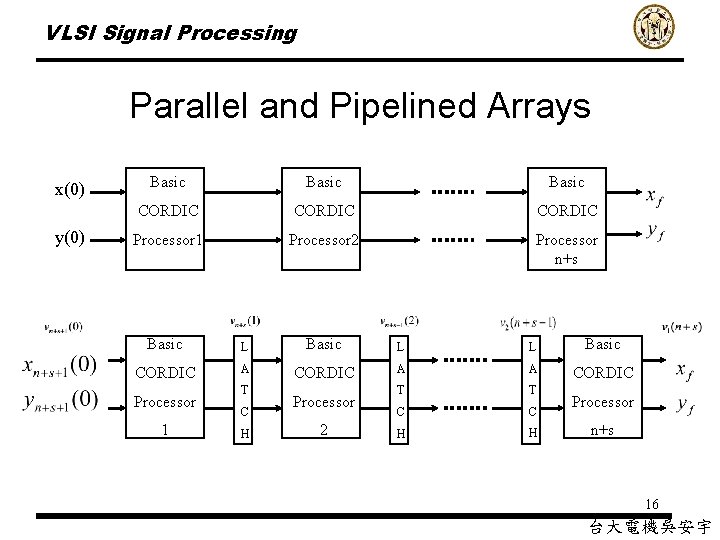

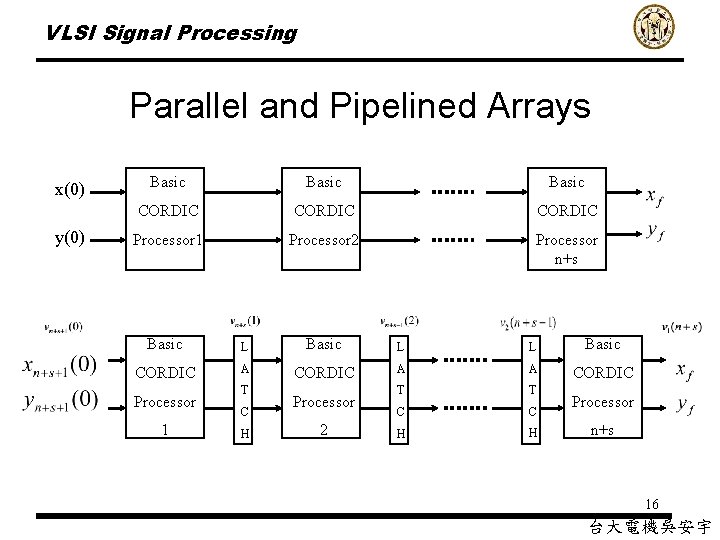

VLSI Signal Processing Parallel and Pipelined Arrays x(0) y(0) Basic CORDIC Processor 1 Processor 2 Processor n+s Basic L L Basic CORDIC A A CORDIC T T C C H H Processor 1 T C H Processor 2 Processor n+s 16 台大電機吳安宇

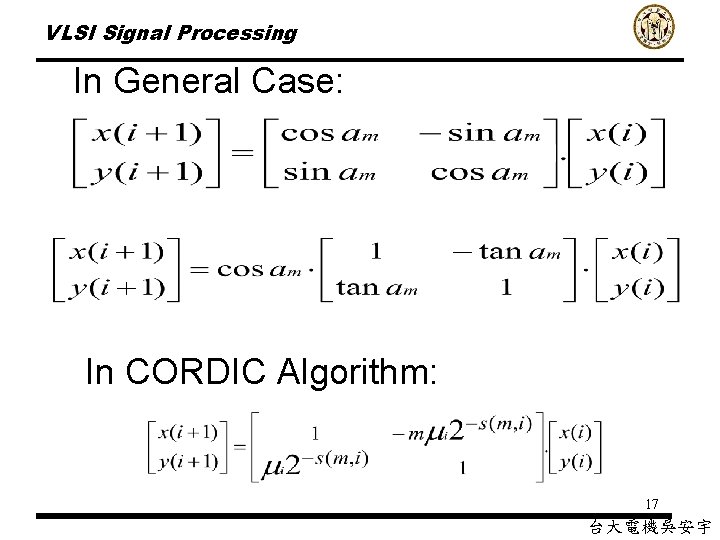

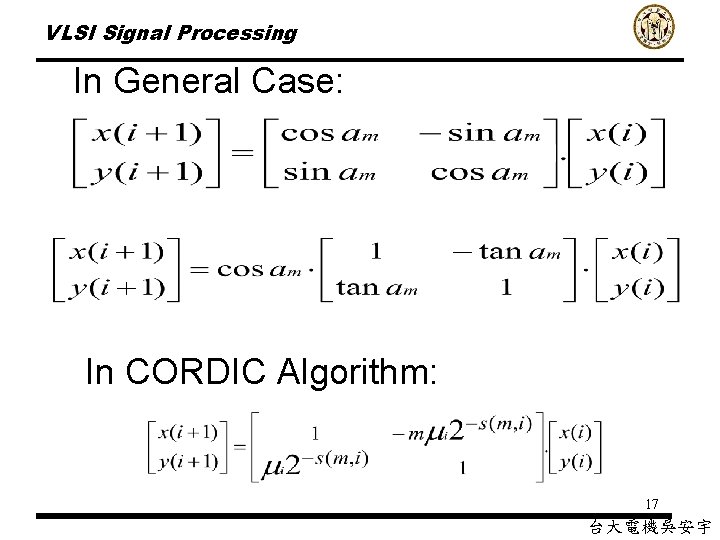

VLSI Signal Processing In General Case: In CORDIC Algorithm: 17 台大電機吳安宇

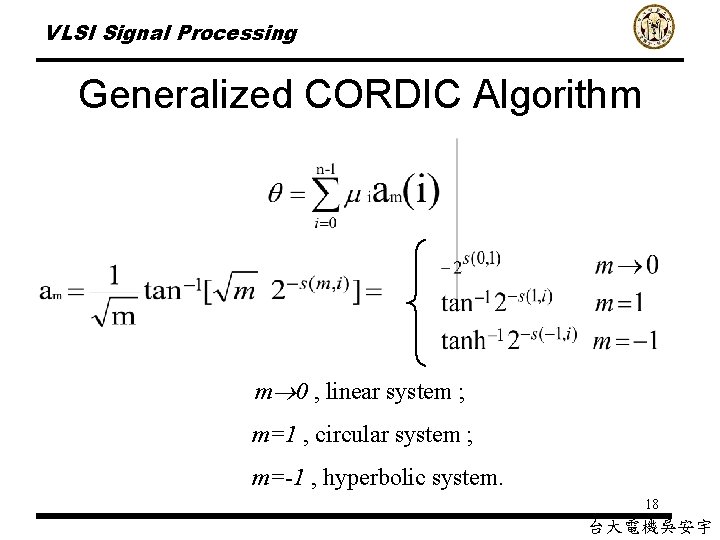

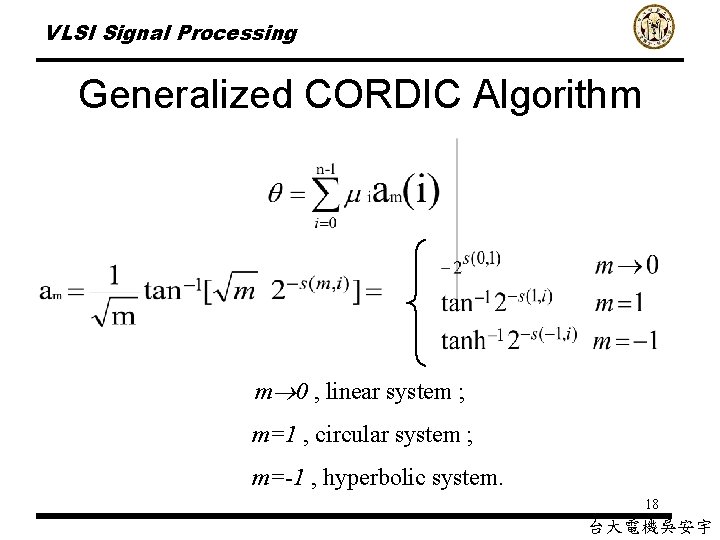

VLSI Signal Processing Generalized CORDIC Algorithm m 0 , linear system ; m=1 , circular system ; m=-1 , hyperbolic system. 18 台大電機吳安宇

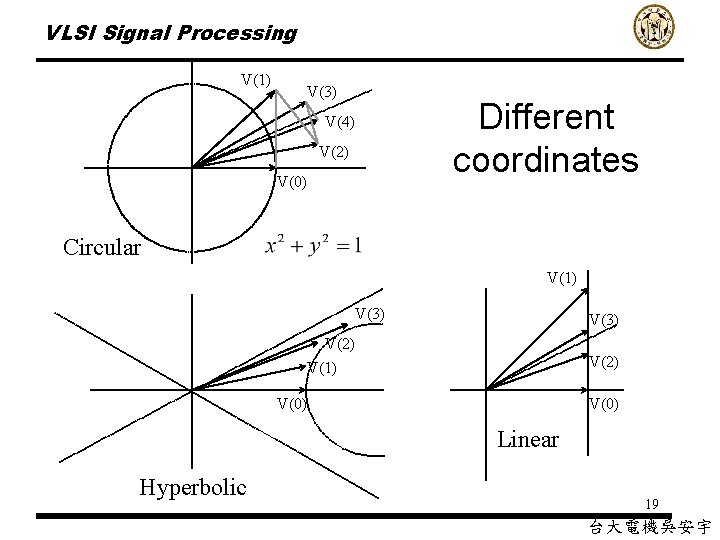

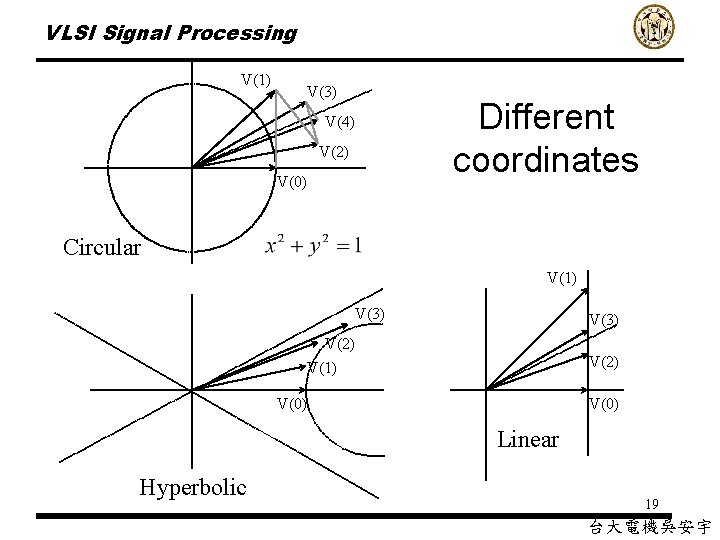

VLSI Signal Processing V(1) V(3) V(4) V(2) V(0) Different coordinates Circular V(1) V(3) V(2) V(1) V(0) Linear Hyperbolic 19 台大電機吳安宇

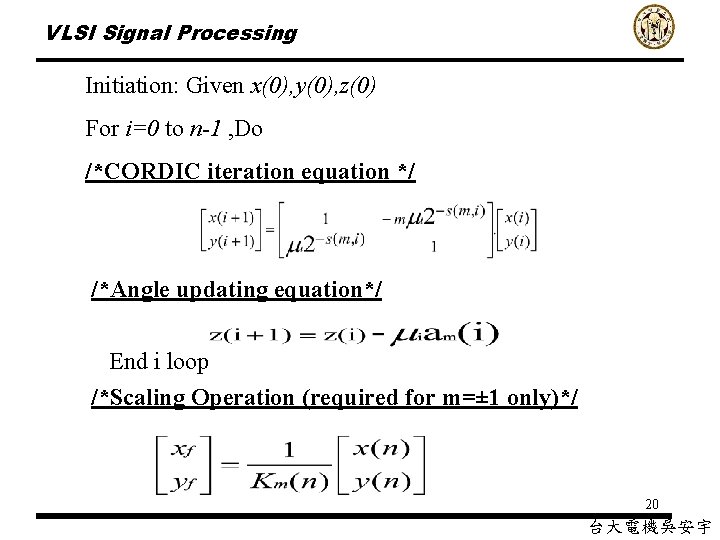

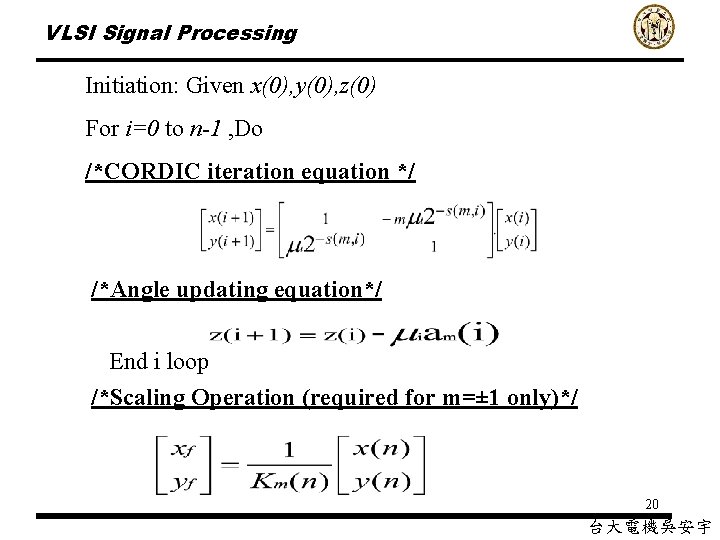

VLSI Signal Processing Initiation: Given x(0), y(0), z(0) For i=0 to n-1 , Do /*CORDIC iteration equation */ /*Angle updating equation*/ End i loop /*Scaling Operation (required for m=± 1 only)*/ 20 台大電機吳安宇

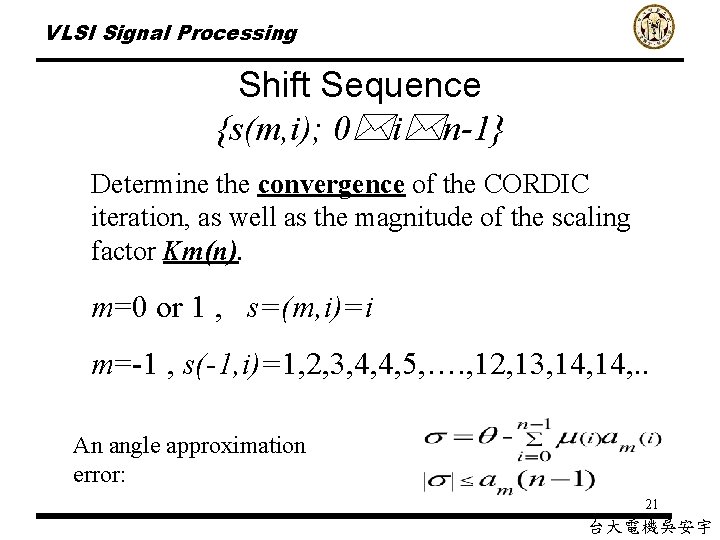

VLSI Signal Processing Shift Sequence {s(m, i); 0 i n-1} Determine the convergence of the CORDIC iteration, as well as the magnitude of the scaling factor Km(n). m=0 or 1 , s=(m, i)=i m=-1 , s(-1, i)=1, 2, 3, 4, 4, 5, …. , 12, 13, 14, . . An angle approximation error: 21 台大電機吳安宇

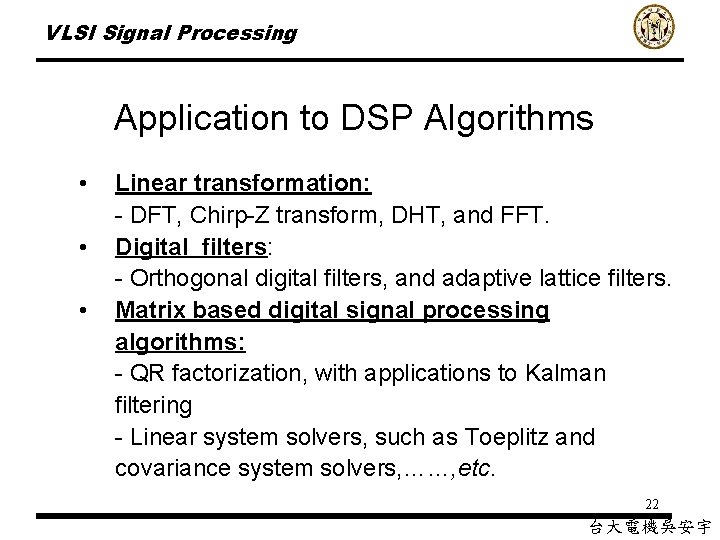

VLSI Signal Processing Application to DSP Algorithms • • • Linear transformation: - DFT, Chirp-Z transform, DHT, and FFT. Digital filters: - Orthogonal digital filters, and adaptive lattice filters. Matrix based digital signal processing algorithms: - QR factorization, with applications to Kalman filtering - Linear system solvers, such as Toeplitz and covariance system solvers, ……, etc. 22 台大電機吳安宇

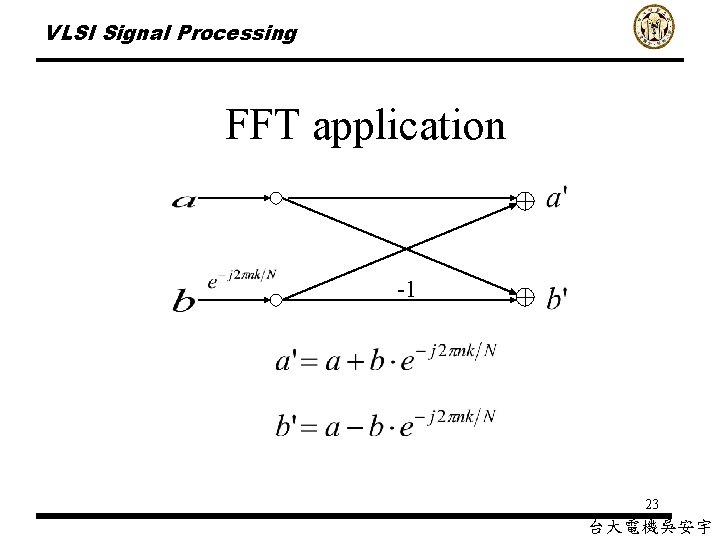

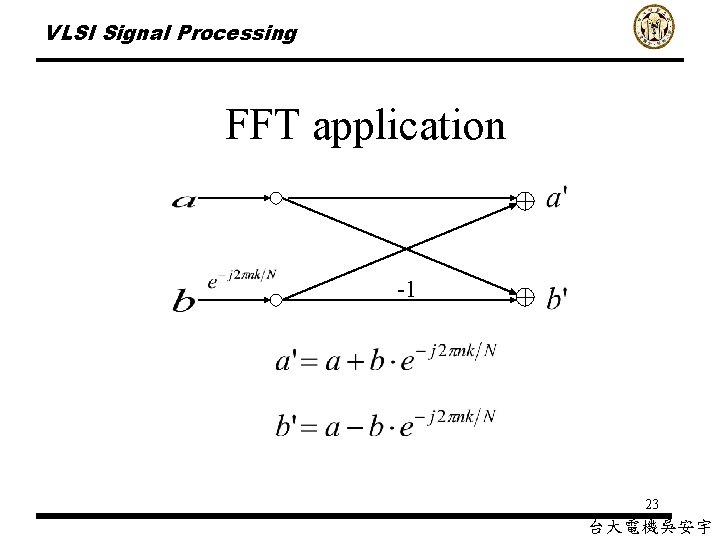

VLSI Signal Processing FFT application -1 23 台大電機吳安宇

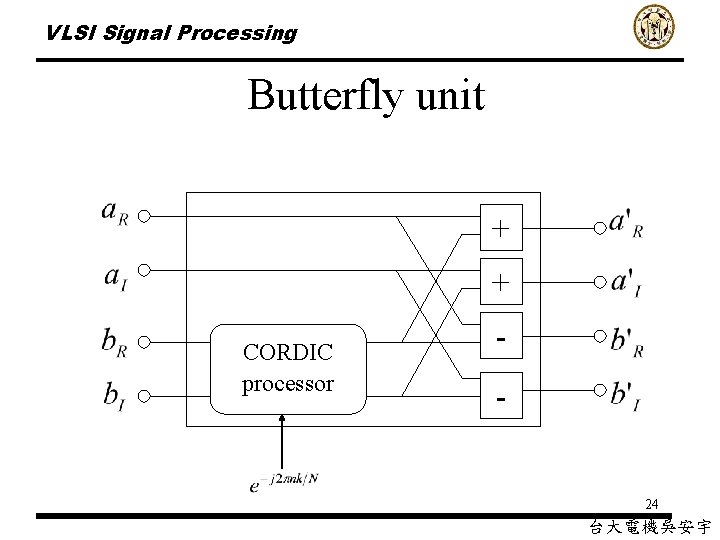

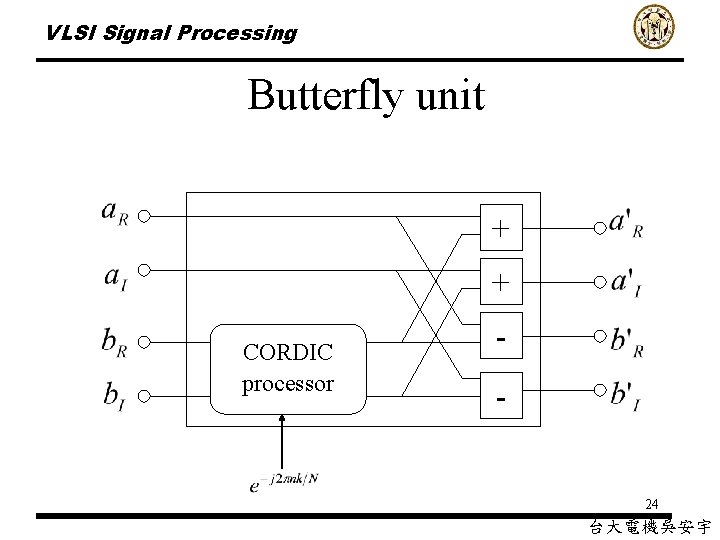

VLSI Signal Processing Butterfly unit + + CORDIC processor - 24 台大電機吳安宇

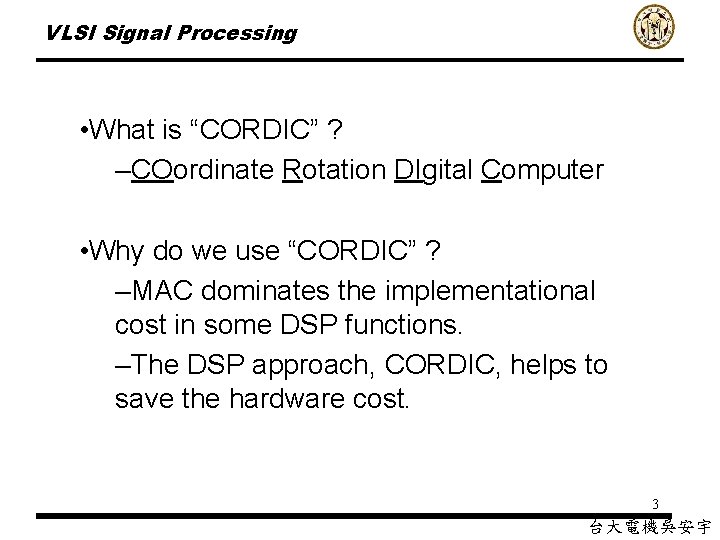

VLSI Signal Processing Conclusions 1. In some cases, CORDIC evaluates rotational functions more efficiently than MAC units. 2. CORDIC saves more hardware cost. 3. By the regularity, the CORDIC based architecture is very suitable for implementation with pipelined VLSI array processors. 4. The utility of the CORDIC based architecture lies in its generality and flexibility. 25 台大電機吳安宇