Topic 5 Processor Architecture Implementation Methodology 2122022 coursecpeg

- Slides: 27

Topic 5: Processor Architecture Implementation Methodology 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 1

Reading List • Slides: Topic 5 x • Henn & Patt: Chapter 5 • Other papers as assigned in class or homework 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 2

ABET Outcomes Ability to apply knowledge of science (e. g. , computer architecture and system organization, and related computer science issues), and engineering (e. g. , performance analysis and benchmarking, ISA simulation and verification) Ability to use the techniques, skills and modern engineering tools necessary for engineering practice Knowledge of related topics in computer science discipline 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 3

Outline • An overview • Datapath building blocks • Implementation of a simple (single-cycle) datapath • A multiple cycle implementation 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 4

Overview • The basic instruction execution flow • Some conventions - 32 bit datapath - clocking strategy (edge-triggered) • We focus on a subset of MIPS 2/12/2022 - Memory-reference instructions: lw, sw - ALU ops: add, sub, and, or - Branch equal instructions (beq) and the jump instruction (J) coursecpeg 323 -05 FTopic 5 -323. ppt 5

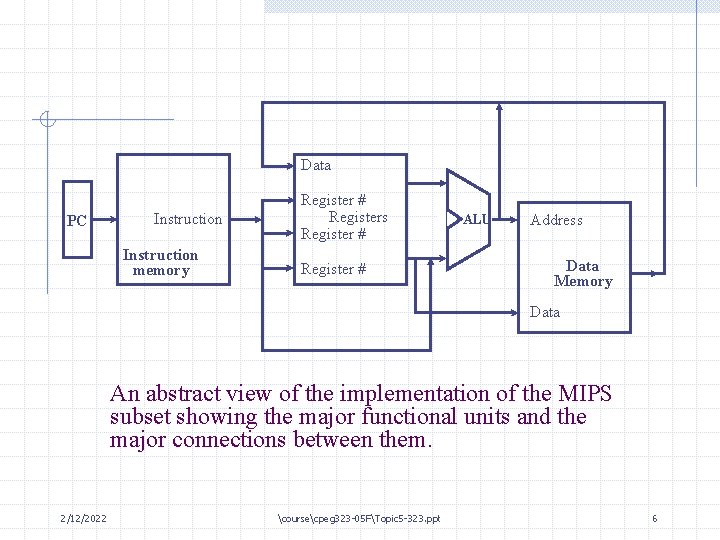

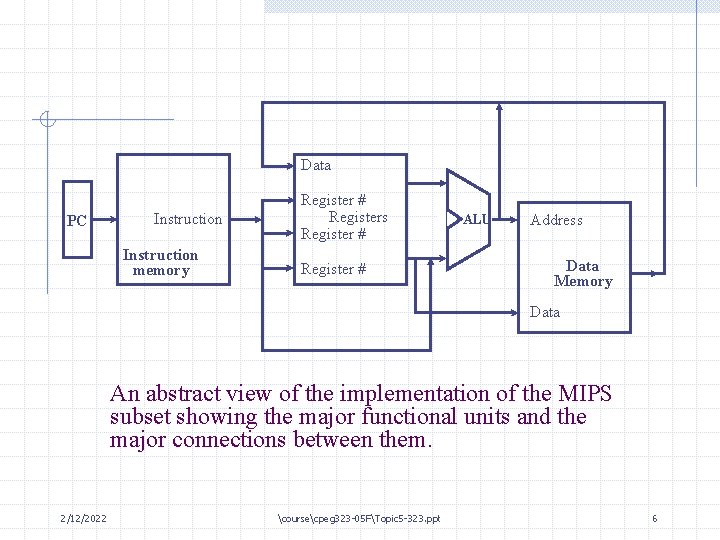

Data PC Instruction memory Register # Registers Register # ALU Address Data Memory Data An abstract view of the implementation of the MIPS subset showing the major functional units and the major connections between them. 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 6

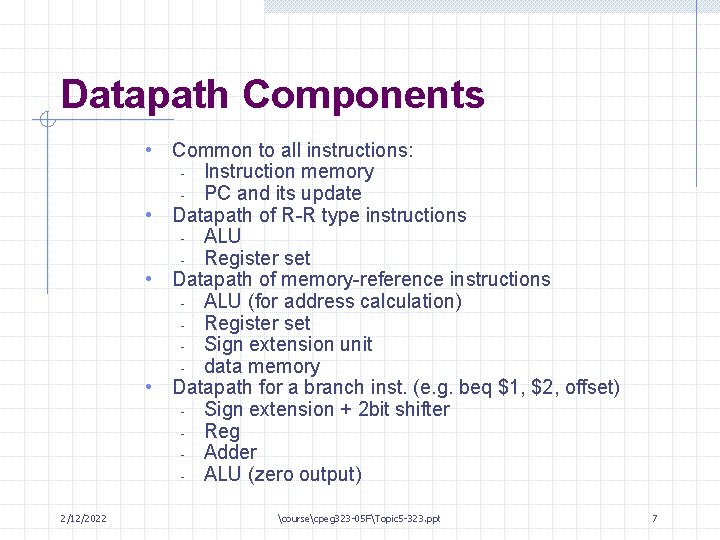

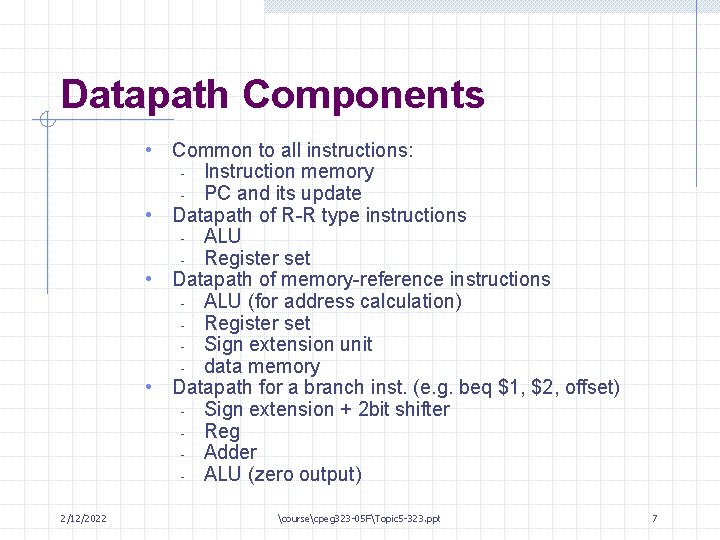

Datapath Components • Common to all instructions: Instruction memory - PC and its update • Datapath of R-R type instructions - ALU - Register set • Datapath of memory-reference instructions - ALU (for address calculation) - Register set - Sign extension unit - data memory • Datapath for a branch inst. (e. g. beq $1, $2, offset) - Sign extension + 2 bit shifter - Reg - Adder - ALU (zero output) - 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 7

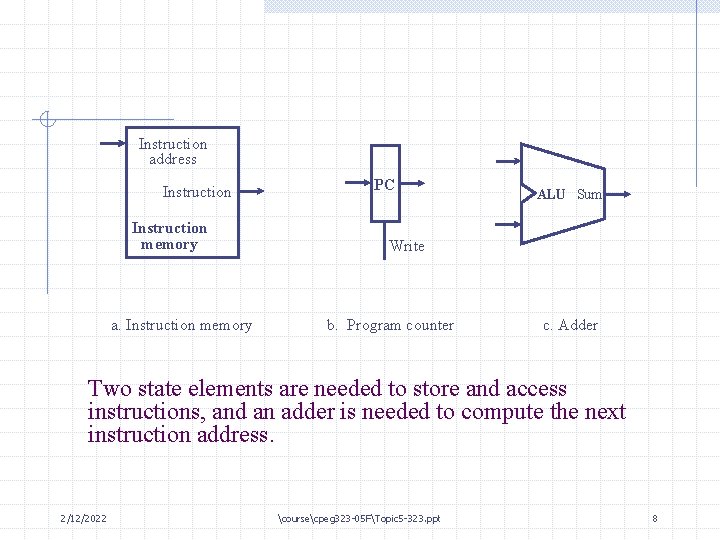

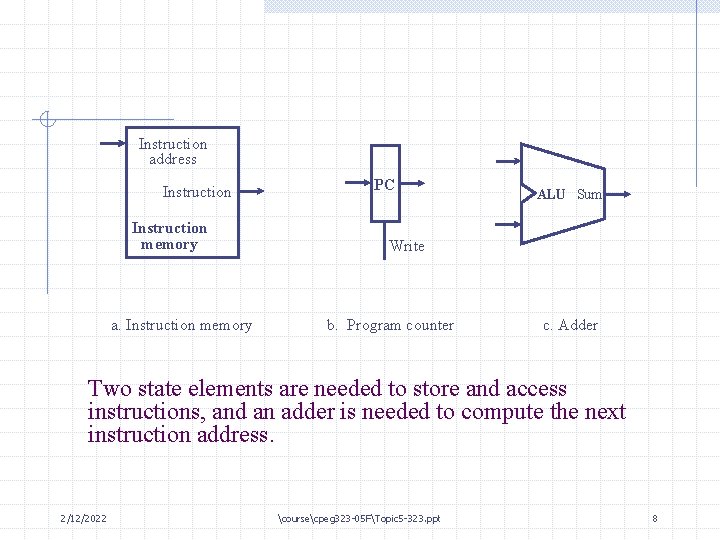

Instruction address Instruction memory a. Instruction memory PC ALU Sum Write b. Program counter c. Adder Two state elements are needed to store and access instructions, and an adder is needed to compute the next instruction address. 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 8

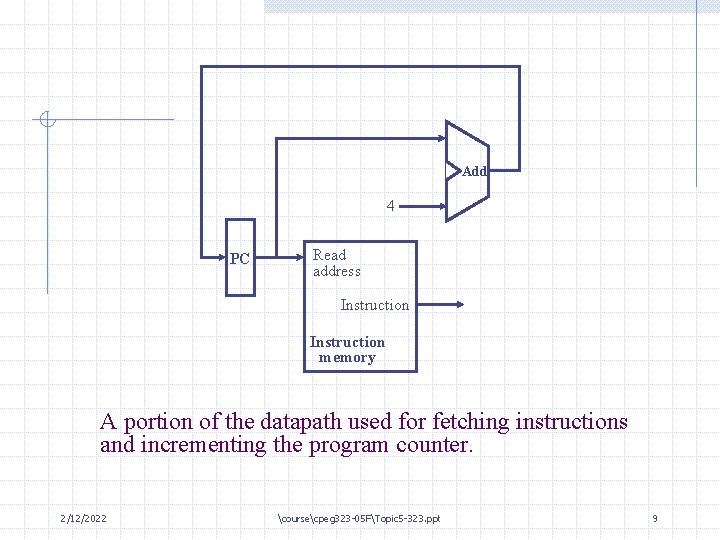

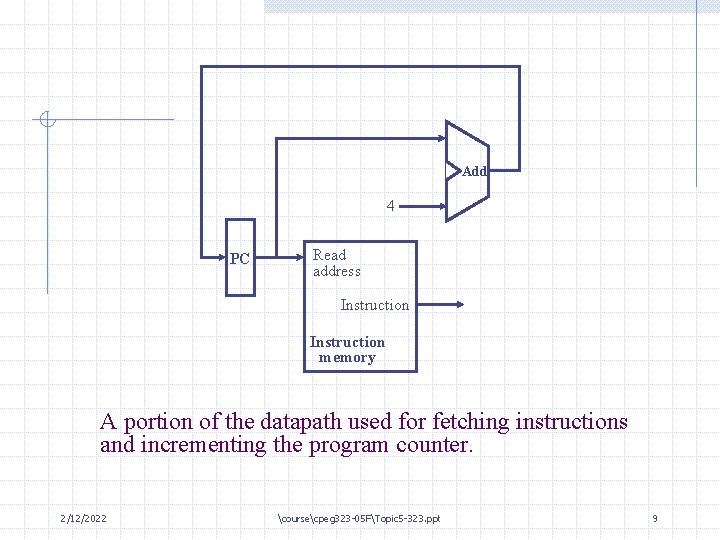

Add 4 PC Read address Instruction memory A portion of the datapath used for fetching instructions and incrementing the program counter. 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 9

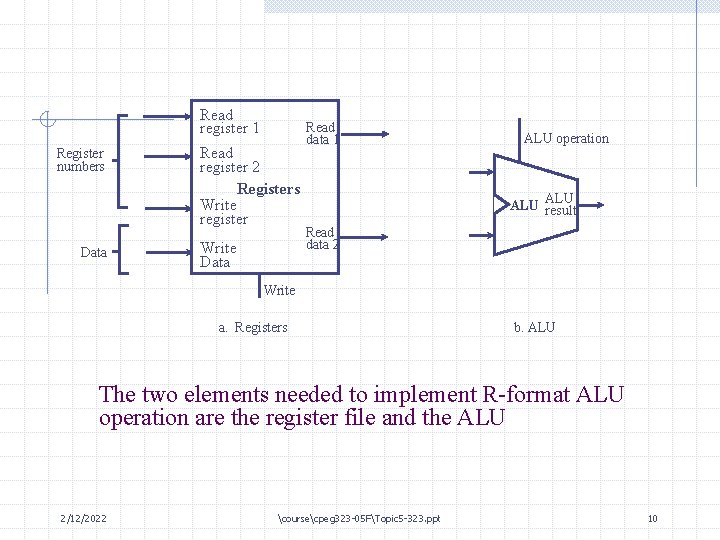

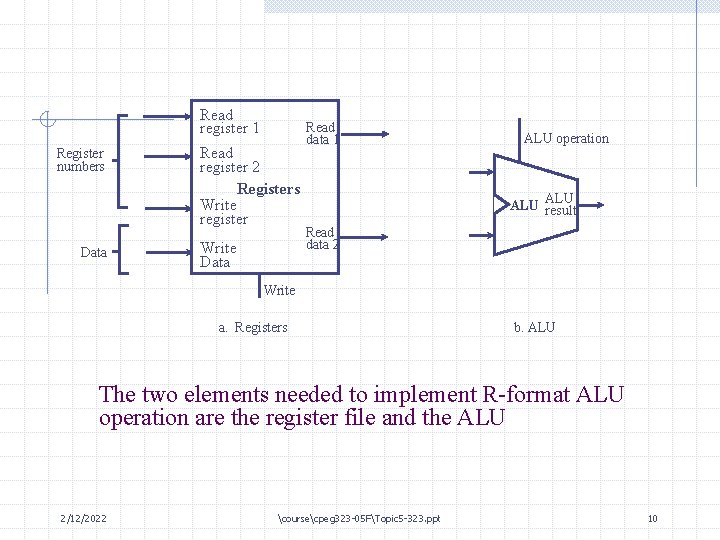

Read register 1 Register numbers Data Read register 2 Registers Write register Write Data Read data 1 ALU operation ALU result Read data 2 Write a. Registers b. ALU The two elements needed to implement R-format ALU operation are the register file and the ALU 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 10

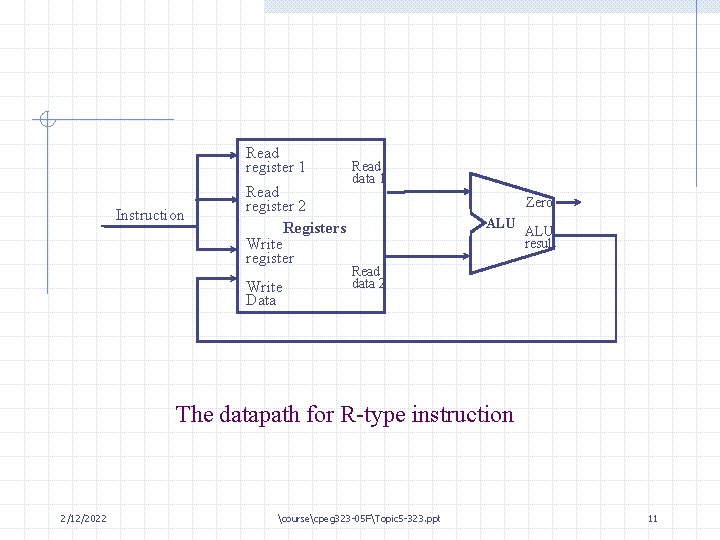

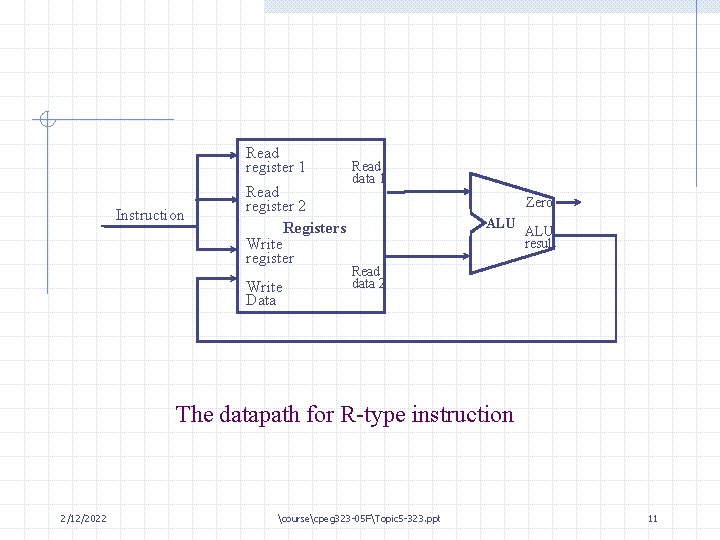

Read register 1 Instruction Read register 2 Registers Write register Write Data Read data 1 Zero ALU result Read data 2 The datapath for R-type instruction 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 11

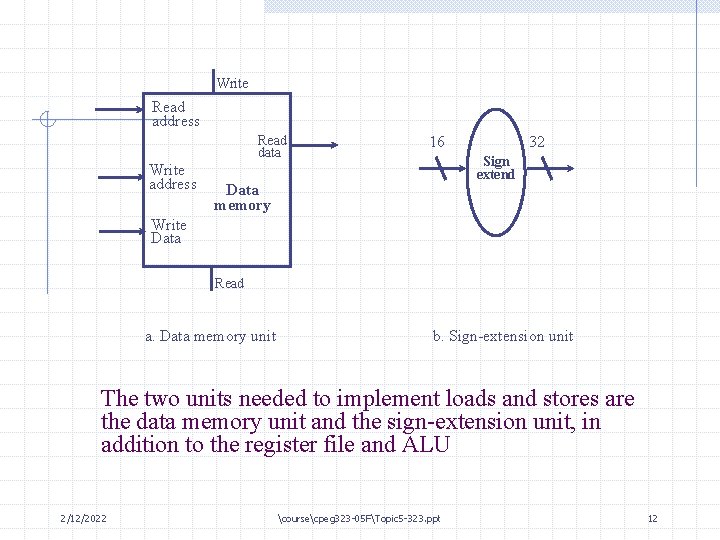

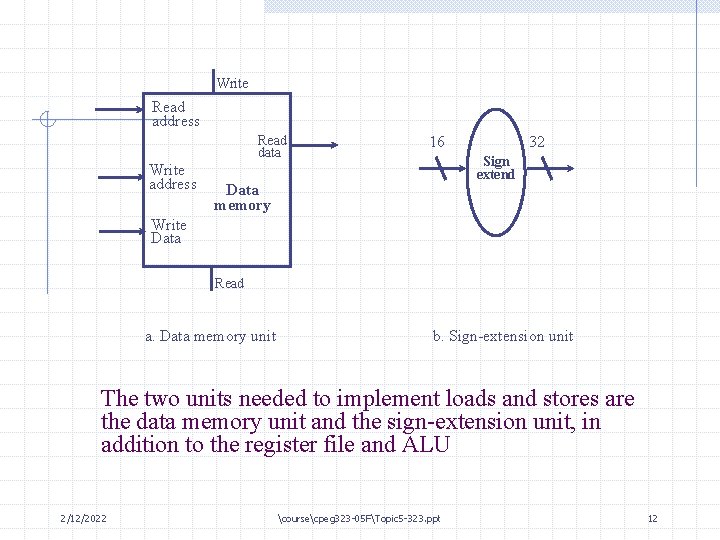

Write Read address Read data Write address 16 32 Sign extend Data memory Write Data Read a. Data memory unit b. Sign-extension unit The two units needed to implement loads and stores are the data memory unit and the sign-extension unit, in addition to the register file and ALU 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 12

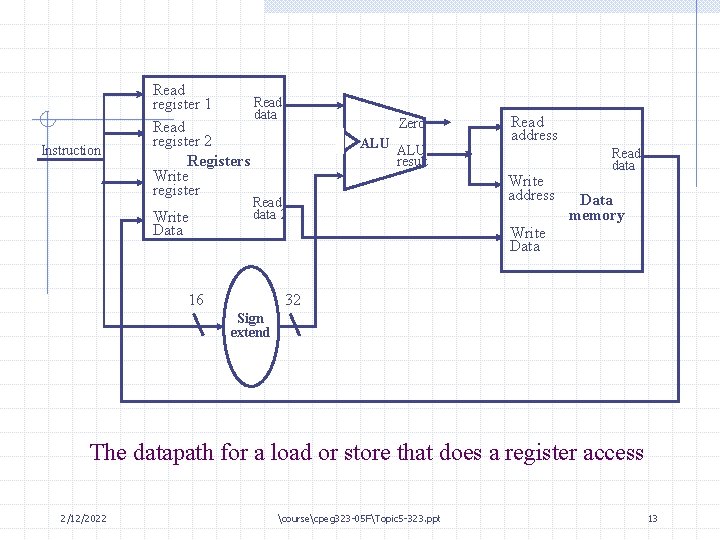

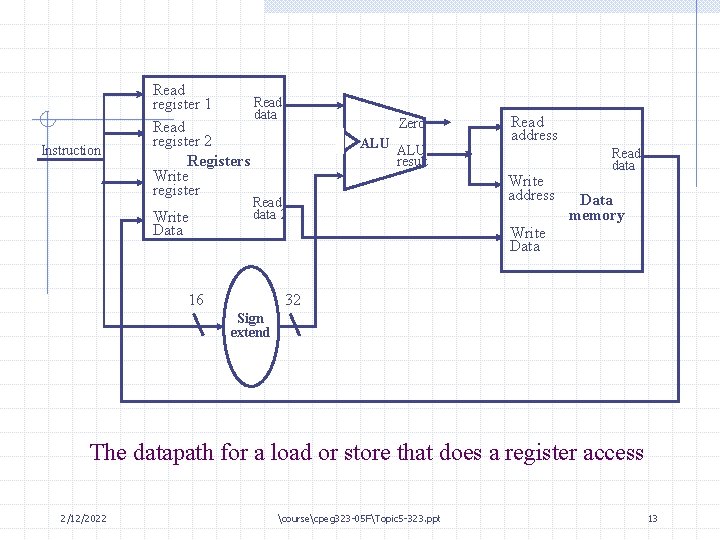

Instruction Read register 1 data 1 Read register 2 Registers Write register Write Data Zero ALU result Read data 2 Read address Write Data 16 Read data Data memory 32 Sign extend The datapath for a load or store that does a register access 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 13

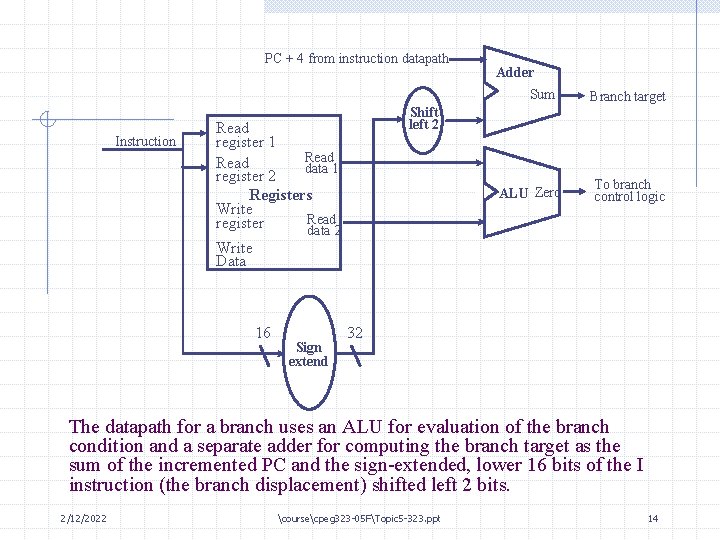

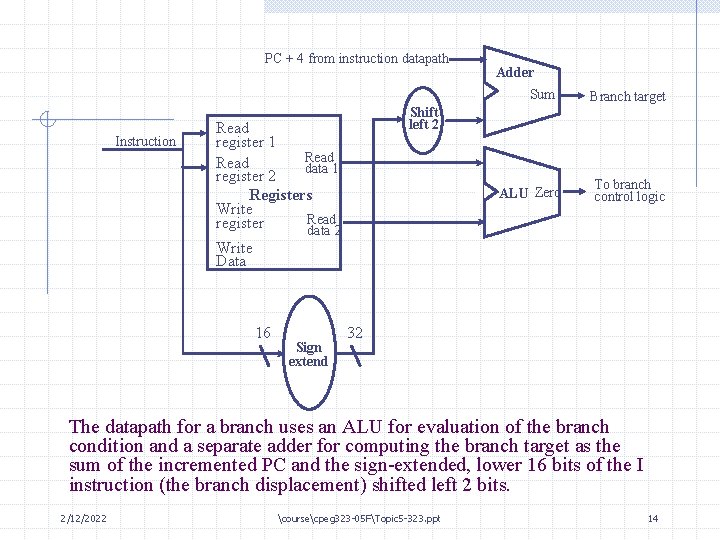

PC + 4 from instruction datapath Adder Sum Instruction Branch target Shift left 2 Read register 1 Read data 1 register 2 Registers Write Read register data 2 ALU Zero To branch control logic Write Data 16 Sign extend 32 The datapath for a branch uses an ALU for evaluation of the branch condition and a separate adder for computing the branch target as the sum of the incremented PC and the sign-extended, lower 16 bits of the I instruction (the branch displacement) shifted left 2 bits. 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 14

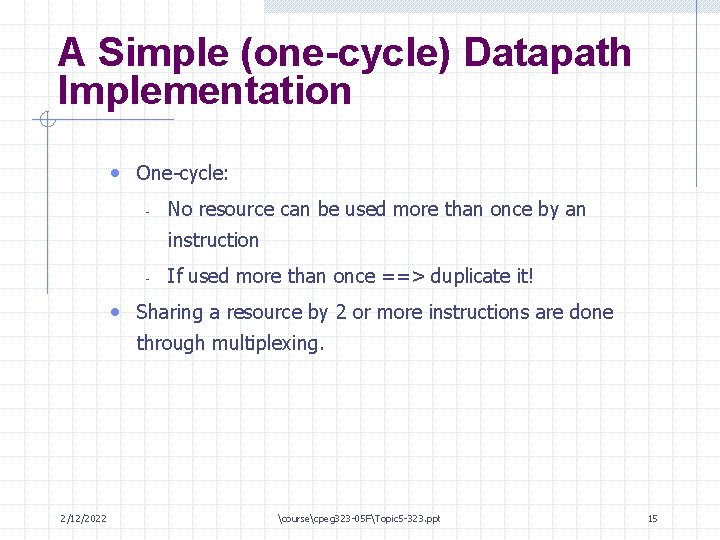

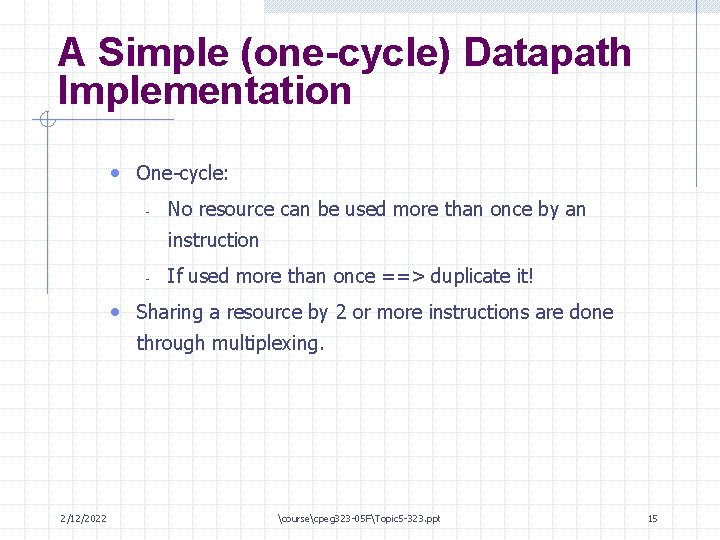

A Simple (one-cycle) Datapath Implementation • One-cycle: - No resource can be used more than once by an instruction - If used more than once ==> duplicate it! • Sharing a resource by 2 or more instructions are done through multiplexing. 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 15

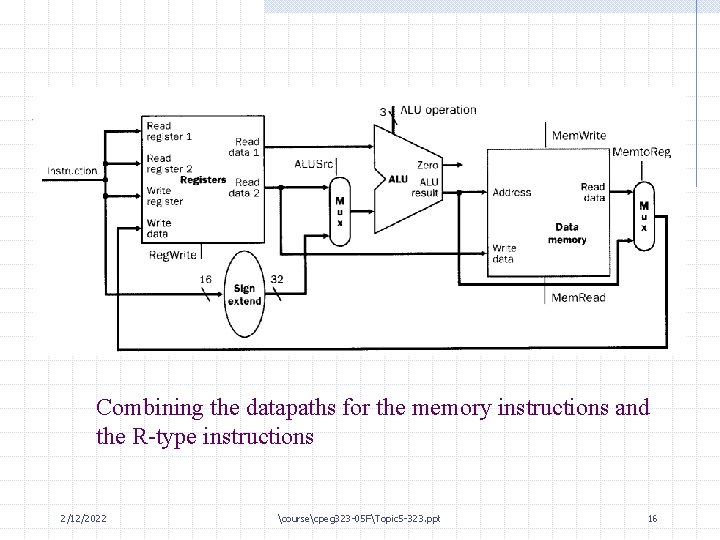

Combining the datapaths for the memory instructions and the R-type instructions 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 16

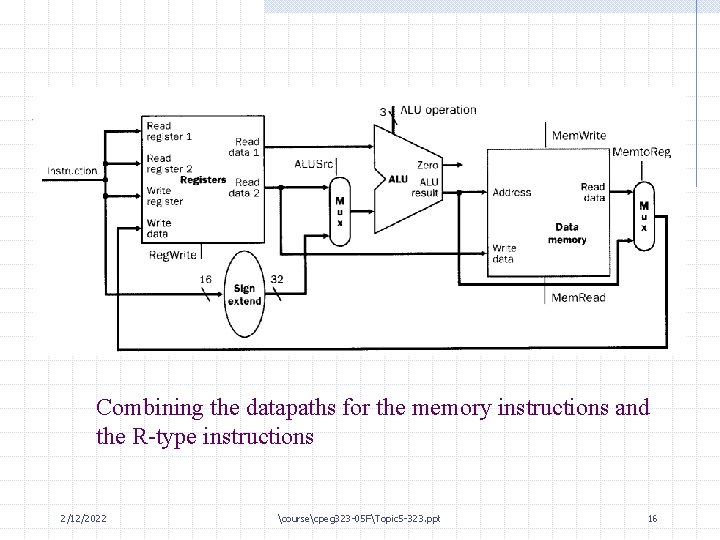

The instruction fetch portion of the datapath is appended to the datapath that handles memory and ALU instructions. 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 17

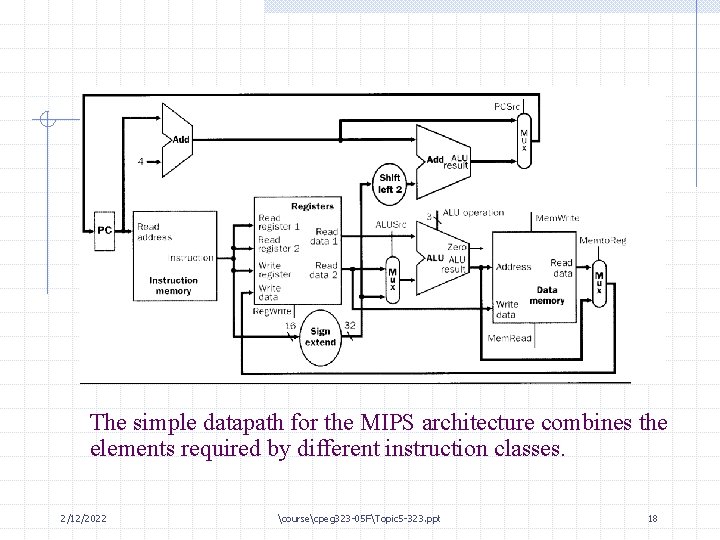

The simple datapath for the MIPS architecture combines the elements required by different instruction classes. 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 18

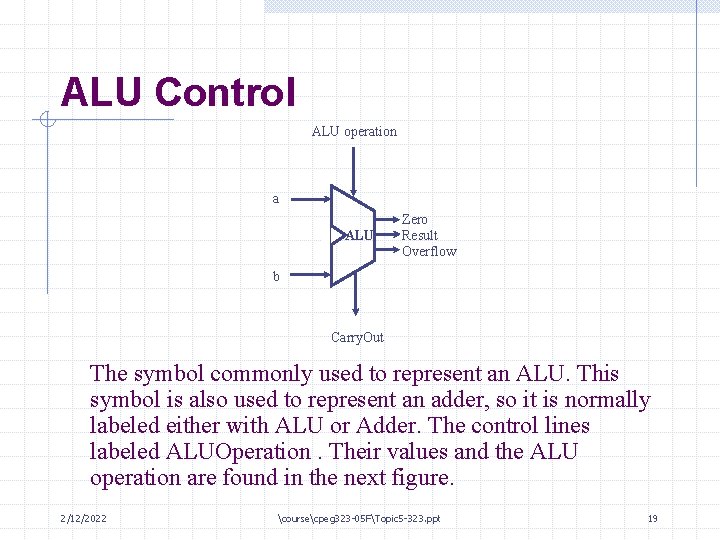

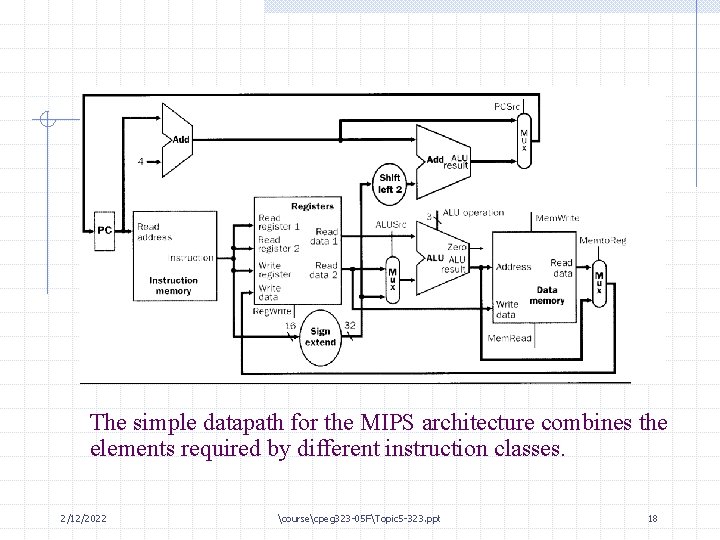

ALU Control ALU operation a ALU Zero Result Overflow b Carry. Out The symbol commonly used to represent an ALU. This symbol is also used to represent an adder, so it is normally labeled either with ALU or Adder. The control lines labeled ALUOperation. Their values and the ALU operation are found in the next figure. 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 19

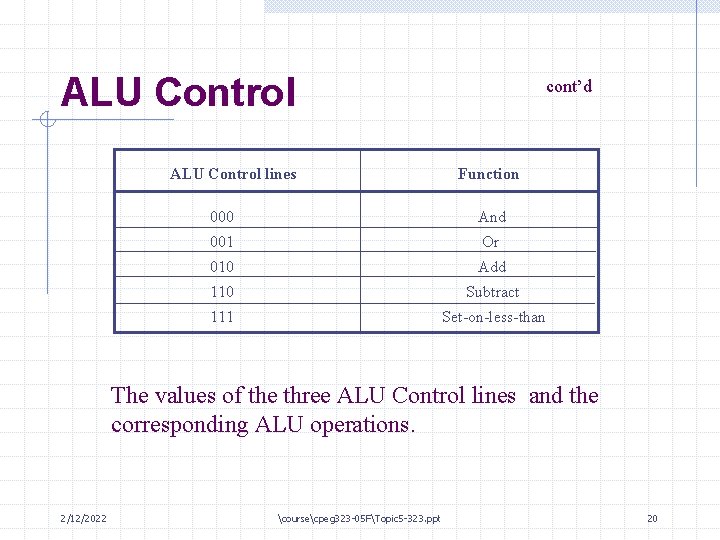

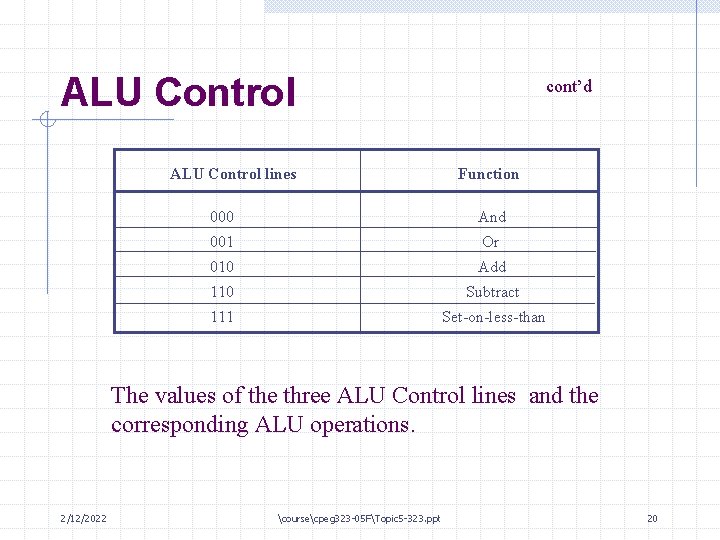

ALU Control lines cont’d Function 000 And 001 Or 010 Add 110 Subtract 111 Set-on-less-than The values of the three ALU Control lines and the corresponding ALU operations. 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 20

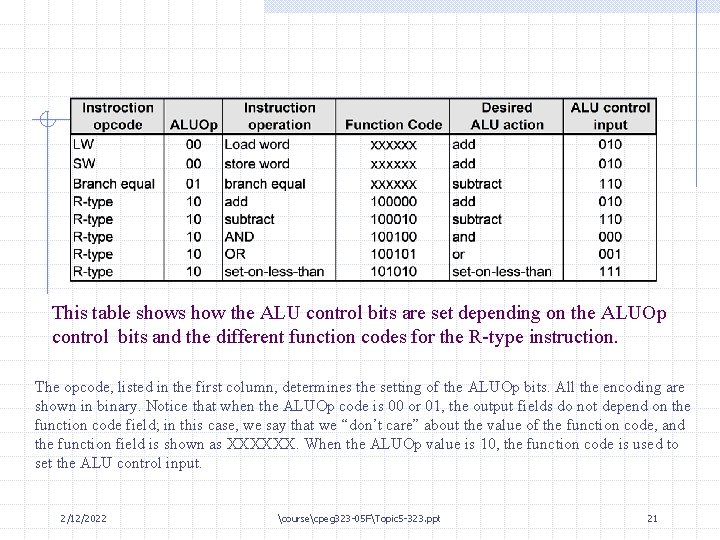

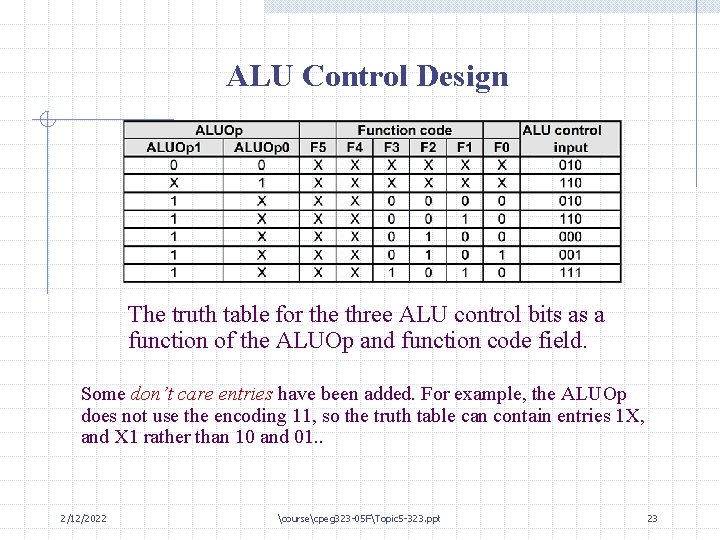

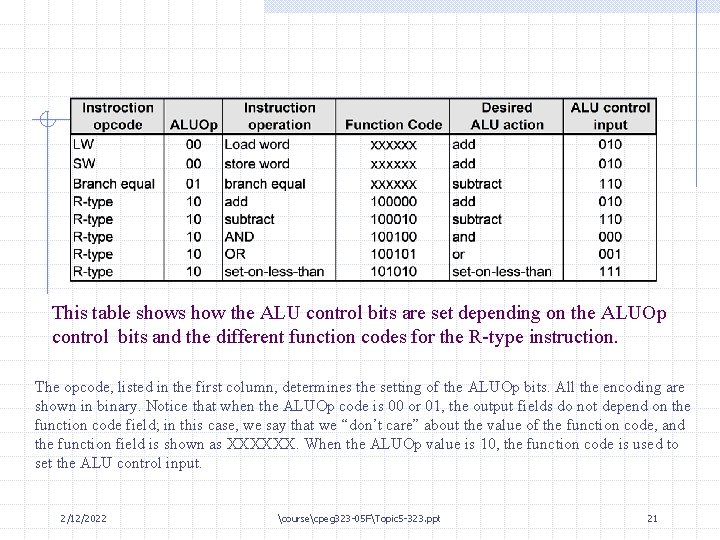

This table shows how the ALU control bits are set depending on the ALUOp control bits and the different function codes for the R-type instruction. The opcode, listed in the first column, determines the setting of the ALUOp bits. All the encoding are shown in binary. Notice that when the ALUOp code is 00 or 01, the output fields do not depend on the function code field; in this case, we say that we “don’t care” about the value of the function code, and the function field is shown as XXXXXX. When the ALUOp value is 10, the function code is used to set the ALU control input. 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 21

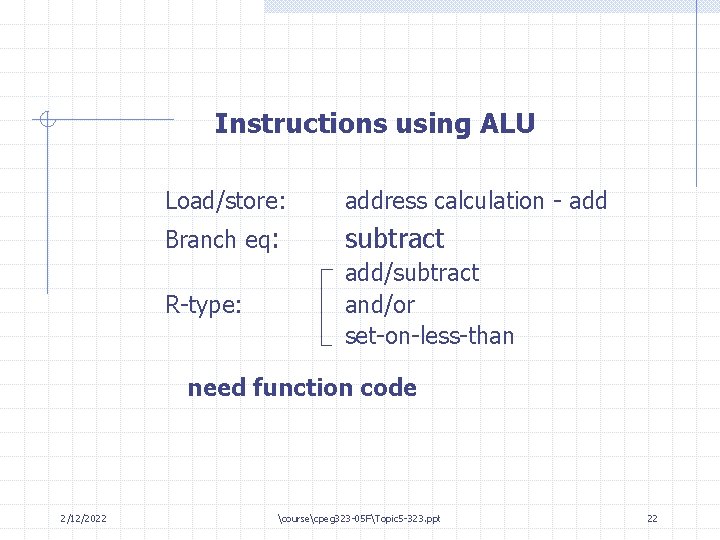

Instructions using ALU Load/store: address calculation - add Branch eq: subtract R-type: add/subtract and/or set-on-less-than need function code 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 22

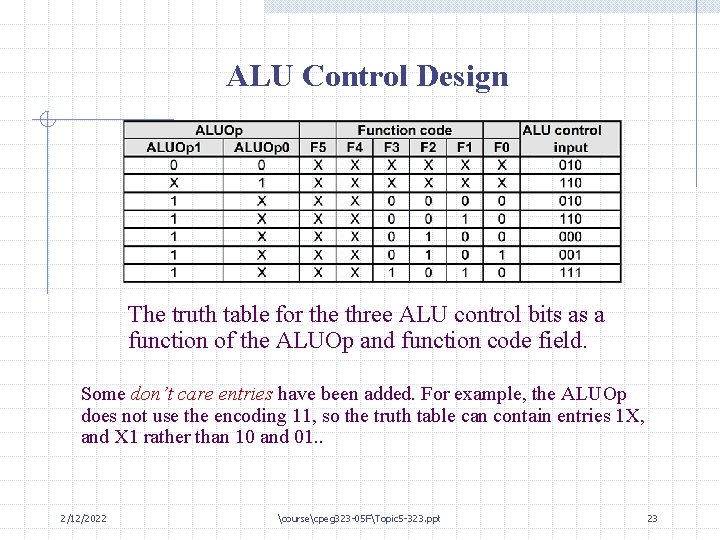

ALU Control Design The truth table for the three ALU control bits as a function of the ALUOp and function code field. Some don’t care entries have been added. For example, the ALUOp does not use the encoding 11, so the truth table can contain entries 1 X, and X 1 rather than 10 and 01. . 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 23

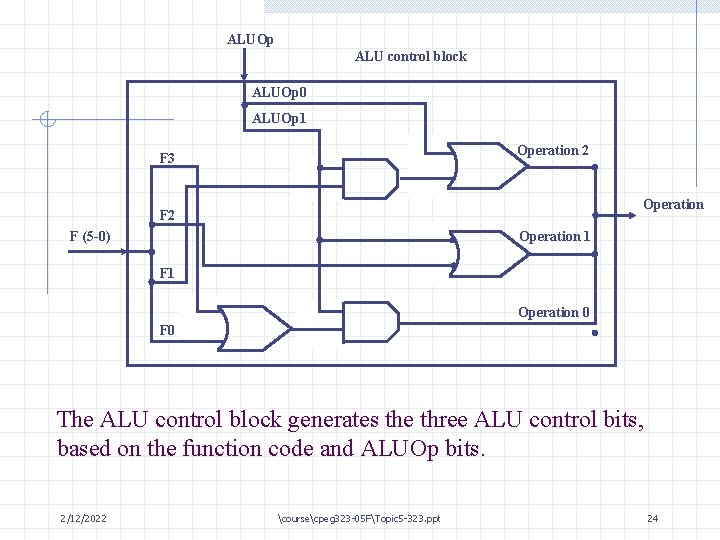

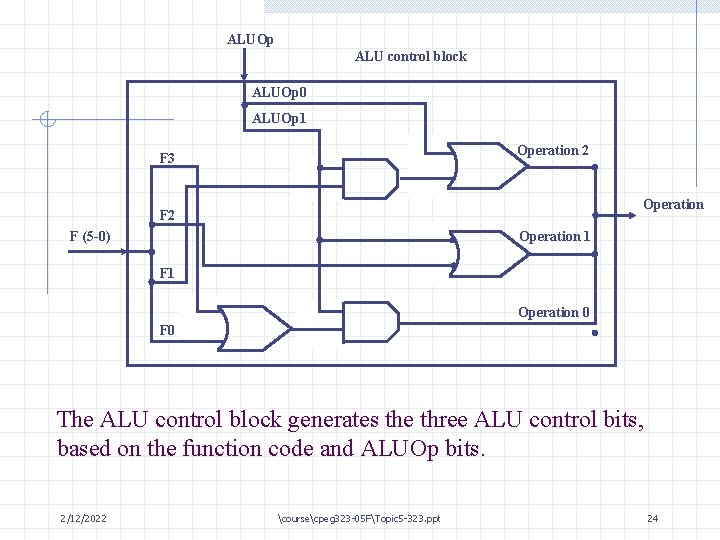

ALUOp ALU control block ALUOp 0 ALUOp 1 Operation 2 F 3 Operation F 2 F (5 -0) Operation 1 F 1 Operation 0 F 0 The ALU control block generates the three ALU control bits, based on the function code and ALUOp bits. 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 24

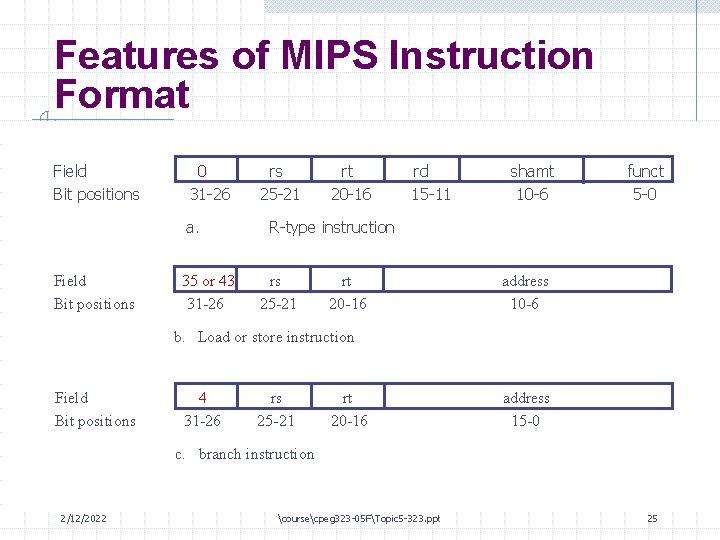

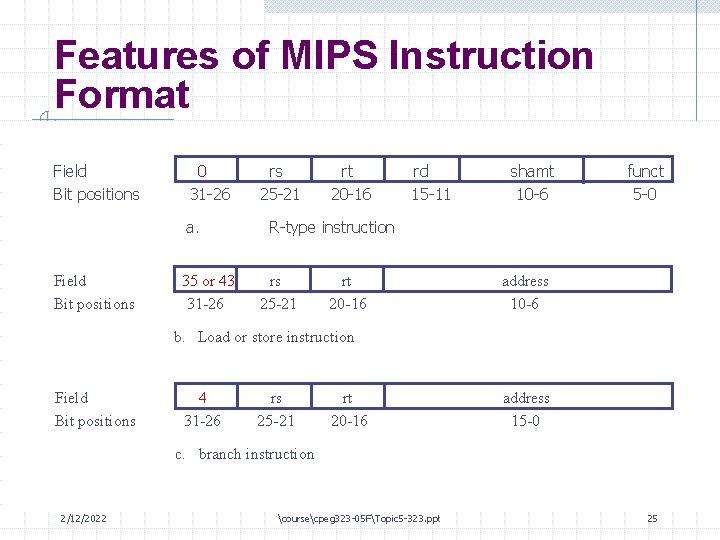

Features of MIPS Instruction Format Field Bit positions 0 31 -26 a. Field Bit positions 35 or 43 31 -26 rs 25 -21 rt 20 -16 rd 15 -11 shamt 10 -6 funct 5 -0 R-type instruction rs 25 -21 rt 20 -16 address 10 -6 b. Load or store instruction Field Bit positions 4 31 -26 rs 25 -21 rt 20 -16 address 15 -0 c. branch instruction 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 25

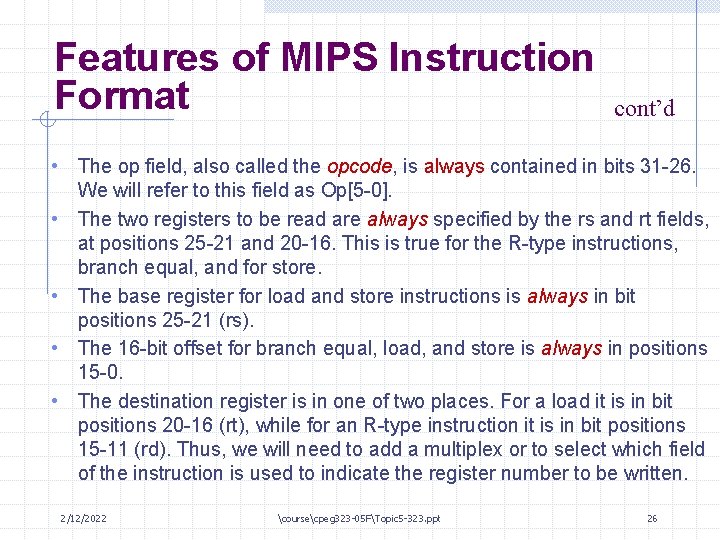

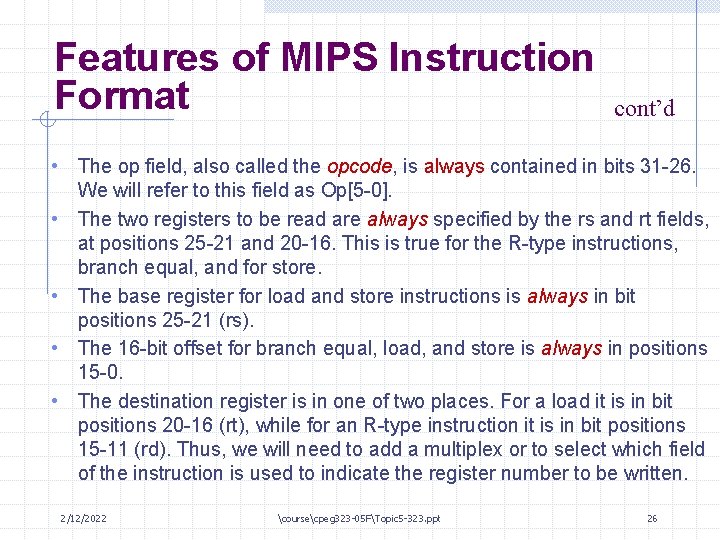

Features of MIPS Instruction Format cont’d • The op field, also called the opcode, is always contained in bits 31 -26. • • We will refer to this field as Op[5 -0]. The two registers to be read are always specified by the rs and rt fields, at positions 25 -21 and 20 -16. This is true for the R-type instructions, branch equal, and for store. The base register for load and store instructions is always in bit positions 25 -21 (rs). The 16 -bit offset for branch equal, load, and store is always in positions 15 -0. The destination register is in one of two places. For a load it is in bit positions 20 -16 (rt), while for an R-type instruction it is in bit positions 15 -11 (rd). Thus, we will need to add a multiplex or to select which field of the instruction is used to indicate the register number to be written. 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 26

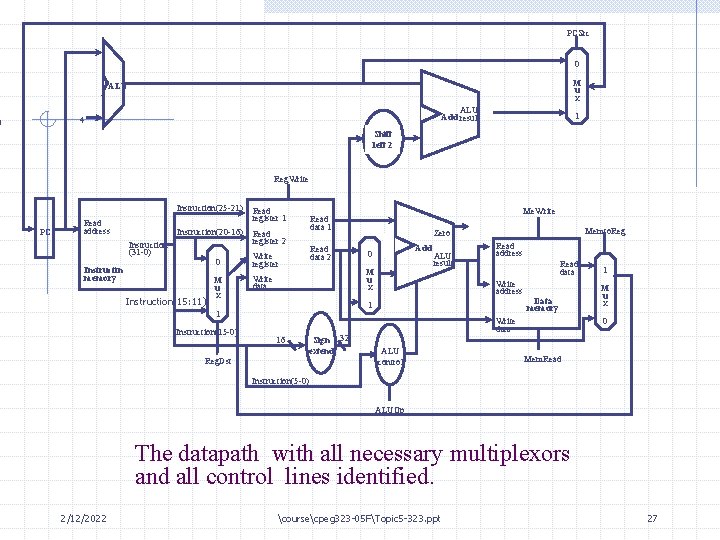

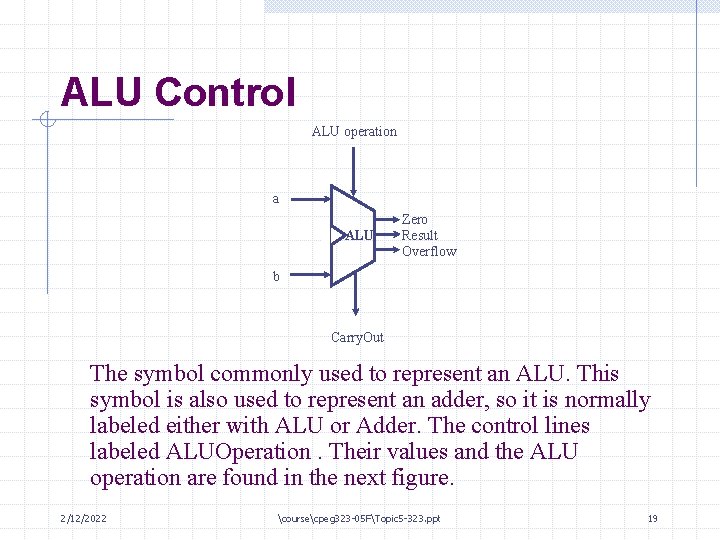

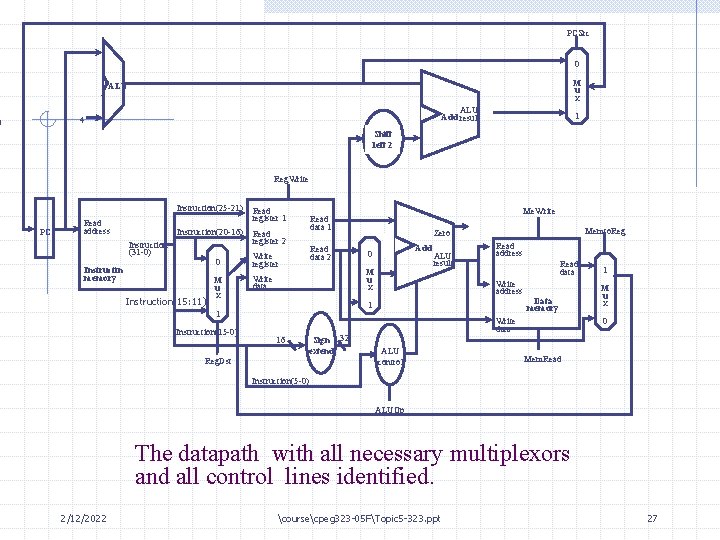

PCSrc 0 M u x ALU Add result 4 1 Shift left 2 Reg. Write Instruction(25 -21) PC Read address Instruction(20 -16) Instruction (31 -0) 0 Instructin memory Instruction(15: 11) M u x Read register 1 Read register 2 Read data 2 Write register Write data Memto. Reg Zero Add 0 M u x ALU result Read address Read data Write address 1 1 Instruction(15 -0) Me. Write Read data 1 16 Sign 32 extend Reg. Dst Data memory M u x 0 Write data ALU control 1 Mem. Read Instruction(5 -0) ALUOp The datapath with all necessary multiplexors and all control lines identified. 2/12/2022 coursecpeg 323 -05 FTopic 5 -323. ppt 27