Topic 3 b Computer Arithmetic ALU Design Introduction

Topic 3 b Computer Arithmetic: ALU Design Introduction to Computer Systems Engineering (CPEG 323) 2020/11/9 cpeg 323 -05 FTopic 3 b 1

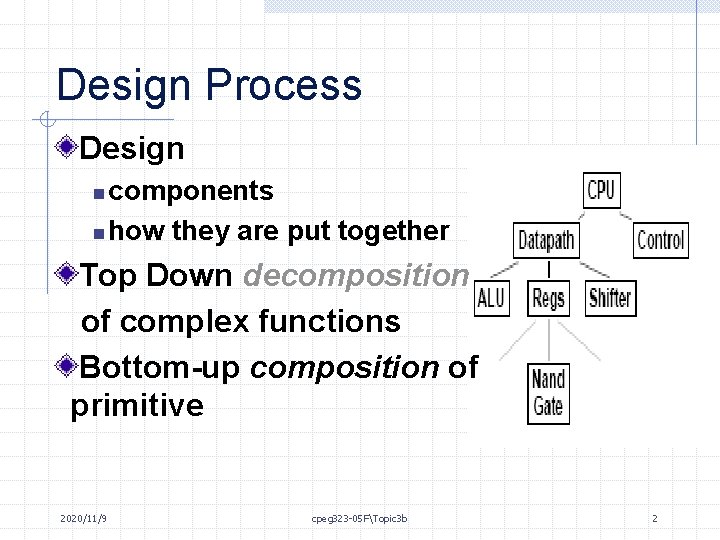

Design Process Design components n how they are put together n Top Down decomposition of complex functions Bottom-up composition of primitive 2020/11/9 cpeg 323 -05 FTopic 3 b 2

Problem: Design an ALU Operations n add, addu, subu, addiu w 2’s complement adder/sub with overflow detection n and, or, andi, ori wbitwise operations Total number of operations = 10 2020/11/9 cpeg 323 -05 FTopic 3 b 3

Design: divide & conquer method Break the problem into simpler parts n n n Work on the parts Put pieces together Verify solution works as a whole Example: Separate immediate instructions from the rest. n Process immediates before ALU w ALU inputs now uniform n 6 non-immediate operations remain w Need 3 bits to specify the ALU mode 2020/11/9 cpeg 323 -05 FTopic 3 b 4

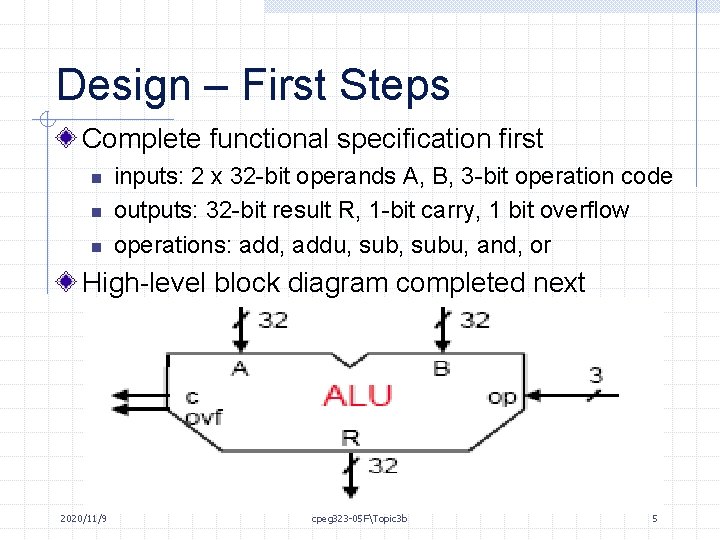

Design – First Steps Complete functional specification first n n n inputs: 2 x 32 -bit operands A, B, 3 -bit operation code outputs: 32 -bit result R, 1 -bit carry, 1 bit overflow operations: add, addu, subu, and, or High-level block diagram completed next 2020/11/9 cpeg 323 -05 FTopic 3 b 5

Design – Reducing the problem to something simpler For our ALU, reduce 32 -bit problem into simpler 1 -bit slices. n Changes big combinational problem to a small combinational problem Put the pieces together to solve the big problem. 2020/11/9 cpeg 323 -05 FTopic 3 b 6

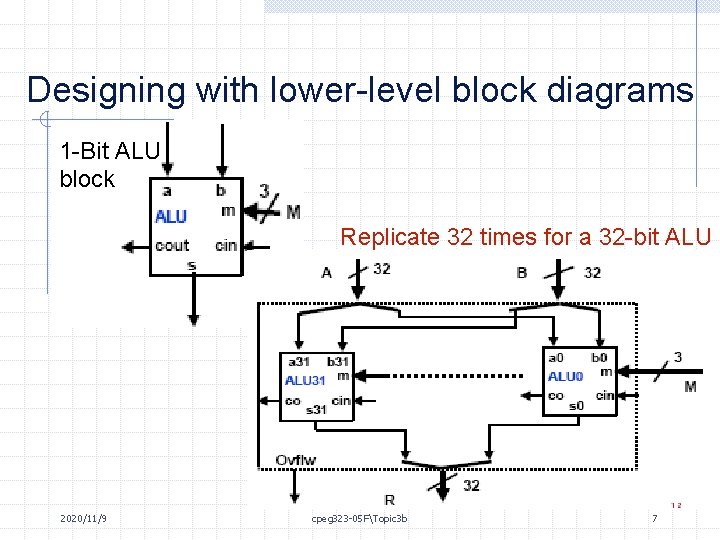

Designing with lower-level block diagrams 1 -Bit ALU block Replicate 32 times for a 32 -bit ALU Replicate 32 times for a 32 bit ALU 2020/11/9 cpeg 323 -05 FTopic 3 b 7

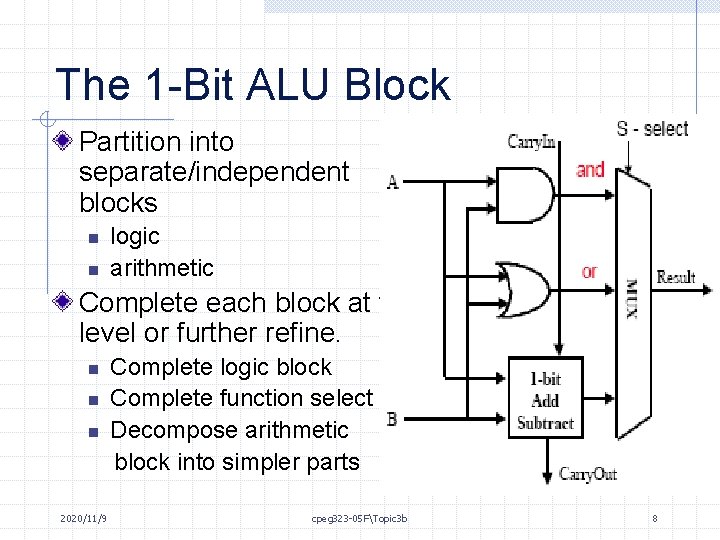

The 1 -Bit ALU Block Partition into separate/independent blocks n n logic arithmetic Complete each block at this level or further refine. n n n 2020/11/9 Complete logic block Complete function select Decompose arithmetic block into simpler parts cpeg 323 -05 FTopic 3 b 8

1 -bit Add Computing A + B n Sum= (a *b*Ci)+ (a *b* Ci)+ (a * b*Ci)+(a *b*Ci) n n Co = (a* Ci) + (b * Ci) + (a * b) This is called full adder. A half adder assumes no Ci. Can you draw the 1 -bit adder according to the above logic? # of gate delays for Sum = 3 # of gate delays for Carry = 2 2020/11/9 cpeg 323 -05 FTopic 3 b 9

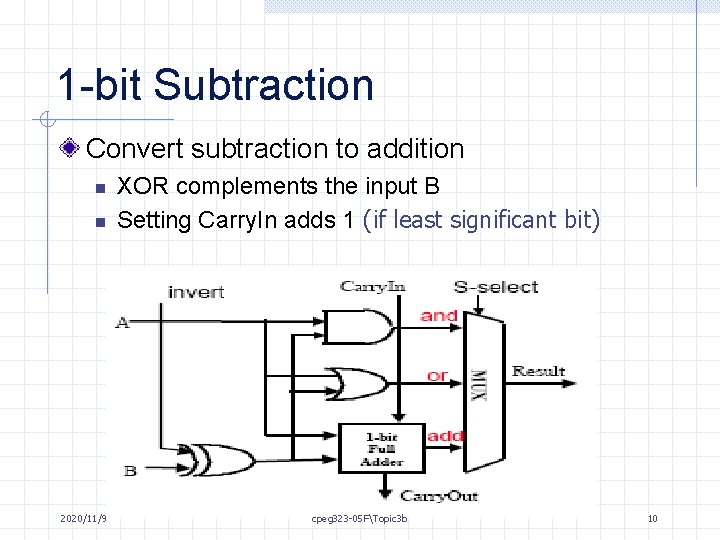

1 -bit Subtraction Convert subtraction to addition n n 2020/11/9 XOR complements the input B Setting Carry. In adds 1 (if least significant bit) cpeg 323 -05 FTopic 3 b 10

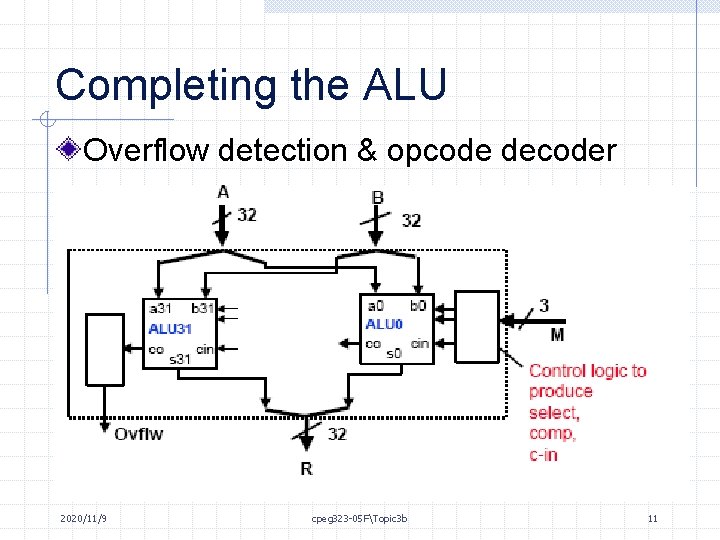

Completing the ALU Overflow detection & opcode decoder 2020/11/9 cpeg 323 -05 FTopic 3 b 11

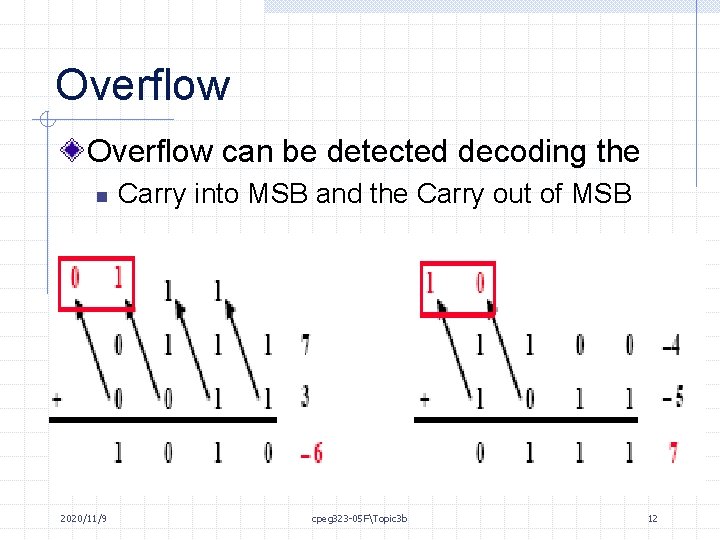

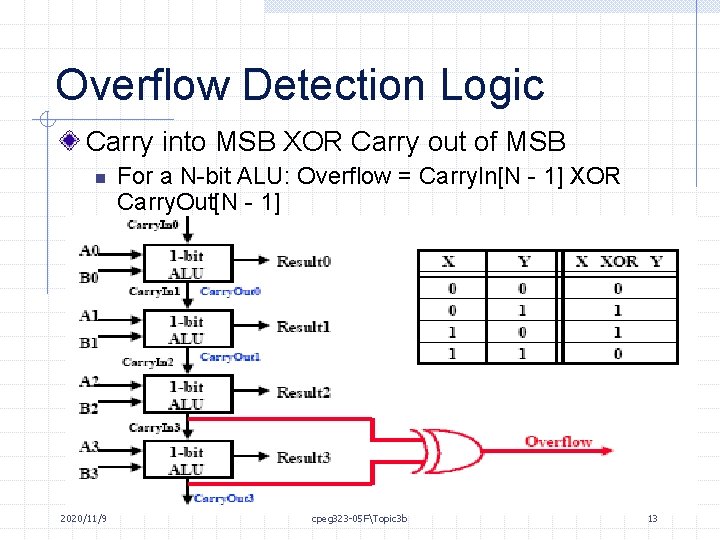

Overflow can be detected decoding the n 2020/11/9 Carry into MSB and the Carry out of MSB cpeg 323 -05 FTopic 3 b 12

Overflow Detection Logic Carry into MSB XOR Carry out of MSB n 2020/11/9 For a N-bit ALU: Overflow = Carry. In[N - 1] XOR Carry. Out[N - 1] cpeg 323 -05 FTopic 3 b 13

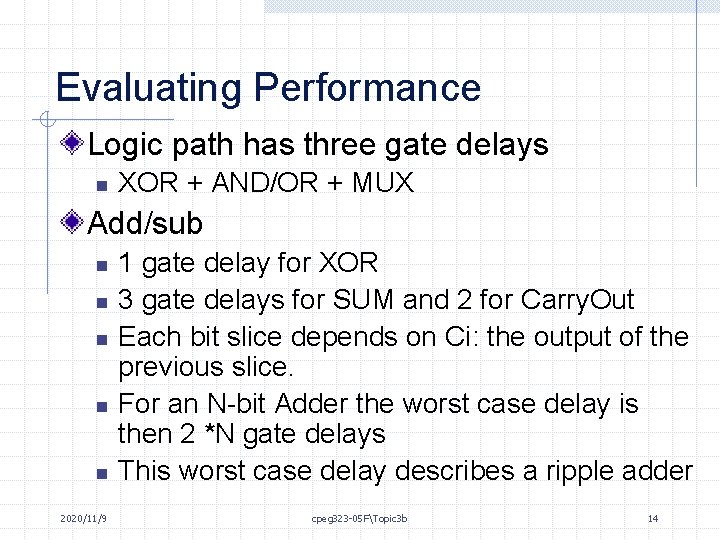

Evaluating Performance Logic path has three gate delays n XOR + AND/OR + MUX Add/sub n n n 2020/11/9 1 gate delay for XOR 3 gate delays for SUM and 2 for Carry. Out Each bit slice depends on Ci: the output of the previous slice. For an N-bit Adder the worst case delay is then 2 *N gate delays This worst case delay describes a ripple adder cpeg 323 -05 FTopic 3 b 14

Evaluating Performance – ALU Block The ALU speed is limited by its slowest block. n n The logic block has 2 gate delays The add/subtract has 2*N + 1 gate delays, where N >> 1 The arithmetic block is significantly limiting performance Consider ways to reduce gate delays in adder 2020/11/9 cpeg 323 -05 FTopic 3 b 15

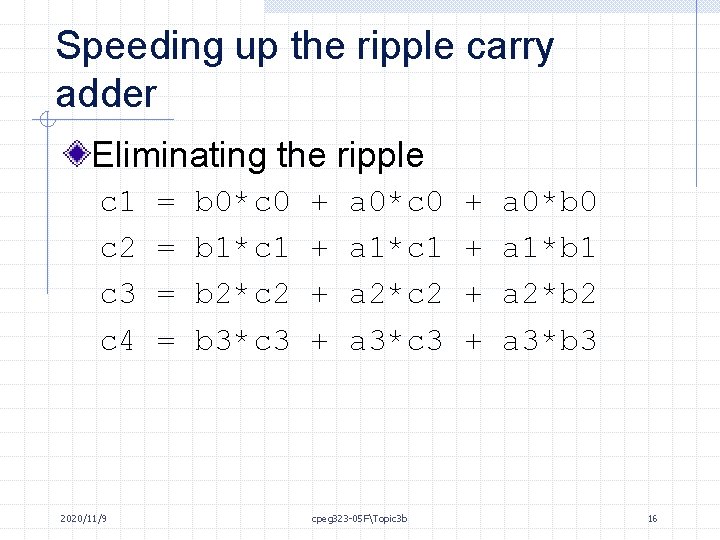

Speeding up the ripple carry adder Eliminating the ripple c 1 c 2 c 3 c 4 2020/11/9 = = b 0*c 0 b 1*c 1 b 2*c 2 b 3*c 3 + + a 0*c 0 a 1*c 1 a 2*c 2 a 3*c 3 cpeg 323 -05 FTopic 3 b + + a 0*b 0 a 1*b 1 a 2*b 2 a 3*b 3 16

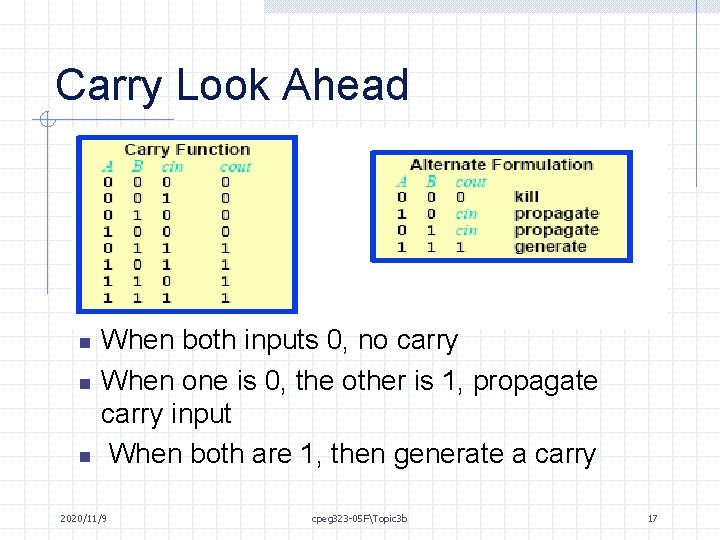

Carry Look Ahead n n n When both inputs 0, no carry When one is 0, the other is 1, propagate carry input When both are 1, then generate a carry 2020/11/9 cpeg 323 -05 FTopic 3 b 17

Carry-lookahead adder Generate gi = ai * bi Propagate pi = ai + bi Write carry out as function of preceding g, p, & co c 1 = g 0 + p 0*c 0 c 2 = g 1 + p 1*c 1 c 3 = g 2 + p 2*c 2 c 4 = g 3 + p 3*c 3 2020/11/9 cpeg 323 -05 FTopic 3 b 18

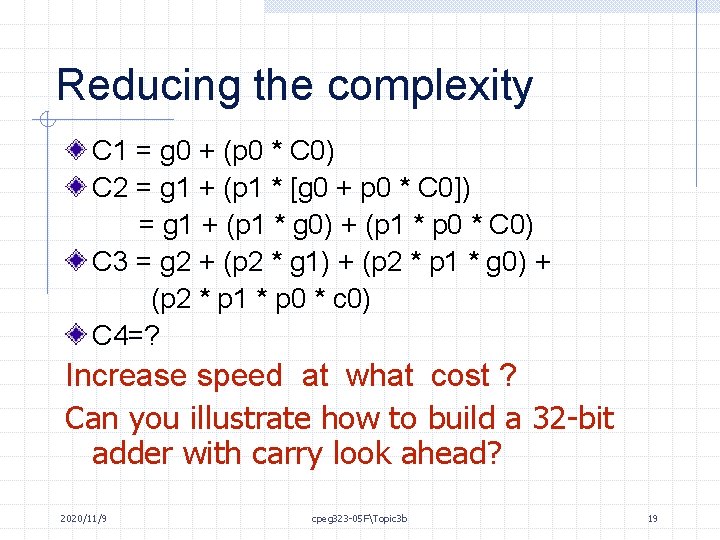

Reducing the complexity C 1 = g 0 + (p 0 * C 0) C 2 = g 1 + (p 1 * [g 0 + p 0 * C 0]) = g 1 + (p 1 * g 0) + (p 1 * p 0 * C 0) C 3 = g 2 + (p 2 * g 1) + (p 2 * p 1 * g 0) + (p 2 * p 1 * p 0 * c 0) C 4=? Increase speed at what cost ? Can you illustrate how to build a 32 -bit adder with carry look ahead? 2020/11/9 cpeg 323 -05 FTopic 3 b 19

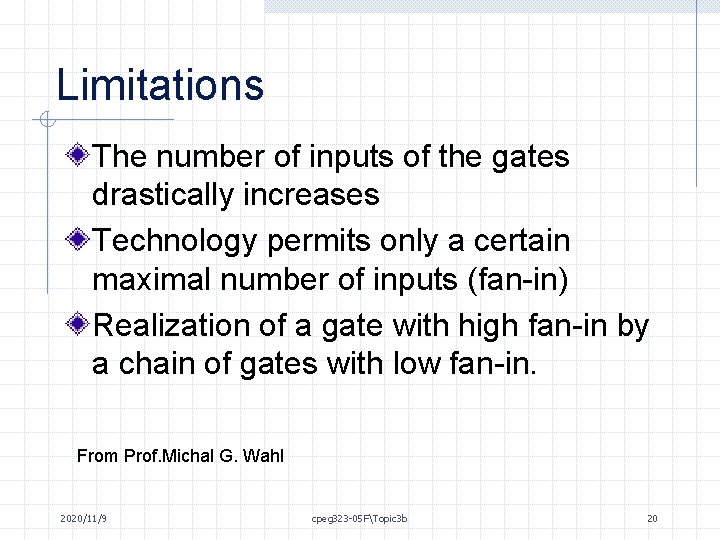

Limitations The number of inputs of the gates drastically increases Technology permits only a certain maximal number of inputs (fan-in) Realization of a gate with high fan-in by a chain of gates with low fan-in. From Prof. Michal G. Wahl 2020/11/9 cpeg 323 -05 FTopic 3 b 20

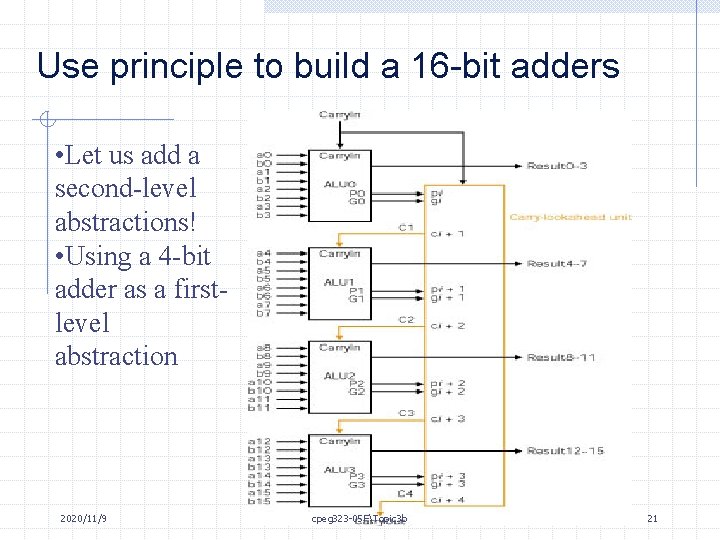

Use principle to build a 16 -bit adders • Let us add a second-level abstractions! • Using a 4 -bit adder as a firstlevel abstraction 2020/11/9 cpeg 323 -05 FTopic 3 b 21

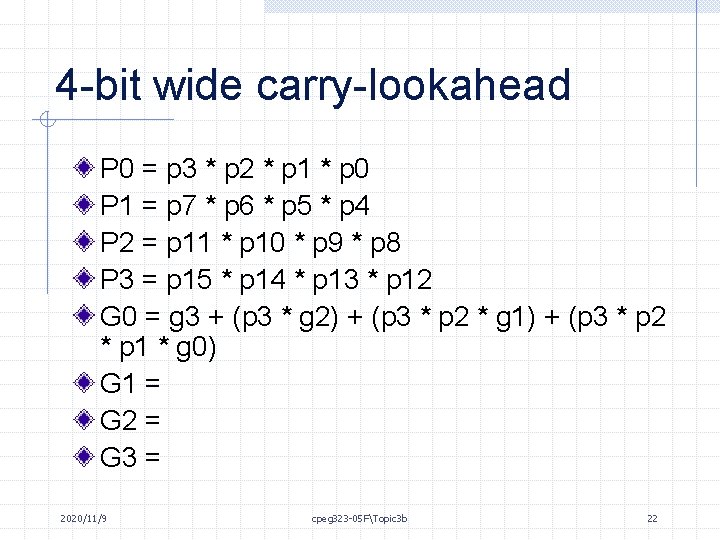

4 -bit wide carry-lookahead P 0 = p 3 * p 2 * p 1 * p 0 P 1 = p 7 * p 6 * p 5 * p 4 P 2 = p 11 * p 10 * p 9 * p 8 P 3 = p 15 * p 14 * p 13 * p 12 G 0 = g 3 + (p 3 * g 2) + (p 3 * p 2 * g 1) + (p 3 * p 2 * p 1 * g 0) G 1 = G 2 = G 3 = 2020/11/9 cpeg 323 -05 FTopic 3 b 22

- Slides: 22