ALU CPU Computer Architecture Introducing ALU ALU Arithmetic

- Slides: 15

ALU & CPU Computer Architecture

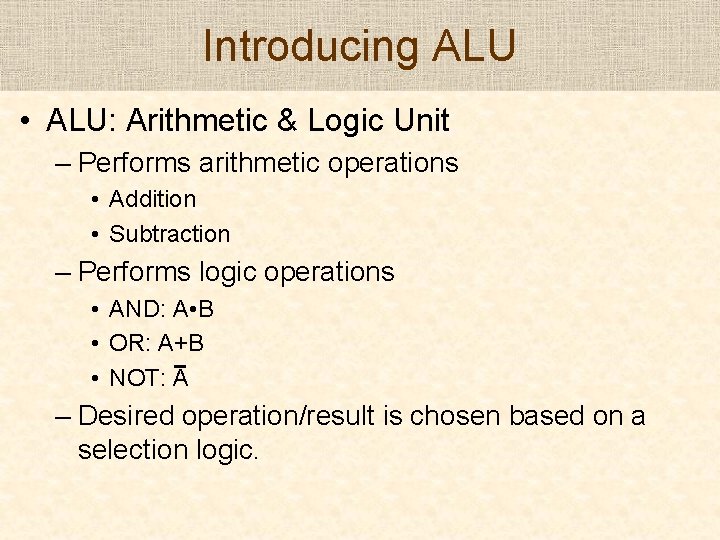

Introducing ALU • ALU: Arithmetic & Logic Unit – Performs arithmetic operations • Addition • Subtraction – Performs logic operations • AND: A • B • OR: A+B • NOT: A – Desired operation/result is chosen based on a selection logic.

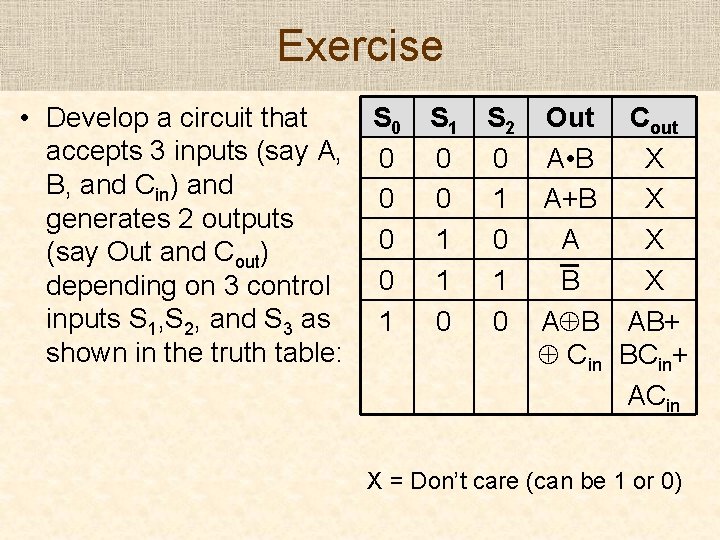

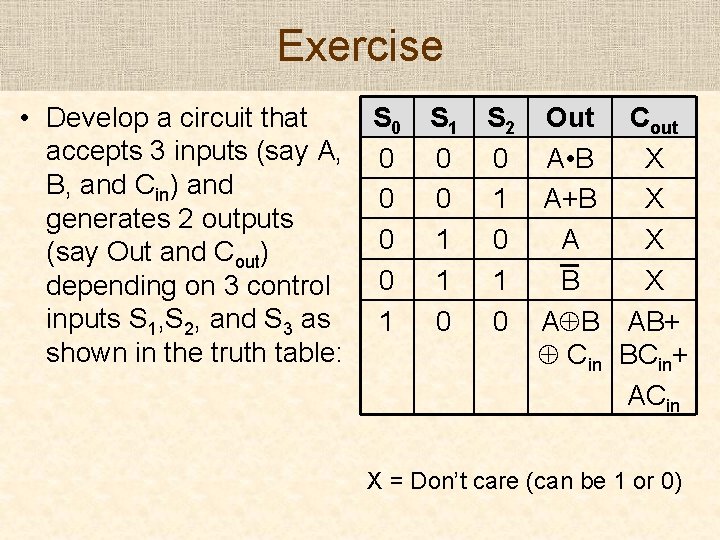

Exercise • Develop a circuit that accepts 3 inputs (say A, B, and Cin) and generates 2 outputs (say Out and Cout) depending on 3 control inputs S 1, S 2, and S 3 as shown in the truth table: S 0 0 0 1 S 1 0 0 1 1 0 S 2 Out Cout 0 A • B X 1 A+B X 0 A X 1 B X 0 A B AB+ Cin BCin+ ACin X = Don’t care (can be 1 or 0)

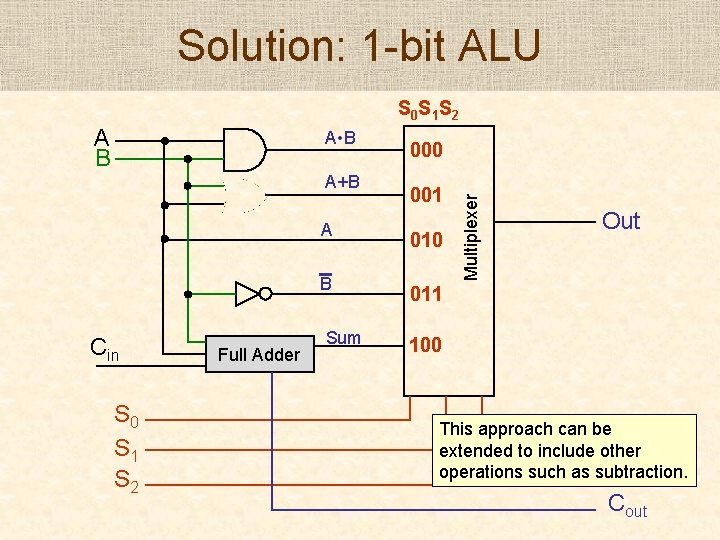

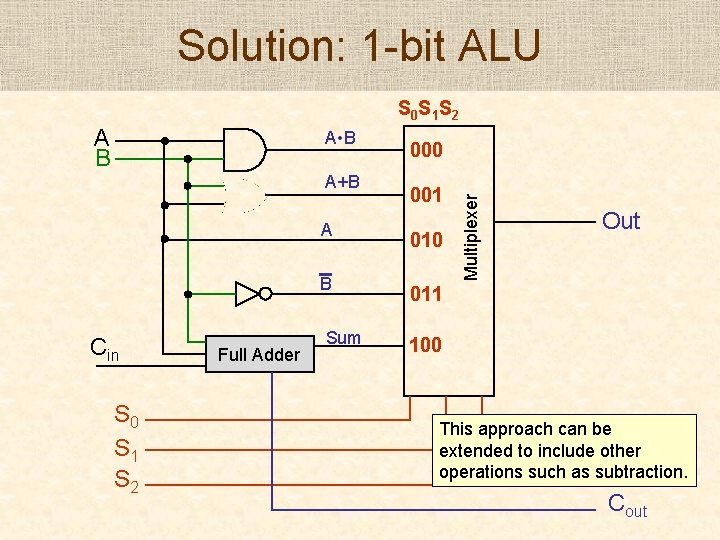

Solution: 1 -bit ALU S 0 S 1 S 2 A • B A+B A B Cin S 0 S 1 S 2 Full Adder Sum 000 001 010 Multiplexer A B Out 011 100 This approach can be extended to include other operations such as subtraction. Cout

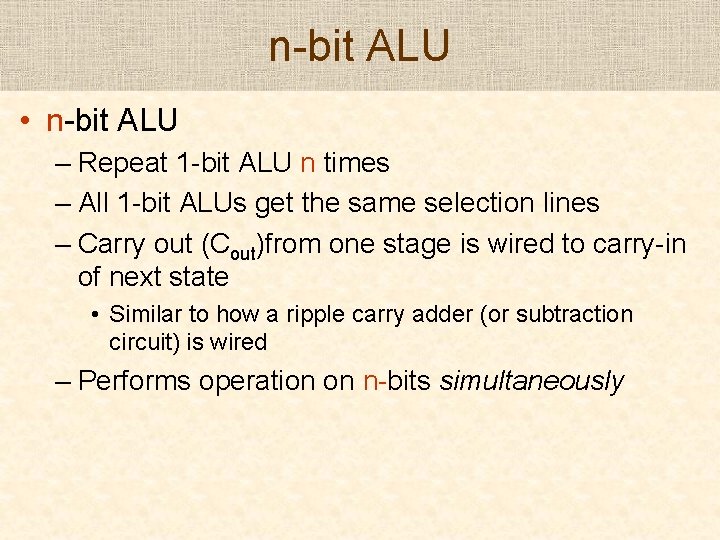

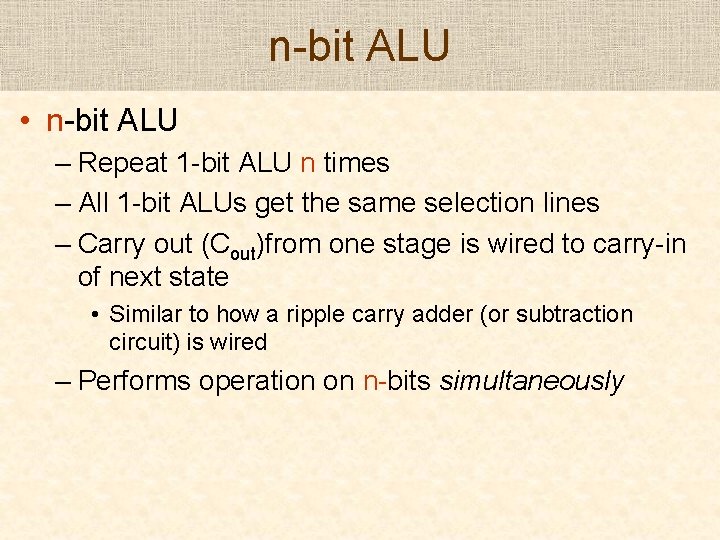

n-bit ALU • n-bit ALU – Repeat 1 -bit ALU n times – All 1 -bit ALUs get the same selection lines – Carry out (Cout)from one stage is wired to carry-in of next state • Similar to how a ripple carry adder (or subtraction circuit) is wired – Performs operation on n-bits simultaneously

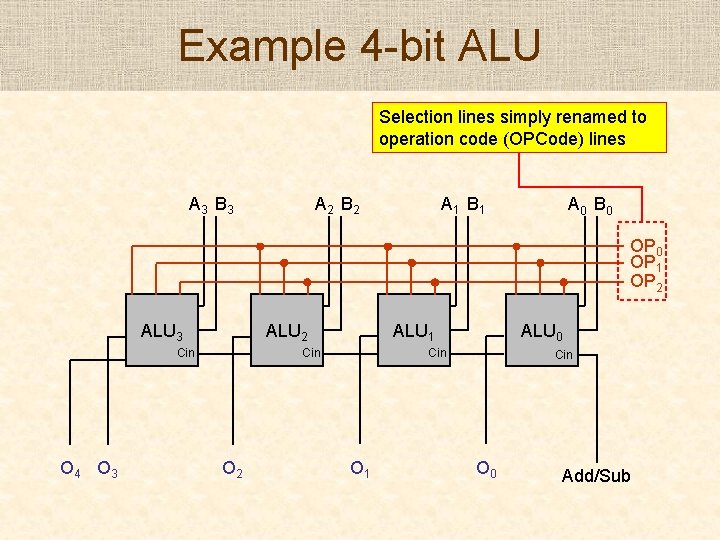

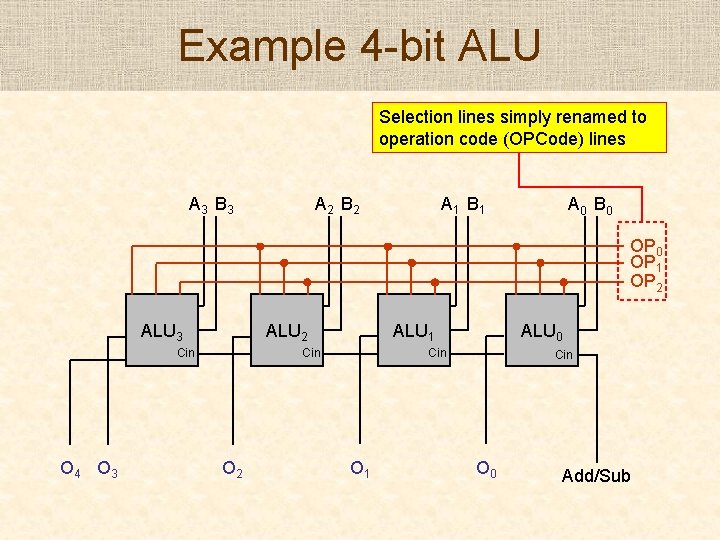

Example 4 -bit ALU Selection lines simply renamed to operation code (OPCode) lines A 3 B 3 A 2 B 2 A 1 B 1 A 0 B 0 OP 1 OP 2 ALU 3 ALU 2 Cin O 4 O 3 ALU 1 Cin O 2 ALU 0 Cin O 1 Cin O 0 Add/Sub

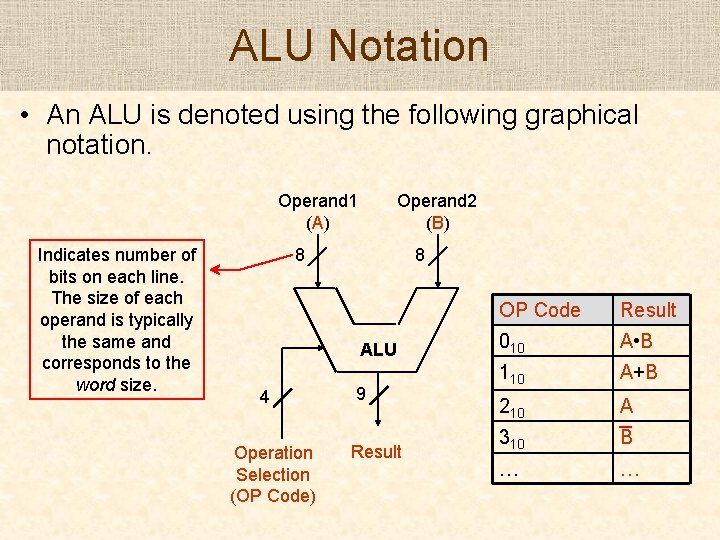

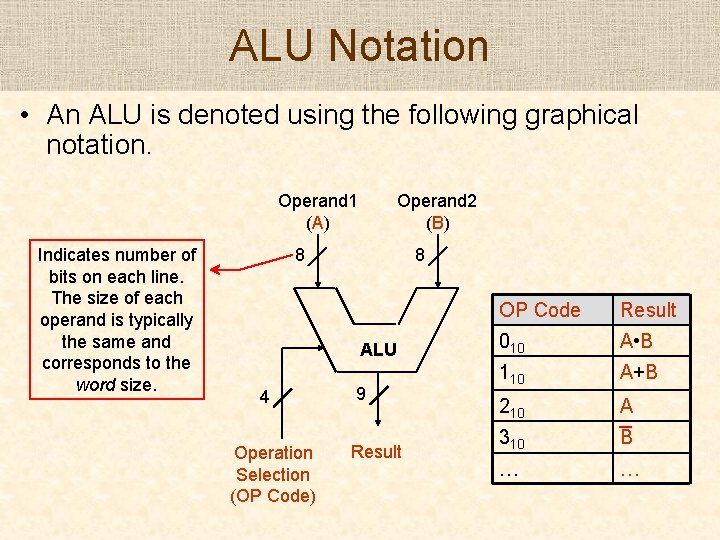

ALU Notation • An ALU is denoted using the following graphical notation. Operand 1 (A) Indicates number of bits on each line. The size of each operand is typically the same and corresponds to the word size. Operand 2 (B) 8 8 ALU 4 Operation Selection (OP Code) 9 Result OP Code Result 010 A • B 110 A+B 210 A 310 B … …

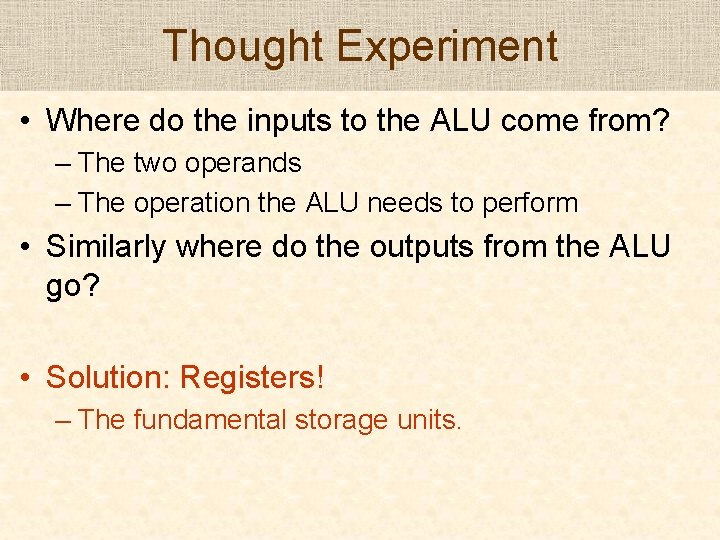

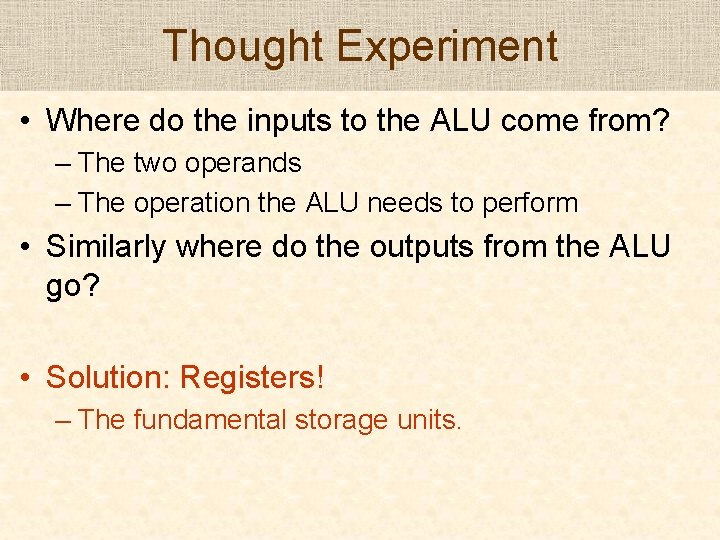

Thought Experiment • Where do the inputs to the ALU come from? – The two operands – The operation the ALU needs to perform • Similarly where do the outputs from the ALU go? • Solution: Registers! – The fundamental storage units.

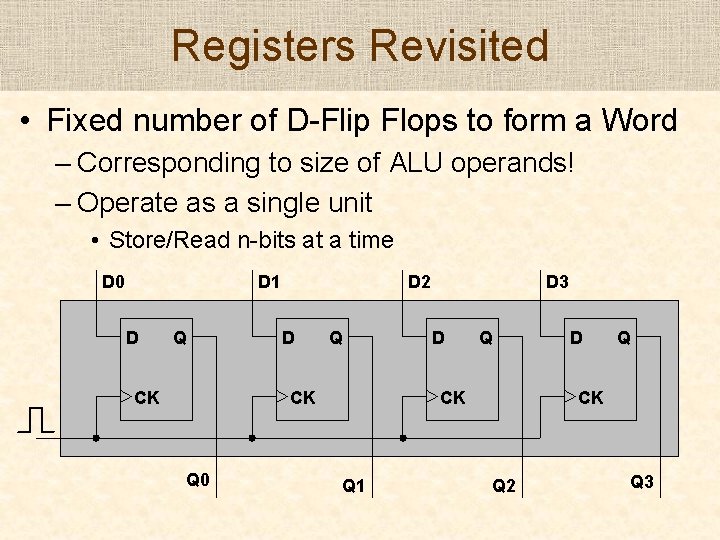

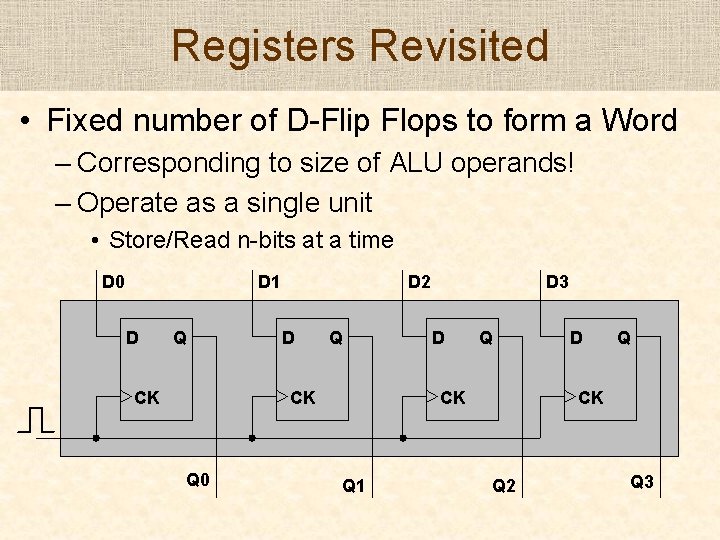

Registers Revisited • Fixed number of D-Flip Flops to form a Word – Corresponding to size of ALU operands! – Operate as a single unit • Store/Read n-bits at a time D 0 D 1 D Q CK D 2 D Q CK Q 0 D 3 D Q CK Q 1 D Q CK Q 2 Q 3

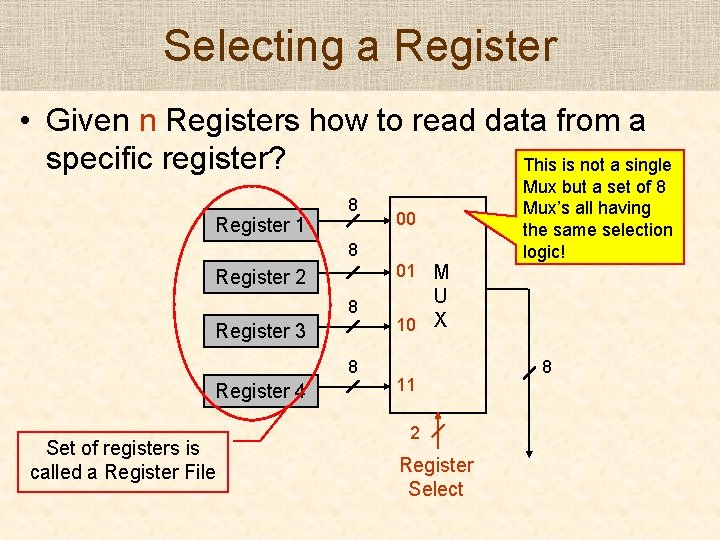

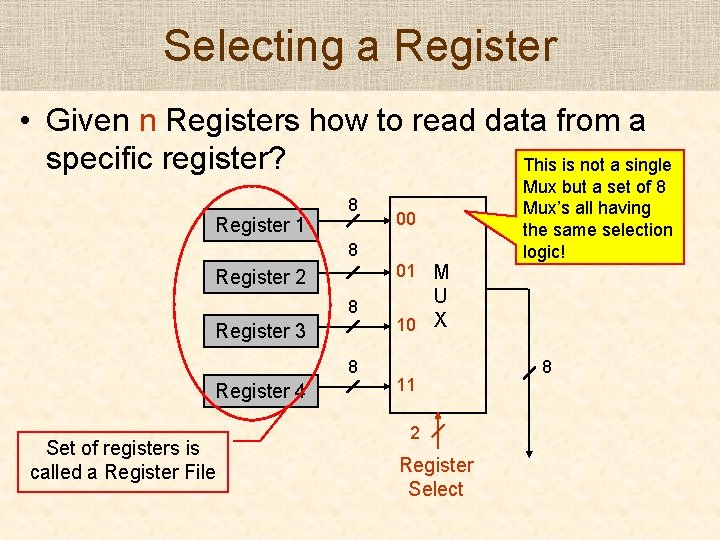

Selecting a Register • Given n Registers how to read data from a specific register? This is not a single Register 1 8 00 8 01 M Register 2 8 Register 3 8 Register 4 Set of registers is called a Register File Mux but a set of 8 Mux’s all having the same selection logic! U 10 X 11 2 Register Select 8

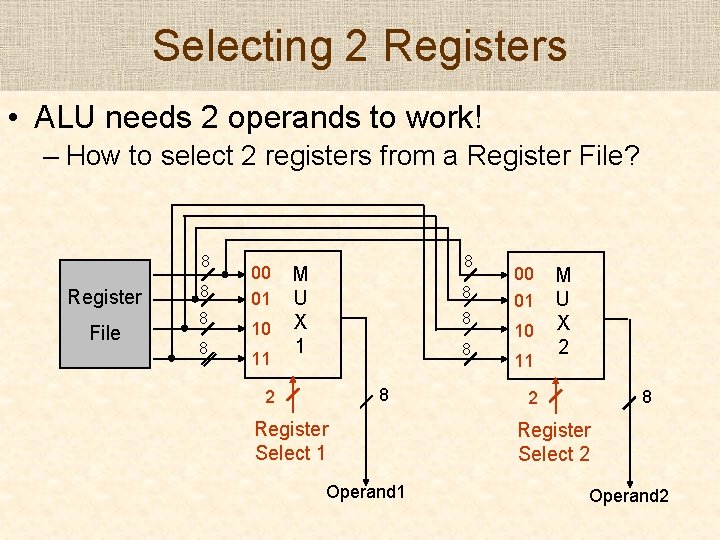

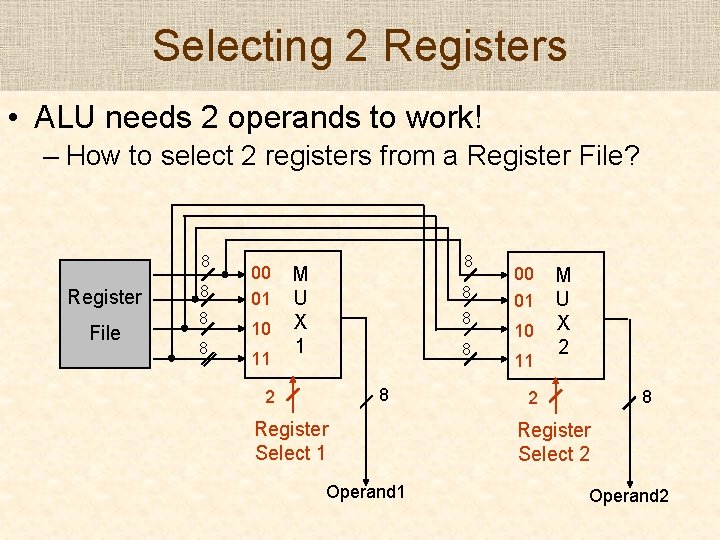

Selecting 2 Registers • ALU needs 2 operands to work! – How to select 2 registers from a Register File? 8 Register File 8 8 8 00 01 10 11 8 M U X 1 8 8 2 Register Select 1 Operand 1 00 01 10 11 M U X 2 8 2 Register Select 2 Operand 2

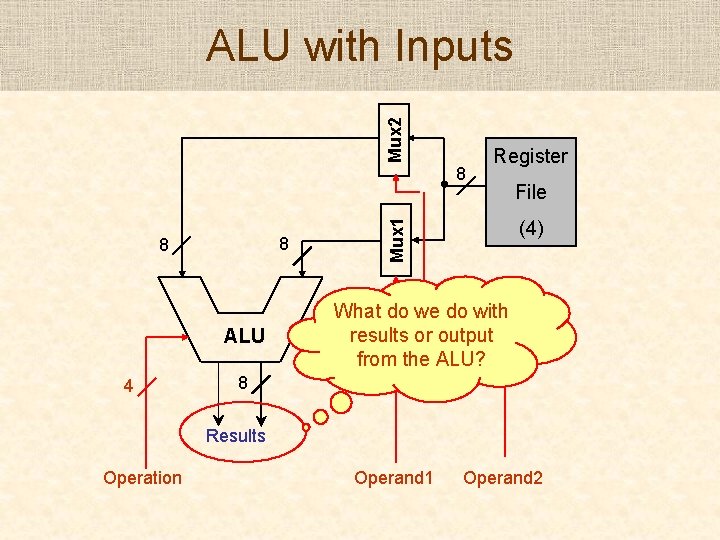

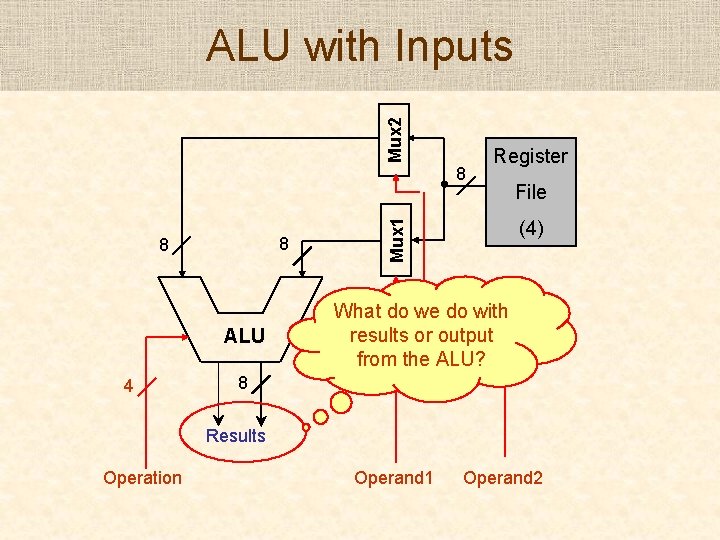

Mux 2 ALU with Inputs 8 8 ALU 4 8 Mux 1 8 Register File (4) What do we do with results or output from 2 the ALU? 2 Results Operation Operand 1 Operand 2

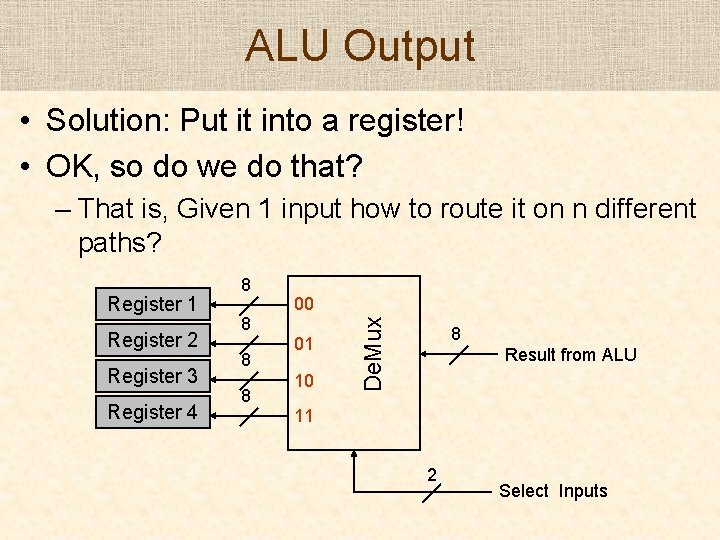

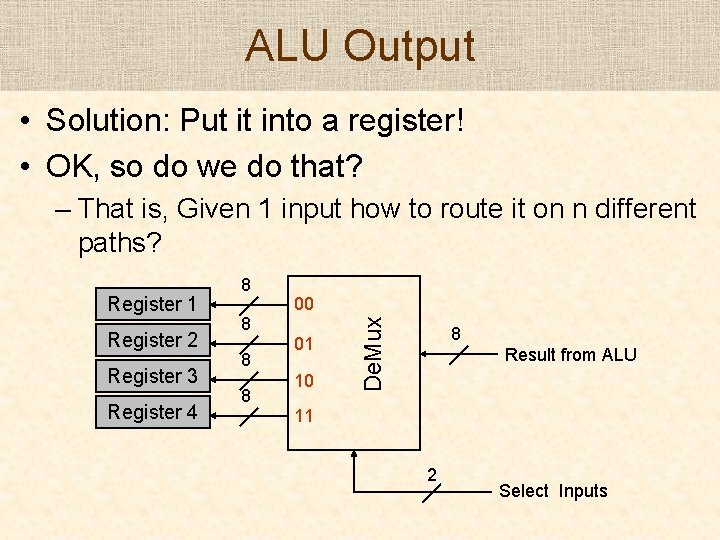

ALU Output • Solution: Put it into a register! • OK, so do we do that? – That is, Given 1 input how to route it on n different paths? Register 2 Register 3 Register 4 8 8 8 00 01 10 De. Mux Register 1 8 8 Result from ALU 11 2 Select Inputs

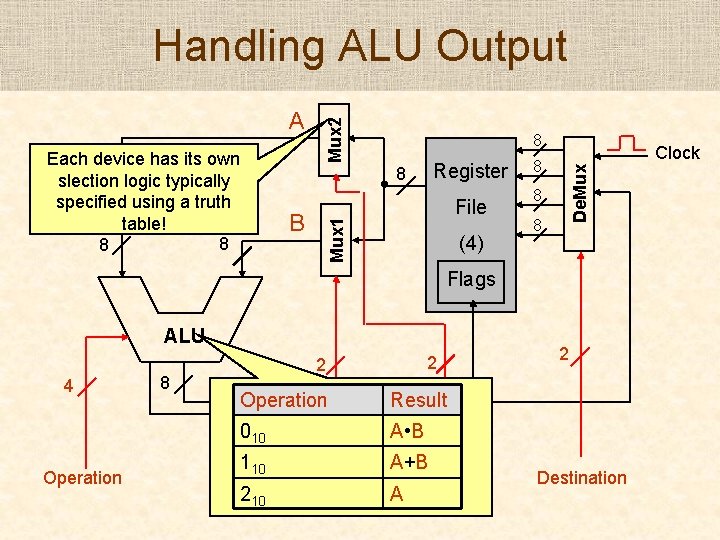

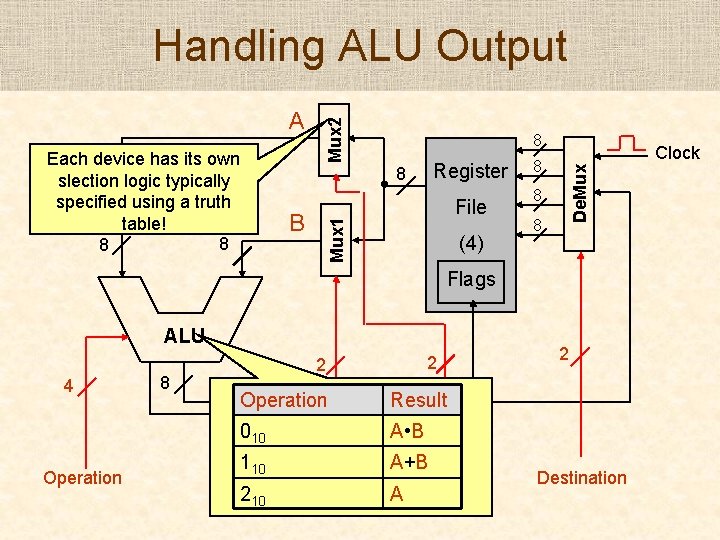

Each device has its own slection logic typically specified using a truth table! 8 8 8 Register 8 Mux 1 B File (4) Clock 8 De. Mux A Mux 2 Handling ALU Output 8 8 Flags ALU 4 Operation 8 2 2 Operation Result 010 A • B 110 210 Operand 1 A+B Operand 2 A 2 Destination

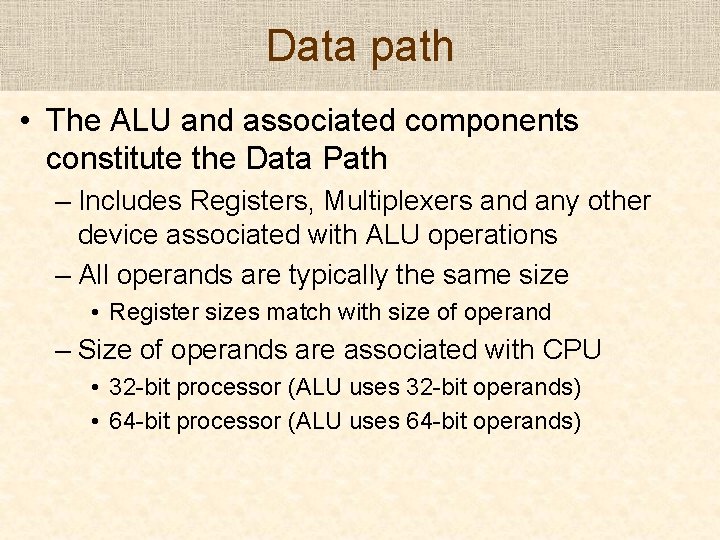

Data path • The ALU and associated components constitute the Data Path – Includes Registers, Multiplexers and any other device associated with ALU operations – All operands are typically the same size • Register sizes match with size of operand – Size of operands are associated with CPU • 32 -bit processor (ALU uses 32 -bit operands) • 64 -bit processor (ALU uses 64 -bit operands)